#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

ĿХF

| Product Status                  | Obsolete                                                             |

|---------------------------------|----------------------------------------------------------------------|

| Core Processor                  | PowerPC e500mc                                                       |

| Number of Cores/Bus Width       | 4 Core, 32-Bit                                                       |

| Speed                           | 1.3GHz                                                               |

| Co-Processors/DSP               | Security; SEC 4.2                                                    |

| RAM Controllers                 | DDR3, DDR3L                                                          |

| Graphics Acceleration           | No                                                                   |

| Display & Interface Controllers | -                                                                    |

| Ethernet                        | 10/100/1000Mbps (5), 10Gbps (1)                                      |

| SATA                            | SATA 3Gbps (2)                                                       |

| USB                             | USB 2.0 + PHY (2)                                                    |

| Voltage - I/O                   | 1.0V, 1.35V, 1.5V, 1.8V, 2.5V, 3.3V                                  |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                     |

| Security Features               | Boot Security, Cryptography, Random Number Generator, Secure Fusebox |

| Package / Case                  | 780-BBGA, FCBGA                                                      |

| Supplier Device Package         | 780-FCPBGA (23x23)                                                   |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=p2041nse1nnb            |

|                                 |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1 | Pin A  | ssignments and Reset States                        |

|---|--------|----------------------------------------------------|

|   | 1.1    | 780 FC-PBGA Ball Layout Diagrams4                  |

|   | 1.2    | Pinout List                                        |

| 2 | Electr | rical Characteristics                              |

|   | 2.1    | Overall DC Electrical Characteristics              |

|   | 2.2    | Power Up Sequencing                                |

|   | 2.3    | Power Down Requirements                            |

|   | 2.4    | Power Characteristics                              |

|   | 2.5    | Thermal                                            |

|   | 2.6    | Input Clocks                                       |

|   | 2.7    | RESET Initialization                               |

|   | 2.8    | Power-on Ramp Rate                                 |

|   | 2.9    | DDR3 and DDR3L SDRAM Controller                    |

|   | 2.10   | eSPI                                               |

|   | 2.11   | DUART                                              |

|   | 2.12   | Ethernet: Data path Three-Speed Ethernet (dTSEC),  |

|   |        | Management Interface, IEEE Std 1588                |

|   | 2.13   | USB                                                |

|   | 2.14   | Enhanced Local Bus Interface                       |

|   | 2.15   | Enhanced Secure Digital Host Controller (eSDHC)74  |

|   | 2.16   | Multicore Programmable Interrupt Controller (MPIC) |

|   |        | Specifications                                     |

|   | 2.17   | JTAG Controller                                    |

|   | 2.18  | l <sup>2</sup> C                                     |

|---|-------|------------------------------------------------------|

|   | 2.19  | GPIO                                                 |

|   | 2.20  | High-Speed Serial Interfaces (HSSI)                  |

| 3 | Hard  | ware Design Considerations 110                       |

|   | 3.1   | System Clocking 110                                  |

|   | 3.2   | Supply Power Default Setting 117                     |

|   | 3.3   | Power Supply Design 119                              |

|   | 3.4   | Decoupling Recommendations 121                       |

|   | 3.5   | SerDes Block Power Supply Decoupling                 |

|   |       | Recommendations                                      |

|   | 3.6   | Connection Recommendations                           |

|   | 3.7   | Recommended Thermal Model                            |

|   | 3.8   | Thermal Management Information 130                   |

| 4 | Pack  | age Information                                      |

|   | 4.1   | Package Parameters for the FC-PBGA 132               |

|   | 4.2   | Mechanical Dimensions of the FC-PBGA 133             |

| 5 | Secu  | rity Fuse Processor                                  |

| 6 | Orde  | ring Information                                     |

|   | 6.1   | Part Numbering Nomenclature                          |

|   | 6.2   | Orderable Part Numbers Addressed by this Document134 |

| 7 | Revis | sion History 136                                     |

#### **Pin Assignments and Reset States**

### Table 1. Pin List by Bus (continued)

| Signal                                                           | Signal Description           | Package<br>Pin Number | Pin<br>Type | Power<br>Supply  | Note   |

|------------------------------------------------------------------|------------------------------|-----------------------|-------------|------------------|--------|

| EVT8/GPIO29/IRQ11                                                | Event 8                      | AC24                  | I/O         | $OV_{DD}$        | _      |

| EVT9/IRQ_OUT                                                     | Event 9                      | Y24                   | I/O         | $OV_{DD}$        | —      |

| M1DVAL/LB_DVAL/IIC3_SCL/GPIO16/<br>SDHC_CD/DMA1_DACK0            | Debug Data Valid             | AB23                  | 0           | $OV_{DD}$        | -      |

| MSRCID0/LB_SRCID0/IIC3_SDA/GPIO17/<br>DMA_DDONE0/SDHC_WP         | Debug Source ID 0            | AB26                  | 0           | $OV_{DD}$        | 4, 31  |

| MSRCID1/LB_MSRCID1/EVT5/IIC4_SCL/<br>LB_SRCID1/GPIO18/DMA1_DREQ0 | Debug Source ID 1            | AC23                  | 0           | $OV_{DD}$        | -      |

| MSRCID2/LB_SRCID2/EVT6/IIC4_SDA/<br>LB_SRCID2/GPIO19             | Debug Source ID 2            | V24                   | 0           | $OV_{DD}$        | _      |

| CLK_OUT                                                          | Clock Out                    | T27                   | 0           | $OV_{DD}$        | 6      |

|                                                                  | Clock                        |                       | I           |                  | 1      |

| RTC                                                              | Real Time Clock              | P28                   | I           | OV <sub>DD</sub> |        |

| SYSCLK                                                           | System Clock                 | R28                   | I           | OV <sub>DD</sub> | _      |

|                                                                  | JTAG                         | -                     | 11          |                  | 1      |

| ТСК                                                              | Test Clock                   | Y28                   | Ι           | OV <sub>DD</sub> | _      |

| TDI                                                              | Test Data In                 | W28                   | I           | OV <sub>DD</sub> | 7      |

| TDO                                                              | Test Data Out                | AA28                  | 0           | OV <sub>DD</sub> | 6      |

| TMS                                                              | Test Mode Select             | W27                   | I           | $OV_{DD}$        | 7      |

| TRST                                                             | Test Reset                   | Y27                   | I           | $OV_DD$          | 7      |

|                                                                  | DFT                          |                       |             |                  | 1      |

| SCAN_MODE                                                        | Scan Mode                    | V28                   | Ι           | OV <sub>DD</sub> | 35     |

| TEST_SEL                                                         | Test Mode Select             | T28                   | I           | OV <sub>DD</sub> | 12, 26 |

|                                                                  | Power Management             |                       | 11          |                  |        |

| ASLEEP                                                           | Asleep                       | R22                   | 0           | OV <sub>DD</sub> | 31     |

|                                                                  | Input /Output Voltage Select |                       |             |                  |        |

| IO_VSEL0                                                         | I/O Voltage Select           | AB28                  | I           | OV <sub>DD</sub> | 27     |

| IO_VSEL1                                                         | I/O Voltage Select           | U23                   | I           | OV <sub>DD</sub> | 27     |

| IO_VSEL2                                                         | I/O Voltage Select           | AB21                  | I           | OV <sub>DD</sub> | 27     |

| IO_VSEL3                                                         | I/O Voltage Select           | Y23                   | I           | OV <sub>DD</sub> | 27     |

| IO_VSEL4                                                         | I/O Voltage Select           | Y21                   | I           | OV <sub>DD</sub> | 27     |

|                                                                  | Power and Ground Signals     |                       | 1           |                  | 1      |

| GND168                                                           | Ground                       | A23                   |             | _                | _      |

| GND167                                                           | Ground                       | B23                   |             | _                |        |

#### **Pin Assignments and Reset States**

### Table 1. Pin List by Bus (continued)

| Signal         | Signal Description                  | Package<br>Pin Number | Pin<br>Type | Power<br>Supply | Note |

|----------------|-------------------------------------|-----------------------|-------------|-----------------|------|

| XGND08         | SerDes Transceiver GND              | C21                   | _           | _               | _    |

| XGND07         | SerDes Transceiver GND              | D9                    | —           | _               | _    |

| XGND06         | SerDes Transceiver GND              | D13                   |             | _               |      |

| XGND05         | SerDes Transceiver GND              | D19                   | —           | —               | _    |

| XGND04         | SerDes Transceiver GND              | F6                    | —           | —               | —    |

| XGND03         | SerDes Transceiver GND              | F21                   | —           | —               | -    |

| XGND02         | SerDes Transceiver GND              | G3                    | —           | —               | -    |

| XGND01         | SerDes Transceiver GND              | H5                    | —           |                 | _    |

| SGND17         | SerDes Core Logic GND               | A5                    | —           | _               |      |

| SGND16         | SerDes Core Logic GND               | A8                    | —           | —               | _    |

| SGND15         | SerDes Core Logic GND               | A12                   | —           | —               | _    |

| SGND14         | SerDes Core Logic GND               | A16                   | —           | —               | -    |

| SGND13         | SerDes Core Logic GND               | A20                   | —           | —               | —    |

| SGND12         | SerDes Core Logic GND               | B1                    | —           | —               | -    |

| SGND11         | SerDes Core Logic GND               | B6                    | —           | —               | —    |

| SGND10         | SerDes Core Logic GND               | B10                   | —           | —               | —    |

| SGND09         | SerDes Core Logic GND               | B14                   | —           | —               | -    |

| SGND08         | SerDes Core Logic GND               | B18                   | —           | —               | —    |

| SGND07         | SerDes Core Logic GND               | B22                   | —           | —               | —    |

| SGND06         | SerDes Core Logic GND               | C3                    | —           | —               | —    |

| SGND05         | SerDes Core Logic GND               | D2                    | —           | —               | _    |

| SGND04         | SerDes Core Logic GND               | D17                   | —           | —               | -    |

| SGND03         | SerDes Core Logic GND               | E3                    | —           | —               | —    |

| SGND02         | SerDes Core Logic GND               | F1                    | —           | —               | —    |

| SGND01         | SerDes Core Logic GND               | H2                    | —           | —               | —    |

| AGND_SRDS1     | SerDes PLL1 GND                     | C2                    | —           | —               | _    |

| AGND_SRDS2     | SerDes PLL2 GND                     | B17                   | —           | —               | —    |

| SENSEGND_CA_PL | Core Group A and Platform GND Sense | G8                    | —           | —               | 8    |

| SENSEGND_CB    | Core Group B GND Sense              | AA16                  | —           | —               | 8    |

| USB1_AGND06    | USB1 PHY Transceiver GND            | J28                   | —           | —               | _    |

| USB1_AGND05    | USB1 PHY Transceiver GND            | K27                   | —           |                 | -    |

| USB1_AGND04    | USB1 PHY Transceiver GND            | L27                   | —           | —               | -    |

| USB1_AGND03    | USB1 PHY Transceiver GND            | M22                   | —           |                 | -    |

| USB1_AGND02    | USB1 PHY Transceiver GND            | M24                   | _           | _               | _    |

### Table 2. Absolute Operating Conditions<sup>1</sup> (continued)

| Parameter | Symbol | Max Value | Unit | Note |

|-----------|--------|-----------|------|------|

| Note:     |        |           |      |      |

- 1. Functional operating conditions are given in Table 3. Absolute maximum ratings are stress ratings only; functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- Caution: MV<sub>IN</sub> must not exceed GV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 3. Caution: LV<sub>IN</sub> must not exceed LV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 4. **Caution:** CV<sub>IN</sub> must not exceed CV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 5. Caution: BV<sub>IN</sub> must not exceed BV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 6. Caution: OV<sub>IN</sub> must not exceed OV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 7. (C,X,B,G,L,O)V<sub>IN</sub> may overshoot (for V<sub>IH</sub>) or undershoot (for V<sub>IL</sub>) to the voltages and maximum duration shown in Figure 7.

- Ethernet MII Management Interface 2 pins function as open drain I/Os. The interface conforms to 1.2 V nominal voltage levels. LV<sub>DD</sub> must be powered to use this interface.

- 9. Supply voltage specified at the voltage sense pin. Voltage input pins must be regulated to provide specified voltage at the sense pin.

- 10.Core Group A and Platform supply (VDD\_CA\_PL) and Core Group B supply (VDD\_CB) were separate supplies in Rev1.0, they are tied together in Rev1.1.

## 2.1.2 Recommended Operating Conditions

This table provides the recommended operating conditions for this device. Note that proper device operation outside these conditions is not guaranteed.

| Parameter                                                                                                                                      | Symbol                   | Recommended Value                           | Unit | Note |

|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------------------------|------|------|

| Core Group A (cores 0–1) and platform supply voltage (Silicon Rev 1.0)                                                                         | V <sub>DD_CA_PL</sub>    | 1.0 ± 50 mV                                 | V    | 4, 5 |

| Core Group B (cores 2–3) supply voltage<br>(Silicon Rev 1.0)                                                                                   | V <sub>DD_CB</sub>       | 1.0 ± 50 mV                                 | V    | 4, 5 |

| Core Group A (cores 0–1), Core Group B<br>(cores 2–3) and platform supply voltage<br>(Silicon Rev 1.1)                                         | V <sub>DD_CA_CB_PL</sub> | 1.0 ± 50 mV                                 | V    | 4, 5 |

| PLL supply voltage (core, platform, DDR)                                                                                                       | AV <sub>DD</sub>         | 1.0 ± 50 mV                                 | V    | _    |

| PLL supply voltage (SerDes)                                                                                                                    | AV <sub>DD_SRDS</sub>    | 1.0 ± 50 mV                                 | V    | _    |

| Fuse programming override supply                                                                                                               | POV <sub>DD</sub>        | 1.5 ± 75 mV                                 | V    | 2    |

| DUART, I <sup>2</sup> C, DMA, MPIC, GPIO, system<br>control and power management, clocking,<br>debug, I/O voltage select, and JTAG I/O voltage | OV <sub>DD</sub>         | 3.3 ± 165 mV                                | V    | -    |

| eSPI, eSDHC, GPIO                                                                                                                              | CV <sub>DD</sub>         | 3.3 ± 165 mV<br>2.5 ± 125 mV<br>1.8 ± 90 mV | V    | _    |

| DDR DRAM I/O voltage<br>DDR3<br>DDR3L                                                                                                          | GV <sub>DD</sub>         | 1.5 ± 75 mV<br>1.35 ± 67 mV                 | V    | _    |

**Table 3. Recommended Operating Conditions**

While VDD is ramping, current may be supplied from VDD through the chip to GVDD. Nevertheless, GVDD from an external supply should follow the sequencing described above.

### WARNING

Only 100,000 POR cycles are permitted per lifetime of a device.

All supplies must be at their stable values within 75 ms.

Items on the same line have no ordering requirement with respect to one another. Items on separate lines must be ordered sequentially such that voltage rails on a previous step must reach 90% of their value before the voltage rails on the current step reach 10% of theirs.

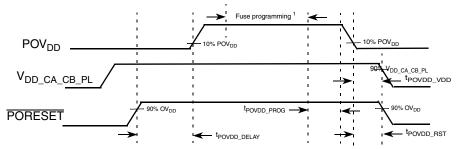

This figure provides the  $POV_{DD}$  timing diagram.

**NOTE:** POV<sub>DD</sub> must be stable at 1.5 V prior to initiating fuse programming.

### Figure 8. POV<sub>DD</sub> Timing Diagram

This table provides information on the power-down and power-up sequence parameters for POV<sub>DD</sub>.

Table 5. POV<sub>DD</sub> Timing <sup>5</sup>

| Driver Type              | Min | Мах | Unit    | Note |

|--------------------------|-----|-----|---------|------|

| <sup>t</sup> POVDD_DELAY | 100 | —   | SYSCLKs | 1    |

| tpovdd_prog              | 0   | —   | μs      | 2    |

| tpovdd_vdd               | 0   | —   | μs      | 3    |

| <sup>t</sup> povdd_rst   | 0   | —   | μs      | 4    |

Note:

1. Delay required from the negation of PORESET to driving POV<sub>DD</sub> ramp up. Delay measured from PORESET negation at 90% OV<sub>DD</sub> to 10% POV<sub>DD</sub> ramp up.

Delay required from fuse programming finished to POV<sub>DD</sub> ramp down start. Fuse programming must complete while POV<sub>DD</sub> is stable at 1.5 V. No activity other than that required for secure boot fuse programming is permitted while POV<sub>DD</sub> driven to any voltage above GND, including the reading of the fuse block. The reading of the fuse block may only occur while POV<sub>DD</sub> = GND. After fuse programming is completed, it is required to return POV<sub>DD</sub> = GND.

Delay required from POV<sub>DD</sub> ramp down complete to V<sub>DD\_CA\_CB\_PL</sub> ramp down start. POV<sub>DD</sub> must be grounded to minimum 10% POV<sub>DD</sub> before V<sub>DD\_CA\_CB\_PL</sub> is at 90% V<sub>DD</sub>.

Delay required from POV<sub>DD</sub> ramp down complete to PORESET assertion. POV<sub>DD</sub> must be grounded to minimum 10% POV<sub>DD</sub> before PORESET assertion reaches 90% OV<sub>DD</sub>.

5. Only two secure boot fuse programming events are permitted per lifetime of a device.

To guarantee MCKE low during power up, the above sequencing for  $GV_{DD}$  is required. If there is no concern about any of the DDR signals being in an indeterminate state during power up, the sequencing for  $GV_{DD}$  is not required.

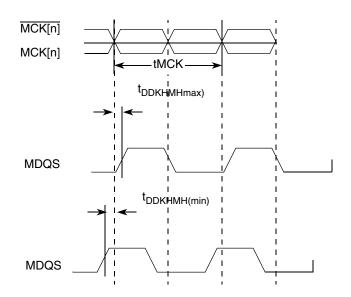

This figure shows the DDR3 and DDR3L SDRAM interface output timing for the MCK to MDQS skew measurement (t<sub>DDKHMH</sub>).

Figure 10. t<sub>DDKHMH</sub> Timing Diagram

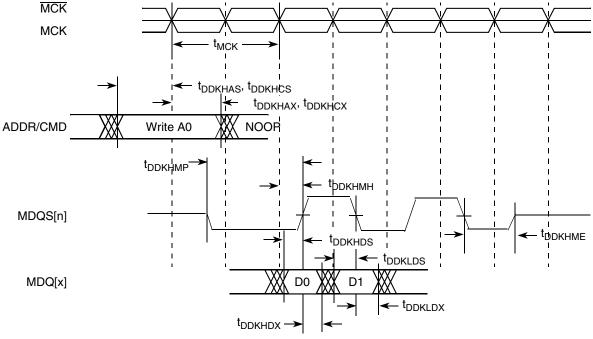

This figure shows the DDR3 and DDR3L SDRAM output timing diagram.

Figure 11. DDR3 and DDR3L Output Timing Diagram

## 2.11.2 DUART AC Electrical Specifications

This table provides the AC timing parameters for the DUART interface.

### Table 35. DUART AC Timing Specifications

For recommended operating conditions, see Table 3.

| Parameter         | Parameter Value                    |      | Note |

|-------------------|------------------------------------|------|------|

| Minimum baud rate | f <sub>PLAT</sub> /(2 × 1,048,576) | baud | 1    |

| Maximum baud rate | f <sub>PLAT</sub> /(2 × 16)        | baud | 1, 2 |

| Oversample rate   | 16                                 | _    | 3    |

Note:

- 1. f<sub>PLAT</sub> refers to the internal platform clock.

- 2. The actual attainable baud rate is limited by the latency of interrupt processing.

- 3. The middle of a start bit is detected as the eighth sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled every 16<sup>th</sup> sample.

## 2.12 Ethernet: Data path Three-Speed Ethernet (dTSEC), Management Interface, IEEE Std 1588

This section provides the AC and DC electrical characteristics for the data path three-speed Ethernet controller, the Ethernet Management Interface, and the IEEE Std 1588 interface.

## 2.12.1 SGMII Timing Specifications

See Section 2.20.8, "SGMII Interface."

## 2.12.2 RGMII Timing Specifications

This section discusses the electrical characteristics for the MII and RGMII interfaces.

## 2.12.2.1 RGMII DC Electrical Characteristics

This table shows the RGMII DC electrical characteristics when operating at  $LV_{DD} = 2.5$  V supply.

### Table 36. RGMII DC Electrical Characteristics (LV<sub>DD</sub> = 2.5 V)

For recommended operating conditions, see Table 3.

| Parameter                                                        | Symbol          | Min  | Мах  | Unit | Note |

|------------------------------------------------------------------|-----------------|------|------|------|------|

| Input high voltage                                               | V <sub>IH</sub> | 1.70 | _    | V    | 1    |

| Input low voltage                                                | V <sub>IL</sub> |      | 0.70 | V    | 1    |

| Input current ( $LV_{IN} = 0$ V or $LV_{IN} = LV_{DD}$ )         | I <sub>IH</sub> | _    | ±40  | μA   | 2    |

| Output high voltage (LV <sub>DD</sub> = min, $I_{OH} = -1.0$ mA) | V <sub>OH</sub> | 2.00 | _    | V    |      |

| Output low voltage ( $LV_{DD}$ = min, $I_{OL}$ = 1.0 mA)         | V <sub>OL</sub> | _    | 0.40 | V    |      |

Note:

1. The min  $V_{IL}$  and max  $V_{IH}$  values are based on the respective min and max  $LV_{IN}$  values found in Table 3.

2. The symbol V<sub>IN</sub>, in this case, represents the LV<sub>IN</sub> symbols referenced in Table 2 and Table 3.

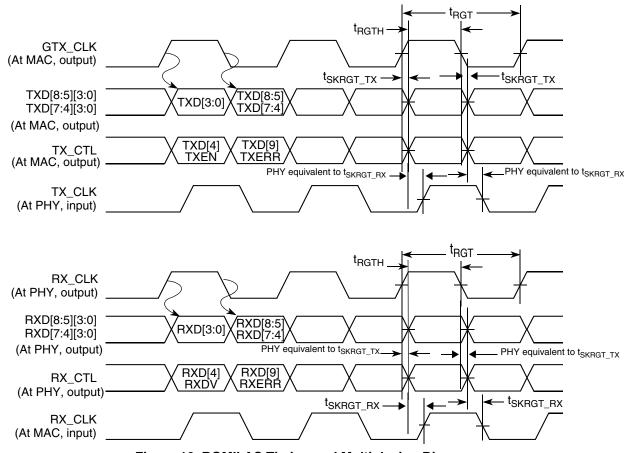

Figure 16. RGMII AC Timing and Multiplexing Diagrams

## 2.12.3 Ethernet Management Interface

This section discusses the electrical characteristics for the EMI1 interfaces. EMI1 is the PHY management interface controlled by the MDIO controller associated with Frame Manager 1 1GMAC–1.

## 2.12.3.1 Ethernet Management Interface DC Electrical Characteristics

The Ethernet management interface is defined to operate at a supply voltage of 3.3 V. The DC electrical characteristics for the Ethernet management interface is provided in this table.

### Table 38. Ethernet Management Interface DC Electrical Characteristics (LV<sub>DD</sub> = 3.3 V)

For recommended operating conditions, see Table 3.

| Parameter                                                             | Symbol          | Min  | Max | Unit | Note |

|-----------------------------------------------------------------------|-----------------|------|-----|------|------|

| Input high voltage                                                    | V <sub>IH</sub> | 2.0  | —   | V    | 2    |

| Input low voltage                                                     | V <sub>IL</sub> | _    | 0.9 | V    | 2    |

| Input high current (LV <sub>DD</sub> = Max, V <sub>IN</sub> = 2.1 V)  | I <sub>IH</sub> |      | 40  | μΑ   | 1    |

| Input low current (LV <sub>DD</sub> = Max, V <sub>IN</sub> = 0.5 V)   | IIL             | -600 | —   | μΑ   | 1    |

| Output high voltage ( $LV_{DD} = Min$ , $I_{OH} = -1.0 mA$ )          | V <sub>OH</sub> | 2.4  | _   | V    | _    |

| Output low voltage (LV <sub>DD</sub> = Min, I <sub>OL</sub> = 1.0 mA) | V <sub>OL</sub> |      | 0.4 | V    |      |

### Table 52. MPIC DC Electrical Characteristics (OV<sub>DD</sub> = 3.3 V) (continued)

For recommended operating conditions, see Table 3.

| Parameter | Symbol | Min | Мах | Unit | Note |  |

|-----------|--------|-----|-----|------|------|--|

|-----------|--------|-----|-----|------|------|--|

#### Note:

- 1. The min VIL and max VIH values are based on the min and max OVIN respective values found in Table 3.

- 2. The symbol OV<sub>IN</sub>, in this case, represents the OV<sub>IN</sub> symbol referenced in Table 3.

## 2.16.2 MPIC AC Timing Specifications

This table provides the MPIC input and output AC timing specifications.

### Table 53. MPIC Input AC Timing Specifications

For recommended operating conditions, see Table 3.

| Characteristic                   | Symbol             | Min | Мах | Unit    | Note |

|----------------------------------|--------------------|-----|-----|---------|------|

| MPIC inputs—minimum pulse width  | t <sub>PIWID</sub> | 3   | —   | SYSCLKs | 1    |

| Trust inputs—minimum pulse width | t <sub>TIWID</sub> | 3   | —   | SYSCLKs | 2    |

#### Note:

MPIC inputs and outputs are asynchronous to any visible clock. MPIC outputs must be synchronized before use by any

external synchronous logic. MPIC inputs are required to be valid for at least t<sub>PIWID</sub> ns to ensure proper operation when

working in edge triggered mode.

Trust inputs are asynchronous to any visible clock. Trust inputs are required to be valid for at least t<sub>TIWID</sub> ns to ensure proper operation when working in edge triggered mode. For low power trust input pin LP\_TMP\_DETECT, the voltage is V<sub>DD\_LP</sub> and see Table 3 for the voltage requirment.

## 2.17 JTAG Controller

This section describes the DC and AC electrical specifications for the IEEE 1149.1 (JTAG) interface.

## 2.17.1 JTAG DC Electrical Characteristics

This table provides the JTAG DC electrical characteristics.

### Table 54. JTAG DC Electrical Characteristics (OV<sub>DD</sub> = 3.3 V)

For recommended operating conditions, see Table 3.

| Parameter                                                       | Symbol          | Min | Мах | Unit | Note |

|-----------------------------------------------------------------|-----------------|-----|-----|------|------|

| Input high voltage                                              | V <sub>IH</sub> | 2   | —   | V    | 1    |

| Input low voltage                                               | V <sub>IL</sub> | —   | 0.8 | V    | 1    |

| Input current ( $OV_{IN} = 0 V \text{ or } OV_{IN} = OV_{DD}$ ) | I <sub>IN</sub> | —   | ±40 | μΑ   | 2    |

| Output high voltage ( $OV_{DD} = min, I_{OH} = -2 mA$ )         | V <sub>OH</sub> | 2.4 | —   | V    | —    |

| Output low voltage (OV <sub>DD</sub> = min, $I_{OL}$ = 2 mA)    | V <sub>OL</sub> | —   | 0.4 | V    | —    |

#### Note:

1. The min  $V_{IL}$  and max  $V_{IH}$  values are based on the respective min and max  $OV_{IN}$  values found in Table 3.

2. The symbol  $V_{\text{IN}}$  in this case, represents the  $\text{OV}_{\text{IN}}$  symbol found in Table 3.

# 2.19 GPIO

This section describes the DC and AC electrical characteristics for the GPIO interface.

## 2.19.1 GPIO DC Electrical Characteristics

This table provides the DC electrical characteristics for GPIO pins operating at  $CV_{DD}$ ,  $LV_{DD}$  or  $OV_{DD} = 3.3$  V.

### Table 58. GPIO DC Electrical Characteristics (CV<sub>DD</sub>, LV<sub>DD</sub> or OV<sub>DD</sub> = 3.3 V)

For recommended operating conditions, see Table 3.

| Parameter                                                                      | Symbol          | Min | Max | Unit | Note |

|--------------------------------------------------------------------------------|-----------------|-----|-----|------|------|

| Input high voltage                                                             | V <sub>IH</sub> | 2.0 | _   | V    | 1    |

| Input low voltage                                                              | V <sub>IL</sub> | _   | 0.8 | V    | 1    |

| Input current (OV <sub>IN</sub> = 0 V or OV <sub>IN</sub> = OV <sub>DD</sub> ) | I <sub>IN</sub> |     | ±40 | μA   | 2    |

| Output high voltage ( $OV_{DD} = min, I_{OH} = -2 mA$ )                        | V <sub>OH</sub> | 2.4 | _   | V    | _    |

| Output low voltage (OV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA)            | V <sub>OL</sub> | _   | 0.4 | V    | —    |

Note:

1. The min V<sub>IL</sub> and max V<sub>IH</sub> values are based on the min and max L/OV<sub>IN</sub> respective values found in Table 3.

2. The symbol V<sub>IN</sub>, in this case, represents the L/OV<sub>IN</sub> symbol referenced in Section 2.1.2, "Recommended Operating Conditions."

This table provides the DC electrical characteristics for GPIO pins operating at  $CV_{DD}$  or  $LV_{DD} = 2.5$  V.

### Table 59. GPIO DC Electrical Characteristics ( $CV_{DD}$ or $LV_{DD} = 2.5 V$ )

For recommended operating conditions, see Table 3.

| Parameter                                                              | Symbol          | Min | Мах | Unit | Note |

|------------------------------------------------------------------------|-----------------|-----|-----|------|------|

| Input high voltage                                                     | V <sub>IH</sub> | 1.7 | _   | V    | 1    |

| Input low voltage                                                      | V <sub>IL</sub> | _   | 0.7 | V    | 1    |

| Input current ( $V_{IN} = 0 V \text{ or } V_{IN} = LV_{DD}$ )          | I <sub>IN</sub> | _   | ±40 | μA   | 2    |

| Output high voltage<br>( $LV_{DD} = min, I_{OH} = -2 mA$ )             | V <sub>OH</sub> | 2.0 | —   | V    | _    |

| Output low voltage<br>(LV <sub>DD</sub> = min, I <sub>OH</sub> = 2 mA) | V <sub>OL</sub> |     | 0.4 | V    | _    |

Note:

1. The min  $V_{IL}$  and max  $V_{IH}$  values are based on the respective min and max  $LV_{IN}$  values found in Table 3.

2. The symbol V<sub>IN</sub>, in this case, represents the LV<sub>IN</sub> symbol referenced in Section 2.1.2, "Recommended Operating Conditions."

## 2.19.2 GPIO AC Timing Specifications

This table provides the GPIO input and output AC timing specifications.

#### Table 60. GPIO Input AC Timing Specifications

For recommended operating conditions, see Table 3.

| Parameter                       | Symbol             | Min | Unit | Note |

|---------------------------------|--------------------|-----|------|------|

| GPIO inputs—minimum pulse width | t <sub>PIWID</sub> | 20  | ns   | 1    |

#### Note:

GPIO inputs and outputs are asynchronous to any visible clock. GPIO outputs must be synchronized before use by any

external synchronous logic. GPIO inputs are required to be valid for at least t<sub>PIWID</sub> to ensure proper operation.

This figure provides the AC test load for the GPIO.

Figure 31. GPIO AC Test Load

## 2.20 High-Speed Serial Interfaces (HSSI)

The device features a serializer/deserializer (SerDes) interface to be used for high-speed serial interconnect applications. The SerDes interface can be used for PCI Express, Serial RapidIO, Aurora, and SGMII data transfers.

This section describes the common portion of SerDes DC electrical specifications: the DC requirement for SerDes reference clocks. The SerDes data lane's transmitter (Tx) and receiver (Rx) reference circuits are also shown.

## 2.20.1 Signal Terms Definition

The SerDes utilizes differential signaling to transfer data across the serial link. This section defines terms used in the description and specification of differential signals.

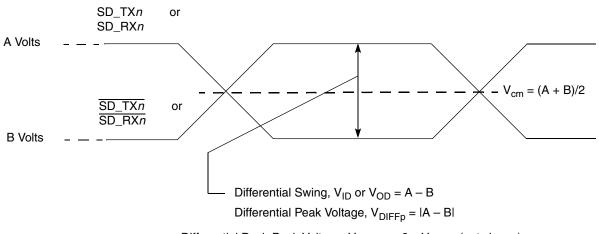

This figure shows how the signals are defined. For illustration purposes only, one SerDes lane is used in the description. This figure shows the waveform for either a transmitter output (SD\_TX*n* and  $\overline{SD_TXn}$ ) or a receiver input (SD\_RX*n* and  $\overline{SD_RXn}$ ). Each signal swings between A volts and B volts where A > B.

Differential Peak-Peak Voltage,  $V_{DIFFpp} = 2 \times V_{DIFFp}$  (not shown)

#### Figure 32. Differential Voltage Definitions for Transmitter or Receiver

Using this waveform, the definitions are as shown in the following list. To simplify the illustration, the definitions assume that the SerDes transmitter and receiver operate in a fully symmetrical differential signaling environment:

**Single-Ended Swing** The transmitter output signals and the receiver input signals  $SD_TXn$ ,  $\overline{SD_TXn}$ ,  $SD_RXn$  and  $\overline{SD_RXn}$  each have a peak-to-peak swing of A - B volts. This is also referred as each signal wire's single-ended swing.

#### Differential Output Voltage, V<sub>OD</sub> (or Differential Output Swing):

The differential output voltage (or swing) of the transmitter,  $V_{OD}$ , is defined as the difference of the two complimentary output voltages:  $V_{SD_TXn} - V_{\overline{SD_TXn}}$ . The  $V_{OD}$  value can be either positive or negative.

#### Differential Input Voltage, VID (or Differential Input Swing):

The differential input voltage (or swing) of the receiver,  $V_{ID}$ , is defined as the difference of the two complimentary input voltages:  $V_{SD_RXn} - V_{\overline{SD_RXn}}$ . The  $V_{ID}$  value can be either positive or negative.

### Differential Peak Voltage, V<sub>DIFFp</sub>

The peak value of the differential transmitter output signal or the differential receiver input signal is defined as the differential peak voltage,  $V_{DIFFp} = |A - B|$  volts.

### Differential Peak-to-Peak, $V_{DIFFp-p}$

Since the differential output signal of the transmitter and the differential input signal of the receiver each range from A – B to –(A – B) volts, the peak-to-peak value of the differential transmitter output signal or the differential receiver input signal is defined as differential peak-to-peak voltage,  $V_{DIFFp-p} = 2 \times V_{DIFFp} = 2 \times |(A - B)|$  volts, which is twice the differential swing in amplitude, or twice of the differential peak. For example, the output differential peak-peak voltage can also be calculated as  $V_{TX-DIFFp-p} = 2 \times |V_{OD}|$ .

#### **Differential Waveform**

The differential waveform is constructed by subtracting the inverting signal ( $\overline{SD_TXn}$ , for example) from the non-inverting signal ( $\overline{SD_TXn}$ , for example) within a differential pair. There is

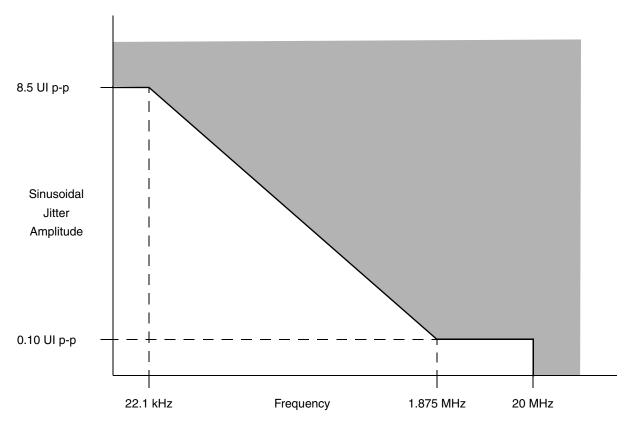

Figure 42. Single-Frequency Sinusoidal Jitter Limits

## 2.20.6 Aurora

This section describes the Aurora clocking requirements and AC and DC electrical characteristics.

## 2.20.6.1 Aurora DC Electrical Characteristics

This section describes the DC electrical characteristics for Aurora.

### 2.20.6.1.1 Aurora DC Clocking Requirements for SD\_REF\_CLK*n* and SD\_REF\_CLK*n*

Only SerDes bank 2(SD\_REF\_CLK2 and SD\_REF\_CLK2) may be used for SerDes Aurora configurations based on the RCW configuration field SRDS\_PRTCL. Aurora is not supported on SerDes banks 1.

For more information on these specifications, see Section 2.20.2, "SerDes Reference Clocks."

### 2.20.6.1.2 Aurora Transmitter DC Electrical Characteristics

This table provides the Aurora transmitter DC electrical characteristics (XVDD = 1.5 V or 1.8 V).

### Table 74. Aurora Transmitter DC Electrical Characteristics (XV<sub>DD</sub> = 1.5 V or 1.8 V)

For recommended operating conditions, see Table 3.

| Parameter                   | Symbol              | Min | Typical | Max  | Unit   |

|-----------------------------|---------------------|-----|---------|------|--------|

| Differential output voltage | V <sub>DIFFPP</sub> | 800 | —       | 1600 | mV p-p |

### Table 77. Aurora Receiver AC Timing Specifications (continued)

For recommended operating conditions, see Table 3.

| Parameter                  | Symbol | Min           | Typical | Мах           | Unit | Note |

|----------------------------|--------|---------------|---------|---------------|------|------|

| Unit Interval: 2.5 GBaud   | UI     | 400 – 100 ppm | 400     | 400 + 100 ppm | ps   | _    |

| Unit Interval: 3.125 GBaud | UI     | 320 – 100 ppm | 320     | 320 + 100 ppm | ps   | —    |

| Unit Interval: 5.0 GBaud   | UI     | 200 – 100 ppm | 200     | 200 + 100 ppm | ps   | —    |

#### Note:

1. Measured at receiver

2. Total jitter is composed of three components: deterministic jitter, random jitter, and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 42. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk and other variable system effects.

## 2.20.7 Serial ATA (SATA)

This section describes the DC and AC electrical specifications for the serial ATA (SATA) interface.

## 2.20.7.1 SATA DC Electrical Characteristics

This section describes the DC electrical characteristics for SATA.

### 2.20.7.1.1 SATA DC Transmitter Output Characteristics

This table provides the DC differential transmitter output DC characteristics for the SATA interface at Gen1i or 1.5 Gbits/s transmission.

### Table 78. Gen1i/1.5G Transmitter (Tx) DC Specifications (XV<sub>DD</sub> = 1.5 V or 1.8 V)

For recommended operating conditions, see Table 3.

| Parameter                      | Symbol                     | Min | Тур | Max | Unit   | Note |

|--------------------------------|----------------------------|-----|-----|-----|--------|------|

| Tx differential output voltage | V <sub>SATA_TXDIFF</sub>   | 400 |     | 600 | mV p-p | 1    |

| Tx differential pair impedance | Z <sub>SATA_TXDIFFIM</sub> | 85  | 100 | 115 | Ω      | 2    |

#### Note:

1. Terminated by 50  $\Omega$  load.

2. DC impedance

This table provides the differential transmitter output DC characteristics for the SATA interface at Gen2i or 3.0 Gbits/s transmission.

### Table 79. Gen 2i/3G Transmitter (Tx) DC Specifications (XV<sub>DD</sub> = 1.5 V or 1.8 V)

For recommended operating conditions, see Table 3.

| Parameter                      | Symbol                     | Min | Тур | Мах | Unit   | Note |

|--------------------------------|----------------------------|-----|-----|-----|--------|------|

| Tx diff output voltage         | V <sub>SATA_TXDIFF</sub>   | 400 | —   | 700 | mV p-p | 1    |

| Tx differential pair impedance | Z <sub>SATA_TXDIFFIM</sub> | 85  | 100 | 115 | Ω      | _    |

Note:

1. Terminated by 50  $\Omega$  load.

#### Table 82. SATA Reference Clock Input Requirements (continued)

For recommended operating conditions, see Table 3.

| Parameter                                                                    | Symbol              | Min | Тур | Max | Unit | Note    |

|------------------------------------------------------------------------------|---------------------|-----|-----|-----|------|---------|

| SD_REF_CLK/SD_REF_CLK cycle-to-cycle<br>clock jitter (period jitter)         | t <sub>CLK_CJ</sub> |     |     | 100 | ps   | 2       |

| SD_REF_CLK/SD_REF_CLK total reference clock jitter, phase jitter (peak-peak) | t <sub>CLK_PJ</sub> | -50 |     | +50 | ps   | 2, 3, 4 |

Note:

1. Caution: Only 100, 125 MHz have been tested. In-between values do not work correctly with the rest of the system.

2. At RefClk input

3. In a frequency band from 150 kHz to 15 MHz at BER of  $10^{-12}$

4. Total peak-to-peak deterministic jitter must be less than or equal to 50 ps.

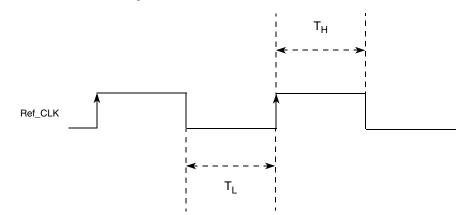

This figure shows the reference clock timing waveform.

Figure 43. Reference Clock Timing Waveform

## 2.20.7.3 AC Transmitter Output Characteristics

This table provides the differential transmitter output AC characteristics for the SATA interface at Gen1i or 1.5 Gbits/s transmission. The AC timing specifications do not include RefClk jitter.

### Table 83. Gen1i/1.5 G Transmitter (Tx) AC Specifications

For recommended operating conditions, see Table 3.

| Parameter                              | Symbol                      | Min      | Тур      | Мах      | Unit   | Note |

|----------------------------------------|-----------------------------|----------|----------|----------|--------|------|

| Channel speed                          | t <sub>CH_SPEED</sub>       |          | 1.5      |          | Gbps   |      |

| Unit Interval                          | T <sub>UI</sub>             | 666.4333 | 666.6667 | 670.2333 | ps     | _    |

| Total jitter data-data 5 UI            | U <sub>SATA_TXTJ5UI</sub>   | —        | —        | 0.355    | UI p-p | 1    |

| Total jitter, data-data 250 UI         | U <sub>SATA_TXTJ250UI</sub> | —        | —        | 0.47     | UI p-p | 1    |

| Deterministic jitter, data-data 5 UI   | U <sub>SATA_TXDJ5UI</sub>   | —        | _        | 0.175    | UI p-p | 1    |

| Deterministic jitter, data-data 250 UI | U <sub>SATA_TXDJ250UI</sub> | —        | —        | 0.22     | UI p-p | 1    |

This table provides the differential receiver input AC characteristics for the SATA interface at Gen2i or 3.0 Gbits/s transmission. The AC timing specifications do not include RefClk jitter.

Table 86. Gen 2i/3G Receiver (Rx) AC Specifications

For recommended operating conditions, see Table 3.

| Parameter                                             | Symbol                        | Min      | Typical  | Мах      | Unit   | Note |

|-------------------------------------------------------|-------------------------------|----------|----------|----------|--------|------|

| Unit Interval                                         | T <sub>UI</sub>               | 333.2167 | 333.3333 | 335.1167 | ps     |      |

| Total jitter $f_{C3dB} = f_{BAUD} \div 10$            | U <sub>SATA_TXTJfB/10</sub>   |          |          | 0.46     | UI p-p | 1    |

| Total jitter $f_{C3dB} = f_{BAUD} \div 500$           | U <sub>SATA_TXTJfB/500</sub>  |          |          | 0.60     | UI p-p | 1    |

| Total jitter $f_{C3dB} = f_{BAUD} \div 1667$          | U <sub>SATA_TXTJfB/1667</sub> | —        |          | 0.65     | UI p-p | 1    |

| Deterministic jitter, $f_{C3dB} = f_{BAUD} \div 10$   | U <sub>SATA_TXDJfB/10</sub>   | —        | —        | 0.35     | UI p-p | 1    |

| Deterministic jitter, $f_{C3dB} = f_{BAUD} \div 500$  | U <sub>SATA_TXDJfB/500</sub>  | —        | —        | 0.42     | UI p-p | 1    |

| Deterministic jitter, $f_{C3dB} = f_{BAUD} \div 1667$ | U <sub>SATA_TXDJfB/1667</sub> |          | —        | 0.35     | UI p-p | 1    |

Note:

1. Measured at receiver.

## 2.20.8 SGMII Interface

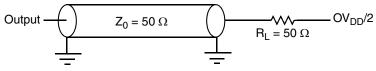

Each SGMII port features a 4-wire AC-coupled serial link from the SerDes interface of the device, as shown in Figure 44, where  $C_{TX}$  is the external (on board) AC-coupled capacitor. Each output pin of the SerDes transmitter differential pair features 50- $\Omega$  output impedance. Each input of the SerDes receiver differential pair features 50- $\Omega$  on-die termination to XGND. The reference circuit of the SerDes transmitter and receiver is shown in Figure 39.

## 2.20.8.0.1 SGMII Clocking Requirements for SD\_REF\_CLK*n* and SD\_REF\_CLK*n*

When operating in SGMII mode, the EC\_GTX\_CLK125 clock is not required for this port. Instead, a SerDes reference clock is required on SD\_REF\_CLK[1:2] and SD\_REF\_CLK[1:2] pins. SerDes banks 1–2 may be used for SerDes SGMII configurations based on the RCW Configuration field SRDS\_PRTCL.

For more information on these specifications, see Section 2.20.2, "SerDes Reference Clocks."

## 2.20.8.1 SGMII DC Electrical Characteristics

This section discusses the electrical characteristics for the SGMII interface.

### 2.20.8.1.1 SGMII Transmit DC Timing Specifications

This table describe the SGMII SerDes transmitter and receiver AC-coupled DC electrical characteristics for 1.25 GBaud. Transmitter DC characteristics are measured at the transmitter outputs ( $SD_TXn$  and  $\overline{SD_TXn}$ ) as shown in Figure 45.

### Table 87. SGMII DC Transmitter Electrical Characteristics (XV<sub>DD</sub> = 1.5 V or 1.8 V)

For recommended operating conditions, see Table 3.

| Parameter           | Symbol          | Min                | Тур | Мах                                      | Unit | Note |

|---------------------|-----------------|--------------------|-----|------------------------------------------|------|------|

| Output high voltage | V <sub>OH</sub> | _                  | _   | 1.5 x IV <sub>OD</sub> I <sub>-max</sub> | mV   | 1    |

| Output low voltage  | V <sub>OL</sub> | $ V_{OD} _{min}/2$ | _   | —                                        | mV   | 1    |

#### Hardware Design Considerations

$ECn_GTX_CLK125$  is a 125-MHz input clock on the dTSEC ports. If the dTSEC ports are not used for RGMII, the  $ECn_GTX_CLK125$  input can be tied off to GND.

If RCW field I2C = 0b0100 or 0b0101 (RCW bits 354–357), the SDHC\_WP and  $\overline{SDHC_CD}$  input signals are enabled for external use. If SDHC\_WP and  $\overline{SDHC_CD}$  are selected and not used, they must be externally pulled low such that SDHC\_WP = 0 (write enabled) and  $\overline{SDHC_CD} = 0$  (card detected). If RCW field I2C  $\neq$  0b0100 or 0b0101, thereby selecting either I2C3 or GPIO functionality, SDHC\_WP and  $\overline{SDHC_CD}$  are internally driven such that SDHC\_WP = write enabled and  $\overline{SDHC_CD} = card detected$  and the selected I2C3 or GPIO external pin functionality may be used.

TMP\_DETECT pin and LP\_TMP DETECT pin are active low input to the Security Monitor (refer to the "Secure Boot and Trust Architecture" chapter of the chip reference manual). If a tamper sensor is used, it must maintain the signal at the specified voltage until a tamper is detected. A 1K pulldown resistor strongly recommended. If Trust is used without tamper sensors, tie high.VDD\_LP must be connected even if Low Power features aren't used. Otherwise, the LP\_Section will generate internal errors that will prevent the high power trust section from reaching Trusted/Secure state.

## 3.6.1 Legacy JTAG Configuration Signals

Correct operation of the JTAG interface requires configuration of a group of system control pins as demonstrated in Figure 55. Care must be taken to ensure that these pins are maintained at a valid negated state under normal operating conditions as most have asynchronous behavior and spurious assertion will give unpredictable results.

Boundary-scan testing is enabled through the JTAG interface signals. The TRST signal is optional in the IEEE Std 1149.1 specification, but it is provided on all processors built on Power Architecture technology. The device requires TRST to be asserted during power-on reset flow to ensure that the JTAG boundary logic does not interfere with normal chip operation. While the TAP controller can be forced to the reset state using only the TCK and TMS signals, generally systems assert TRST during the power-on reset flow. Simply tying TRST to PORESET is not practical because the JTAG interface is also used for accessing the common on-chip processor (COP), which implements the debug interface to the chip.

The COP function of these processors allow a remote computer system (typically, a PC with dedicated hardware and debugging software) to access and control the internal operations of the processor. The COP interface connects primarily through the JTAG port of the processor, with some additional status monitoring signals. The COP port requires the ability to independently assert PORESET or TRST in order to fully control the processor. If the target system has independent reset sources, such as voltage monitors, watchdog timers, power supply failures, or push-button switches, then the COP reset signals must be merged into these signals with logic.

The arrangement shown in Figure 55 allows the COP port to independently assert **PORESET** or **TRST**, while ensuring that the target can drive **PORESET** as well.

The COP interface has a standard header, shown in Figure 54, for connection to the target system, and is based on the 0.025" square-post, 0.100" centered header assembly (often called a Berg header). The connector typically has pin 14 removed as a connector key.

The COP header adds many benefits such as breakpoints, watchpoints, register and memory examination/modification, and other standard debugger features. An inexpensive option can be to leave the COP header unpopulated until needed.

There is no standardized way to number the COP header; so emulator vendors have issued many different pin numbering schemes. Some COP headers are numbered top-to-bottom then left-to-right, while others use left-to-right then top-to-bottom. Still others number the pins counter-clockwise from pin 1 (as with an IC). Regardless of the numbering scheme, the signal placement recommended in Figure 54 is common to all known emulators.

## 3.6.1.1 Termination of Unused Signals

If the JTAG interface and COP header is not used, Freescale recommends the following connections:

TRST must be tied to PORESET through a 0 kΩ isolation resistor so that it is asserted when the system reset signal (PORESET) is asserted, ensuring that the JTAG scan chain is initialized during the power-on reset flow. Freescale recommends that the COP header be designed into the system as shown in Figure 55. If this is not possible, the

**Revision History**

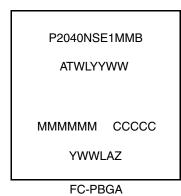

## 6.2.1 Part Marking

Parts are marked as in the example shown in this figure.

#### Notes:

P2040NSE1MMB is the orderable part number. See Table 107 for details.

ATWLYYWW is the test traceability code.

MMMMMM is the mask number.

CCCCC is the country code.

YWWLAZ is the assembly traceability code.

### Figure 64. Part Marking for FC-PBGA Device

# 7 Revision History

This table provides a revision history for this document.

### Table 108. Revision History

| Rev.<br>Number | Date    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2              | 02/2013 | <ul> <li>In Table 7, "P2040 I/O Power Supply Estimated Values," updated the USB power supply with USB_Vdd_3P3 and updated the typical value with "0.003" in the Others (Reset, System Clock, JTAG &amp; Misc.) row.</li> <li>In Table 8, "Device AVDD Power Dissipation," removed V<sub>DD_LP</sub> from table.</li> <li>Added Table 10, "VDD_LP Power Dissipation."</li> <li>In Table 53, "MPIC Input AC Timing Specifications," added Trust inputs AC timing and footnote 2.</li> <li>In Table 93, "Processor Clocking Specifications," updated footnote 8 with Rev 1.1 silicon.</li> <li>In Table 107, "Part Numbering Nomenclature," added "C" in the Die Revision collumn.</li> <li>In Section 6.2, "Orderable Part Numbers Addressed by this Document," added the device part numbers for Rev 2.0 silicon.</li> </ul> |

| Rev.<br>Number | Date    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | 09/2012 | <ul> <li>In Table 1, "Pin List by Bus", added note for pin V<sub>DD_LP</sub></li> <li>Updated Table 8, "Device AVDD Power Dissipation".</li> <li>In Table 12, "SYSCLK DC Electrical Characteristics (OV<sub>DD</sub> = 3.3 V)", updated the input current max value and added input capacitance max value.</li> <li>In Table 51, "eSDHC AC Timing Specifications", updated input setup times from 5 ns to 2.5 ns.</li> <li>In Section 3.1.6.2, "Minimum Platform Frequency Requirements for High-Speed Interfaces", updated the note that the "PCI Express link width" refers to "a single port".</li> <li>In Section 4.1, "Package Parameters for the FC-PBGA", updated the solder ball composition and module height.</li> <li>In Section 4.2, "Mechanical Dimensions of the FC-PBGA", updated the figure for the mechanical dimensions.</li> <li>In Section 3.6, "Connection Recommendations", removed the sentence "If no aspect of Trust Architecture is to be used, all Trust Architecture pins can be tied to GND."</li> </ul> |

| 0              | 06/2012 | Initial public release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Freescale, the Freescale logo, and QorlQ are trademarks of Freescale Semiconductor, Inc. Reg., U.S. Pat. & Tm. Off. CoreNet is a trademark of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © 2010–2013 Freescale Semiconductor, Inc.

Document Number: P2040EC Rev. 2 02/2013