Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

## **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                           |

|---------------------------------|-----------------------------------------------------------|

| Product Status                  | Active                                                    |

| Core Processor                  | PowerPC e500mc                                            |

| Number of Cores/Bus Width       | 4 Core, 32-Bit                                            |

| Speed                           | 1.5GHz                                                    |

| Co-Processors/DSP               | -                                                         |

| RAM Controllers                 | DDR3, DDR3L                                               |

| Graphics Acceleration           | No                                                        |

| Display & Interface Controllers | -                                                         |

| Ethernet                        | 10/100/1000Mbps (5), 10Gbps (1)                           |

| SATA                            | SATA 3Gbps (2)                                            |

| USB                             | USB 2.0 + PHY (2)                                         |

| Voltage - I/O                   | 1.0V, 1.35V, 1.5V, 1.8V, 2.5V, 3.3V                       |

| Operating Temperature           | 0°C ~ 105°C (TA)                                          |

| Security Features               | -                                                         |

| Package / Case                  | 780-BBGA, FCBGA                                           |

| Supplier Device Package         | 780-FCPBGA (23x23)                                        |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=p2041nsn1pnb |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 1. Pin List by Bus (continued)

| Signal | Signal Description | Package<br>Pin Number | Pin<br>Type | Power<br>Supply  | Note |

|--------|--------------------|-----------------------|-------------|------------------|------|

| MDQ29  | Data               | AC4                   | I/O         | GV <sub>DD</sub> | _    |

| MDQ30  | Data               | AE1                   | I/O         | $GV_DD$          | _    |

| MDQ31  | Data               | AE3                   | I/O         | $GV_DD$          | _    |

| MDQ32  | Data               | AE16                  | I/O         | $GV_DD$          | _    |

| MDQ33  | Data               | AD16                  | I/O         | $GV_DD$          | _    |

| MDQ34  | Data               | AE19                  | I/O         | $GV_DD$          | _    |

| MDQ35  | Data               | AD19                  | I/O         | $GV_DD$          | _    |

| MDQ36  | Data               | AF15                  | I/O         | $GV_DD$          | _    |

| MDQ37  | Data               | AF16                  | I/O         | $GV_DD$          | _    |

| MDQ38  | Data               | AF18                  | I/O         | $GV_DD$          | _    |

| MDQ39  | Data               | AF19                  | I/O         | $GV_DD$          | _    |

| MDQ40  | Data               | AH23                  | I/O         | $GV_DD$          | _    |

| MDQ41  | Data               | AG23                  | I/O         | $GV_DD$          | _    |

| MDQ42  | Data               | AH27                  | I/O         | $GV_DD$          | _    |

| MDQ43  | Data               | AG27                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ44  | Data               | AG21                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ45  | Data               | AH22                  | I/O         | $GV_DD$          | _    |

| MDQ46  | Data               | AH26                  | I/O         | $GV_DD$          | _    |

| MDQ47  | Data               | AG26                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ48  | Data               | AF21                  | I/O         | $GV_DD$          | _    |

| MDQ49  | Data               | AD21                  | I/O         | $GV_DD$          | _    |

| MDQ50  | Data               | AF24                  | I/O         | $GV_DD$          | _    |

| MDQ51  | Data               | AD24                  | I/O         | $GV_DD$          | _    |

| MDQ52  | Data               | AE20                  | I/O         | $GV_DD$          | _    |

| MDQ53  | Data               | AD20                  | I/O         | $GV_DD$          | _    |

| MDQ54  | Data               | AD23                  | I/O         | $GV_DD$          | _    |

| MDQ55  | Data               | AE25                  | I/O         | $GV_DD$          | _    |

| MDQ56  | Data               | AF26                  | I/O         | $GV_DD$          | _    |

| MDQ57  | Data               | AF27                  | I/O         | $GV_DD$          | _    |

| MDQ58  | Data               | AD25                  | I/O         | $GV_DD$          | _    |

| MDQ59  | Data               | AD26                  | I/O         | $GV_DD$          | _    |

| MDQ60  | Data               | AG28                  | I/O         | $GV_DD$          | _    |

| MDQ61  | Data               | AF25                  | I/O         | $GV_DD$          | _    |

| MDQ62  | Data               | AD27                  | I/O         | $GV_DD$          | _    |

P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2

Table 1. Pin List by Bus (continued)

| Signal | Signal Description             | Package<br>Pin Number | Pin<br>Type | Power<br>Supply  | Note |

|--------|--------------------------------|-----------------------|-------------|------------------|------|

| MCK0   | Clock                          | AD14                  | 0           | $GV_DD$          | _    |

| MCK1   | Clock                          | AE13                  | 0           | GV <sub>DD</sub> | _    |

| MCK2   | Clock                          | AG13                  | 0           | $GV_DD$          | _    |

| мск3   | Clock                          | AG14                  | 0           | $GV_DD$          | _    |

| MCK0   | Clock Complements              | AE14                  | 0           | $GV_DD$          | _    |

| MCK1   | Clock Complements              | AD13                  | 0           | $GV_DD$          | _    |

| MCK2   | Clock Complements              | AH13                  | 0           | GV <sub>DD</sub> | _    |

| MCK3   | Clock Complements              | AH14                  | 0           | GV <sub>DD</sub> | _    |

| MODT0  | On Die Termination             | AC19                  | 0           | GV <sub>DD</sub> | _    |

| MODT1  | On Die Termination             | AD22                  | 0           | GV <sub>DD</sub> | _    |

| MODT2  | On Die Termination             | AG18                  | 0           | GV <sub>DD</sub> | _    |

| MODT3  | On Die Termination             | AH21                  | 0           | $GV_DD$          | _    |

| MDIC0  | Driver Impedance Calibration   | AG12                  | I/O         | $GV_DD$          | 16   |

| MDIC1  | Driver Impedance Calibration   | AE12                  | I/O         | $GV_DD$          | 16   |

|        | Local Bus Controller Interface | <u> </u>              |             |                  |      |

| LAD00  | Muxed Data/Address             | J6                    | I/O         | BV <sub>DD</sub> | 3    |

| LAD01  | Muxed Data/Address             | J4                    | I/O         | BV <sub>DD</sub> | 3    |

| LAD02  | Muxed Data/Address             | K2                    | I/O         | $BV_DD$          | 3    |

| LAD03  | Muxed Data/Address             | K4                    | I/O         | BV <sub>DD</sub> | 3    |

| LAD04  | Muxed Data/Address             | L1                    | I/O         | BV <sub>DD</sub> | 3    |

| LAD05  | Muxed Data/Address             | J5                    | I/O         | $BV_DD$          | 3    |

| LAD06  | Muxed Data/Address             | N5                    | I/O         | BV <sub>DD</sub> | 3    |

| LAD07  | Muxed Data/Address             | N2                    | I/O         | BV <sub>DD</sub> | 3    |

| LAD08  | Muxed Data/Address             | N3                    | I/O         | BV <sub>DD</sub> | 3    |

| LAD09  | Muxed Data/Address             | N1                    | I/O         | BV <sub>DD</sub> | 3    |

| LAD10  | Muxed Data/Address             | P4                    | I/O         | BV <sub>DD</sub> | 3    |

| LAD11  | Muxed Data/Address             | R7                    | I/O         | BV <sub>DD</sub> | 3    |

| LAD12  | Muxed Data/Address             | T4                    | I/O         | BV <sub>DD</sub> | 3    |

| LAD13  | Muxed Data/Address             | U2                    | I/O         | BV <sub>DD</sub> | 3    |

| LAD14  | Muxed Data/Address             | Т6                    | I/O         | BV <sub>DD</sub> | 3    |

| LAD15  | Muxed Data/Address             | T7                    | I/O         | BV <sub>DD</sub> | 3    |

| LA16   | Address                        | K6                    | I/O         | BV <sub>DD</sub> | 31   |

| LA17   | Address                        | К3                    | I/O         | BV <sub>DD</sub> | 31   |

| LA18   | Address                        | P6                    | I/O         | BV <sub>DD</sub> | 31   |

P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2

Table 1. Pin List by Bus (continued)

| Signal                                                |                                                 |      | Pin<br>Type | Power<br>Supply  | Note |

|-------------------------------------------------------|-------------------------------------------------|------|-------------|------------------|------|

| SD_RX04                                               | Receive Data (positive)                         | A2   | I           | $XV_{DD}$        | _    |

| SD_RX03                                               | Receive Data (positive)                         | E1   | I           | $XV_{DD}$        | _    |

| SD_RX02                                               | Receive Data (positive)                         | G1   | I           | $XV_{DD}$        | _    |

| SD_RX13                                               | Receive Data (negative)                         | A21  | I           | $XV_{DD}$        | _    |

| SD_RX12                                               | Receive Data (negative)                         | A19  | I           | $XV_{DD}$        | _    |

| SD_RX11                                               | Receive Data (negative)                         | A15  | I           | $XV_{DD}$        | _    |

| SD_RX10                                               | Receive Data (negative)                         | B13  | I           | $XV_{DD}$        | _    |

| SD_RX07                                               | Receive Data (negative)                         | A11  | I           | $XV_{DD}$        | _    |

| SD_RX06                                               | Receive Data (negative)                         | A9   | I           | $XV_{DD}$        | _    |

| SD_RX05                                               | Receive Data (negative)                         | A7   | I           | $XV_{DD}$        | _    |

| SD_RX04                                               | Receive Data (negative)                         | A3   | I           | $XV_{DD}$        | _    |

| SD_RX03                                               | Receive Data (negative)                         | E2   | I           | $XV_{DD}$        | _    |

| SD_RX02                                               | Receive Data (negative)                         | G2   | I           | $XV_{DD}$        | _    |

| SD_REF_CLK1                                           | SerDes Bank 1 PLL Reference Clock               | D3   | I           | $XV_{DD}$        | _    |

| SD_REF_CLK1                                           | SerDes Bank 1 PLL Reference Clock<br>Complement | D4   | I           | $XV_{DD}$        | _    |

| SD_REF_CLK2                                           | SerDes Bank 2 PLL Reference Clock               | E17  | I           | $XV_{DD}$        | _    |

| SD_REF_CLK2                                           | SerDes Bank 2 PLL Reference Clock<br>Complement | F17  | I           | $XV_{DD}$        | _    |

|                                                       | General-Purpose Input/Output                    |      |             |                  |      |

| GPIO00/SPI_CS0/SDHC_DATA4                             | General Purpose Input/Output                    | H26  | I/O         | CV <sub>DD</sub> | _    |

| GPIO01/SPI_CS1/SDHC_DATA5                             | General Purpose Input/Output                    | H23  | I/O         | CV <sub>DD</sub> | _    |

| GPIO02/SPI_CS2/SDHC_DATA6                             | General Purpose Input/Output                    | H27  | I/O         | CV <sub>DD</sub> | _    |

| GPIO03SPI_CS3/SDHC_DATA7                              | General Purpose Input/Output                    | H24  | I/O         | CV <sub>DD</sub> | _    |

| GPIO08/UART1_SOUT                                     | General Purpose Input/Output                    | R23  | I/O         | OV <sub>DD</sub> | _    |

| GPIO09/UART2_SOUT                                     | General Purpose Input/Output                    | P26  | I/O         | $OV_{DD}$        | _    |

| GPIO10/UART1_SIN                                      | General Purpose Input/Output                    | R26  | I/O         | $OV_DD$          | _    |

| GPIO11/UART2_SIN                                      | General Purpose Input/Output                    | P27  | I/O         | OV <sub>DD</sub> | _    |

| GPIO12/UART1_RTS/UART3_SOUT                           | General Purpose Input/Output                    | P24  | I/O         | OV <sub>DD</sub> | _    |

| GPIO13/UART2_RTS/UART4_SOUT                           | General Purpose Input/Output                    | P25  | I/O         | OV <sub>DD</sub> | _    |

| GPIO14/UART1_CTS/UART3_SIN                            | General Purpose Input/Output                    | R25  | I/O         | OV <sub>DD</sub> | _    |

| GPIO15/UART2_CTS/UART4_SIN                            | General Purpose Input/Output                    | P23  | I/O         | OV <sub>DD</sub> | _    |

| GPIO16/IIC3_SCL/M1DVAL/LB_DVAL/<br>DMA1_DACK0/SDHC_CD | General Purpose Input/Output                    | AB23 | I/O         | $OV_{DD}$        | _    |

Table 1. Pin List by Bus (continued)

| Signal | Signal Description | Package<br>Pin Number | Pin<br>Type | Power<br>Supply | Note |

|--------|--------------------|-----------------------|-------------|-----------------|------|

| GND166 | Ground             | B25                   | _           | _               | _    |

| GND165 | Ground             | C23                   | _           | _               | _    |

| GND164 | Ground             | D23                   | _           | _               | _    |

| GND163 | Ground             | D27                   | _           | _               | _    |

| GND162 | Ground             | E24                   | _           | _               | _    |

| GND161 | Ground             | F22                   | _           | _               | _    |

| GND160 | Ground             | F27                   | _           | _               | _    |

| GND159 | Ground             | G10                   | _           | _               | _    |

| GND158 | Ground             | G12                   | _           | _               |      |

| GND157 | Ground             | G14                   | _           | _               | _    |

| GND156 | Ground             | G16                   | _           | _               |      |

| GND155 | Ground             | G18                   | _           | _               |      |

| GND154 | Ground             | G21                   | _           | _               |      |

| GND153 | Ground             | G22                   | _           | _               | _    |

| GND152 | Ground             | НЗ                    | _           | _               | _    |

| GND151 | Ground             | H4                    | _           | _               | _    |

| GND150 | Ground             | H10                   | _           | _               | _    |

| GND149 | Ground             | H12                   | _           | _               |      |

| GND148 | Ground             | H14                   | _           | _               | _    |

| GND147 | Ground             | H16                   | _           | _               | _    |

| GND146 | Ground             | H18                   | _           | _               | _    |

| GND145 | Ground             | H21                   | _           | _               | _    |

| GND144 | Ground             | H25                   | _           | _               |      |

| GND143 | Ground             | J2                    | _           | _               | _    |

| GND142 | Ground             | J8                    | _           | _               | _    |

| GND141 | Ground             | J10                   | _           | _               | _    |

| GND140 | Ground             | J12                   | _           | _               | _    |

| GND139 | Ground             | J14                   | _           | _               | _    |

| GND138 | Ground             | J16                   | _           | _               | _    |

| GND137 | Ground             | J18                   | _           | _               | _    |

| GND136 | Ground             | J21                   | _           | _               | _    |

| GND135 | Ground             | K5                    | _           | _               | _    |

| GND134 | Ground             | K8                    | _           | _               | _    |

| GND133 | Ground             | K10                   | _           | _               | _    |

Table 1. Pin List by Bus (continued)

| Signal | Signal Description     | Package<br>Pin Number | Pin<br>Type | Power<br>Supply | Note |

|--------|------------------------|-----------------------|-------------|-----------------|------|

| GND030 | Ground                 | AB10                  | _           | _               | _    |

| GND029 | Ground                 | AB11                  | _           | _               | _    |

| GND028 | Ground                 | AB12                  | _           | _               | _    |

| GND027 | Ground                 | AB15                  | _           | _               | _    |

| GND026 | Ground                 | AB22                  | _           | _               | _    |

| GND025 | Ground                 | AC5                   | _           | _               | _    |

| GND024 | Ground                 | AC17                  | _           | _               | _    |

| GND023 | Ground                 | AC20                  | _           | _               | _    |

| GND022 | Ground                 | AC26                  | _           | _               | _    |

| GND021 | Ground                 | AD12                  | _           | _               | _    |

| GND020 | Ground                 | AD15                  | _           | _               | _    |

| GND019 | Ground                 | AE2                   | _           | _               | _    |

| GND018 | Ground                 | AE5                   | _           | _               | _    |

| GND017 | Ground                 | AE8                   | _           | _               | _    |

| GND016 | Ground                 | AE11                  | _           | _               | _    |

| GND015 | Ground                 | AE15                  | _           | _               | _    |

| GND014 | Ground                 | AE18                  | _           | _               | _    |

| GND013 | Ground                 | AE21                  | _           | _               | _    |

| GND012 | Ground                 | AE24                  | _           | _               | _    |

| GND011 | Ground                 | AE27                  | _           | _               | _    |

| GND010 | Ground                 | AF13                  | _           | _               | _    |

| GND009 | Ground                 | AF14                  | _           | _               | _    |

| GND008 | Ground                 | AG4                   | _           | _               | _    |

| GND007 | Ground                 | AG7                   | _           | _               | _    |

| GND006 | Ground                 | AG10                  | _           | _               | _    |

| GND005 | Ground                 | AG19                  | _           | _               | _    |

| GND004 | Ground                 | AG22                  | _           | _               | _    |

| GND003 | Ground                 | AG25                  | _           | _               | _    |

| GND002 | Ground                 | AH12                  | _           | _               | _    |

| GND001 | Ground                 | AH15                  | _           | _               | _    |

| XGND12 | SerDes Transceiver GND | C5                    | _           | _               | _    |

| XGND11 | SerDes Transceiver GND | C7                    | _           | _               | _    |

| XGND10 | SerDes Transceiver GND | C11                   | _           | _               | _    |

| XGND09 | SerDes Transceiver GND | C15                   | _           | _               | _    |

Table 1. Pin List by Bus (continued)

| Signal      | Signal Description       | Package<br>Pin Number | Pin<br>Type | Power<br>Supply  | Note     |

|-------------|--------------------------|-----------------------|-------------|------------------|----------|

| USB1_AGND01 | USB1 PHY Transceiver GND | M28                   | _           | _                | <u> </u> |

| USB2_AGND06 | USB2 PHY Transceiver GND | J22                   | _           | _                | _        |

| USB2_AGND05 | USB2 PHY Transceiver GND | J24                   | _           | _                | _        |

| USB2_AGND04 | USB2 PHY Transceiver GND | J26                   | _           | _                | _        |

| USB2_AGND03 | USB2 PHY Transceiver GND | K25                   | _           | _                | _        |

| USB2_AGND02 | USB2 PHY Transceiver GND | L25                   | _           | _                | _        |

| USB2_AGND01 | USB2 PHY Transceiver GND | M26                   | _           | _                | _        |

| OVDD06      | General I/O Supply       | N20                   | _           | $OV_{DD}$        | _        |

| OVDD05      | General I/O Supply       | P20                   | _           | OV <sub>DD</sub> | <u> </u> |

| OVDD04      | General I/O Supply       | R20                   | _           | OV <sub>DD</sub> | _        |

| OVDD03      | General I/O Supply       | T20                   | _           | OV <sub>DD</sub> | _        |

| OVDD02      | General I/O Supply       | T26                   | _           | OV <sub>DD</sub> | <u> </u> |

| OVDD01      | General I/O Supply       | W26                   | _           | OV <sub>DD</sub> | T —      |

| CVDD2       | eSPI and eSDHC Supply    | K20                   | _           | CV <sub>DD</sub> | _        |

| CVDD1       | eSPI and eSDHC Supply    | M20                   | _           | CV <sub>DD</sub> | T —      |

| GVDD17      | DDR Supply               | AA8                   | _           | GV <sub>DD</sub> | _        |

| GVDD16      | DDR Supply               | AA9                   | _           | GV <sub>DD</sub> | _        |

| GVDD15      | DDR Supply               | AA10                  | _           | GV <sub>DD</sub> | <u> </u> |

| GVDD14      | DDR Supply               | AA11                  | _           | GV <sub>DD</sub> | T —      |

| GVDD13      | DDR Supply               | AA12                  | _           | $GV_DD$          | _        |

| GVDD12      | DDR Supply               | AA13                  | _           | GV <sub>DD</sub> | T —      |

| GVDD11      | DDR Supply               | AA14                  | _           | $GV_DD$          | _        |

| GVDD10      | DDR Supply               | AA15                  | _           | $GV_DD$          | _        |

| GVDD09      | DDR Supply               | AB13                  | _           | $GV_DD$          | _        |

| GVDD08      | DDR Supply               | AB14                  | _           | $GV_DD$          | _        |

| GVDD07      | DDR Supply               | AC13                  | _           | GV <sub>DD</sub> | _        |

| GVDD06      | DDR Supply               | AC14                  | _           | $GV_DD$          | _        |

| GVDD05      | DDR Supply               | AF6                   | _           | $GV_DD$          | _        |

| GVDD04      | DDR Supply               | AF9                   | _           | GV <sub>DD</sub> | _        |

| GVDD03      | DDR Supply               | AF17                  | _           | $GV_DD$          | _        |

| GVDD02      | DDR Supply               | AF20                  | _           | $GV_DD$          | T —      |

| GVDD01      | DDR Supply               | AF23                  | _           | $GV_DD$          | _        |

| BVDD07      | Local Bus Supply         | J7                    | _           | $BV_DD$          | T —      |

| BVDD06      | Local Bus Supply         | K7                    | _           | BV <sub>DD</sub> | T —      |

P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2

Table 1. Pin List by Bus (continued)

| Signal             | Signal Description                            | Package<br>Pin Number        | Pin<br>Type | Power<br>Supply                      | Note |

|--------------------|-----------------------------------------------|------------------------------|-------------|--------------------------------------|------|

| SENSEVDD_CA_PL     | Core Group A and Platform Vdd Sense           | H8                           | _           | _                                    | 8    |

| SENSEVDD_CB        | Core Group B Vdd Sense                        | AB16                         | _           | _                                    | 8    |

| USB1_VDD_3P3       | USB1 PHY Transceiver 3.3 V Supply             | M23                          | _           | _                                    | _    |

| USB2_VDD_3P3       | USB2 PHY Transceiver 3.3 V Supply             | J23                          | _           | _                                    | _    |

| USB1_VDD_1P0       | USB1 PHY PLL 1.0 V Supply                     | L22                          | _           | _                                    | _    |

| USB2_VDD_1P0       | USB2 PHY PLL 1.0 V Supply                     | K22                          | _           | _                                    | _    |

|                    | Analog Signals                                |                              |             |                                      |      |

| MVREF              | SSTL_1.5/1.35 Reference Voltage               | W7                           | I           | GV <sub>DD</sub> /2                  | _    |

| SD_IMP_CAL_TX      | SerDes Tx Impedance Calibration               | E21                          | I           | 200Ω<br>(±1%) to<br>XV <sub>DD</sub> | 21   |

| SD_IMP_CAL_RX      | SerDes Rx Impedance Calibration               | F7                           | I           | $200\Omega$ (±1%) to $SV_{DD}$       | 22   |

| TEMP_ANODE         | Temperature Diode Anode                       | V5                           | _           | internal<br>diode                    | 9    |

| TEMP_CATHODE       | Temperature Diode Cathode                     | Temperature Diode Cathode U6 |             | internal<br>diode                    | 9    |

| USB2_IBIAS_REXT    | USB PHY2 Reference Bias Current<br>Generation | K23                          | _           | GND                                  | 32   |

| USB1_IBIAS_REXT    | USB PHY1 Reference Bias Current<br>Generation | L23                          | _           | GND                                  | 32   |

| USB2_VDD_1P8_DECAP | USB2 PHY 1.8 V Output to External Decap       | K24                          | _           | GND                                  | 33   |

| USB1_VDD_1P8_DECAP | USB1 PHY 1.8 V Output to External Decap       | L24                          | _           | GND                                  | 33   |

|                    | No Connection Pins                            |                              |             |                                      |      |

| NC03               | No Connection                                 | W4                           | _           | _                                    | 11   |

| NC04               | No Connection                                 | W3                           | _           | _                                    | 11   |

| NC05               | No Connection                                 | W1                           | _           | _                                    | 11   |

| NC06               | No Connection                                 | H7                           | _           | _                                    | 11   |

| NC07               | No Connection                                 | G7                           | _           | _                                    | 11   |

| NC08               | No Connection                                 | F20                          | _           | _                                    | 11   |

| NC09               | No Connection                                 | F19                          | _           | _                                    | 11   |

| NC10               | No Connection F18                             |                              | _           | _                                    | 11   |

| NC11               | No Connection                                 | F16                          | _           | _                                    | 11   |

| NC12               | No Connection                                 | F13                          | _           | _                                    | 11   |

P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2

While VDD is ramping, current may be supplied from VDD through the chip to GVDD. Nevertheless, GVDD from an external supply should follow the sequencing described above.

#### WARNING

Only 100,000 POR cycles are permitted per lifetime of a device.

All supplies must be at their stable values within 75 ms.

Items on the same line have no ordering requirement with respect to one another. Items on separate lines must be ordered sequentially such that voltage rails on a previous step must reach 90% of their value before the voltage rails on the current step reach 10% of theirs.

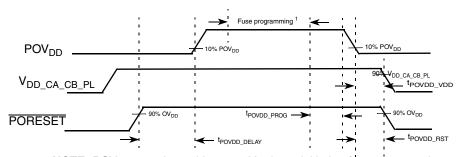

This figure provides the  $POV_{DD}$  timing diagram.

**NOTE:** POV<sub>DD</sub> must be stable at 1.5 V prior to initiating fuse programming.

Figure 8. POV<sub>DD</sub> Timing Diagram

This table provides information on the power-down and power-up sequence parameters for POV<sub>DD</sub>.

| Driver Type  | Min | Max | Unit    | Note |

|--------------|-----|-----|---------|------|

| tpovdd_delay | 100 | _   | SYSCLKs | 1    |

| tpovdd_prog  | 0   | _   | μ\$     | 2    |

| tpovdd_vdd   | 0   | _   | μs      | 3    |

| tpovdd_rst   | 0   | _   | μ\$     | 4    |

Table 5. POV<sub>DD</sub> Timing <sup>5</sup>

#### Note:

- Delay required from the negation of PORESET to driving POV<sub>DD</sub> ramp up. Delay measured from PORESET negation at 90% OV<sub>DD</sub> to 10% POV<sub>DD</sub> ramp up.

- Delay required from fuse programming finished to POV<sub>DD</sub> ramp down start. Fuse programming must complete while POV<sub>DD</sub> is stable at 1.5 V. No activity other than that required for secure boot fuse programming is permitted while POV<sub>DD</sub> driven to any voltage above GND, including the reading of the fuse block. The reading of the fuse block may only occur while POV<sub>DD</sub> = GND. After fuse programming is completed, it is required to return POV<sub>DD</sub> = GND.

- 3. Delay required from POV<sub>DD</sub> ramp down complete to V<sub>DD\_CA\_CB\_PL</sub> ramp down start. POV<sub>DD</sub> must be grounded to minimum 10% POV<sub>DD</sub> before V<sub>DD\_CA\_CB\_PL</sub> is at 90% V<sub>DD</sub>.

- 4. Delay required from POV<sub>DD</sub> ramp down complete to PORESET assertion. POV<sub>DD</sub> must be grounded to minimum 10% POV<sub>DD</sub> before PORESET assertion reaches 90% OV<sub>DD</sub>.

- 5. Only two secure boot fuse programming events are permitted per lifetime of a device.

To guarantee MCKE low during power up, the above sequencing for  $GV_{DD}$  is required. If there is no concern about any of the DDR signals being in an indeterminate state during power up, the sequencing for  $GV_{DD}$  is not required.

P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2

This table shows the estimated power dissipation on the AV<sub>DD</sub> and AV<sub>DD</sub> supplies for the device PLLs, at allowable voltage levels.

Table 8. Device AV<sub>DD</sub> Power Dissipation

| AV <sub>DD</sub> s      | Typical | Maximum | Unit | Note |

|-------------------------|---------|---------|------|------|

| AV <sub>DD_DDR</sub>    | 5       | 15      | mW   | 1    |

| AV <sub>DD_CC1</sub>    |         |         |      |      |

| AV <sub>DD_CC2</sub>    |         |         |      |      |

| AV <sub>DD_PLAT</sub>   |         |         |      |      |

| AV <sub>DD_SRDS1</sub>  | _       | 36      | mW   | 2    |

| AV <sub>DD_SRDS2</sub>  |         |         |      |      |

| USB_V <sub>DD_1P0</sub> | _       | 10      | mW   | 3    |

#### Note:

- 1.  $V_{DD\_CA\_CB\_PL}$ ,  $T_A = 80^{\circ}C$ ,  $T_J = 105^{\circ}C$ 2.  $SV_{DD} = 1.0$  V,  $T_A = 80^{\circ}C$ ,  $T_J = 105^{\circ}C$

- 3. USB\_V<sub>DD 1P0</sub> = 1.0V,  $T_A = 80$ °C,  $T_J = 105$ °C

This table shows the estimated power dissipation on the POV<sub>DD</sub> supply for the chip at allowable voltage levels.

Table 9. POV<sub>DD</sub> Power Dissipation

| Supply            | Maximum | Unit | Notes |

|-------------------|---------|------|-------|

| POV <sub>DD</sub> | 450     | mW   | 1     |

#### Note:

1. To ensure device reliability, fuse programming must be performed within the recommended fuse programming temperature range per Table 3.

This table shows the estimated power dissipation on the V<sub>DD LP</sub> supply for the device, at allowable voltage levels.

Table 10. V<sub>DD\_LP</sub> Power Dissipation

| Supply                               | Maximum | Unit | Notes |

|--------------------------------------|---------|------|-------|

| V <sub>DD_LP</sub> (Device on, 105C) | 1.5     | mW   | 1     |

| V <sub>DD_LP</sub> (Device off, 70C) | 195     | uW   | 2     |

| V <sub>DD_LP</sub> (Device off, 40C) | 132     | uW   | 2     |

#### Note:

- 1.  $V_{DD\_LP} = 1.0 \text{ V}, T_J = 105$ °C.

- 2. When the device is off, V<sub>DD LP</sub> may be supplied by battery power to retain the Zeroizable Master Key and other Trust Architecture state. Board should implement a PMIC, which switches V<sub>DD LP</sub> to battery when the SoC is powered down. See the Trust Architecture chapter in the device reference manual for more information.

#### 2.5 **Thermal**

Table 11. Package Thermal Characteristics <sup>6</sup>

| Rating                                  | Board                   | Symbol         | Value | Unit | Note |

|-----------------------------------------|-------------------------|----------------|-------|------|------|

| Junction to ambient, natural convection | Single-layer board (1s) | $R_{\ThetaJA}$ | 21    | °C/W | 1, 2 |

| Junction to ambient, natural convection | Four-layer board (2s2p) | $R_{\ThetaJA}$ | 15    | °C/W | 1, 3 |

#### P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2

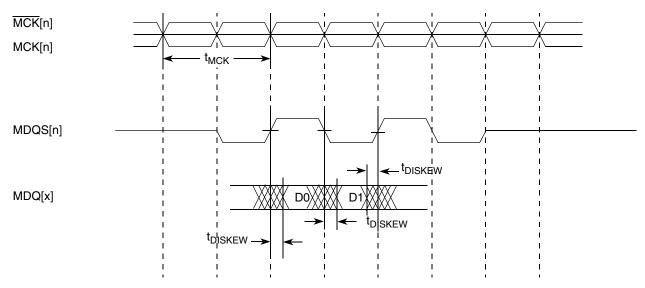

Figure 9. DDR3 and DDR3L SDRAM Interface Input Timing Diagram

# 2.9.2.2 DDR3 and DDDR3L SDRAM Interface Output AC Timing Specifications

This table provides the DDR3/DDR3L SDRAM output AC timing specifications.

Table 27. DDR3 and DDR3L SDRAM Interface Output AC Timing Specifications

For recommended operating conditions, see Table 3.

| Parameter                                 | Symbol <sup>1</sup> | Min   | Max      | Unit | Note |

|-------------------------------------------|---------------------|-------|----------|------|------|

| MCK[n] cycle time                         | t <sub>MCK</sub>    | 1.67  | 2.5      | ns   | 2    |

| ADDR/CMD output setup with respect to MCK | t <sub>DDKHAS</sub> |       |          | ns   | 3    |

| 1200 MT/s data rate                       |                     | 0.675 | _        |      |      |

| 1066 MT/s data rate                       |                     | 0.744 | _        |      |      |

| 800 MT/s data rate                        |                     | 0.917 | _        |      |      |

| ADDR/CMD output hold with respect to MCK  | t <sub>DDKHAX</sub> |       |          | ns   | 3    |

| 1200 MT/s data rate                       |                     | 0.675 | _        |      |      |

| 1066 MT/s data rate                       |                     | 0.744 | _        |      |      |

| 800 MT/s data rate                        |                     | 0.917 | _        |      |      |

| MCS[n] output setup with respect to MCK   | t <sub>DDKHCS</sub> |       |          | ns   | 3    |

| 1200 MT/s data rate                       |                     | 0.675 | _        |      |      |

| 1066 MT/s data rate                       |                     | 0.744 | _        |      |      |

| 800 MT/s data rate                        |                     | 0.917 | _        |      |      |

| MCS[n] output hold with respect to MCK    | t <sub>DDKHCX</sub> |       |          | ns   | 3    |

| 1200 MT/s data rate                       |                     | 0.675 | _        |      |      |

| 1066 MT/s data rate                       |                     | 0.744 | <u> </u> |      |      |

| 800 MT/s data rate                        |                     | 0.917 | _        |      |      |

# 2.14 Enhanced Local Bus Interface

This section describes the DC and AC electrical specifications for the enhanced local bus interface.

# 2.14.1 Enhanced Local Bus DC Electrical Characteristics

This table provides the DC electrical characteristics for the enhanced local bus interface operating at  $BV_{DD} = 3.3 \text{ V}$ .

Table 46. Enhanced Local Bus DC Electrical Characteristics (BV<sub>DD</sub> = 3.3 V)

For recommended operating conditions, see Table 3.

| Parameter                                                                    | Symbol          | Min | Max | Unit | Note |

|------------------------------------------------------------------------------|-----------------|-----|-----|------|------|

| Input high voltage                                                           | V <sub>IH</sub> | 2   | _   | V    | 1    |

| Input low voltage                                                            | V <sub>IL</sub> | _   | 0.8 | V    | 1    |

| Input current (V <sub>IN</sub> = 0 V or V <sub>IN</sub> = BV <sub>DD</sub> ) | I <sub>IN</sub> | _   | ±40 | μΑ   | 2    |

| Output high voltage<br>(BV <sub>DD</sub> = min, I <sub>OH</sub> = -2 mA)     | V <sub>OH</sub> | 2.4 | _   | V    | _    |

| Output low voltage<br>(BV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA)       | V <sub>OL</sub> | _   | 0.4 | V    | _    |

#### Note:

- 1. The min  $V_{IL}$  and max  $V_{IH}$  values are based on the respective min and max  $BV_{IN}$  values found in Table 3.

- 2. The symbol  $V_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Section 2.1.2, "Recommended Operating Conditions."

This table provides the DC electrical characteristics for the enhanced local bus interface operating at  $BV_{DD} = 2.5 \text{ V}$ .

Table 47. Enhanced Local Bus DC Electrical Characteristics (BV<sub>DD</sub> = 2.5 V)

For recommended operating conditions, see Table 3.

| Parameter                                                              | Symbol          | Min | Max | Unit | Note |

|------------------------------------------------------------------------|-----------------|-----|-----|------|------|

| Input high voltage                                                     | V <sub>IH</sub> | 1.7 | _   | V    | 1    |

| Input low voltage                                                      | V <sub>IL</sub> | _   | 0.7 | V    | 1    |

| Input current $(V_{IN} = 0 \text{ V or } V_{IN} = BV_{DD})$            | I <sub>IN</sub> | _   | ±40 | μΑ   | 2    |

| Output high voltage $(BV_{DD} = min, I_{OH} = -1 mA)$                  | V <sub>OH</sub> | 2.0 | _   | V    | _    |

| Output low voltage<br>(BV <sub>DD</sub> = min, I <sub>OL</sub> = 1 mA) | V <sub>OL</sub> | _   | 0.4 | V    | _    |

#### Note:

- 1. The min  $V_{IL}$  and max  $V_{IH}$  values are based on the respective min and max  $BV_{IN}$  values found in Table 3

- 2. The symbol  $V_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Section 2.1.2, "Recommended Operating Conditions."

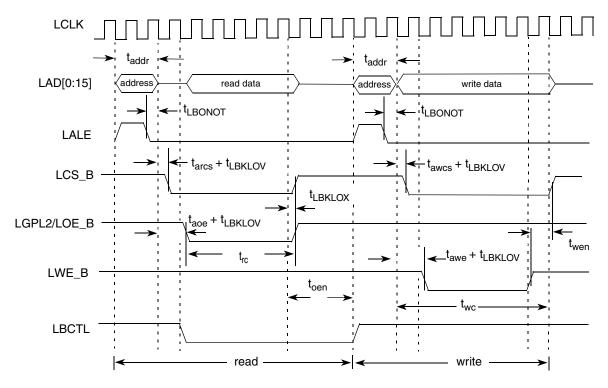

This figure shows how the AC timing diagram applies to GPCM. The same principle applies to UPM and FCM.

<sup>1</sup> t<sub>addr</sub> is programmable and determined by LCRR[EADC] and ORx[EAD].

Figure 22. GPCM Output Timing Diagram

# 2.15 Enhanced Secure Digital Host Controller (eSDHC)

This section describes the DC and AC electrical specifications for the eSDHC interface.

# 2.15.1 eSDHC DC Electrical Characteristics

This table provides the eSDHC electrical characteristics.

## **Table 50. eSDHC Interface DC Electrical Characteristics**

For recommended operating conditions, see Table 3.

| Characteristic               | Symbol                           | Condition                                            | Min                                  | Max                                 | Unit | Note |

|------------------------------|----------------------------------|------------------------------------------------------|--------------------------------------|-------------------------------------|------|------|

| Input high voltage           | V <sub>IH</sub>                  | _                                                    | $0.625 \times \text{CV}_{\text{DD}}$ | _                                   | V    | 1    |

| Input low voltage            | V <sub>IL</sub>                  | _                                                    | _                                    | $0.25 \times \text{CV}_{\text{DD}}$ | V    | 1    |

| Input/output leakage current | I <sub>IN</sub> /I <sub>OZ</sub> | _                                                    | -50                                  | 50                                  | μА   | _    |

| Output high voltage          | V <sub>OH</sub>                  | I <sub>OH</sub> = -100 μA at<br>CV <sub>DD</sub> min | $0.75 \times \text{CV}_{\text{DD}}$  | 1                                   | V    | _    |

$<sup>^{2}</sup>$   $t_{arcs}$ ,  $t_{awcs}$ ,  $t_{aoe}$ ,  $t_{rc}$ ,  $t_{oen}$ ,  $t_{awe}$ ,  $t_{wc}$ ,  $t_{wen}$  are determined by ORx. See the chip reference manual.

# Table 52. MPIC DC Electrical Characteristics (OV<sub>DD</sub> = 3.3 V) (continued)

For recommended operating conditions, see Table 3.

| Julianico Julianico IIII IIII IIII IIII IIII IIII IIII I |  | Parameter | Parameter Symbo | Min | Max | Unit | Note |

|----------------------------------------------------------|--|-----------|-----------------|-----|-----|------|------|

|----------------------------------------------------------|--|-----------|-----------------|-----|-----|------|------|

#### Note:

- 1. The min V<sub>IL</sub>and max V<sub>IH</sub> values are based on the min and max OV<sub>IN</sub> respective values found in Table 3.

- The symbol OV<sub>IN</sub>, in this case, represents the OV<sub>IN</sub> symbol referenced in Table 3.

# 2.16.2 MPIC AC Timing Specifications

This table provides the MPIC input and output AC timing specifications.

#### Table 53. MPIC Input AC Timing Specifications

For recommended operating conditions, see Table 3.

| Characteristic                   | Symbol             | Min | Max | Unit    | Note |

|----------------------------------|--------------------|-----|-----|---------|------|

| MPIC inputs—minimum pulse width  | t <sub>PIWID</sub> | 3   | _   | SYSCLKs | 1    |

| Trust inputs—minimum pulse width | t <sub>TIWID</sub> | 3   | _   | SYSCLKs | 2    |

#### Note:

- MPIC inputs and outputs are asynchronous to any visible clock. MPIC outputs must be synchronized before use by any

external synchronous logic. MPIC inputs are required to be valid for at least t<sub>PIWID</sub> ns to ensure proper operation when

working in edge triggered mode.

- Trust inputs are asynchronous to any visible clock. Trust inputs are required to be valid for at least t<sub>TIWID</sub> ns to ensure proper operation when working in edge triggered mode. For low power trust input pin LP\_TMP\_DETECT, the voltage is V<sub>DD\_LP</sub> and see Table 3 for the voltage requirment.

# 2.17 JTAG Controller

This section describes the DC and AC electrical specifications for the IEEE 1149.1 (JTAG) interface.

## 2.17.1 JTAG DC Electrical Characteristics

This table provides the JTAG DC electrical characteristics.

## Table 54. JTAG DC Electrical Characteristics (OV<sub>DD</sub> = 3.3 V)

For recommended operating conditions, see Table 3.

| Parameter                                                                      | Symbol          | Min | Max | Unit | Note |

|--------------------------------------------------------------------------------|-----------------|-----|-----|------|------|

| Input high voltage                                                             | V <sub>IH</sub> | 2   | _   | V    | 1    |

| Input low voltage                                                              | V <sub>IL</sub> | _   | 0.8 | V    | 1    |

| Input current (OV <sub>IN</sub> = 0 V or OV <sub>IN</sub> = OV <sub>DD</sub> ) | I <sub>IN</sub> | _   | ±40 | μΑ   | 2    |

| Output high voltage (OV <sub>DD</sub> = min, I <sub>OH</sub> = -2 mA)          | V <sub>OH</sub> | 2.4 | _   | V    | _    |

| Output low voltage (OV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA)            | V <sub>OL</sub> | _   | 0.4 | V    | _    |

#### Note:

- 1. The min  $V_{IL}$  and max  $V_{IH}$  values are based on the respective min and max  $OV_{IN}$  values found in Table 3.

- The symbol V<sub>IN</sub>, in this case, represents the OV<sub>IN</sub> symbol found in Table 3.

P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2

Table 65. PCI Express 2.0 (5 GT/s) Differential Receiver (Rx) Input DC Specifications (XV<sub>DD</sub> = 1.5 V or 1.8 V) (continued)

| Parameter                        | Symbol                           | Min | Тур | Max | Unit | Note                                                                                                                                                                     |

|----------------------------------|----------------------------------|-----|-----|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Electrical idle detect threshold | V <sub>RX-IDLE-DET-DIFFp-p</sub> | 65  | _   | 175 |      | $\begin{array}{l} V_{RX\text{-IDLE-DET-DIFFp-p}} = \\ 2 \times IV_{RX\text{-D+}} - V_{RX\text{-D-}}I \\ \text{Measured at the package pins of the receiver} \end{array}$ |

#### Note:

- 1. Measured at the package pins with a test load of 50  $\Omega$  to GND on each pin.

- 2. Impedance during all LTSSM states. When transitioning from a fundamental reset to detect (the initial state of the LTSSM) there is a 5 ms transition time before receiver termination values must be met on all unconfigured lanes of a port.

- 3. The Rx DC common mode impedance that exists when no power is present or fundamental reset is asserted. This helps ensure that the receiver detect circuit does not falsely assume a receiver is powered on when it is not. This term must be measured at 300 mV above the Rx ground.

# 2.20.4.5 PCI Express AC Physical Layer Specifications

This section contains the DC specifications for the physical layer of PCI Express on this device.

# 2.20.4.5.1 PCI Express AC Physical Layer Transmitter Specifications

This section discusses the PCI Express AC physical layer transmitter specifications 2.5 GT/s and 5 GT/s.

This table defines the PCI Express 2.0 (2.5 GT/s) AC specifications for the differential output at all transmitters. The parameters are specified at the component pins. The AC timing specifications do not include RefClk jitter.

Table 66. PCI Express 2.0 (2.5 GT/s) Differential Transmitter (Tx) Output AC Specifications

For recommended operating conditions, see Table 3.

| Parameter                                                                    | Symbol                                           | Min    | Тур | Max    | Unit | Note                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------|--------------------------------------------------|--------|-----|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Unit interval                                                                | UI                                               | 399.88 | 400 | 400.12 | ps   | Each UI is 400 ps ± 300 ppm. UI does not account for spread spectrum clock dictated variations. See note 1.                                                                                                                                                                                                                                                         |

| Minimum Tx eye width                                                         | T <sub>TX-EYE</sub>                              | 0.75   | _   |        | UI   | The maximum transmitter jitter can be derived as $T_{TX-MAX-JITTER} = 1 - T_{TX-EYE} = 0.25$ UI. Does not include spread spectrum or RefCLK jitter. Includes device random jitter at $10^{-12}$ . See notes 2 and 3.                                                                                                                                                |

| Maximum time between the jitter median and maximum deviation from the median | T <sub>TX-EYE-MEDIAN-</sub><br>to-<br>MAX-JITTER |        | _   | 0.125  | UI   | Jitter is defined as the measurement variation of the crossing points ( $V_{TX-DIFFp-p} = 0$ V) in relation to a recovered Tx UI. A recovered Tx UI is calculated over 3500 consecutive unit intervals of sample data. Jitter is measured using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the Tx UI. See notes 2 and 3. |

| AC coupling capacitor                                                        | C <sub>TX</sub>                                  | 75     | _   | 200    | nF   | All transmitters must be AC coupled. The AC coupling is required either within the media or within the transmitting component itself. See note 4.                                                                                                                                                                                                                   |

• The use of active circuits in the receiver, often referred to as adaptive equalization.

# 2.20.5.3 Serial RapidIO Clocking Requirements for SD\_REF\_CLK*n* and SD\_REF\_CLK*n*

SerDes bank 1 (SD\_REF\_CLK1 and SD\_REF\_CLK1) may be used for various SerDes Serial RapidIO configurations based on the RCW configuration field SRDS\_PRTCL. Serial RapidIO is not supported on SerDes banks 2.

For more information on these specifications, see Section 2.20.2, "SerDes Reference Clocks."

# 2.20.5.4 DC Requirements for Serial RapidIO

This section explains the DC requirements for the Serial RapidIO interface.

## 2.20.5.4.1 DC Serial RapidIO Timing Transmitter Specifications

LP-Serial transmitter electrical and timing specifications are stated in the text and tables of this section.

The differential return loss, S11, of the transmitter in each case is better than the following:

- −10 dB for (Baud Frequency) ÷ 10 < Freq(f) < 625 MHz

- $-10 \text{ dB} + 10 \text{log}(f \div 625 \text{ MHz}) \text{ dB for } 625 \text{ MHz} \le \text{Freq}(f) \le \text{Baud Frequency}$

The reference impedance for the differential return loss measurements is  $100-\Omega$  resistive. Differential return loss includes contributions from on-chip circuitry, chip packaging, and any off-chip components related to the driver. The output impedance requirement applies to all valid output levels.

It is recommended that the 20%–80% rise/fall time of the transmitter, as measured at the transmitter output, have a minimum value 60 ps in each case.

It is recommended that the timing skew at the output of an LP-Serial transmitter between the two signals that comprise a differential pair not exceed 20 ps at 2.50 GBaud and 15 ps at 3.125 GBaud and XX ps at 5 GBaud.

This table defines the transmitter DC specifications for Serial RapidIO operating at  $XV_{DD} = 1.5 \text{ V}$  or 1.8 V.

Table 70. Serial RapidIO Transmitter DC Timing Specifications—2.5 GBaud, 3.125 GBaud, 5 GBaud For recommended operating conditions, see Table 3.

| Parameter                             | Symbol              | Min   | Тур | Max  | Unit   | Note |

|---------------------------------------|---------------------|-------|-----|------|--------|------|

| Output voltage                        | V <sub>O</sub>      | -0.40 | _   | 2.30 | V      | 1    |

| Long-run differential output voltage  | V <sub>DIFFPP</sub> | 800   | _   | 1600 | mV p-p | _    |

| Short-run differential output voltage | V <sub>DIFFPP</sub> | 500   | _   | 1000 | mV p-p | _    |

#### Note:

1. Voltage relative to COMMON of either signal comprising a differential pair.

# 2.20.5.4.2 DC Serial RapidIO Receiver Specifications

LP-Serial receiver electrical and timing specifications are stated in the text and tables of this section.

Receiver input impedance results in a differential return loss better than 10 dB and a common mode return loss better than 6 dB from 100 MHz to  $(0.8) \times (Baud Frequency)$ . This includes contributions from on-chip circuitry, the chip package, and any off-chip components related to the receiver. AC coupling components are included in this requirement. The reference impedance for return loss measurements is 100- $\Omega$  resistive for differential return loss and 25- $\Omega$  resistive for common mode.

P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2

This table defines the receiver DC specifications for Serial RapidIO operating at  $XV_{DD} = 1.5 \text{ V}$  or 1.8 V.

Table 71. Serial RapidIO Receiver DC Timing Specifications—2.5 GBaud, 3.125 GBaud, 5 GBaud

For recommended operating conditions, see Table 3.

| Parameter                  | Symbol   | Min | Тур | Max  | Unit   | Note |

|----------------------------|----------|-----|-----|------|--------|------|

| Differential input voltage | $V_{IN}$ | 200 |     | 1600 | mV p-p | 1    |

#### Note:

1. Measured at the receiver.

# 2.20.5.5 AC Requirements for Serial RapidIO

This section explains the AC requirements for the Serial RapidIO interface.

# 2.20.5.5.1 AC Requirements for Serial RapidIO Transmitter

This table defines the transmitter AC specifications for the Serial RapidIO interface. The AC timing specifications do not include RefClk jitter.

Table 72. Serial RapidIO Transmitter AC Timing Specifications

For recommended operating conditions, see Table 3.

| Parameter                  | Symbol         | Min          | Typical | Max          | Unit   |

|----------------------------|----------------|--------------|---------|--------------|--------|

| Deterministic jitter       | $J_{D}$        | _            | _       | 0.17         | UI p-p |

| Total jitter               | J <sub>T</sub> | _            | _       | 0.35         | UI p-p |

| Unit interval: 2.5 GBaud   | UI             | 400 – 100ppm | 400     | 400 + 100ppm | ps     |

| Unit interval: 3.125 GBaud | UI             | 320 – 100ppm | 320     | 320 + 100ppm | ps     |

This table defines the receiver AC specifications for Serial RapidIO. The AC timing specifications do not include RefClk jitter.

## **Table 73. Serial RapidIO Receiver AC Timing Specifications**

For recommended operating conditions, see Table 3.

| Parameter                                          | Symbol   | Min          | Typical | Max               | Unit   | Note |

|----------------------------------------------------|----------|--------------|---------|-------------------|--------|------|

| Deterministic jitter tolerance                     | $J_D$    | 0.37         | _       | _                 | UI p-p | 1    |

| Combined deterministic and random jitter tolerance | $J_{DR}$ | 0.55         | _       | _                 | UI p-p | 1    |

| Total jitter tolerance <sup>2</sup>                | $J_T$    | 0.65         | _       | _                 | UI p-p | 1    |

| Bit error rate                                     | BER      | _            | _       | 10 <sup>-12</sup> | _      | _    |

| Unit interval: 2.5 GBaud                           | UI       | 400 – 100ppm | 400     | 400 + 100ppm      | ps     | _    |

| Unit interval: 3.125 GBaud                         | UI       | 320 – 100ppm | 320     | 320 + 100ppm      | ps     | _    |

#### Note:

- 1. Measured at receiver

- 2. Total jitter is composed of three components: deterministic jitter, random jitter, and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 42. The sinusoidal jitter component is included to ensure margin for low-frequency jitter, wander, noise, crosstalk, and other variable system effects.

P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2

## Table 82. SATA Reference Clock Input Requirements (continued)

For recommended operating conditions, see Table 3.

| Parameter                                                                    | Symbol               | Min             | Тур | Max | Unit | Note    |

|------------------------------------------------------------------------------|----------------------|-----------------|-----|-----|------|---------|

| SD_REF_CLK/SD_REF_CLK cycle-to-cycle clock jitter (period jitter)            | t <sub>CLK</sub> _CJ | _               | _   | 100 | ps   | 2       |

| SD_REF_CLK/SD_REF_CLK total reference clock jitter, phase jitter (peak-peak) | t <sub>CLK_PJ</sub>  | <del>-</del> 50 | ı   | +50 | ps   | 2, 3, 4 |

#### Note:

- 1. Caution: Only 100, 125 MHz have been tested. In-between values do not work correctly with the rest of the system.

- 2. At RefClk input

- 3. In a frequency band from 150 kHz to 15 MHz at BER of 10<sup>-12</sup>

- 4. Total peak-to-peak deterministic jitter must be less than or equal to 50 ps.

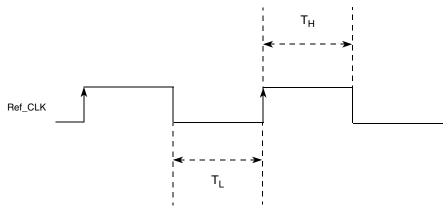

This figure shows the reference clock timing waveform.

Figure 43. Reference Clock Timing Waveform

# 2.20.7.3 AC Transmitter Output Characteristics

This table provides the differential transmitter output AC characteristics for the SATA interface at Gen1i or 1.5 Gbits/s transmission. The AC timing specifications do not include RefClk jitter.

Table 83. Gen1i/1.5 G Transmitter (Tx) AC Specifications

For recommended operating conditions, see Table 3.

| Parameter                              | Symbol                      | Min      | Тур      | Max      | Unit   | Note |

|----------------------------------------|-----------------------------|----------|----------|----------|--------|------|

| Channel speed                          | t <sub>CH_SPEED</sub>       | _        | 1.5      | _        | Gbps   | _    |

| Unit Interval                          | T <sub>UI</sub>             | 666.4333 | 666.6667 | 670.2333 | ps     | _    |

| Total jitter data-data 5 UI            | U <sub>SATA_TXTJ5UI</sub>   | _        | _        | 0.355    | UI p-p | 1    |

| Total jitter, data-data 250 UI         | U <sub>SATA_TXTJ250UI</sub> | _        | _        | 0.47     | UI p-p | 1    |

| Deterministic jitter, data-data 5 UI   | U <sub>SATA_TXDJ5UI</sub>   | _        | _        | 0.175    | UI p-p | 1    |

| Deterministic jitter, data-data 250 UI | U <sub>SATA_TXDJ250UI</sub> | _        | _        | 0.22     | UI p-p | 1    |

P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2

This table provides the differential receiver input AC characteristics for the SATA interface at Gen2i or 3.0 Gbits/s transmission. The AC timing specifications do not include RefClk jitter.

## Table 86. Gen 2i/3G Receiver (Rx) AC Specifications

For recommended operating conditions, see Table 3.

| Parameter                                                          | Symbol                        | Min      | Typical  | Max      | Unit   | Note |

|--------------------------------------------------------------------|-------------------------------|----------|----------|----------|--------|------|

| Unit Interval                                                      | T <sub>UI</sub>               | 333.2167 | 333.3333 | 335.1167 | ps     | _    |

| Total jitter f <sub>C3dB</sub> = f <sub>BAUD</sub> ÷ 10            | U <sub>SATA_TXTJfB/10</sub>   | _        | _        | 0.46     | UI p-p | 1    |

| Total jitter f <sub>C3dB</sub> = f <sub>BAUD</sub> ÷ 500           | U <sub>SATA_TXTJfB/500</sub>  | _        | _        | 0.60     | UI p-p | 1    |

| Total jitter f <sub>C3dB</sub> = f <sub>BAUD</sub> ÷ 1667          | U <sub>SATA_TXTJfB/1667</sub> | _        | _        | 0.65     | UI p-p | 1    |

| Deterministic jitter, f <sub>C3dB</sub> = f <sub>BAUD</sub> ÷ 10   | U <sub>SATA_TXDJfB/10</sub>   | _        | _        | 0.35     | UI p-p | 1    |

| Deterministic jitter, f <sub>C3dB</sub> = f <sub>BAUD</sub> ÷ 500  | U <sub>SATA_TXDJfB/500</sub>  | _        | _        | 0.42     | UI p-p | 1    |

| Deterministic jitter, f <sub>C3dB</sub> = f <sub>BAUD</sub> ÷ 1667 | U <sub>SATA_TXDJfB/1667</sub> | _        | _        | 0.35     | UI p-p | 1    |

#### Note:

## 2.20.8 SGMII Interface

Each SGMII port features a 4-wire AC-coupled serial link from the SerDes interface of the device, as shown in Figure 44, where  $C_{TX}$  is the external (on board) AC-coupled capacitor. Each output pin of the SerDes transmitter differential pair features 50- $\Omega$  output impedance. Each input of the SerDes receiver differential pair features 50- $\Omega$  on-die termination to XGND. The reference circuit of the SerDes transmitter and receiver is shown in Figure 39.

# 2.20.8.0.1 SGMII Clocking Requirements for SD\_REF\_CLKn and SD\_REF\_CLKn

When operating in SGMII mode, the EC\_GTX\_CLK125 clock is not required for this port. Instead, a SerDes reference clock is required on SD\_REF\_CLK[1:2] and SD\_REF\_CLK[1:2] pins. SerDes banks 1–2 may be used for SerDes SGMII configurations based on the RCW Configuration field SRDS\_PRTCL.

For more information on these specifications, see Section 2.20.2, "SerDes Reference Clocks."

## 2.20.8.1 SGMII DC Electrical Characteristics

This section discusses the electrical characteristics for the SGMII interface.

# 2.20.8.1.1 SGMII Transmit DC Timing Specifications

This table describe the SGMII SerDes transmitter and receiver AC-coupled DC electrical characteristics for 1.25 GBaud. Transmitter DC characteristics are measured at the transmitter outputs  $(SD_TXn)$  and  $\overline{SD_TXn}$  as shown in Figure 45.

Table 87. SGMII DC Transmitter Electrical Characteristics (XV<sub>DD</sub> = 1.5 V or 1.8 V)

For recommended operating conditions, see Table 3.

| Parameter           | Symbol          | Min                                   | Тур | Max                                      | Unit | Note |

|---------------------|-----------------|---------------------------------------|-----|------------------------------------------|------|------|

| Output high voltage | V <sub>OH</sub> | _                                     | _   | 1.5 x IV <sub>OD</sub> I <sub>-max</sub> | mV   | 1    |

| Output low voltage  | V <sub>OL</sub> | IV <sub>OD</sub> I <sub>-min</sub> /2 | _   | _                                        | mV   | 1    |

P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2

<sup>1.</sup> Measured at receiver.

# 3.3 Power Supply Design

This section discusses the power supply design.

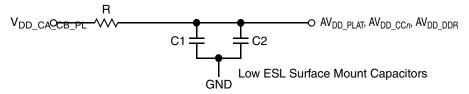

# 3.3.1 PLL Power Supply Filtering

Each of the PLLs described in Section 3.1, "System Clocking," is provided with power through independent power supply pins (AV<sub>DD\_PLAT</sub>, AV<sub>DD\_CCn</sub>, AV<sub>DD\_DDR</sub>, and AV<sub>DD\_SRDSn</sub>). AV<sub>DD\_PLAT</sub>, AV<sub>DD\_CCn</sub> and AV<sub>DD\_DDR</sub> voltages must be derived directly from the V<sub>DD\_CA\_CB\_PL</sub> source through a low frequency filter scheme. AV<sub>DD\_SRDSn</sub> voltages must be derived directly from the SV<sub>DD</sub> source through a low frequency filter scheme.

The recommended solution for PLL filtering is to provide independent filter circuits per PLL power supply, as illustrated in Figure 50, one for each of the  $AV_{DD}$  pins. By providing independent filters to each PLL the opportunity to cause noise injection from one PLL to the other is reduced.

This circuit is intended to filter noise in the PLL's resonant frequency range from a 500-kHz to 10-MHz range.

Each circuit must be placed as close as possible to the specific  $AV_{DD}$  pin being supplied to minimize noise coupled from nearby circuits. It must be possible to route directly from the capacitors to the  $AV_{DD}$  pin, which is on the periphery of the footprint, without the inductance of vias.

Figure 50 shows the PLL power supply filter circuit.

#### Where:

```

R = 5 \Omega \pm 5\%

C1 = 10 \mu F \pm 10\%, 0603, X5R, \text{ with ESL} \le 0.5 \text{ nH}

C2 = 1.0 \mu F \pm 10\%, 0402, X5R, \text{ with ESL} \le 0.5 \text{ nH}

```

#### NOTE

A higher capacitance value for C2 may be used to improve the filter as long as the other C2 parameters do not change (0402 body, X5R, ESL  $\leq$  0.5 nH).

Voltage for AV<sub>DD</sub> is defined at the PLL supply filter and not the pin of AV<sub>DD</sub>.

Figure 50. PLL Power Supply Filter Circuit

The  $AV_{DD\_SRDSn}$  signals provides power for the analog portions of the SerDes PLL. To ensure stability of the internal clock, the power supplied to the PLL is filtered using a circuit similar to the one shown in following Figure 51. For maximum effectiveness, the filter circuit is placed as closely as possible to the  $AV_{DD\_SRDSn}$  balls to ensure it filters out as much noise as possible. The ground connection must be near the  $AV_{DD\_SRDSn}$  balls. The 0.003- $\mu$ F capacitor is closest to the balls, followed by two 2.2- $\mu$ F capacitors, and finally the 1- $\Omega$  resistor to the board supply plane. The capacitors are connected from  $AV_{DD\_SRDSn}$

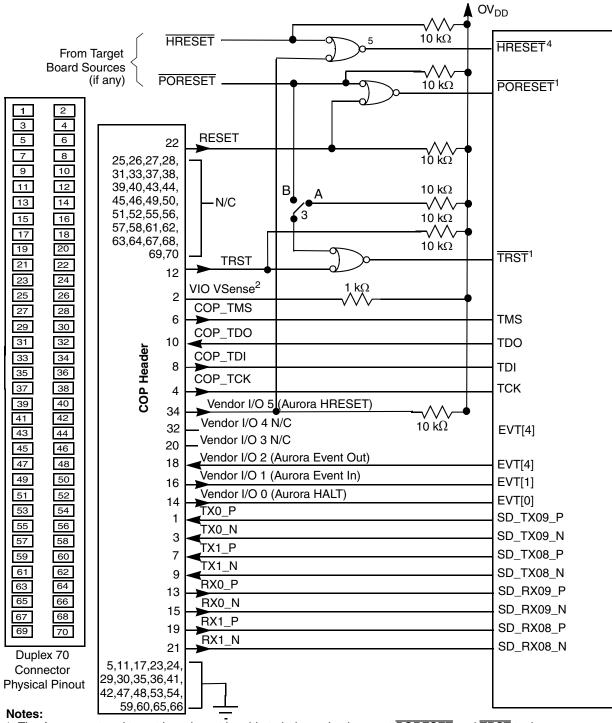

- 1. The Aurora port and target board must be able to independently assert PORESET and TRST to the processor in order to fully control the processor as shown here.

- 2. Populate this with a 1  $k\Omega$  resistor for short-circuit/current-limiting protection.

- 3. This switch is included as a precaution for BSDL testing. The switch must be closed to position A during BSDL testing to avoid accidentally asserting the TRST line. If BSDL testing is not being performed, this switch must be closed to position B.

- 4. Asserting HRESET causes a hard reset on the device. 5. This is an open-drain gate.

Figure 59. Aurora 70 Pin Connector Duplex Interface Connection

P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2