Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 25MHz                                                                    |

| Connectivity               | UART/USART                                                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 4KB (2K x 16)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 4x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

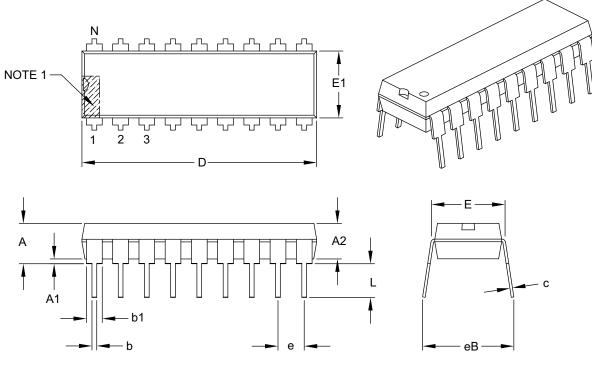

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 18-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f1230-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

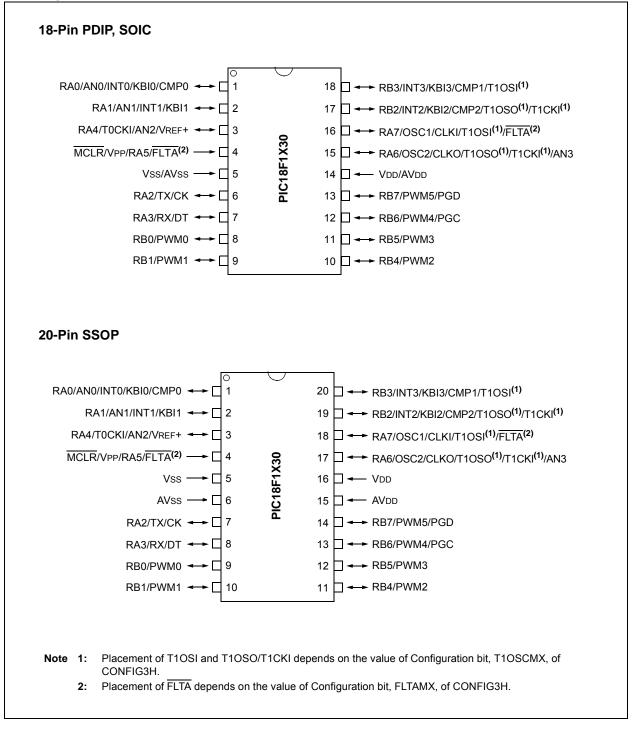

### **Pin Diagrams**

#### 8.7 **Operation During Code-Protect**

Data EEPROM memory has its own code-protect bits in Configuration Words. External read and write operations are disabled if either of these mechanisms are enabled.

The microcontroller itself can both read and write to the internal data EEPROM, regardless of the state of the code-protect Configuration bit. Refer to Section 20.0 "Special Features of the CPU" for additional information.

#### 8.8 Using the Data EEPROM

The data EEPROM is a high-endurance, byte addressable array that has been optimized for the storage of frequently changing information (e.g., program variables or other data that are updated often). Frequently changing values will typically be updated more often than specification D124. If this is not the case, an array refresh must be performed. For this reason, variables that change infrequently (such as constants, IDs, calibration, etc.) should be stored in Flash program memory.

A simple data EEPROM refresh routine is shown in Example 8-3.

Note: If data EEPROM is only used to store constants and/or data that changes rarely, an array refresh is likely not required. See specification D124.

| EXAMPLE 8-3: DATA EEPROM REFRESH ROUTINE |        |               |                              |  |  |  |

|------------------------------------------|--------|---------------|------------------------------|--|--|--|

|                                          | CLRF   | EEADR         | ; Start at address 0         |  |  |  |

|                                          | BCF    | EECON1, CFGS  | ; Set for memory             |  |  |  |

|                                          | BCF    | EECON1, EEPGD | ; Set for Data EEPROM        |  |  |  |

|                                          | BCF    | INTCON, GIE   | ; Disable interrupts         |  |  |  |

|                                          | BSF    | EECON1, WREN  | ; Enable writes              |  |  |  |

| LOOP                                     |        |               | ; Loop to refresh array      |  |  |  |

|                                          | BSF    | EECON1, RD    | ; Read current address       |  |  |  |

|                                          | MOVLW  | 55h           | ;                            |  |  |  |

| Required                                 | MOVWF  | EECON2        | ; Write 55h                  |  |  |  |

| Sequence                                 | MOVLW  | 0AAh          | ;                            |  |  |  |

|                                          | MOVWF  | EECON2        | ; Write OAAh                 |  |  |  |

|                                          | BSF    | EECON1, WR    | ; Set WR bit to begin write  |  |  |  |

|                                          | BTFSC  | EECON1, WR    | ; Wait for write to complete |  |  |  |

|                                          | BRA    | \$-2          |                              |  |  |  |

|                                          | INCFSZ | EEADR, F      | ; Increment address          |  |  |  |

|                                          | BRA    | LOOP          | ; Not zero, do it again      |  |  |  |

|                                          |        |               |                              |  |  |  |

|                                          | BCF    | EECON1, WREN  | ; Disable writes             |  |  |  |

|                                          | BSF    | INTCON, GIE   | ; Enable interrupts          |  |  |  |

####

| TABLE 8-1: | REGISTERS ASSOCIATED WITH DATA EEPROM MEMORY |

|------------|----------------------------------------------|

|            |                                              |

| Name   | Bit 7                                   | Bit 6          | Bit 5         | Bit 4       | Bit 3  | Bit 2  | Bit 1  | Bit 0 | Reset<br>Values on<br>Page: |

|--------|-----------------------------------------|----------------|---------------|-------------|--------|--------|--------|-------|-----------------------------|

| INTCON | GIE/GIEH                                | PEIE/GIEL      | TMR0IE        | INT0IE      | RBIE   | TMR0IF | INT0IF | RBIF  | 47                          |

| EEADR  | ADR EEPROM Address Register             |                |               |             |        |        |        |       |                             |

| EEDATA | EEPROM Data Register                    |                |               |             |        |        |        |       |                             |

| EECON2 | EEPROM Co                               | ontrol Registe | er 2 (not a p | hysical reg | ister) |        |        |       | 49                          |

| EECON1 | CON1 EEPGD CFGS — FREE WRERR WREN WR RD |                |               |             |        |        |        |       | 49                          |

| IPR2   | OSCFIP                                  | _              |               | EEIP        |        | LVDIP  | _      | _     | 49                          |

| PIR2   | OSCFIF                                  | _              |               | EEIF        |        | LVDIF  |        |       | 49                          |

| PIE2   | OSCFIE                                  |                | _             | EEIE        | _      | LVDIE  | _      | _     | 49                          |

Legend: — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

Example 9-3 shows the sequence to do a 16 x 16 unsigned multiplication. Equation 9-1 shows the algorithm that is used. The 32-bit result is stored in four registers (RES3:RES0).

### EQUATION 9-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

| RES3:RES0= | ARG1H:ARG1L • ARG2H:ARG2L                |

|------------|------------------------------------------|

| =          | $(ARG1H \bullet ARG2H \bullet 2^{16}) +$ |

|            | $(ARG1H \bullet ARG2L \bullet 2^8) +$    |

|            | $(ARG1L \bullet ARG2H \bullet 2^8) +$    |

|            | (ARG1L • ARG2L)                          |

### EXAMPLE 9-3: 16 x 16 UNSIGNED MULTIPLY ROUTINE

|   | MOVF   | ARG1L, W    |   |                 |

|---|--------|-------------|---|-----------------|

|   | MULWF  | ARG2L       | ; | ARG1L * ARG2L-> |

|   |        |             | ; | PRODH:PRODL     |

|   | MOVFF  | PRODH, RES1 | ; |                 |

|   | MOVFF  | PRODL, RESO | ; |                 |

| ; |        |             |   |                 |

|   | MOVF   | ARG1H, W    |   |                 |

|   | MULWF  | ARG2H       | ; | ARG1H * ARG2H-> |

|   |        |             | ; | PRODH:PRODL     |

|   |        | PRODH, RES3 |   |                 |

|   | MOVFF  | PRODL, RES2 | ; |                 |

| ; |        |             |   |                 |

|   |        | ARG1L, W    |   |                 |

|   | MULWF  | ARG2H       | ; | ARG1L * ARG2H-> |

|   |        |             | ; | PRODH:PRODL     |

|   |        |             | ; |                 |

|   |        | RES1, F     |   |                 |

|   |        | PRODH, W    |   | products        |

|   |        | RES2, F     | ; |                 |

|   |        | WREG        | ; |                 |

|   | ADDWFC | RES3, F     | ; |                 |

| ; |        |             |   |                 |

|   |        | ARG1H, W    |   |                 |

|   | MULWF  | ARG2L       |   | ARG1H * ARG2L-> |

|   |        |             |   | PRODH:PRODL     |

|   |        | PRODL, W    |   |                 |

|   |        | RES1, F     |   |                 |

|   |        | PRODH, W    |   | products        |

|   |        | RES2, F     |   |                 |

|   | CLRF   |             | ; |                 |

|   | ADDWFC | RES3, F     | ; |                 |

Example 9-4 shows the sequence to do a 16 x 16 signed multiply. Equation 9-2 shows the algorithm used. The 32-bit result is stored in four registers (RES3:RES0). To account for the sign bits of the arguments, the MSb for each argument pair is tested and the appropriate subtractions are done.

#### EQUATION 9-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

| RES3:RES0=ARG1H:ARG1L • ARG2H:ARG2L                             |

|-----------------------------------------------------------------|

| $= (ARG1H \bullet ARG2H \bullet 2^{16}) +$                      |

| $(ARG1H \bullet ARG2L \bullet 2^8) +$                           |

| $(ARG1L \bullet ARG2H \bullet 2^8) +$                           |

| $(ARG1L \bullet ARG2L) +$                                       |

| $(-1 \bullet ARG2H < 7 > \bullet ARG1H:ARG1L \bullet 2^{16}) +$ |

| $(-1 \bullet ARG1H < 7 > \bullet ARG2H:ARG2L \bullet 2^{16})$   |

#### EXAMPLE 9-4: 16 x 16 SIGNED MULTIPLY ROUTINE

|     | MOVF   | ARG1L, W      |   |                  |

|-----|--------|---------------|---|------------------|

|     |        |               | ; | ARG1L * ARG2L -> |

|     |        |               |   | PRODH:PRODL      |

|     | MOVFF  | PRODH, RES1   |   |                  |

|     | MOVFF  | PRODL, RESO   |   |                  |

| ;   |        |               |   |                  |

|     | MOVF   | ARG1H, W      |   |                  |

|     | MULWF  |               | ; | ARG1H * ARG2H -> |

|     |        |               |   | PRODH:PRODL      |

|     | MOVFF  | PRODH, RES3   |   |                  |

|     | MOVFF  | PRODL, RES2   |   |                  |

| ;   |        | 110000, 11000 |   |                  |

| ,   | MOVE   | ARG1L, W      |   |                  |

|     |        |               | ; | ARG1L * ARG2H -> |

|     | HOLMI  |               |   | PRODH:PRODL      |

|     | MOVF   |               | ; | TRODIT TRODE     |

|     |        |               |   | Add cross        |

|     | MOVF   |               |   | products         |

|     | ADDWEC |               |   | products         |

|     |        |               | ; |                  |

|     |        |               | ; |                  |

|     | ADDWFC | RES3, F       | ; |                  |

| ;   | MOLTE  |               |   |                  |

|     |        | ARG1H, W      |   |                  |

|     | MULWF  |               |   | ARG1H * ARG2L -> |

|     |        |               |   | PRODH:PRODL      |

|     | MOVF   |               | ; | - 11             |

|     |        |               |   | Add cross        |

|     | MOVF   |               |   | products         |

|     |        |               | ; |                  |

|     |        | WREG          | ; |                  |

|     | ADDWFC | RES3, F       | ; |                  |

| ;   |        |               |   |                  |

|     |        |               |   | ARG2H:ARG2L neg? |

|     | BRA    |               |   | no, check ARG1   |

|     |        |               | ; |                  |

|     | SUBWF  | RES2          | ; |                  |

|     |        | ARG1H, W      | ; |                  |

|     | SUBWFB | RES3          |   |                  |

| ;   |        |               |   |                  |

| SIG | N_ARG1 |               |   |                  |

|     |        |               |   | ARG1H:ARG1L neg? |

|     | BRA    |               | ; | no, done         |

|     |        |               | ; |                  |

|     | SUBWF  | RES2          | ; |                  |

|     |        | ARG2H, W      | ; |                  |

|     | SUBWFB | RES3          |   |                  |

| ;   |        |               |   |                  |

| CON | T_CODE |               |   |                  |

|     | :      |               |   |                  |

|     |        |               |   |                  |

| Name    | Bit 7                 | Bit 6                 | Bit 5    | Bit 4                                                     | Bit 3   | Bit 2  | Bit 1  | Bit 0 | Reset<br>Values<br>on Page: |  |  |

|---------|-----------------------|-----------------------|----------|-----------------------------------------------------------|---------|--------|--------|-------|-----------------------------|--|--|

| PORTA   | RA7 <sup>(1)</sup>    | RA6 <sup>(1)</sup>    | RA5      | RA4                                                       | RA3     | RA2    | RA1    | RA0   | 50                          |  |  |

| LATA    | LATA7 <sup>(1)</sup>  | LATA6 <sup>(1)</sup>  | PORTA OL | ORTA Output Latch Register (Read and Write to Data Latch) |         |        |        |       |                             |  |  |

| TRISA   | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | PORTA Da | PORTA Data Direction Control Register                     |         |        |        |       |                             |  |  |

| INTCON  | GIE/GIEH              | PEIE/GIEL             | TMR0IE   | TMROIE INTOIE RBIE TMROIF INTOIF RBIF                     |         |        |        |       |                             |  |  |

| INTCON2 | RBPU                  | INTEDG0               | INTEDG1  | INTEDG2                                                   | INTEDG3 | TMR0IP | INT3IP | RBIP  | 47                          |  |  |

| ADCON1  | _                     | _                     | _        | VCFG0                                                     | PCFG3   | PCFG2  | PCFG1  | PCFG0 | 48                          |  |  |

| CMCON   | C2OUT                 | C1OUT                 | COOUT    | —                                                         | —       | CMEN2  | CMEN1  | CMEN0 | 48                          |  |  |

| CVRCON  | CVREN                 | _                     | CVRR     | CVRSS                                                     | CVR3    | CVR2   | CVR1   | CVR0  | 48                          |  |  |

TABLE 10-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

Legend: — = unimplemented, read as '0'. Shaded cells are not used by PORTA.

**Note 1:** RA7:RA6 and their associated latch and data direction bits are enabled as I/O pins based on oscillator configuration; otherwise, they are read as '0'.

# 11.0 INTERRUPTS

The PIC18F1230/1330 devices have multiple interrupt sources and an interrupt priority feature that allows most interrupt sources to be assigned a high-priority level or a low-priority level. The high-priority interrupt vector is at 0008h and the low-priority interrupt vector is at 0018h. High-priority interrupt events will interrupt any low-priority interrupts that may be in progress.

There are thirteen registers which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2, PIR3

- PIE1, PIE2, PIE3

- IPR1, IPR2, IPR3

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/ compiler to automatically take care of the placement of these bits within the specified register.

In general, interrupt sources have three bits to control their operation. They are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- Priority bit to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address 0008h or 0018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit, which enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit, which enables/disables all interrupt sources. All interrupts branch to address 0008h in Compatibility mode.

When an interrupt is responded to, the global interrupt enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High-priority interrupt sources can interrupt a lowpriority interrupt. Low-priority interrupts are not processed while high-priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (0008h or 0018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INT pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding enable bit or the GIE bit.

**Note:** Do not use the MOVFF instruction to modify any of the interrupt control registers while **any** interrupt is enabled. Doing so may cause erratic microcontroller behavior.

| R/W-0                                                                      | U-0                                                                                                       | U-0             | R/W-0 | U-0 | R/W-0 | U-0 | U-0   |  |  |  |

|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------|-------|-----|-------|-----|-------|--|--|--|

| OSCFIE                                                                     |                                                                                                           | —               | EEIE  | —   | LVDIE | —   |       |  |  |  |

| bit 7                                                                      |                                                                                                           |                 |       |     |       |     | bit 0 |  |  |  |

|                                                                            |                                                                                                           |                 |       |     |       |     |       |  |  |  |

| Legend:                                                                    |                                                                                                           |                 |       |     |       |     |       |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'       |                                                                                                           |                 |       |     |       |     |       |  |  |  |

| -n = Value at POR (1' = Bit is set (0' = Bit is cleared x = Bit is unknown |                                                                                                           |                 |       |     |       |     |       |  |  |  |

| bit 7<br>bit 6-5                                                           | OSCFIE: Oscillator Fail Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled<br>Unimplemented: Read as '0' |                 |       |     |       |     |       |  |  |  |

| bit 4                                                                      | •                                                                                                         |                 |       |     |       |     |       |  |  |  |

| bit 3                                                                      | Unimplement                                                                                               | ted: Read as 'd | )'    |     |       |     |       |  |  |  |

| bit 2                                                                      | LVDIE: Low-Voltage Detect Interrupt Enable bit                                                            |                 |       |     |       |     |       |  |  |  |

|                                                                            | 1 = Enabled<br>0 = Disabled                                                                               |                 |       |     |       |     |       |  |  |  |

| bit 1-0                                                                    | Unimplement                                                                                               | ted: Read as 'd | )'    |     |       |     |       |  |  |  |

#### REGISTER 11-9: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

| U-0   | U-0 | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-------|-----|-----|-----|-------|

| —     | —   | —   | PTIE  | —   | —   | —   | —     |

| bit 7 |     |     |       |     |     |     | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

- bit 7-5 Unimplemented: Read as '0'

- bit 4 PTIE: PWM Time Base Interrupt Enable bit

- 1 = PWM enabled

- 0 = PWM disabled

- bit 3-0 Unimplemented: Read as '0'

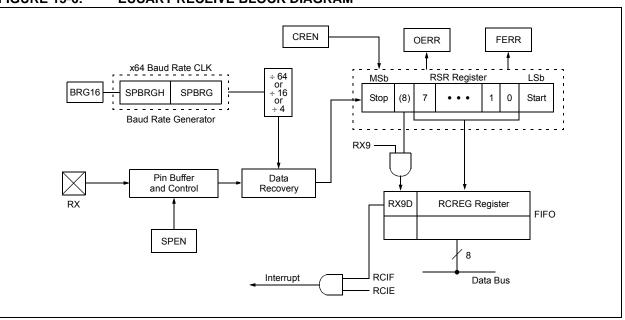

### 15.2.2 EUSART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 15-6. The data is received on the RX pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc. This mode would typically be used in RS-232 systems.

To set up an Asynchronous Reception:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, set enable bit RCIE.

- 4. If 9-bit reception is desired, set bit RX9.

- 5. Enable the reception by setting bit CREN.

- Flag bit, RCIF, will be set when reception is complete and an interrupt will be generated if enable bit, RCIE, was set.

- Read the RCSTA register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

- 10. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

# 15.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are required, set the RCEN bit and select the desired priority level with the RCIP bit.

- 4. Set the RX9 bit to enable 9-bit reception.

- 5. Set the ADDEN bit to enable address detect.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF bit will be set when reception is complete. The interrupt will be Acknowledged if the RCIE and GIE bits are set.

- Read the RCSTA register to determine if any error occurred during reception, as well as read bit 9 of data (if applicable).

- 9. Read RCREG to determine if the device is being addressed.

- 10. If any error occurred, clear the CREN bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and interrupt the CPU.

#### FIGURE 15-6: EUSART RECEIVE BLOCK DIAGRAM

# 18.0 COMPARATOR VOLTAGE REFERENCE MODULE

The comparator voltage reference is a 16-tap resistor ladder network that provides a selectable reference voltage. Its purpose is to provide a reference for the analog comparators.

A block diagram of the module is shown in Figure 18-1. The resistor ladder is segmented to provide two ranges of CVREF values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/VSS or an external voltage reference.

# 18.1 Configuring the Comparator Voltage Reference

The voltage reference module is controlled through the CVRCON register (Register 18-1). The comparator voltage reference provides two ranges of output voltage, each with 16 distinct levels. The range to be used is selected by the CVRR bit (CVRCON<5>). The primary difference between the ranges is the size of the steps selected by the CVREF selection bits (CVR3:CVR0), with one range offering finer resolution. The equations used to calculate the output of the comparator voltage reference are as follows:

$\frac{\text{If CVRR} = 1:}{\text{CVREF} = ((\text{CVR3:CVR0})/24) \times \text{CVRSRC}}$  $\frac{\text{If CVRR} = 0:}{\text{CVREF} = ((\text{CVR3:CVR0})/24) + (((\text{CVR3:CVR0})/24) \times \text{CVRSRC})}$

CVREF = (CVRSRC x 1/4) + (((CVR3:CVR0)/32) x CVRSRC)

The comparator reference supply voltage can come from either AVDD or AVSS, or the external VREF+ that is multiplexed with RA4 and AVSS. The voltage source is selected by the CVRSS bit (CVRCON<4>).

Additionally, the voltage reference can select the unscaled VREF+ input for use by the comparators, bypassing the CVREF module. (See Table 18-1 and Figure 18-1.)

The settling time of the comparator voltage reference must be considered when changing the CVREF output (see Table 23-3 in **Section 23.0 "Electrical Characteristics"**).

TABLE 18-1: VOLTAGE REFERENCE OUTPUT

| CVREN | CVRSS | CVREF    | Comparator Input              |

|-------|-------|----------|-------------------------------|

| 0     | 0     | Disabled | No reference                  |

| 0     | 1     | Disabled | From VREF<br>(CVREF bypassed) |

| 1     | 0     | Enabled  | From CVREF                    |

| 1     | 1     | Enabled  | From CVREF                    |

| R/W-0           | U-0                                                                  | R/W-0            | R/W-0         | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|----------------------------------------------------------------------|------------------|---------------|-------------------|------------------|-----------------|-------|

| CVREN           | 0-0                                                                  | CVRR             | CVRSS         | CVR3              | CVR2             | CVR1            | CVR0  |

|                 | —                                                                    | CVKK             | CVRSS         | CVR3              | CVR2             | CVRI            |       |

| bit 7           |                                                                      |                  |               |                   |                  |                 | bit 0 |

| Legend:         |                                                                      |                  |               |                   |                  |                 |       |

| R = Readable    | bit                                                                  | W = Writable     | hit           | U = Unimpler      | mented bit, read | 1 as '0'        |       |

| -n = Value at F |                                                                      | '1' = Bit is set |               | '0' = Bit is cle  |                  | x = Bit is unkr | nown  |

|                 |                                                                      |                  |               |                   |                  |                 |       |

| bit 7           | CVREN: Com                                                           | parator Voltag   | e Reference I | Enable bit        |                  |                 |       |

|                 | 1 = CVREF cit                                                        |                  |               |                   |                  |                 |       |

|                 |                                                                      | rcuit powered    |               |                   |                  |                 |       |

| bit 6           | Unimplemen                                                           | ted: Read as '   | 0'            |                   |                  |                 |       |

| bit 5           | CVRR: Comp                                                           | arator VREF R    | ange Selectio | n bit             |                  |                 |       |

|                 |                                                                      |                  |               | step size (low r  | •                |                 |       |

|                 | 0 = 0.25  CVR                                                        | SRC to 0.75 C    | VRSRC, with C | VRSRC/32 step     | size (high rang  | le)             |       |

| bit 4           | CVRSS: Com<br>When CVRR                                              | •                | Source Select | ion bit           |                  |                 |       |

|                 |                                                                      |                  |               | RC = (VREF+) –    | ( <b>Δ\/</b> SS) |                 |       |

|                 |                                                                      |                  | •             | RC = AVDD - AV    | · /              |                 |       |

|                 | When CVRR                                                            |                  |               |                   |                  |                 |       |

|                 | 1 = VREF+ input used directly, comparator voltage reference bypassed |                  |               |                   |                  |                 |       |

|                 |                                                                      | ence is provide  |               |                   |                  |                 |       |

| bit 3-0         |                                                                      | •                | REF Value Se  | lection bits (0 ≤ | (CVR3:CVR0)      | ≤ 15)           |       |

|                 | When CVRR                                                            |                  |               |                   |                  |                 |       |

|                 | CVREF = ((CV<br>When CVRR                                            |                  |               |                   |                  |                 |       |

|                 | CVREF = (CVF                                                         |                  | R3:CVR0)/32   | ) • (CVRSRC)      |                  |                 |       |

|                 |                                                                      |                  |               | , ()              |                  |                 |       |

## REGISTER 18-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

### REGISTER 20-11: CONFIG7L: CONFIGURATION REGISTER 7 LOW (BYTE ADDRESS 30000Ch)

| U-0        | U-0                                                                    | U-0            | U-0                         | U-0          | U-0              | R/C-1                | R/C-1                |  |  |

|------------|------------------------------------------------------------------------|----------------|-----------------------------|--------------|------------------|----------------------|----------------------|--|--|

|            | —                                                                      | _              | _                           | —            | —                | EBTR1 <sup>(1)</sup> | EBTR0 <sup>(1)</sup> |  |  |

| bit 7      | bit 7                                                                  |                |                             |              |                  |                      |                      |  |  |

|            |                                                                        |                |                             |              |                  |                      |                      |  |  |

| Legend:    |                                                                        |                |                             |              |                  |                      |                      |  |  |

| R = Reada  | ble bit                                                                | C = Clearable  | e bit                       | U = Unimpler | mented bit, read | as '0'               |                      |  |  |

| -n = Value | when device is unp                                                     | programmed     |                             | u = Unchang  | ed from progran  | nmed state           |                      |  |  |

|            |                                                                        |                |                             |              |                  |                      |                      |  |  |

| bit 7-2    | Unimplement                                                            | ted: Read as ' | 0'                          |              |                  |                      |                      |  |  |

| bit 1      | EBTR1: Table                                                           | e Read Protect | ion bit (Block <sup>·</sup> | 1 Code Memor | y Area)          |                      |                      |  |  |

|            | 1 = Block 1 is not protected from table reads executed in other blocks |                |                             |              |                  |                      |                      |  |  |

|            | 0 = Block 1 is protected from table reads executed in other blocks     |                |                             |              |                  |                      |                      |  |  |

| bit 0      | EBTR0: Table Read Protection bit (Block 0 Code Memory Area)            |                |                             |              |                  |                      |                      |  |  |

|            | 1 = Block 0 is not protected from table reads executed in other blocks |                |                             |              |                  |                      |                      |  |  |

|            | 0 = Block 0 is protected from table reads executed in other blocks     |                |                             |              |                  |                      |                      |  |  |

**Note 1:** It is recommended to enable the corresponding CPx bit to protect block from external read operations.

### REGISTER 20-12: CONFIG7H: CONFIGURATION REGISTER 7 HIGH (BYTE ADDRESS 30000Dh)

| U-0                                    | R/C-1                | U-0 | U-0 | U-0                                 | U-0 | U-0 | U-0   |  |  |

|----------------------------------------|----------------------|-----|-----|-------------------------------------|-----|-----|-------|--|--|

| —                                      | EBTRB <sup>(1)</sup> | —   | —   | —                                   | —   | —   | —     |  |  |

| bit 7                                  |                      |     |     | •                                   |     |     | bit 0 |  |  |

|                                        |                      |     |     |                                     |     |     |       |  |  |

| Legend:                                | Legend:              |     |     |                                     |     |     |       |  |  |

| R = Readable bit C = Clearable bit     |                      |     | bit | U = Unimplemented bit, read as '0'  |     |     |       |  |  |

| -n = Value when device is unprogrammed |                      |     |     | u = Unchanged from programmed state |     |     |       |  |  |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                                   |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | EBTRB: Table Read Protection bit (Boot Block Memory Area)                                                                                                                    |

|         | <ul> <li>1 = Boot Block is not protected from table reads executed in other blocks</li> <li>0 = Boot Block is protected from table reads executed in other blocks</li> </ul> |

|         | ·                                                                                                                                                                            |

| bit 5-0 | Unimplemented: Read as '0'                                                                                                                                                   |

| Note 1: | It is recommended to enable the corresponding CPx bit to protect block from external read operations.                                                                        |

#### FIGURE 22-1: GENERAL FORMAT FOR INSTRUCTIONS

| FIGURE 22-1: | GENERAL FORMAT FOR INSTRUCTIONS                                                                                                                                                                                                                                                                       |                      |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|              | Byte-oriented file register operations                                                                                                                                                                                                                                                                | Example Instruction  |

|              | 15     10     9     8     7     0       OPCODE     d     a     f (FILE #)       d = 0 for result destination to be WREG register       d = 1 for result destination to be file register (f)       a = 0 to force Access Bank       a = 1 for BSR to select bank       f = 8-bit file register address | ADDWF MYREG, W, B    |

|              | Byte to Byte move operations (2-word)                                                                                                                                                                                                                                                                 |                      |

|              | 15       12       11       0         OPCODE       f (Source FILE #)       15       12       11       0         15       12       11       0       1111       f (Destination FILE #)         f = 12-bit file register address       12       12       12       12                                      | MOVFF MYREG1, MYREG2 |

|              | Bit-oriented file register operations                                                                                                                                                                                                                                                                 |                      |

|              | 15     12 11     9 8 7     0       OPCODE     b (BIT #)     a     f (FILE #)       b = 3-bit position of bit in file register (f)       a = 0 to force Access Bank                                                                                                                                    | BSF MYREG, bit, B    |

|              | a = 1 for BSR to select bank<br>f = 8-bit file register address                                                                                                                                                                                                                                       |                      |

|              | -                                                                                                                                                                                                                                                                                                     |                      |

|              | Literal operations           15         8         7         0           OPCODE         k (literal)           k = 8-bit immediate value                                                                                                                                                                | MOVLW 7Fh            |

|              |                                                                                                                                                                                                                                                                                                       |                      |

|              | Control operations<br>CALL, GOTO and Branch operations<br>15 8 7 0                                                                                                                                                                                                                                    |                      |

|              | OPCODE n<7:0> (literal)                                                                                                                                                                                                                                                                               | GOTO Label           |

|              | 15 12 11 0                                                                                                                                                                                                                                                                                            |                      |

|              | n = 20-bit immediate value                                                                                                                                                                                                                                                                            |                      |

|              | 15 8 7 0                                                                                                                                                                                                                                                                                              |                      |

|              | OPCODE S n<7:0> (literal)                                                                                                                                                                                                                                                                             | CALL MYFUNC          |

|              | 15 12 11 0                                                                                                                                                                                                                                                                                            |                      |

|              | 1111 n<19:8> (literal)<br>S = Fast bit                                                                                                                                                                                                                                                                |                      |

|              |                                                                                                                                                                                                                                                                                                       |                      |

|              | 15 11 10 0<br>OPCODE n<10:0> (literal)                                                                                                                                                                                                                                                                | BRA MYFUNC           |

|              |                                                                                                                                                                                                                                                                                                       |                      |

|              | 15 8 7 0<br>OPCODE n<7:0> (literal)                                                                                                                                                                                                                                                                   | BC MYFUNC            |

|              |                                                                                                                                                                                                                                                                                                       |                      |

|              |                                                                                                                                                                                                                                                                                                       |                      |

| DAV   | ,                 | Decimal A                     | Adjust W Re                                                              | gister                         | DECF     |                           | Decreme                                                     | nt f                                                                             |                  |

|-------|-------------------|-------------------------------|--------------------------------------------------------------------------|--------------------------------|----------|---------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------|------------------|

| Synta | ax:               | DAW                           |                                                                          |                                | Syntax:  |                           | DECF f{,                                                    | d {,a}}                                                                          |                  |

| Oper  | ands:             | None                          |                                                                          |                                | Operano  | ds:                       | 0 ≤ f ≤ 255                                                 |                                                                                  |                  |

| Oper  | ation:            |                               | > 9] or [DC = 1<br>6 → W<3:0>;                                           | ] then,                        | ·        |                           | d ∈ [0,1]<br>a ∈ [0,1]                                      |                                                                                  |                  |

|       |                   | else,                         | o , 11 (0.0°,                                                            |                                | Operatio | on:                       | $(f) - 1 \rightarrow de$                                    | est                                                                              |                  |

|       |                   | (W<3:0>) –                    | → W<3:0>                                                                 |                                | Status A | Affected:                 | C, DC, N, 0                                                 | DV, Z                                                                            |                  |

|       |                   | lf [W<7:4> ∙                  | + DC > 9] or [C                                                          | C = 1] then,                   | Encodin  | ıg:                       | 0000                                                        | 01da ff                                                                          | ff ffff          |

|       |                   | (W<7:4>) +                    | $-6 + DC \rightarrow W^{-1}$                                             | -                              | Descript | tion:                     | Decrement                                                   | register 'f'. If                                                                 | 'd' is '0', the  |

|       |                   | else,<br>(W<7:4>) +           | $DC \rightarrow W < 7:4$                                                 | >                              |          |                           |                                                             | ored in W. If 'd<br>ored back in re                                              |                  |

| Statu | s Affected:       | С                             |                                                                          |                                |          |                           | lf 'a' is '0', t                                            | he Access Ba                                                                     | nk is selected.  |

| Enco  | ding:             | 0000                          | 0000 000                                                                 | 00 0111                        |          |                           | lf 'a' is '1', t<br>GPR bank.                               |                                                                                  | ed to select the |

| Desc  | ription:          | resulting fro<br>variables (e | s the eight-bit<br>om the earlier a<br>each in packed<br>es a correct pa | addition of two<br>BCD format) |          |                           | set is enab<br>in Indexed<br>mode wher<br><b>Section 22</b> | led, this instru<br>Literal Offset<br>never f ≤ 95 (5<br>2. <b>2.3 "Byte-O</b> r | Fh). See         |

| Word  | s:                | 1                             |                                                                          |                                |          |                           |                                                             | ed Instruction<br>set Mode" for                                                  |                  |

| Cycle | es:               | 1                             |                                                                          |                                | Words:   |                           | 1                                                           |                                                                                  |                  |

| QC    | ycle Activity:    |                               |                                                                          |                                | Cycles:  |                           | 1                                                           |                                                                                  |                  |

|       | Q1                | Q2                            | Q3                                                                       | Q4                             | -        | e Activity:               |                                                             |                                                                                  |                  |

|       | Decode            | Read<br>register W            | Process<br>Data                                                          | Write<br>W                     |          | Q1                        | Q2                                                          | Q3                                                                               | Q4               |

| Exan  | nple 1:           |                               |                                                                          |                                |          | Decode                    | Read                                                        | Process                                                                          | Write to         |

|       |                   | DAW                           |                                                                          |                                |          |                           | register 'f'                                                | Data                                                                             | destination      |

|       | Before Instruc    | ction                         |                                                                          |                                | Example  | ۵.                        | DECF                                                        | CNT, 1, 0                                                                        | 1                |

|       | W<br>C            | = A5h<br>= 0                  |                                                                          |                                |          | <u>e.</u><br>fore Instruc |                                                             | CINI, I, U                                                                       | ,                |

|       | DC                | = 0<br>= 0                    |                                                                          |                                | De       | CNT                       | = 01h                                                       |                                                                                  |                  |

|       | After Instruction | on                            |                                                                          |                                |          | Z                         | = 0                                                         |                                                                                  |                  |

|       | W                 | = 05h                         |                                                                          |                                | Aft      | er Instructi<br>CNT       | on<br>= 00h                                                 |                                                                                  |                  |

|       | C<br>DC           | = 1<br>= 0                    |                                                                          |                                |          | Z                         | = 1                                                         |                                                                                  |                  |

| Exan  | <u>ple 2:</u>     | Ū                             |                                                                          |                                |          |                           |                                                             |                                                                                  |                  |

|       | Before Instruc    | ction                         |                                                                          |                                |          |                           |                                                             |                                                                                  |                  |

|       | W<br>C<br>DC      | = CEh<br>= 0<br>= 0           |                                                                          |                                |          |                           |                                                             |                                                                                  |                  |

|       | After Instruction | on                            |                                                                          |                                |          |                           |                                                             |                                                                                  |                  |

|       | W<br>C<br>DC      | = 34h<br>= 1<br>= 0           |                                                                          |                                |          |                           |                                                             |                                                                                  |                  |

| GOT         | GOTO Unconditional Branch                |                                          |                                                                                                                                                                                      |         |                                       |  |  |  |

|-------------|------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------|--|--|--|

| Synta       | ax:                                      | GOTO k                                   |                                                                                                                                                                                      |         |                                       |  |  |  |

| Oper        | ands:                                    | $0 \le k \le 104$                        | 8575                                                                                                                                                                                 |         |                                       |  |  |  |

| Oper        | ation:                                   | $k \rightarrow PC<20$                    | ):1>                                                                                                                                                                                 |         |                                       |  |  |  |

| Statu       | is Affected:                             | None                                     |                                                                                                                                                                                      |         |                                       |  |  |  |

|             | oding:<br>vord (k<7:0>)<br>word(k<19:8>) | 1110<br>1111                             |                                                                                                                                                                                      |         |                                       |  |  |  |

| Desc        | ription:                                 | anywhere v<br>2-Mbyte me<br>value 'k' is | GOTO allows an unconditional branch<br>anywhere within entire<br>2-Mbyte memory range. The 20-bit<br>value 'k' is loaded into PC<20:1>.<br>GOTO is always a two-cycle<br>instruction |         |                                       |  |  |  |

| Word        | ls:                                      | 2                                        |                                                                                                                                                                                      |         |                                       |  |  |  |

| Cycle       | es:                                      | 2                                        |                                                                                                                                                                                      |         |                                       |  |  |  |

| QC          | ycle Activity:                           |                                          |                                                                                                                                                                                      |         |                                       |  |  |  |

|             | Q1                                       | Q2                                       | Q3                                                                                                                                                                                   | 1       | Q4                                    |  |  |  |

|             | Decode                                   | Read literal<br>'k'<7:0>,                | No<br>operat                                                                                                                                                                         | tion 'k | ead literal<br>2<19:8>,<br>rite to PC |  |  |  |

|             | No<br>operation                          | No<br>operation                          |                                                                                                                                                                                      |         |                                       |  |  |  |

| <u>Exan</u> | nple:                                    | GOTO THE                                 | RE                                                                                                                                                                                   |         |                                       |  |  |  |

After Instruction

PC = Address (THERE)

| INCF              | Incremen                                                                                                                                                                 | ll I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |                       |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------|--|

| Syntax:           | INCF f{,c                                                                                                                                                                | d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |                       |  |

| Operands:         | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |                       |  |

| Operation:        | (f) + 1 $\rightarrow$ de                                                                                                                                                 | est                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                       |  |

| Status Affected:  | C, DC, N,                                                                                                                                                                | OV, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |                       |  |

| Encoding:         | 0010                                                                                                                                                                     | 10da                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ffff | ffff                  |  |

|                   | placed in W<br>placed bac<br>If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank.<br>If 'a' is '0' a<br>set is enab<br>in Indexed<br>mode wher<br>Section 22<br>Bit-Oriente | The contents of register 'f' are<br>incremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f'.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 22.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |      |                       |  |

| Words:            | 1                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |                       |  |

| Cycles:           | 1                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |                       |  |

| Q Cycle Activity: |                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |                       |  |

| Q1                | Q2                                                                                                                                                                       | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      | Q4                    |  |

| Decode            | Read<br>register 'f'                                                                                                                                                     | Proce<br>Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      | Write to<br>estinatio |  |