Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | UART/USART                                                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 4KB (2K x 16)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 4x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 18-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f1230-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.7.1 OSCILLATOR CONTROL REGISTER

The OSCCON register (Register 3-2) controls several aspects of the device clock's operation, both in full power operation and in power-managed modes.

The System Clock Select bits, SCS1:SCS0, select the clock source. The available clock sources are the primary clock (defined by the FOSC3:FOSC0 Configuration bits), the secondary clock (Timer1 oscillator) and the internal oscillator block. The clock source changes immediately after one or more of the bits is written to, following a brief clock transition interval. The SCS bits are cleared on all forms of Reset.

The Internal Oscillator Frequency Select bits (IRCF2:IRCF0) select the frequency output of the internal oscillator block to drive the device clock. The choices are the INTRC source, the INTOSC source (8 MHz) or one of the frequencies derived from the INTOSC postscaler (31.25 kHz to 4 MHz). If the internal oscillator block is supplying the device clock, changing the states of these bits will have an immediate change on the internal oscillator's output. On device Resets, the default output frequency of the internal oscillator block is set at 1 MHz.

When a nominal output frequency of 31 kHz is selected (IRCF2:IRCF0 = 000), users may choose which internal oscillator acts as the source. This is done with the INTSRC bit in the OSCTUNE register (OSCTUNE<7>). Setting this bit selects INTOSC as a 31.25 kHz clock source by enabling the divide-by-256 output of the INTOSC postscaler. Clearing INTSRC selects INTRC (nominally 31 kHz) as the clock source.

This option allows users to select the tunable and more precise INTOSC as a clock source, while maintaining power savings with a very low clock speed. Regardless of the setting of INTSRC, INTRC always remains the clock source for features such as the Watchdog Timer and the Fail-Safe Clock Monitor.

The OSTS, IOFS and T1RUN bits indicate which clock source is currently providing the device clock. The OSTS bit indicates that the Oscillator Start-up Timer has timed out and the primary clock is providing the device clock in primary clock modes. The IOFS bit indicates when the internal oscillator block has stabilized and is providing the device clock in RC Clock modes. The T1RUN bit (T1CON<6>) indicates when the Timer1 oscillator is providing the device clock in secondary clock modes. In power-managed modes, only one of these three bits will be set at any time. If none of these bits are set, the INTRC is providing the clock or the internal oscillator block has just started and is not yet stable. The IDLEN bit determines if the device goes into Sleep mode or one of the Idle modes when the SLEEP instruction is executed.

The use of the flag and control bits in the OSCCON register is discussed in more detail in **Section 4.0** "**Power-Managed Modes**".

- Note 1: The Timer1 oscillator must be enabled to select the secondary clock source. The Timer1 oscillator is enabled by setting the T1OSCEN bit in the Timer1 Control register (T1CON<3>). If the Timer1 oscillator is not enabled, then any attempt to select a secondary clock source will be ignored.

- 2: It is recommended that the Timer1 oscillator be operating and stable before selecting the secondary clock source or a very long delay may occur while the Timer1 oscillator starts.

#### 3.7.2 OSCILLATOR TRANSITIONS

PIC18F1230/1330 devices contain circuitry to prevent clock "glitches" when switching between clock sources. A short pause in the device clock occurs during the clock switch. The length of this pause is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Clock transitions are discussed in greater detail in **Section 4.1.2 "Entering Power-Managed Modes"**.

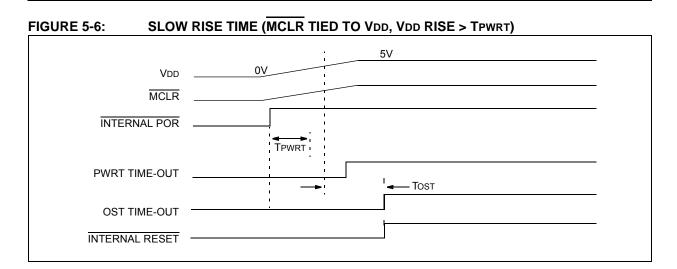

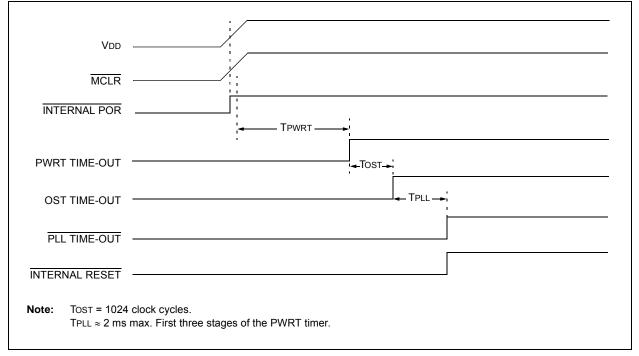

# FIGURE 5-7: TIME-OUT SEQUENCE ON POR W/PLL ENABLED (MCLR TIED TO VDD)

| TABLE 5-4: | INITIA | LIZATIO       | N CONDITIONS FOR                   |                                                                  |                                 |  |  |  |

|------------|--------|---------------|------------------------------------|------------------------------------------------------------------|---------------------------------|--|--|--|

| Register   |        | cable<br>ices | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |  |  |

| TOSU       | 1230   | 1330          | 0 0000                             | 0 0000                                                           | 0 uuuu <b>(3)</b>               |  |  |  |

| TOSH       | 1230   | 1330          | 0000 0000                          | 0000 0000                                                        | uuuu uuuu <b>(3)</b>            |  |  |  |

| TOSL       | 1230   | 1330          | 0000 0000                          | 0000 0000                                                        | uuuu uuuu <sup>(3)</sup>        |  |  |  |

| STKPTR     | 1230   | 1330          | 00-0 0000                          | uu-0 0000                                                        | uu-u uuuu <b>(3)</b>            |  |  |  |

| PCLATU     | 1230   | 1330          | 0 0000                             | 0 0000                                                           | u uuuu                          |  |  |  |

| PCLATH     | 1230   | 1330          | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |  |  |

| PCL        | 1230   | 1330          | 0000 0000                          | 0000 0000                                                        | PC + 2 <sup>(2)</sup>           |  |  |  |

| TBLPTRU    | 1230   | 1330          | 00 0000                            | 00 0000                                                          | uu uuuu                         |  |  |  |

| TBLPTRH    | 1230   | 1330          | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |  |  |

| TBLPTRL    | 1230   | 1330          | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |  |  |

| TABLAT     | 1230   | 1330          | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |  |  |

| PRODH      | 1230   | 1330          | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |

| PRODL      | 1230   | 1330          | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |

| INTCON     | 1230   | 1330          | 0000 000x                          | 0000 000u                                                        | uuuu uuuu <b>(1)</b>            |  |  |  |

| INTCON2    | 1230   | 1330          | 1111 1111                          | 1111 1111                                                        | uuuu uuuu <b>(1)</b>            |  |  |  |

| INTCON3    | 1230   | 1330          | 1100 0000                          | 1100 0000                                                        | uuuu uuuu <b>(1)</b>            |  |  |  |

| INDF0      | 1230   | 1330          | N/A                                | N/A                                                              | N/A                             |  |  |  |

| POSTINC0   | 1230   | 1330          | N/A                                | N/A                                                              | N/A                             |  |  |  |

| POSTDEC0   | 1230   | 1330          | N/A                                | N/A                                                              | N/A                             |  |  |  |

| PREINC0    | 1230   | 1330          | N/A                                | N/A                                                              | N/A                             |  |  |  |

| PLUSW0     | 1230   | 1330          | N/A                                | N/A                                                              | N/A                             |  |  |  |

| FSR0H      | 1230   | 1330          | 0000                               | 0000                                                             | uuuu                            |  |  |  |

| FSR0L      | 1230   | 1330          | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |

| WREG       | 1230   | 1330          | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |

| INDF1      | 1230   | 1330          | N/A                                | N/A                                                              | N/A                             |  |  |  |

| POSTINC1   | 1230   | 1330          | N/A                                | N/A                                                              | N/A                             |  |  |  |

| POSTDEC1   | 1230   | 1330          | N/A                                | N/A                                                              | N/A                             |  |  |  |

| PREINC1    | 1230   | 1330          | N/A                                | N/A                                                              | N/A                             |  |  |  |

| PLUSW1     | 1230   | 1330          | N/A                                | N/A                                                              | N/A                             |  |  |  |

| FSR1H      | 1230   | 1330          | 0000                               | 0000                                                             | uuuu                            |  |  |  |

| FSR1L      | 1230   | 1330          | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |

| BSR        | 1230   | 1330          | 0000                               | 0000                                                             | uuuu                            |  |  |  |

TABLE 5-4:

INITIALIZATION CONDITIONS FOR ALL REGISTERS

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- **2:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 5-3 for Reset value for specific condition.

- **5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read as '0'.

- 6: Reset condition of PWMEN bits depends on the PWMPIN Configuration bit of CONFIG3L.

| Pin                  | Function             | TRIS<br>Setting | MARY<br>I/O | l/O<br>Type | Description                                                                                                                        |

|----------------------|----------------------|-----------------|-------------|-------------|------------------------------------------------------------------------------------------------------------------------------------|

|                      |                      | Setting         |             |             |                                                                                                                                    |

| RB0/PWM0             | RB0                  | 0               | 0           | DIG         | LATB<0> data output; not affected by analog input.                                                                                 |

|                      |                      | 1               | I           | TTL         | PORTB<0> data input; weak pull-up when RBPU bit is cleared.<br>Disabled when analog input enabled. <sup>(1)</sup>                  |

|                      | PWM0                 | 0               | 0           | DIG         | PWM module output PWM0.                                                                                                            |

| RB1PWM1              | RB1                  | 0               | 0           | DIG         | LATB<1> data output; not affected by analog input.                                                                                 |

|                      |                      | 1               | Ι           | TTL         | PORTB<1> data input; weak pull-up when RBPU bit is cleared.<br>Disabled when analog input enabled. <sup>(1)</sup>                  |

|                      | PWM1                 | 0               | 0           | DIG         | PWM module output PWM1.                                                                                                            |

| RB2/INT2/KBI2/       | RB2                  | 0               | 0           | DIG         | LATB<2> data output; not affected by analog input.                                                                                 |

| CMP2/T1OSO/<br>T1CKI |                      | 1               | Ι           | TTL         | PORTB<2> data input; weak pull-up when $\overline{\text{RBPU}}$ bit is cleared. Disabled when analog input enabled. <sup>(1)</sup> |

|                      | INT2                 | 1               | Ι           | ST          | External interrupt 2 input.                                                                                                        |

|                      | KBI2                 | 1               | Ι           | TTL         | Interrupt-on-change pin.                                                                                                           |

|                      | CMP2                 | 1               | I           | ANA         | Comparator 2 input.                                                                                                                |

|                      | T10SO <sup>(2)</sup> | 0               | 0           | ANA         | Timer1 oscillator output.                                                                                                          |

|                      | T1CKI <sup>(2)</sup> | 1               | Ι           | ST          | Timer1 clock input.                                                                                                                |

| RB3/INT3/KBI3/       | RB3                  | 0               | 0           | DIG         | LATB<3> data output; not affected by analog input.                                                                                 |

| CMP1/T1OSI           |                      | 1               | Ι           | TTL         | PORTB<3> data input; weak pull-up when $\overline{\text{RBPU}}$ bit is cleared. Disabled when analog input enabled. <sup>(1)</sup> |

|                      | INT3                 | 1               | I           | ST          | External interrupt 3 input.                                                                                                        |

|                      | KBI3                 | 1               | I           | TTL         | Interrupt-on-change pin.                                                                                                           |

|                      | CMP1                 | 1               | Ι           | ANA         | Comparator 1 input.                                                                                                                |

|                      | T10SI <sup>(2)</sup> | 1               | Ι           | ANA         | Timer1 oscillator input.                                                                                                           |

| RB4/PWM2             | RB4                  | 0               | 0           | DIG         | LATB<4> data output; not affected by analog input.                                                                                 |

|                      |                      | 1               | Ι           | TTL         | PORTB<4> data input; weak pull-up when $\overline{\text{RBPU}}$ bit is cleared. Disabled when analog input enabled. <sup>(1)</sup> |

|                      | PWM2                 | 0               | 0           | DIG         | PWM module output PWM2.                                                                                                            |

| RB5/PWM3             | RB5                  | 0               | 0           | DIG         | LATB<5> data output.                                                                                                               |

|                      |                      | 1               | Ι           | TTL         | PORTB<5> data input; weak pull-up when RBPU bit is cleared.                                                                        |

|                      | PWM3                 | 0               | 0           | DIG         | PWM module output PWM3.                                                                                                            |

| RB6/PWM4/PGC         | RB6                  | 0               | 0           | DIG         | LATB<6> data output.                                                                                                               |

|                      |                      | 1               | Ι           | TTL         | PORTB<6> data input; weak pull-up when RBPU bit is cleared.                                                                        |

|                      | PWM4                 | 0               | 0           | DIG         | PWM module output PWM4.                                                                                                            |

|                      | PGC                  | 1               | Ι           | ST          | In-Circuit Debugger and ICSP™ programming clock pin.                                                                               |

| RB7/PWM5/PGD         | RB7                  | 0               | 0           | DIG         | LATB<7> data output.                                                                                                               |

|                      |                      | 1               | Ι           | TTL         | PORTB<7> data input; weak pull-up when RBPU bit is cleared.                                                                        |

|                      | PWM5                 | 0               | 0           | TTL         | PWM module output PWM4.                                                                                                            |

|                      | PGD                  | 0               | 0           | DIG         | In-Circuit Debugger and ICSP programming data pin.                                                                                 |

TABLE 10-3: PORTB I/O SUMMARY

Legend: DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

**Note 1:** Configuration on POR is determined by the PBADEN Configuration bit. Pins are configured as analog inputs by default when PBADEN is set and digital inputs when PBADEN is cleared.

2: Placement of T1OSI and T1OSO/T1CKI depends on the value of Configuration bit, T1OSCMX, of CONFIG3H.

#### 11.1 INTCON Registers

The INTCON registers are readable and writable registers, which contain various enable, priority and flag bits.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

#### REGISTER 11-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0    | R/W-0     | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-x               |

|----------|-----------|--------|--------|-------|--------|--------|---------------------|

| GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF <sup>(1)</sup> |

| bit 7    |           |        |        |       |        |        | bit 0               |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | GIE/GIEH: Global Interrupt Enable bit<br>When IPEN = 0:<br>1 = Enables all unmasked interrupts<br>0 = Disables all interrupts<br>When IPEN = 1:<br>1 = Enables all high-priority interrupts<br>0 = Disables all interrupts                                                                            |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | PEIE/GIEL: Peripheral Interrupt Enable bit<br><u>When IPEN = 0:</u><br>1 = Enables all unmasked peripheral interrupts<br>0 = Disables all peripheral interrupts<br><u>When IPEN = 1:</u><br>1 = Enables all low-priority peripheral interrupts<br>0 = Disables all low-priority peripheral interrupts |

| bit 5 | TMR0IE: TMR0 Overflow Interrupt Enable bit<br>1 = Enables the TMR0 overflow interrupt<br>0 = Disables the TMR0 overflow interrupt                                                                                                                                                                     |

| bit 4 | INTOIE: INTO External Interrupt Enable bit<br>1 = Enables the INTO external interrupt<br>0 = Disables the INTO external interrupt                                                                                                                                                                     |

| bit 3 | <b>RBIE:</b> RB Port Change Interrupt Enable bit<br>1 = Enables the RB port change interrupt<br>0 = Disables the RB port change interrupt                                                                                                                                                             |

| bit 2 | <b>TMR0IF:</b> TMR0 Overflow Interrupt Flag bit<br>1 = TMR0 register has overflowed (must be cleared in software)<br>0 = TMR0 register did not overflow                                                                                                                                               |

| bit 1 | INTOIF: INTO External Interrupt Flag bit<br>1 = The INTO external interrupt occurred (must be cleared in software)<br>0 = The INTO external interrupt did not occur                                                                                                                                   |

| bit 0 | <b>RBIF:</b> RB Port Change Interrupt Flag bit <sup>(1)</sup><br>1 = At least one of the RB7:RB4 pins changed state (must be cleared in software)<br>0 = None of the RB7:RB4 pins have changed state                                                                                                  |

|       |                                                                                                                                                                                                                                                                                                       |

**Note 1:** A mismatch condition will continue to set this bit. Reading PORTB will end the mismatch condition and allow the bit to be cleared.

#### 13.4 Timer1 Interrupt

The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The Timer1 interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing Timer1 interrupt enable bit, TMR1IE (PIE1<0>).

#### 13.5 Timer1 16-Bit Read/Write Mode

Timer1 can be configured for 16-bit reads and writes (see Figure 13-2). When the RD16 control bit (T1CON<7>) is set, the address for TMR1H is mapped to a buffer register for the high byte of Timer1. A read from TMR1L will load the contents of the high byte of Timer1 into the Timer1 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, is valid due to a rollover between reads.

A write to the high byte of Timer1 must also take place through the TMR1H Buffer register. Timer1 high byte is updated with the contents of TMR1H when a write occurs to TMR1L. This allows a user to write all 16 bits to both the high and low bytes of Timer1 at once.

The high byte of Timer1 is not directly readable or writable in this mode. All reads and writes must take place through the Timer1 High Byte Buffer register. Writes to TMR1H do not clear the Timer1 prescaler. The prescaler is only cleared on writes to TMR1L.

#### 13.6 Using Timer1 as a Real-Time Clock

Adding an external LP oscillator to Timer1 (such as the one described in **Section 13.2 "Timer1 Oscillator**"), gives users the option to include RTC functionality to their applications. This is accomplished with an inexpensive watch crystal to provide an accurate time base and several lines of application code to calculate the time. When operating in Sleep mode and using a battery or super capacitor as a power source, it can completely eliminate the need for a separate RTC device and battery backup.

The application code routine, RTCisr, shown in Example 13-1, demonstrates a simple method to increment a counter at one-second intervals using an Interrupt Service Routine. Incrementing the TMR1 register pair to overflow triggers the interrupt and calls the routine, which increments the seconds counter by one. Additional counters for minutes and hours are incremented as the previous counter overflow.

Since the register pair is 16 bits wide, counting up to overflow the register directly from a 32.768 kHz clock would take 2 seconds. To force the overflow at the required one-second intervals, it is necessary to preload it. The simplest method is to set the MSb of TMR1H with a BSF instruction. Note that the TMR1L register is never preloaded or altered; doing so may introduce cumulative error over many cycles.

For this method to be accurate, Timer1 must operate in Asynchronous mode and the Timer1 overflow interrupt must be enabled (PIE1<0> = 1), as shown in the routine, RTCinit. The Timer1 oscillator must also be enabled and running at all times.

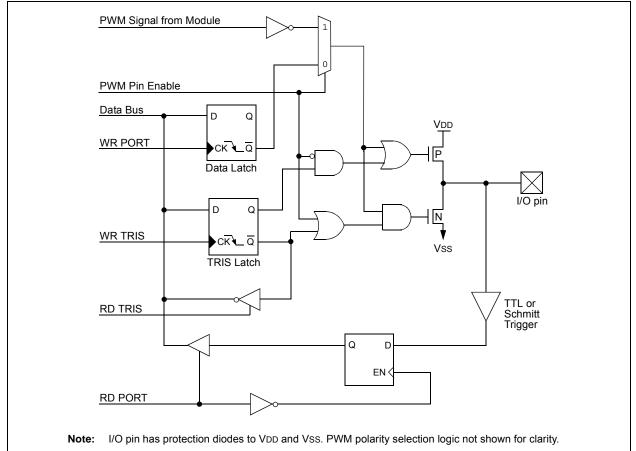

#### FIGURE 14-23: PWM I/O PIN BLOCK DIAGRAM

#### 14.11.3 PWM OUTPUT PIN RESET STATES

The PWMPIN Configuration bit determines the PWM output pins to be PWM output pins, or digital I/O pins, after the device comes out of Reset. If the PWMPIN Configuration bit is unprogrammed (default), the PWMEN2:PWMEN0 control bits will be cleared on a device Reset. Consequently, all PWM outputs will be tri-stated and controlled by the corresponding PORT and TRIS registers. If the PWMPIN Configuration bit is programmed low, the PWMEN2:PWMEN0 control bits will be set to '100' on a device Reset:

All PWM pins will be enabled for PWM output and will have the output polarity defined by the HPOL and LPOL Configuration bits.

#### 14.12 PWM Fault Input

There is one Fault input associated with the PWM module. The main purpose of the input Fault pin is to disable the PWM output signals and drive them into an inactive state. The action of the Fault input is performed

directly in hardware so that when a Fault occurs, it can be managed quickly and the PWMs outputs are put into an inactive state to save the power devices connected to the PWMs.

The PWM Fault input is  $\overline{FLTA}$ , which can come from I/O pins, the CPU or another module. The  $\overline{FLTA}$  pin is an active-low input so it is easy to "OR" many sources to the same input.

The FLTCONFIG register (Register 14-8) defines the settings of the FLTA input.

#### 14.12.1 FAULT PIN ENABLE BIT

By setting the bit FLTAEN in the FLTCONFIG register, the corresponding Fault input is enabled. If FLTAEN bit is cleared, then the Fault input has no effect on the PWM module.

# PIC18F1230/1330

NOTES:

| Bit 7                                         | Bit 6                                                           | Bit 5                                                                                          | Bit 4                                                                                                                                                          | Bit 3                                                                                                                                                                                                                  | Bit 2                                                                                                                                                               | Bit 1                                                                                                                                                                                                                            | Bit 0                                                                                                                                                                                                                                                                             | Reset<br>Values<br>on Page:                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GIE/GIEH                                      | PEIE/GIEL                                                       | TMR0IE                                                                                         | INT0IE                                                                                                                                                         | RBIE                                                                                                                                                                                                                   | TMR0IF                                                                                                                                                              | INT0IF                                                                                                                                                                                                                           | RBIF                                                                                                                                                                                                                                                                              | 47                                                                                                                                                                                                                                                                                                                       |

| _                                             | ADIF RCIF TXIF CMP2IF CMP1IF CMP0IF TMR1IF                      |                                                                                                |                                                                                                                                                                |                                                                                                                                                                                                                        |                                                                                                                                                                     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                          |

| _                                             | - ADIE RCIE TXIE CMP2IE CMP1IE CMP0IE TMR1IE                    |                                                                                                |                                                                                                                                                                |                                                                                                                                                                                                                        |                                                                                                                                                                     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                          |

| _                                             | - ADIP RCIP TXIP CMP2IP CMP1IP CMP0IP TMR1IP                    |                                                                                                |                                                                                                                                                                |                                                                                                                                                                                                                        |                                                                                                                                                                     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                   | 49                                                                                                                                                                                                                                                                                                                       |

| SPEN                                          | SPEN RX9 SREN CREN ADDEN FERR OERR RX9D                         |                                                                                                |                                                                                                                                                                |                                                                                                                                                                                                                        |                                                                                                                                                                     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                          |

| EUSART T                                      | EUSART Transmit Register                                        |                                                                                                |                                                                                                                                                                |                                                                                                                                                                                                                        |                                                                                                                                                                     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                   | 48                                                                                                                                                                                                                                                                                                                       |

| CSRC                                          | TX9                                                             | TXEN                                                                                           | SYNC                                                                                                                                                           | SENDB                                                                                                                                                                                                                  | BRGH                                                                                                                                                                | TRMT                                                                                                                                                                                                                             | TX9D                                                                                                                                                                                                                                                                              | 48                                                                                                                                                                                                                                                                                                                       |

| ABDOVF                                        | ABDOVF RCIDL RXDTP TXCKP BRG16 — WUE ABDEN                      |                                                                                                |                                                                                                                                                                |                                                                                                                                                                                                                        |                                                                                                                                                                     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                   | 48                                                                                                                                                                                                                                                                                                                       |

| EUSART Baud Rate Generator Register High Byte |                                                                 |                                                                                                |                                                                                                                                                                |                                                                                                                                                                                                                        |                                                                                                                                                                     | 48                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                          |

| EUSART B                                      | aud Rate G                                                      | enerator Re                                                                                    | gister Low                                                                                                                                                     | Byte                                                                                                                                                                                                                   |                                                                                                                                                                     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                   | 48                                                                                                                                                                                                                                                                                                                       |

|                                               | GIE/GIEH<br>—<br>SPEN<br>EUSART T<br>CSRC<br>ABDOVF<br>EUSART B | GIE/GIEHPEIE/GIEL—ADIF—ADIE—ADIPSPENRX9EUSART Transmit RegCSRCTX9ABDOVFRCIDLEUSART Baud Rate G | GIE/GIEHPEIE/GIELTMR0IE—ADIFRCIF—ADIERCIE—ADIPRCIPSPENRX9SRENEUSART Transmit RegisterCSRCTX9CSRCTX9TXENABDOVFRCIDLRXDTPEUSART Baud Rate Generator RegisterCSRC | GIE/GIEHPEIE/GIELTMR0IEINT0IEOIE/GIEHPEIE/GIELTMR0IEINT0IEOIEADIFRCIFTXIFOIEADIERCIPTXIPOIEADIPRCIPTXIPSPENRX9SRENCRENEUSART Transmit RegisterCRENSYNCABDOVFRCIDLRXDTPTXCKPEUSART Bud Rate Generator Register HighCREN | GIE/GIEHPEIE/GIELTMR0IEINT0IERBIEADIFRCIFTXIFCMP2IFADIERCIETXIECMP2IEADIPRCIPTXIPCMP2IPSPENRX9SRENCRENADDENEUSARTTansmit RejsterSYNCSENDBABDOVFRCIDLRXDTPTXCKPBRG16 | GIE/GIEHPEIE/GIELTMROIEINTOIERBIETMROIFADIFRCIFTXIFCMP2IFCMP1IFADIERCIETXIECMP2IECMP1IEADIPRCIPTXIPCMP2IPCMP1IPSPENRX9SRENCRENADDENFERREUSART Transmit RegisterSYNCSENDBBRGHABDOVFRCIDLRXDTPTXCKPBRG16EUSART BULRATESHARSHARSHAR | GIE/GIEHPEIE/GIELTMR0IEINT0IERBIETMR0IFINT0IFADIFRCIFTXIFCMP2IFCMP1IFCMP0IFADIERCIETXIECMP2IECMP1IECMP0IEADIPRCIPTXIPCMP2IPCMP1IPCMP0IPSPENRX9SRENCRENADDENFERROERREUSART Transmit RegisterSYNCSENDBBRGHTRMTABDOVFRCIDLRXDTPTXCKPBRG16WUEEUSART BUTSUBARTSUBARTSUBARTSUBARTSUBART | GIE/GIEHPEIE/GIELTMROIEINTOIERBIETMROIFINTOIFRBIFADIFRCIFTXIFCMP2IFCMP1IFCMP0IFTMR1IFADIERCIETXIECMP2IECMP1IECMP0IETMR1IFADIPRCIPTXIPCMP2IPCMP1IPCMP0IPTMR1IPSPENRX9SRENCRENADDENFERROERRRX9DEUSART Transmit RegisterSYNCSENDBBRGHTRMTTX9DABDOVFRCIDLRXDTPTXCKPBRG16WUEABDENEUSART But Rate Generator Register High Byte |

#### TABLE 15-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

**Legend:** — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

#### 18.2 Voltage Reference Accuracy/Error

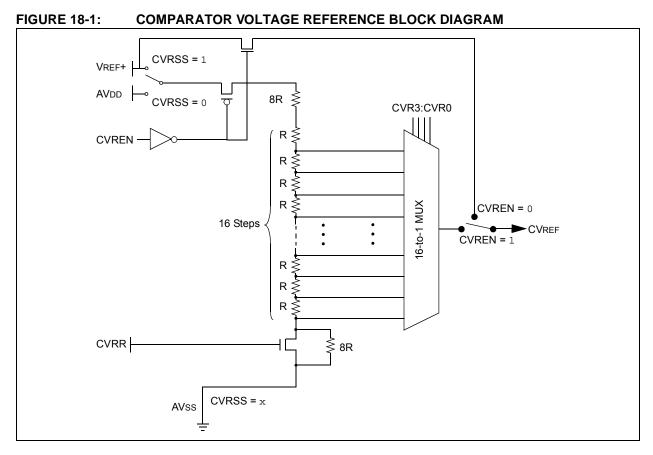

The full range of voltage reference cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 18-1) keep CVREF from approaching the reference source rails. The voltage reference is derived from the reference source; therefore, the CVREF output changes with fluctuations in that source. The tested absolute accuracy of the voltage reference can be found in **Section 23.0 "Electrical Characteristics"**.

# 18.3 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the CVRCON register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

#### 18.4 Effects of a Reset

A device Reset disables the voltage reference by clearing bit, CVREN (CVRCON<7>). This Reset selects the highvoltage range by clearing bit, CVRR (CVRCON<5>). The CVR value select bits are also cleared.

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset<br>Values<br>on Page: |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------------|

| CVRCON | CVREN | _     | CVRR  | CVRSS | CVR3  | CVR2  | CVR1  | CVR0  | 48                          |

| CMCON  | C2OUT | C10UT | COOUT | _     | -     | CMEN2 | CMEN1 | CMEN0 | 48                          |

#### TABLE 18-2: REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE

Legend: Shaded cells are not used with the comparator voltage reference.

#### 19.5 Applications

In many applications, the ability to detect a drop below a particular threshold is desirable.

For general battery applications, Figure 19-3 shows a possible voltage curve. Over time, the device voltage decreases. When the device voltage reaches voltage VA, the LVD logic generates an interrupt at time TA. The interrupt could cause the execution of an ISR, which would allow the application to perform "housekeeping tasks" and perform a controlled shutdown before the device voltage exits the valid operating range at TB. The LVD, thus, would give the application a time window, represented by the difference between TA and TB, to safely exit.

#

#### **19.6 Operation During Sleep**

When enabled, the LVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the LVDIF bit will be set and the device will wakeup from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

#### 19.7 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the LVD module to be turned off.

#### TABLE 19-1: REGISTERS ASSOCIATED WITH LOW-VOLTAGE DETECT MODULE

| Name   | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0 | Reset<br>Values<br>on Page: |

|--------|----------|-----------|--------|--------|-------|--------|--------|-------|-----------------------------|

| LVDCON | _        |           | IRVST  | LVDEN  | LVDL3 | LVDL2  | LVDL1  | LVDL0 | 48                          |

| INTCON | GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF  | 47                          |

| PIR2   | OSCFIF   | —         | —      | EEIF   | _     | LVDIF  | _      | —     | 49                          |

| PIE2   | OSCFIE   | —         | —      | EEIE   | _     | LVDIE  | _      | —     | 49                          |

| IPR2   | OSCFIP   | _         |        | EEIP   | _     | LVDIP  | _      | _     | 49                          |

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the LVD module.

# PIC18F1230/1330

# REGISTER 20-1: CONFIG1H: CONFIGURATION REGISTER 1 HIGH (BYTE ADDRESS 300001h)

| R/P-0        | R/P-0                                                                                                          | U-0                                                                                                                                            | U-0                                                                                                                        | R/P-0                                                                                     | R/P-1            | R/P-1    | R/P-1 |

|--------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------|----------|-------|

| IESO         | FCMEN                                                                                                          |                                                                                                                                                |                                                                                                                            | FOSC3                                                                                     | FOSC2            | FOSC1    | FOSC0 |

| bit 7        |                                                                                                                |                                                                                                                                                |                                                                                                                            |                                                                                           |                  |          | bit ( |

| Legend:      |                                                                                                                |                                                                                                                                                |                                                                                                                            |                                                                                           |                  |          |       |

| R = Readable | e bit                                                                                                          | P = Program                                                                                                                                    | nable bit                                                                                                                  | U = Unimplen                                                                              | nented bit, read | l as '0' |       |

|              | nen device is unp                                                                                              | •                                                                                                                                              |                                                                                                                            |                                                                                           | ed from program  |          |       |

|              |                                                                                                                | Jiogrammed                                                                                                                                     |                                                                                                                            | u Ononange                                                                                | sa nom program   |          |       |

| bit 7        | IESO: Interna                                                                                                  | I/External Osc                                                                                                                                 | illator Switcho                                                                                                            | ver bit                                                                                   |                  |          |       |

|              |                                                                                                                | Switchover me<br>Switchover me                                                                                                                 |                                                                                                                            |                                                                                           |                  |          |       |

| bit 6        | FCMEN: Fail-                                                                                                   | Safe Clock Mo                                                                                                                                  | nitor Enable b                                                                                                             | pit                                                                                       |                  |          |       |

|              |                                                                                                                | Clock Monitor<br>Clock Monitor                                                                                                                 |                                                                                                                            |                                                                                           |                  |          |       |

| bit 5-4      | Unimplemen                                                                                                     | ted: Read as '                                                                                                                                 | 0'                                                                                                                         |                                                                                           |                  |          |       |

| bit 3-0      | FOSC3:FOS                                                                                                      | <b>C0:</b> Oscillator S                                                                                                                        | Selection bits                                                                                                             |                                                                                           |                  |          |       |

|              | 101x = Exten<br>1001 = Intern<br>1000 = Intern<br>0111 = Exten<br>0110 = HS os<br>0101 = EC os<br>0100 = EC os | al oscillator blo<br>nal RC oscillat<br>scillator, PLL e<br>scillator, port fu<br>scillator, CLKO<br>nal RC oscillat<br>scillator<br>scillator | or, CLKO func-<br>ock, CLKO func-<br>ock, port function, port function<br>nabled (Clock<br>unction on RA6<br>function on R | ction on RA6<br>nction on RA6,<br>ion on RA6 and<br>on on RA6<br>Frequency = 4<br>o<br>A6 |                  | ו RA7    |       |

#### REGISTER 20-9: CONFIG6L: CONFIGURATION REGISTER 6 LOW (BYTE ADDRESS 30000Ah)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/C-1 | R/C-1 |

|-------|-----|-----|-----|-----|-----|-------|-------|

| —     | —   | —   | —   | —   | —   | WRT1  | WRT0  |

| bit 7 |     |     |     |     |     |       | bit 0 |

| Legend:                      |                   |                                     |

|------------------------------|-------------------|-------------------------------------|

| R = Readable bit             | C = Clearable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when device is un | programmed        | u = Unchanged from programmed state |

| bit 7-2 | Unimplemented: Read as '0'                                                                  |

|---------|---------------------------------------------------------------------------------------------|

| bit 1   | WRT1: Write Protection bit (Block 1 Code Memory Area)                                       |

|         | <ul><li>1 = Block 1 is not write-protected</li><li>0 = Block 1 is write-protected</li></ul> |

| bit 0   | WRT0: Write Protection bit (Block 0 Code Memory Area)                                       |

|         | <ul><li>1 = Block 0 is not write-protected</li><li>0 = Block 0 is write-protected</li></ul> |

#### REGISTER 20-10: CONFIG6H: CONFIGURATION REGISTER 6 HIGH (BYTE ADDRESS 30000Bh)

| R/C-1 | R/C-1 | R-1                 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|---------------------|-----|-----|-----|-----|-------|

| WRTD  | WRTB  | WRTC <sup>(1)</sup> | -   | —   | —   | —   | —     |

| bit 7 |       |                     |     |     |     |     | bit 0 |

| Legend:    |                                                |                                     |  |  |  |  |  |

|------------|------------------------------------------------|-------------------------------------|--|--|--|--|--|

| R = Read   | able bit C = Clearable bit                     | U = Unimplemented bit, read as '0'  |  |  |  |  |  |

| -n = Value | e when device is unprogrammed                  | u = Unchanged from programmed state |  |  |  |  |  |

|            |                                                |                                     |  |  |  |  |  |

| bit 7      | pit 7 WRTD: Write Protection bit (Data EEPROM) |                                     |  |  |  |  |  |

|            | 1 = Data EEPROM is not write-protect           | sted                                |  |  |  |  |  |

|            | 0 = Data EEPROM is write-protected             |                                     |  |  |  |  |  |

| bit 6 | WR | TB: | Write | e I | Prote | ctio | n bit ( | (Boo | t E | Block Memory Area) |

|-------|----|-----|-------|-----|-------|------|---------|------|-----|--------------------|

|       |    | -   |       |     |       |      |         |      |     |                    |

- 1 = Boot Block is not write-protected 0 = Boot Block is write-protected

- bit 5 WRTC: Write Protection bit (Configuration Registers)<sup>(1)</sup>

- 1 = Configuration registers are not write-protected

- 0 = Configuration registers are write-protected

- bit 4-0 Unimplemented: Read as '0'

Note 1: This bit is read-only in normal execution mode; it can be written only in Program mode.

#### 21.11 PICSTART Plus Development Programmer

The PICSTART Plus Development Programmer is an easy-to-use, low-cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus Development Programmer supports most PIC devices in DIP packages up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus Development Programmer is CE compliant.

#### 21.12 PICkit 2 Development Programmer

The PICkit<sup>™</sup> 2 Development Programmer is a low-cost programmer and selected Flash device debugger with an easy-to-use interface for programming many of Microchip's baseline, mid-range and PIC18F families of Flash memory microcontrollers. The PICkit 2 Starter Kit includes a prototyping development board, twelve sequential lessons, software and HI-TECH's PICC<sup>™</sup> Lite C compiler, and is designed to help get up to speed quickly using PIC<sup>®</sup> microcontrollers. The kit provides everything needed to program, evaluate and develop applications using Microchip's powerful, mid-range Flash memory family of microcontrollers.

### 21.13 Demonstration, Development and Evaluation Boards

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart<sup>®</sup> battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Check the Microchip web page (www.microchip.com) and the latest *"Product Selector Guide"* (DS00148) for the complete list of demonstration, development and evaluation kits.

# PIC18F1230/1330

| ADDWF                                                                                                                                                                                                                                 | ADD W to Indexed<br>(Indexed Literal Offset mode)                |                            |        |                         |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------|--------|-------------------------|--|--|--|--|--|

| Syntax:                                                                                                                                                                                                                               | ADDWF                                                            | [k] {,d}                   |        |                         |  |  |  |  |  |

| Operands:                                                                                                                                                                                                                             | $\begin{array}{l} 0 \leq k \leq 95 \\ d  \in  [0,1] \end{array}$ | $0 \le k \le 95$           |        |                         |  |  |  |  |  |

| Operation:                                                                                                                                                                                                                            | (W) + ((FSF                                                      | R2) + k) –                 | → dest |                         |  |  |  |  |  |

| Status Affected:                                                                                                                                                                                                                      | N, OV, C, D                                                      | C, Z                       |        |                         |  |  |  |  |  |

| Encoding:                                                                                                                                                                                                                             | 0010                                                             | 01d0                       | kkkk   | kkkk                    |  |  |  |  |  |

| Description:<br>The contents of W are added to the<br>contents of the register indicated by<br>FSR2, offset by the value 'k'.<br>If 'd' is '0', the result is stored in W. I<br>is '1', the result is stored back in<br>register 'f'. |                                                                  |                            |        |                         |  |  |  |  |  |

| Words:                                                                                                                                                                                                                                | 1                                                                |                            |        |                         |  |  |  |  |  |

| Cycles:                                                                                                                                                                                                                               | 1                                                                |                            |        |                         |  |  |  |  |  |

| Q Cycle Activity:                                                                                                                                                                                                                     |                                                                  |                            |        |                         |  |  |  |  |  |

| Q1                                                                                                                                                                                                                                    | Q2                                                               | Q3                         |        | Q4                      |  |  |  |  |  |

| Decode                                                                                                                                                                                                                                | Read 'k'                                                         | Proce<br>Data              |        | Write to<br>destination |  |  |  |  |  |

| Example:                                                                                                                                                                                                                              | ADDWF                                                            | [OFST],                    | , 0    |                         |  |  |  |  |  |

| Before Instructi                                                                                                                                                                                                                      | on                                                               |                            |        |                         |  |  |  |  |  |

| W<br>OFST<br>FSR2<br>Contents<br>of 0A2Ch<br>After Instructior                                                                                                                                                                        | =<br>=<br>=<br>=                                                 | 17h<br>2Ch<br>0A00h<br>20h |        |                         |  |  |  |  |  |

| W<br>Contents<br>of 0A2Ch                                                                                                                                                                                                             | =                                                                | 37h<br>20h                 |        |                         |  |  |  |  |  |