Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 4x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f1230-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                                           | Pi            | Pin Number |                                      |             | Buffer |                                            |  |  |

|---------------------------------------------------------------------------|---------------|------------|--------------------------------------|-------------|--------|--------------------------------------------|--|--|

| Pin Name                                                                  | PDIP,<br>SOIC | SSOP       | QFN                                  | Pin<br>Type | Туре   | Description                                |  |  |

| Vss                                                                       | 5             | 5          | 3                                    | Р           |        | Ground reference for logic and I/O pins.   |  |  |

| Vdd                                                                       | 14            | 16         | 19                                   | Р           | _      | Positive supply for logic and I/O pins.    |  |  |

| AVss                                                                      | 5             | 6          | 5                                    | Р           | _      | Ground reference for A/D Converter module. |  |  |

| AVdd                                                                      | 14            | 15         | 17                                   | Р           | —      | Positive supply for A/D Converter module.  |  |  |

| NC                                                                        | _             | _          | 2, 4, 6,<br>11, 14,<br>18, 22,<br>25 | _           | _      | No Connect.                                |  |  |

| Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output |               |            |                                      |             |        |                                            |  |  |

## TABLE 1-2:PIC18F1230/1330 PINOUT I/O DESCRIPTIONS (CONTINUED)

ST = Schmitt Trigger input with CMOS levels

I = Input P = Power

O = Output

**Note 1:** Placement of FLTA depends on the value of Configuration bit, FLTAMX, of CONFIG3H.

2: Placement of T1OSI and T1OSO/T1CKI depends on the value of Configuration bit, T1OSCMX, of CONFIG3H.

| File Name | Bit 7                                                                                                   | Bit 6                                                                                                                              | Bit 5          | Bit 4         | Bit 3          | Bit 2         | Bit 1            | Bit 0       | Value on<br>POR, BOR | Details<br>on<br>Page: |

|-----------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------|----------------|---------------|------------------|-------------|----------------------|------------------------|

| TOSU      | —                                                                                                       | —                                                                                                                                  | —              | Top-of-Stack  | Upper Byte (T  | OS<20:16>)    |                  |             | 0 0000               | 47, 52                 |

| TOSH      | Top-of-Stack                                                                                            | High Byte (TC                                                                                                                      | S<15:8>)       |               |                |               |                  |             | 0000 0000            | 47, 52                 |

| TOSL      | Top-of-Stack                                                                                            | Low Byte (TO                                                                                                                       | S<7:0>)        |               |                |               |                  |             | 0000 0000            | 47, 52                 |

| STKPTR    | STKFUL <sup>(5)</sup>                                                                                   | STKUNF <sup>(5)</sup>                                                                                                              | _              | SP4           | SP0            | 00-0 0000     | 47, 53           |             |                      |                        |

| PCLATU    | _                                                                                                       | _                                                                                                                                  | _              | Holding Regi  | ster for PC<20 | :16>          |                  |             | 0 0000               | 47, 52                 |

| PCLATH    | Holding Regi                                                                                            | ster for PC<15                                                                                                                     | :8>            |               |                |               |                  |             | 0000 0000            | 47, 52                 |

| PCL       | PC Low Byte                                                                                             | (PC<7:0>)                                                                                                                          |                |               |                |               |                  |             | 0000 0000            | 47, 52                 |

| TBLPTRU   | —                                                                                                       | —                                                                                                                                  | bit 21         | Program Mer   | nory Table Poi | nter Upper By | te (TBLPTR<20    | D:16>)      | 00 0000              | 47, 74                 |

| TBLPTRH   | Program Mer                                                                                             | Program Memory Table Pointer High Byte (TBLPTR<15:8>)                                                                              |                |               |                |               |                  |             |                      | 47, 74                 |

| TBLPTRL   | Program Mer                                                                                             | nory Table Poi                                                                                                                     | nter Low Byte  | e (TBLPTR<7:0 | )>)            |               |                  |             | 0000 0000            | 47, 74                 |

| TABLAT    | Program Mer                                                                                             | nory Table Lat                                                                                                                     | ch             |               |                |               |                  |             | 0000 0000            | 47, 74                 |

| PRODH     | Product Regi                                                                                            | ster High Byte                                                                                                                     |                |               |                |               |                  |             | xxxx xxxx            | 47, 85                 |

| PRODL     | Product Regi                                                                                            | Product Register Low Byte                                                                                                          |                |               |                |               |                  |             | xxxx xxxx            | 47, 85                 |

| INTCON    | GIE/GIEH                                                                                                | PEIE/GIEL                                                                                                                          | TMR0IE         | <b>INT0IE</b> | RBIE           | TMR0IF        | <b>INT0IF</b>    | RBIF        | x000 0000x           | 47, 95                 |

| INTCON2   | RBPU                                                                                                    | INTEDG0                                                                                                                            | INTEDG1        | INTEDG2       | INTEDG3        | TMR0IP        | INT3IP           | RBIP        | 1111 1111            | 47, 96                 |

| INTCON3   | INT2IP                                                                                                  | INT1IP                                                                                                                             | INT3IE         | INT2IE        | INT1IE         | INT3IF        | INT2IF           | INT1IF      | 1100 0000            | 47, 97                 |

| INDF0     | Uses content                                                                                            | Uses contents of FSR0 to address data memory – value of FSR0 not changed (not a physical register)                                 |                |               |                |               |                  |             |                      | 47, 66                 |

| POSTINC0  | Uses contents of FSR0 to address data memory – value of FSR0 post-incremented (not a physical register) |                                                                                                                                    |                |               |                |               |                  | register)   | N/A                  | 47, 66                 |

| POSTDEC0  | Uses content                                                                                            | Uses contents of FSR0 to address data memory – value of FSR0 post-decremented (not a physical register)                            |                |               |                |               |                  |             | N/A                  | 47, 66                 |

| PREINC0   | Uses contents of FSR0 to address data memory – value of FSR0 pre-incremented (not a physical register)  |                                                                                                                                    |                |               |                |               |                  | register)   | N/A                  | 47, 66                 |

| PLUSW0    |                                                                                                         | Uses contents of FSR0 to address data memory – value of FSR0 pre-incremented (not a physical register) – value of FSR0 offset by W |                |               |                |               |                  |             | N/A                  | 47, 66                 |

| FSR0H     | —                                                                                                       | —                                                                                                                                  |                | _             | Indirect Data  | Memory Addre  | ess Pointer 0 H  | igh Byte    | 0000                 | 47, 66                 |

| FSR0L     | Indirect Data                                                                                           | Memory Addr                                                                                                                        | ess Pointer 0  | Low Byte      |                |               |                  |             | xxxx xxxx            | 47, 66                 |

| WREG      | Working Reg                                                                                             | ister                                                                                                                              |                |               |                |               |                  |             | xxxx xxxx            | 47, 54                 |

| INDF1     | Uses content                                                                                            | s of FSR1 to a                                                                                                                     | iddress data n | nemory – valu | e of FSR1 not  | changed (not  | a physical regis | ster)       | N/A                  | 47, 66                 |

| POSTINC1  | Uses content                                                                                            | s of FSR1 to a                                                                                                                     | iddress data n | nemory – valu | e of FSR1 pos  | t-incremented | (not a physical  | register)   | N/A                  | 47, 66                 |

| POSTDEC1  | Uses content                                                                                            | s of FSR1 to a                                                                                                                     | iddress data n | nemory – valu | e of FSR1 pos  | t-decremented | l (not a physica | l register) | N/A                  | 47, 66                 |

| PREINC1   | Uses content                                                                                            | s of FSR1 to a                                                                                                                     | iddress data n | nemory – valu | e of FSR1 pre- | incremented ( | not a physical r | register)   | N/A                  | 47, 66                 |

| PLUSW1    | Uses content<br>value of FSR                                                                            |                                                                                                                                    | iddress data n | nemory – valu | e of FSR1 pre- | incremented ( | not a physical r | register) – | N/A                  | 47, 66                 |

| FSR1H     | —                                                                                                       | —                                                                                                                                  | —              | —             | Indirect Data  | Memory Addre  | ess Pointer 1 H  | igh Byte    | 0000                 | 47, 66                 |

| FSR1L     | Indirect Data                                                                                           | Memory Addr                                                                                                                        | ess Pointer 1  | Low Byte      |                |               |                  |             | xxxx xxxx            | 47, 66                 |

| BSR       | _                                                                                                       | _                                                                                                                                  | _              | _             | Bank Select F  | Register      |                  |             | 0000                 | 47, 57                 |

| INDF2     | Uses content                                                                                            | s of FSR2 to a                                                                                                                     | iddress data n | nemory – valu | e of FSR2 not  | changed (not  | a physical regis | ster)       | N/A                  | 48, 66                 |

| POSTINC2  | Uses content                                                                                            | s of FSR2 to a                                                                                                                     | iddress data n | nemory – valu | e of FSR2 pos  | -incremented  | (not a physical  | register)   | N/A                  | 48, 66                 |

| POSTDEC2  | Uses content                                                                                            | s of FSR2 to a                                                                                                                     | iddress data n | nemory – valu | e of FSR2 pos  | t-decremented | l (not a physica | l register) | N/A                  | 48, 66                 |

| PREINC2   | Uses content                                                                                            | s of FSR2 to a                                                                                                                     | iddress data n | nemory – valu | e of FSR2 pre- | incremented ( | not a physical r | egister)    | N/A                  | 48, 66                 |

| PLUSW2    | Uses content value of FSR                                                                               |                                                                                                                                    | iddress data n | nemory – valu | e of FSR2 pre- | incremented ( | not a physical r | register) – | N/A                  | 48, 66                 |

| FSR2H     | _                                                                                                       | —                                                                                                                                  | _              | _             | Indirect Data  | Memory Addr   | ess Pointer 2 H  | igh Byte    | 0000                 | 48, 66                 |

| FSR2L     | Indirect Data Memory Address Pointer 2 Low Byte                                                         |                                                                                                                                    |                |               |                |               |                  |             | xxxx xxxx            | 48, 66                 |

**TABLE 6-2: REGISTER FILE SUMMARY (PIC18F1230/1330)**

Note 1: The SBOREN bit is only available when the BOREN1:BOREN0 Configuration bits = 01; otherwise, it is disabled and reads as '0'. See Section 5.4 "Brown-out Reset (BOR)".

2: The PLLEN bit is only available in specific oscillator configurations; otherwise, it is disabled and reads as '0'. See Section 3.6.4 "PLL in INTOSC Modes".

The RA5 bit is only available when Master Clear Reset is disabled (MCLRE Configuration bit = 0); otherwise, RA5 reads as 3: '0'. This bit is read-only.

4: RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

5: Bit 7 and bit 6 are cleared by user software or by a POR.

6: Reset condition of PWMEN bits depends on the PWMPIN Configuration bit of CONFIG3L.

7: This bit has no effect if the Configuration bit, WDTEN, is enabled.

# PIC18F1230/1330

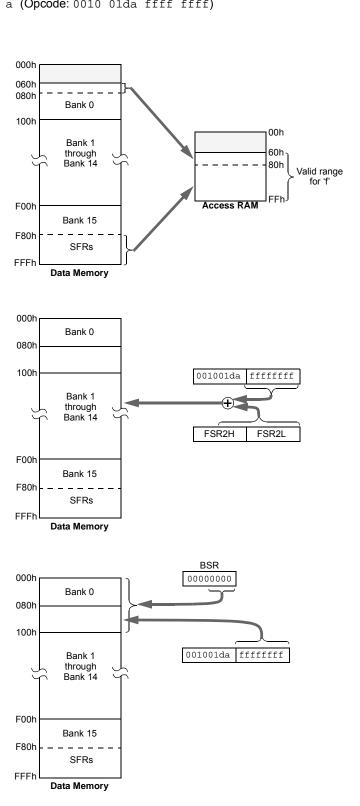

#### FIGURE 6-8: COMPARING ADDRESSING OPTIONS FOR BIT-ORIENTED AND BYTE-ORIENTED INSTRUCTIONS (EXTENDED INSTRUCTION SET ENABLED)

**EXAMPLE INSTRUCTION:** ADDWF, f, d, a (Opcode: 0010 01da ffff ffff)

#### When 'a' = 0 and $f \ge 60h$ :

The instruction executes in Direct Forced mode. 'f' is interpreted as a location in the Access RAM between 060h and 0FFh. This is the same as locations 060h to 07Fh (Bank 0) and F80h to FFFh (Bank 15) of data memory.

Locations below 60h are not available in this addressing mode.

#### When 'a' = 0 and $f \le 5Fh$ :

The instruction executes in Indexed Literal Offset mode. 'f' is interpreted as an offset to the address value in FSR2. The two are added together to obtain the address of the target register for the instruction. The address can be anywhere in the data memory space.

Note that in this mode, the correct syntax is now: ADDWF [k], d where 'k' is the same as 'f'.

#### When 'a' = 1 (all values of f):

The instruction executes in Direct mode (also known as Direct Long mode). 'f' is interpreted as a location in one of the 16 banks of the data memory space. The bank is designated by the Bank Select Register (BSR). The address can be in any implemented bank in the data memory space.

| REGISTER 7-1: | EECON1: EEPROM CONTROL REGISTER 1 |

|---------------|-----------------------------------|

|---------------|-----------------------------------|

| R/W-x | R/W-x | U-0 | R/W-0 | R/W-x                | R/W-0 | R/S-0 | R/S-0 |

|-------|-------|-----|-------|----------------------|-------|-------|-------|

| EEPGD | CFGS  | —   | FREE  | WRERR <sup>(1)</sup> | WREN  | WR    | RD    |

| bit 7 |       |     |       |                      |       |       | bit 0 |

| Legend:           | S = Settable bit |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7 | EEPGD: Flash Program or Data EEPROM Memory Select bit                                                                                                                                                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = Access Flash program memory                                                                                                                                                                                                                                          |

|       | 0 = Access data EEPROM memory                                                                                                                                                                                                                                            |

| bit 6 | CFGS: Flash Program/Data EEPROM or Configuration Select bit                                                                                                                                                                                                              |

|       | 1 = Access Configuration registers                                                                                                                                                                                                                                       |

|       | 0 = Access Flash program or data EEPROM memory                                                                                                                                                                                                                           |

| bit 5 | Unimplemented: Read as '0'                                                                                                                                                                                                                                               |

| bit 4 | FREE: Flash Row Erase Enable bit                                                                                                                                                                                                                                         |

|       | <ul> <li>1 = Erase the program memory row addressed by TBLPTR on the next WR command<br/>(cleared by completion of erase operation)</li> </ul>                                                                                                                           |

|       | 0 = Perform write-only                                                                                                                                                                                                                                                   |

| bit 3 | WRERR: Flash Program/Data EEPROM Error Flag bit <sup>(1)</sup>                                                                                                                                                                                                           |

|       | <ul> <li>1 = A write operation is prematurely terminated (any Reset during self-timed programming in normal<br/>operation, or an improper write attempt)</li> </ul>                                                                                                      |

|       | 0 = The write operation completed                                                                                                                                                                                                                                        |

| bit 2 | WREN: Flash Program/Data EEPROM Write Enable bit                                                                                                                                                                                                                         |

|       | 1 = Allows write cycles to Flash program/data EEPROM                                                                                                                                                                                                                     |

|       | 0 = Inhibits write cycles to Flash program/data EEPROM                                                                                                                                                                                                                   |

| bit 1 | WR: Write Control bit                                                                                                                                                                                                                                                    |

|       | <ul> <li>1 = Initiates a data EEPROM erase/write cycle or a program memory erase cycle or write cycle.<br/>(The operation is self-timed and the bit is cleared by hardware once write is complete.<br/>The WR bit can only be set (not cleared) in software.)</li> </ul> |

|       | 0 = Write cycle to the EEPROM is complete                                                                                                                                                                                                                                |

| bit 0 | RD: Read Control bit                                                                                                                                                                                                                                                     |

|       | <ul> <li>1 = Initiates an EEPROM read. (Read takes one cycle. RD is cleared in hardware. The RD bit can only<br/>be set (not cleared) in software. RD bit cannot be set when EEPGD = 1 or CFGS = 1.)</li> </ul>                                                          |

|       | 0 = Does not initiate an EEPROM read                                                                                                                                                                                                                                     |

|       | (hap a WRERR assure the EERCR and CECS hits are not cleared. This allows tracing of the array                                                                                                                                                                            |

**Note 1:** When a WRERR occurs, the EEPGD and CFGS bits are not cleared. This allows tracing of the error condition.

## 7.2.2 TABLAT – TABLE LATCH REGISTER

The Table Latch (TABLAT) is an 8-bit register mapped into the SFR space. The Table Latch register is used to hold 8-bit data during data transfers between program memory and data RAM.

#### 7.2.3 TBLPTR – TABLE POINTER REGISTER

The Table Pointer (TBLPTR) register addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL). These three registers join to form a 22-bit wide pointer. The low-order 21 bits allow the device to address up to 2 Mbytes of program memory space. The 22nd bit allows access to the device ID, the user ID and the Configuration bits.

The Table Pointer register, TBLPTR, is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways based on the table operation. These operations are shown in Table 7-1. These operations on the TBLPTR only affect the low-order 21 bits.

### 7.2.4 TABLE POINTER BOUNDARIES

TBLPTR is used in reads, writes and erases of the Flash program memory.

When a TBLRD is executed, all 22 bits of the TBLPTR determine which byte is read from program memory into TABLAT.

When the timed write to program memory begins (via the WR bit), the 19 MSbs of the TBLPTR (TBLPTR<21:3>) determine which program memory block of 8 bytes is written to. The Table Pointer register's three LSBs (TBLPTR<2:0>) are ignored. For more detail, see Section 7.5 "Writing to Flash Program Memory".

When an erase of program memory is executed, the 16 MSbs of the Table Pointer register (TBLPTR<21:6>) point to the 64-byte block that will be erased. The Least Significant bits (TBLPTR<5:0>) are ignored.

Figure 7-3 describes the relevant boundaries of TBLPTR based on Flash program memory operations.

| TABLE 7-1: | TABLE POINTER OPERATIONS WITH TBLRD AND TBLWT INSTRUCTIONS |

|------------|------------------------------------------------------------|

|------------|------------------------------------------------------------|

| Example            | Operation on Table Pointer                  |  |  |  |  |  |  |

|--------------------|---------------------------------------------|--|--|--|--|--|--|

| TBLRD*<br>TBLWT*   | TBLPTR is not modified                      |  |  |  |  |  |  |

| TBLRD*+<br>TBLWT*+ | TBLPTR is incremented after the read/write  |  |  |  |  |  |  |

| TBLRD*-<br>TBLWT*- | TBLPTR is decremented after the read/write  |  |  |  |  |  |  |

| TBLRD+*<br>TBLWT+* | TBLPTR is incremented before the read/write |  |  |  |  |  |  |

#### FIGURE 7-3: TABLE POINTER BOUNDARIES BASED ON OPERATION

| R/W-      | 1 R/W-1                                       | R/W-0                                                                                                                                             | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0           |  |  |  |  |  |

|-----------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|------------------|-----------------|-----------------|--|--|--|--|--|

| INT2I     | P INT1IP                                      | INT3IE                                                                                                                                            | INT2IE           | INT1IE           | INT3IF           | INT2IF          | INT1IF          |  |  |  |  |  |

| bit 7     |                                               |                                                                                                                                                   |                  |                  |                  | ·               | bit (           |  |  |  |  |  |

|           |                                               |                                                                                                                                                   |                  |                  |                  |                 |                 |  |  |  |  |  |

| Legend:   |                                               |                                                                                                                                                   |                  |                  |                  |                 |                 |  |  |  |  |  |

| R = Read  |                                               | W = Writable                                                                                                                                      |                  |                  | mented bit, read |                 |                 |  |  |  |  |  |

| -n = Valu | e at POR                                      | '1' = Bit is set                                                                                                                                  |                  | '0' = Bit is cle | eared            | x = Bit is unkr | nown            |  |  |  |  |  |

| bit 7     | INT2IP: INT                                   | 2 External Interr                                                                                                                                 | upt Priority bi  | t                |                  |                 |                 |  |  |  |  |  |

|           | 1 = High pri                                  |                                                                                                                                                   |                  |                  |                  |                 |                 |  |  |  |  |  |

|           | 0 = Low prie                                  | ority                                                                                                                                             |                  |                  |                  |                 |                 |  |  |  |  |  |

| bit 6     | INT1IP: INT                                   | 1 External Interr                                                                                                                                 | upt Priority bi  | t                |                  |                 |                 |  |  |  |  |  |

|           | 1 = High pri                                  |                                                                                                                                                   |                  |                  |                  |                 |                 |  |  |  |  |  |

|           | 0 = Low prie                                  | •                                                                                                                                                 |                  |                  |                  |                 |                 |  |  |  |  |  |

| bit 5     |                                               | INT3IE: INT3 External Interrupt Enable bit                                                                                                        |                  |                  |                  |                 |                 |  |  |  |  |  |

|           |                                               | <ul> <li>1 = Enables the INT3 external interrupt</li> <li>0 = Disables the INT3 external interrupt</li> </ul>                                     |                  |                  |                  |                 |                 |  |  |  |  |  |

| bit 4     |                                               | INT2IE: INT2 External Interrupt Enable bit                                                                                                        |                  |                  |                  |                 |                 |  |  |  |  |  |

|           |                                               | 1 = Enables the INT2 external interrupt                                                                                                           |                  |                  |                  |                 |                 |  |  |  |  |  |

|           | 0 = Disable                                   | 0 = Disables the INT2 external interrupt                                                                                                          |                  |                  |                  |                 |                 |  |  |  |  |  |

| bit 3     |                                               | 1 External Interr                                                                                                                                 | •                | t                |                  |                 |                 |  |  |  |  |  |

|           |                                               | <ul> <li>1 = Enables the INT1 external interrupt</li> <li>0 = Disables the INT1 external interrupt</li> </ul>                                     |                  |                  |                  |                 |                 |  |  |  |  |  |

| bit 2     |                                               | 3 External Interr                                                                                                                                 | •                |                  |                  |                 |                 |  |  |  |  |  |

| DIL Z     |                                               | 3 external inter                                                                                                                                  |                  | (must be clear   | ed in software)  |                 |                 |  |  |  |  |  |

|           |                                               | 3 external inter                                                                                                                                  |                  |                  | cu in soltware)  |                 |                 |  |  |  |  |  |

| bit 1     | INT2IF: INT                                   | 2 External Interr                                                                                                                                 | upt Flag bit     |                  |                  |                 |                 |  |  |  |  |  |

|           |                                               | 1 = The INT2 external interrupt occurred (must be cleared in software)                                                                            |                  |                  |                  |                 |                 |  |  |  |  |  |

|           | 0 = The INT2 external interrupt did not occur |                                                                                                                                                   |                  |                  |                  |                 |                 |  |  |  |  |  |

| bit 0     | INT1IF: INT1 External Interrupt Flag bit      |                                                                                                                                                   |                  |                  |                  |                 |                 |  |  |  |  |  |

|           |                                               | <ul> <li>1 = The INT1 external interrupt occurred (must be cleared in software)</li> <li>0 = The INT1 external interrupt did not occur</li> </ul> |                  |                  |                  |                 |                 |  |  |  |  |  |

|           |                                               |                                                                                                                                                   | מאר מום חטר טר   | JUUI             |                  |                 |                 |  |  |  |  |  |

| Note:     | Interrupt flag bits                           |                                                                                                                                                   |                  |                  |                  |                 |                 |  |  |  |  |  |

|           | enable bit or the                             |                                                                                                                                                   |                  |                  |                  |                 | errupt flag bit |  |  |  |  |  |

|           | are clear prior to                            | enabling an inte                                                                                                                                  | errupt. This fea | ature allows for | sonware pollir   | ıg.             |                 |  |  |  |  |  |

#### REGISTER 11-3: INTCON3: INTERRUPT CONTROL REGISTER 3

| R/W-0                                                                      | U-0                                                                                                | U-0                                   | R/W-0 | U-0 | R/W-0 | U-0 | U-0   |  |  |

|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------|-------|-----|-------|-----|-------|--|--|

| OSCFIE                                                                     |                                                                                                    | —                                     | EEIE  | —   | LVDIE | —   |       |  |  |

| bit 7                                                                      |                                                                                                    |                                       |       |     |       |     | bit 0 |  |  |

|                                                                            |                                                                                                    |                                       |       |     |       |     |       |  |  |

| Legend:                                                                    |                                                                                                    |                                       |       |     |       |     |       |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'       |                                                                                                    |                                       |       |     |       |     |       |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                                                                                                    |                                       |       |     |       |     |       |  |  |

| bit 7<br>bit 6-5                                                           | 1 = Enabled<br>0 = Disabled                                                                        | illator Fail Inter<br>ted: Read as '0 | ·     |     |       |     |       |  |  |

| bit 4                                                                      | <b>EEIE:</b> Data EEPROM/Flash Write Operation Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled |                                       |       |     |       |     |       |  |  |

| bit 3                                                                      | Unimplement                                                                                        | ted: Read as 'd                       | )'    |     |       |     |       |  |  |

| bit 2                                                                      | LVDIE: Low-Voltage Detect Interrupt Enable bit                                                     |                                       |       |     |       |     |       |  |  |

|                                                                            | 1 = Enabled<br>0 = Disabled                                                                        |                                       |       |     |       |     |       |  |  |

| bit 1-0                                                                    | Unimplement                                                                                        | ted: Read as 'd                       | )'    |     |       |     |       |  |  |

#### REGISTER 11-9: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

| U-0   | U-0 | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-------|-----|-----|-----|-------|

| —     | —   | —   | PTIE  | —   | —   | —   | —     |

| bit 7 |     |     |       |     |     |     | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

- bit 7-5 Unimplemented: Read as '0'

- bit 4 PTIE: PWM Time Base Interrupt Enable bit

- 1 = PWM enabled

- 0 = PWM disabled

- bit 3-0 Unimplemented: Read as '0'

## 11.5 RCON Register

Γ.

The RCON register contains flag bits which are used to determine the cause of the last Reset or wake-up from Idle or Sleep modes. RCON also contains the IPEN bit which enables interrupt priorities.

The operation of the SBOREN bit and the Reset flag bits is discussed in more detail in **Section 5.1 "RCON Register"**.

### REGISTER 11-13: RCON: RESET CONTROL REGISTER

| R/W-0 | R/W-1 <sup>(1)</sup> | U-0 | R/W-1 | R-1 | R-1 | R/W-0 <sup>(2)</sup> | R/W-0 |

|-------|----------------------|-----|-------|-----|-----|----------------------|-------|

| IPEN  | SBOREN               | _   | RI    | TO  | PD  | POR                  | BOR   |

| bit 7 |                      |     |       |     |     |                      | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | <b>IPEN:</b> Interrupt Priority Enable bit<br>1 = Enable priority levels on interrupts<br>0 = Disable priority levels on interrupts (PIC16CXXX Compatibility mode) |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | <b>SBOREN:</b> BOR Software Enable bit <sup>(1)</sup>                                                                                                              |

|       | For details of bit operation, see Register 5-1.                                                                                                                    |

| bit 5 | Unimplemented: Read as '0'                                                                                                                                         |

| bit 4 | RI: RESET Instruction Flag bit                                                                                                                                     |

|       | For details of bit operation, see Register 5-1.                                                                                                                    |

| bit 3 | TO: Watchdog Time-out Flag bit                                                                                                                                     |

|       | For details of bit operation, see Register 5-1.                                                                                                                    |

| bit 2 | PD: Power-Down Detection Flag bit                                                                                                                                  |

|       | For details of bit operation, see Register 5-1.                                                                                                                    |

| bit 1 | <b>POR:</b> Power-on Reset Status bit <sup>(2)</sup>                                                                                                               |

|       | For details of bit operation, see Register 5-1.                                                                                                                    |

| bit 0 | BOR: Brown-out Reset Status bit                                                                                                                                    |

|       | For details of bit operation, see Register 5-1.                                                                                                                    |

|       |                                                                                                                                                                    |

- Note 1: If SBOREN is enabled, its Reset state is '1'; otherwise, it is '0'. See Register 5-1 for additional information.

- 2: The actual Reset value of POR is determined by the type of device Reset. See Register 5-1 for additional information.

# 13.0 TIMER1 MODULE

The Timer1 timer/counter module has the following features:

- 16-bit timer/counter (two 8-bit registers; TMR1H and TMR1L)

- Readable and writable (both registers)

- · Internal or external clock select

- Interrupt on overflow from FFFFh to 0000h

- · Status of system clock operation

Figure 13-1 is a simplified block diagram of the Timer1 module.

Register 13-1 details the Timer1 Control register. This register controls the operating mode of the Timer1 module and contains the Timer1 Oscillator Enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

The Timer1 oscillator can be used as a secondary clock source in power-managed modes. When the T1RUN bit is set, the Timer1 oscillator provides the system clock. If the Fail-Safe Clock Monitor is enabled and the Timer1 oscillator fails while providing the system clock, polling the T1RUN bit will indicate whether the clock is being provided by the Timer1 oscillator or another source.

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

### REGISTER 13-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0 | R-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|---------|---------|---------|--------|--------|--------|

| RD16  | T1RUN | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |       |         |         |         |        |        | bit 0  |

| Legend:      |                |                                                                |                                                 |                               |  |  |  |  |  |

|--------------|----------------|----------------------------------------------------------------|-------------------------------------------------|-------------------------------|--|--|--|--|--|

| R = Readab   | le bit         | W = Writable bit                                               | U = Unimplemented bit,                          | read as '0'                   |  |  |  |  |  |

| -n = Value a | t POR          | '1' = Bit is set                                               | '0' = Bit is cleared                            | x = Bit is unknown            |  |  |  |  |  |

| bit 7        | <b>RD16:</b> 1 | 6-Bit Read/Write Mode Enabl                                    | le bit                                          |                               |  |  |  |  |  |

|              | 1 = Ena        | bles register read/write of Tin                                | ner1 in one 16-bit operation                    |                               |  |  |  |  |  |

|              | 0 = Ena        | bles register read/write of Tin                                | ner1 in two 8-bit operations                    |                               |  |  |  |  |  |

| bit 6        | T1RUN:         | Timer1 System Clock Status                                     | bit                                             |                               |  |  |  |  |  |

|              |                | rice clock is derived from Time                                |                                                 |                               |  |  |  |  |  |

|              |                | rice clock is derived from anot                                |                                                 |                               |  |  |  |  |  |

| bit 5-4      |                | S1:T1CKPS0: Timer1 Input C                                     | lock Prescale Select bits                       |                               |  |  |  |  |  |

|              |                | 11 = 1:8 Prescale value                                        |                                                 |                               |  |  |  |  |  |

|              |                | 10 = 1:4 Prescale value<br>01 = 1:2 Prescale value             |                                                 |                               |  |  |  |  |  |

|              |                | Prescale value                                                 |                                                 |                               |  |  |  |  |  |

| bit 3        | T1OSCE         | T1OSCEN: Timer1 Oscillator Enable bit                          |                                                 |                               |  |  |  |  |  |

|              | 1 = Time       | 1 = Timer1 oscillator is enabled                               |                                                 |                               |  |  |  |  |  |

|              |                | er1 oscillator is shut off                                     |                                                 |                               |  |  |  |  |  |

|              |                | -                                                              | esistor are turned off to elimin                | ate power drain.              |  |  |  |  |  |

| bit 2        |                | : Timer1 External Clock Inpu                                   | t Synchronization Select bit                    |                               |  |  |  |  |  |

|              | -              | $\frac{MR1CS = 1}{2}$                                          | - inn4                                          |                               |  |  |  |  |  |

|              |                | ot synchronize external clock<br>chronize external clock input | input                                           |                               |  |  |  |  |  |

|              |                | When $TMR1CS = 0$ :                                            |                                                 |                               |  |  |  |  |  |

|              | This bit i     | s ignored. Timer1 uses the in                                  | ternal clock when TMR1CS =                      | 0.                            |  |  |  |  |  |

| bit 1        | TMR1CS         | S: Timer1 Clock Source Select                                  | ct bit                                          |                               |  |  |  |  |  |

|              | 1 = Exte       | ernal clock from T1OSO/T1Cl                                    | <i (on="" edge)<sup="" rising="" the="">(1)</i> |                               |  |  |  |  |  |

|              | 0 = Inte       | rnal clock (Fosc/4)                                            |                                                 |                               |  |  |  |  |  |

| bit 0        | TMR10          | N: Timer1 On bit                                               |                                                 |                               |  |  |  |  |  |

|              |                | ıbles Timer1<br>os Timer1                                      |                                                 |                               |  |  |  |  |  |

| Note 1. Pla  | coment of T1   | OSI and T1OSO/T1CKI depen                                      | ids on the value of the Configur                | ation bit. T1OSCMX. of CONFIG |  |  |  |  |  |

Note 1: Placement of T1OSI and T1OSO/T1CKI depends on the value of the Configuration bit, T1OSCMX, of CONFIG3H.

# 14.5 PWM Period

The PWM period is defined by the PTPER register pair (PTPERL and PTPERH). The PWM period has 12-bit resolution by combining 4 LSBs of PTPERH and 8 bits of PTPERL. PTPER is a double-buffered register used to set the counting period for the PWM time base.

The PTPER buffer contents are loaded into the PTPER register at the following times:

- Free-Running and Single-Shot modes: When the PTMR register is reset to zero after a match with the PTPER register.

- Continuous Up/Down Count modes: When the PTMR register is zero. The value held in the PTPER buffer is automatically loaded into the PTPER register when the PWM time base is disabled (PTEN = 0). Figure 14-9 and Figure 14-10 indicate the times when the contents of the PTPER buffer are loaded into the actual PTPER register.

The PWM period can be calculated from the following formulas:

### EQUATION 14-1: PWM PERIOD FOR FREE-RUNNING MODE

$T_{PWM} = \frac{(PTPER + 1) \times PTMRPS}{FOSC/4}$

#### EQUATION 14-2: PWM PERIOD FOR CONTINUOUS UP/DOWN COUNT MODE

$TPWM = \frac{(2 \text{ x PTPER}) \text{ x PTMRPS}}{\frac{FOSC}{4}}$

The PWM frequency is the inverse of period; or

## **EQUATION 14-3: PWM FREQUENCY**

$PWM Frequency = \frac{1}{PWM Period}$

The maximum resolution (in bits) for a given device oscillator and PWM frequency can be determined from the following formula:

#### EQUATION 14-4: PWM RESOLUTION

Resolution =

$$\frac{\log\left(\frac{\text{Fosc}}{\text{Fpwm}}\right)}{\log(2)}$$

The PWM resolutions and frequencies are shown for a selection of execution speeds and PTPER values in Table 14-2. The PWM frequencies in Table 14-2 are calculated for Edge-Aligned PWM mode. For Center-Aligned mode, the PWM frequencies will be approximately one-half the values indicated in this table.

#### TABLE 14-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS

| PWM Frequency = 1/TPWM |      |                |                   |                  |  |  |  |  |

|------------------------|------|----------------|-------------------|------------------|--|--|--|--|

| Fosc                   | MIPS | PTPER<br>Value | PWM<br>Resolution | PWM<br>Frequency |  |  |  |  |

| 40 MHz                 | 10   | 0FFFh          | 14 bits           | 2.4 kHz          |  |  |  |  |

| 40 MHz                 | 10   | 07FFh          | 13 bits           | 4.9 kHz          |  |  |  |  |

| 40 MHz                 | 10   | 03FFh          | 12 bits           | 9.8 kHz          |  |  |  |  |

| 40 MHz                 | 10   | 01FFh          | 11 bits           | 19.5 kHz         |  |  |  |  |

| 40 MHz                 | 10   | FFh            | 10 bits           | 39.0 kHz         |  |  |  |  |

| 40 MHz                 | 10   | 7Fh            | 9 bits            | 78.1 kHz         |  |  |  |  |

| 40 MHz                 | 10   | 3Fh            | 8 bits            | 156.2 kHz        |  |  |  |  |

| 40 MHz                 | 10   | 1Fh            | 7 bits            | 312.5 kHz        |  |  |  |  |

| 40 MHz                 | 10   | 0Fh            | 6 bits            | 625 kHz          |  |  |  |  |

| 25 MHz                 | 6.25 | 0FFFh          | 14 bits           | 1.5 kHz          |  |  |  |  |

| 25 MHz                 | 6.25 | 03FFh          | 12 bits           | 6.1 kHz          |  |  |  |  |

| 25 MHz                 | 6.25 | FFh            | 10 bits           | 24.4 kHz         |  |  |  |  |

| 10 MHz                 | 2.5  | 0FFFh          | 14 bits           | 610 Hz           |  |  |  |  |

| 10 MHz                 | 2.5  | 03FFh          | 12 bits           | 2.4 kHz          |  |  |  |  |

| 10 MHz                 | 2.5  | FFh            | 10 bits           | 9.8 kHz          |  |  |  |  |

| 5 MHz                  | 1.25 | 0FFFh          | 14 bits           | 305 Hz           |  |  |  |  |

| 5 MHz                  | 1.25 | 03FFh          | 12 bits           | 1.2 kHz          |  |  |  |  |

| 5 MHz                  | 1.25 | FFh            | 10 bits           | 4.9 kHz          |  |  |  |  |

| 4 MHz                  | 1    | 0FFFh          | 14 bits           | 244 Hz           |  |  |  |  |

| 4 MHz                  | 1    | 03FFh          | 12 bits           | 976 Hz           |  |  |  |  |

| 4 MHz                  | 1    | FFh            | 10 bits           | 3.9 kHz          |  |  |  |  |

| 4 IVIFIZ               |      |                | aned opera        |                  |  |  |  |  |

**Note:** For center-aligned operation, PWM frequencies will be approximately 1/2 the value indicated in the table.

# 14.6 PWM Duty Cycle

PWM duty cycle is defined by the PDCx (PDCxL and PDCxH) registers. There are a total of three PWM Duty Cycle registers for four pairs of PWM channels. The Duty Cycle registers have 14-bit resolution by combining the six LSbs of PDCxH with the 8 bits of PDCxL. PDCx is a double-buffered register used to set the counting period for the PWM time base.

#### 14.6.1 PWM DUTY CYCLE REGISTERS

There are three 14-bit Special Function Registers used to specify duty cycle values for the PWM module:

- PDC0 (PDC0L and PDC0H)

- PDC1 (PDC1L and PDC1H)

- PDC2 (PDC2L and PDC2H)

The value in each Duty Cycle register determines the amount of time that the PWM output is in the active state. The upper 12 bits of PDCx hold the actual duty cycle value from PTMRH/L<11:0>, while the lower two bits control which internal Q clock the duty cycle match will occur. This 2-bit value is decoded from the Q clocks, as shown in Figure 14-11, when the prescaler is 1:1 (PTCKPS<1:0> = 00).

In Edge-Aligned mode, the PWM period starts at Q1 and ends when the Duty Cycle register matches the PTMR register as follows. The duty cycle match is considered when the upper 12 bits of the PDCx are equal to the

# PTMRH<7:0> PTMRL<7:0> PTMR<11:0> Q Clocks<sup>(1)</sup> PTMRH<3:0> PTMRL<7:0> <1:0> Unused Comparator Unused PDCxH<5:0> PDCxL<7:0> PDCx<13:0> PDCxH<7:0> PDCxL<7:0> Note 1: This value is decoded from the Q clocks: 00 = duty cycle match occurs on Q1 01 = duty cycle match occurs on Q2 10 = duty cycle match occurs on Q3 11 = duty cycle match occurs on Q4

#### FIGURE 14-11: DUTY CYCLE COMPARISON

PTMR and the lower 2 bits are equal to Q1, Q2, Q3 or Q4, depending on the lower two bits of the PDCx (when the prescaler is 1:1 or PTCKPS<1:0 > = 00).

| Note: | When     | the     | prescaler  | is   | not   | 1:1   |

|-------|----------|---------|------------|------|-------|-------|

|       | (PTCKI   | PS<1:0  | )> ≠ ~00), | the  | duty  | cycle |

|       | match    | occurs  | s at the Q | 1 cl | ock o | f the |

|       | instruct | ion cy  | cle when   | the  | PTMR  | and   |

|       | PDCx r   | natch o | occurs.    |      |       |       |

Each compare unit has logic that allows override of the PWM signals. This logic also ensures that the PWM signals will complement each other (with dead-time insertion) in Complementary mode (see **Section 14.7** "**Dead-Time Generators**").

Note: To get the correct PWM duty cycle, always multiply the calculated PWM duty cycle value by four before writing it to the PWM Duty Cycle registers. This is due to the two additional LSBs in the PWM Duty Cycle registers which are compared against the internal Q clock for the PWM duty cycle match.

|              |                       | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                       |                |                             |                       |            |                             |                       |            |                             |  |

|--------------|-----------------------|-------------------------------|-----------------------------|-----------------------|----------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|

| BAUD<br>RATE | Fosc                  | Fosc = 40.000 MHz Fosc =      |                             |                       | c = 20.000 MHz |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 0.3          | 0.300                 | 0.00                          | 8332                        | 0.300                 | 0.02           | 4165                        | 0.300                 | 0.02       | 2082                        | 0.300                 | -0.04      | 1665                        |  |

| 1.2          | 1.200                 | 0.02                          | 2082                        | 1.200                 | -0.03          | 1041                        | 1.200                 | -0.03      | 520                         | 1.201                 | -0.16      | 415                         |  |

| 2.4          | 2.402                 | 0.06                          | 1040                        | 2.399                 | -0.03          | 520                         | 2.404                 | 0.16       | 259                         | 2.403                 | -0.16      | 207                         |  |

| 9.6          | 9.615                 | 0.16                          | 259                         | 9.615                 | 0.16           | 129                         | 9.615                 | 0.16       | 64                          | 9.615                 | -0.16      | 51                          |  |

| 19.2         | 19.231                | 0.16                          | 129                         | 19.231                | 0.16           | 64                          | 19.531                | 1.73       | 31                          | 19.230                | -0.16      | 25                          |  |

| 57.6         | 58.140                | 0.94                          | 42                          | 56.818                | -1.36          | 21                          | 56.818                | -1.36      | 10                          | 55.555                | 3.55       | 8                           |  |

| 115.2        | 113.636               | -1.36                         | 21                          | 113.636               | -1.36          | 10                          | 125.000               | 8.51       | 4                           | _                     | —          | —                           |  |

| TABLE 15-3: | <b>BAUD RATES FOR</b> | ASYNCHRONOUS MODES | (CONTINUED) |

|-------------|-----------------------|--------------------|-------------|

|-------------|-----------------------|--------------------|-------------|

| BAUD        | Fosc = 4.000 MHz      |            |                             | Fos                   | c = 2.000  | MHz                         | Fos                   | Fosc = 1.000 MHz |                             |  |

|-------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------------|-----------------------------|--|

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) |  |

| 0.3         | 0.300                 | 0.04       | 832                         | 0.300                 | -0.16      | 415                         | 0.300                 | -0.16            | 207                         |  |

| 1.2         | 1.202                 | 0.16       | 207                         | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16            | 51                          |  |

| 2.4         | 2.404                 | 0.16       | 103                         | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16            | 25                          |  |

| 9.6         | 9.615                 | 0.16       | 25                          | 9.615                 | -0.16      | 12                          | —                     | _                | _                           |  |

| 19.2        | 19.231                | 0.16       | 12                          | —                     | _          | _                           | —                     | _                | _                           |  |

| 57.6        | 62.500                | 8.51       | 3                           | —                     | _          | _                           | —                     | _                | _                           |  |

| 115.2       | 125.000               | 8.51       | 1                           | —                     | _          |                             | _                     | —                | _                           |  |

|              | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |            |                             |                       |                   |                             |                       |            |                             |                       |            |                             |

|--------------|------------------------------------------------------|------------|-----------------------------|-----------------------|-------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc                                                 | = 40.000   | ) MHz                       | Fosc                  | Fosc = 20.000 MHz |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |

| (K)          | Actual<br>Rate<br>(K)                                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | 0.300                                                | 0.00       | 33332                       | 0.300                 | 0.00              | 16665                       | 0.300                 | 0.00       | 8332                        | 0.300                 | -0.01      | 6665                        |

| 1.2          | 1.200                                                | 0.00       | 8332                        | 1.200                 | 0.02              | 4165                        | 1.200                 | 0.02       | 2082                        | 1.200                 | -0.04      | 1665                        |

| 2.4          | 2.400                                                | 0.02       | 4165                        | 2.400                 | 0.02              | 2082                        | 2.402                 | 0.06       | 1040                        | 2.400                 | -0.04      | 832                         |

| 9.6          | 9.606                                                | 0.06       | 1040                        | 9.596                 | -0.03             | 520                         | 9.615                 | 0.16       | 259                         | 9.615                 | -0.16      | 207                         |

| 19.2         | 19.193                                               | -0.03      | 520                         | 19.231                | 0.16              | 259                         | 19.231                | 0.16       | 129                         | 19.230                | -0.16      | 103                         |

| 57.6         | 57.803                                               | 0.35       | 172                         | 57.471                | -0.22             | 86                          | 58.140                | 0.94       | 42                          | 57.142                | 0.79       | 34                          |

| 115.2        | 114.943                                              | -0.22      | 86                          | 116.279               | 0.94              | 42                          | 113.636               | -1.36      | 21                          | 117.647               | -2.12      | 16                          |

|              |                       | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                       |                  |                             |                       |                  |                             |  |  |  |