Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

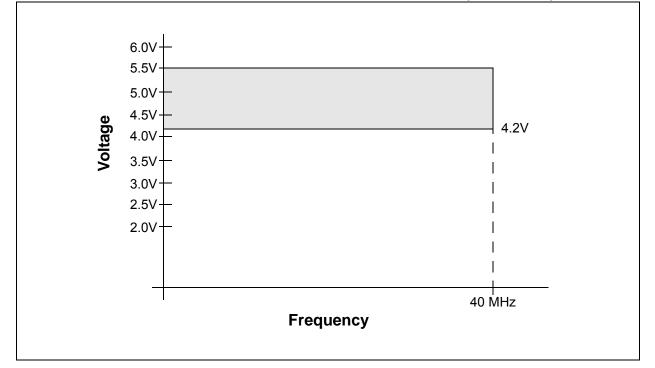

| Speed                      | 40MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 4KB (2K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

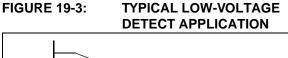

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 4x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

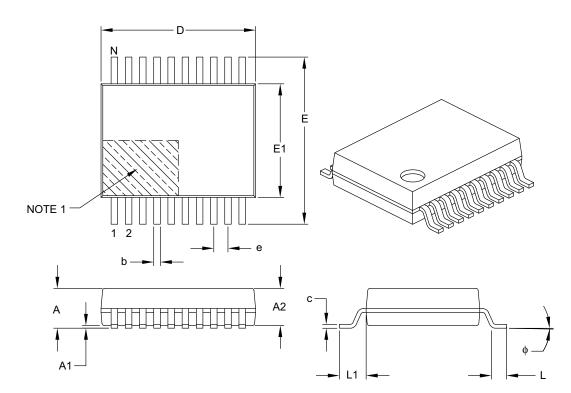

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f1230t-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| ABLE 5-4:                   |      | LIZATIO | N CONDITIONS FOR                   | ALL REGISTERS (CONT                                              |                                 |  |  |

|-----------------------------|------|---------|------------------------------------|------------------------------------------------------------------|---------------------------------|--|--|

| Register Applicable Devices |      |         | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |  |

| INDF2                       | 1230 | 1330    | N/A                                | N/A                                                              | N/A                             |  |  |

| POSTINC2                    | 1230 | 1330    | N/A                                | N/A                                                              | N/A                             |  |  |

| POSTDEC2                    | 1230 | 1330    | N/A                                | N/A                                                              | N/A                             |  |  |

| PREINC2                     | 1230 | 1330    | N/A                                | N/A                                                              | N/A                             |  |  |

| PLUSW2                      | 1230 | 1330    | N/A                                | N/A                                                              | N/A                             |  |  |

| FSR2H                       | 1230 | 1330    | 0000                               | 0000                                                             | uuuu                            |  |  |

| FSR2L                       | 1230 | 1330    | XXXX XXXX                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |

| STATUS                      | 1230 | 1330    | x xxxx                             | u uuuu                                                           | u uuuu                          |  |  |

| TMR0H                       | 1230 | 1330    | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |  |

| TMR0L                       | 1230 | 1330    | XXXX XXXX                          | սսսս սսսս                                                        | uuuu uuuu                       |  |  |

| TOCON                       | 1230 | 1330    | 1111 1111                          | 1111 1111                                                        | uuuu uuuu                       |  |  |

| OSCCON                      | 1230 | 1330    | 0100 q000                          | 0100 q000                                                        | uuuu uuqu                       |  |  |

| LVDCON                      | 1230 | 1330    | 00 0101                            | 00 0101                                                          | uu uuuu                         |  |  |

| WDTCON                      | 1230 | 1330    | 0                                  | 0                                                                | u                               |  |  |

| RCON <sup>(4)</sup>         | 1230 | 1330    | 0q-1 11q0                          | 0q-q qquu                                                        | uq-u qquu                       |  |  |

| TMR1H                       | 1230 | 1330    | xxxx xxxx                          | սսսս սսսս                                                        | uuuu uuuu                       |  |  |

| TMR1L                       | 1230 | 1330    | XXXX XXXX                          | սսսս սսսս                                                        | uuuu uuuu                       |  |  |

| T1CON                       | 1230 | 1330    | 0000 0000                          | սՕսս սսսս                                                        | սսսս սսսս                       |  |  |

| ADRESH                      | 1230 | 1330    | XXXX XXXX                          | սսսս սսսս                                                        | uuuu uuuu                       |  |  |

| ADRESL                      | 1230 | 1330    | XXXX XXXX                          | սսսս սսսս                                                        | uuuu uuuu                       |  |  |

| ADCON0                      | 1230 | 1330    | 0 0000                             | 0 0000                                                           | u uuuu                          |  |  |

| ADCON1                      | 1230 | 1330    | 0 1111                             | 0 1111                                                           | u uuuu                          |  |  |

| ADCON2                      | 1230 | 1330    | 0-00 0000                          | 0-00 0000                                                        | u-uu uuuu                       |  |  |

| BAUDCON                     | 1230 | 1330    | 01-00 0-00                         | 01-00 0-00                                                       | uu-uu u-uu                      |  |  |

| CVRCON                      | 1230 | 1330    | 0-00 0000                          | 0-00 0000                                                        | u-uu uuuu                       |  |  |

| CMCON                       | 1230 | 1330    | 000000                             | 000000                                                           | uuuuuu                          |  |  |

| SPBRGH                      | 1230 | 1330    | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |  |

| SPBRG                       | 1230 | 1330    | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |  |

| RCREG                       | 1230 | 1330    | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |  |

| TXREG                       | 1230 | 1330    | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |  |

| TXSTA                       | 1230 | 1330    | 0000 0010                          | 0000 0010                                                        | uuuu uuuu                       |  |  |

| RCSTA                       | 1230 | 1330    | 0000 000x                          | 0000 000x                                                        | uuuu uuuu                       |  |  |

## TABLE 5-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- **2:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 5-3 for Reset value for specific condition.

- **5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read as '0'.

- 6: Reset condition of PWMEN bits depends on the PWMPIN Configuration bit of CONFIG3L.

## 6.1.1 PROGRAM COUNTER

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21 bits wide and is contained in three separate 8-bit registers. The low byte, known as the PCL register, is both readable and writable. The high byte, or PCH register, contains the PC<15:8> bits; it is not directly readable or writable. Updates to the PCH register are performed through the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCH register. Updates to the PCU register are performed through the PCLATH register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCU register are performed through the PCLATU register.

The contents of PCLATH and PCLATU are transferred to the program counter by any operation that writes to the PCL. Similarly, the upper two bytes of the program counter are transferred to PCLATH and PCLATU by an operation that reads the PCL. This is useful for computed offsets to the PC (see **Section 6.1.4.1 "Computed GOTO"**).

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the Least Significant bit of PCL is fixed to a value of '0'. The PC increments by 2 to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

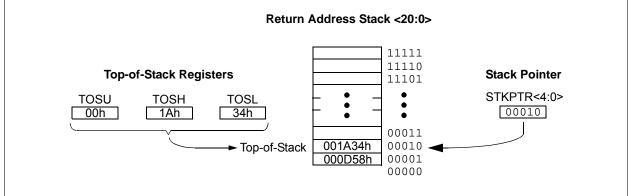

### 6.1.2 RETURN ADDRESS STACK

The return address stack allows any combination of up to 31 program calls and interrupts to occur. The PC is pushed onto the stack when a CALL or RCALL instruction is executed or an interrupt is Acknowledged. The PC value is pulled off the stack on a RETURN, RETLW or a RETFIE instruction. PCLATU and PCLATH are not affected by any of the RETURN or CALL instructions.

The stack operates as a 31-word by 21-bit RAM and a 5-bit Stack Pointer, STKPTR. The stack space is not part of either program or data space. The Stack Pointer is readable and writable and the address on the top of the stack is readable and writable through the Top-of-Stack Special Function Registers. Data can also be pushed to, or popped from the stack, using these registers.

A CALL type instruction causes a push onto the stack; the Stack Pointer is first incremented and the location pointed to by the Stack Pointer is written with the contents of the PC (already pointing to the instruction following the CALL). A RETURN type instruction causes a pop from the stack; the contents of the location pointed to by the STKPTR are transferred to the PC and then the Stack Pointer is decremented.

The Stack Pointer is initialized to '00000' after all Resets. There is no RAM associated with the location corresponding to a Stack Pointer value of '00000'; this is only a Reset value. Status bits indicate if the stack is full, has overflowed or has underflowed.

### 6.1.2.1 Top-of-Stack Access

Only the top of the return address stack (TOS) is readable and writable. A set of three registers, TOSU:TOSH:TOSL, hold the contents of the stack location pointed to by the STKPTR register (Figure 6-2). This allows users to implement a software stack if necessary. After a CALL, RCALL or interrupt, the software can read the pushed value by reading the TOSU:TOSH:TOSL registers. These values can be placed on a user-defined software stack. At return time, the software can return these values to TOSU:TOSH:TOSL and do a return.

The user must disable the global interrupt enable bits while accessing the stack to prevent inadvertent stack corruption.

# 13.0 TIMER1 MODULE

The Timer1 timer/counter module has the following features:

- 16-bit timer/counter (two 8-bit registers; TMR1H and TMR1L)

- Readable and writable (both registers)

- · Internal or external clock select

- Interrupt on overflow from FFFFh to 0000h

- · Status of system clock operation

Figure 13-1 is a simplified block diagram of the Timer1 module.

Register 13-1 details the Timer1 Control register. This register controls the operating mode of the Timer1 module and contains the Timer1 Oscillator Enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

The Timer1 oscillator can be used as a secondary clock source in power-managed modes. When the T1RUN bit is set, the Timer1 oscillator provides the system clock. If the Fail-Safe Clock Monitor is enabled and the Timer1 oscillator fails while providing the system clock, polling the T1RUN bit will indicate whether the clock is being provided by the Timer1 oscillator or another source.

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

### REGISTER 13-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0 | R-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|---------|---------|---------|--------|--------|--------|

| RD16  | T1RUN | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |       |         |         |         |        |        | bit 0  |

| Legend:      |                                                                                                               |                                 |                                                 |                               |  |  |  |  |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------------------------------------|-------------------------------|--|--|--|--|--|--|--|--|

| R = Readab   | le bit                                                                                                        | W = Writable bit                | U = Unimplemented bit,                          | read as '0'                   |  |  |  |  |  |  |  |  |

| -n = Value a | t POR                                                                                                         | '1' = Bit is set                | '0' = Bit is cleared                            | x = Bit is unknown            |  |  |  |  |  |  |  |  |

| bit 7        | <b>RD16:</b> 1                                                                                                | 6-Bit Read/Write Mode Enabl     | le bit                                          |                               |  |  |  |  |  |  |  |  |

|              | 1 = Ena                                                                                                       | bles register read/write of Tin | ner1 in one 16-bit operation                    |                               |  |  |  |  |  |  |  |  |

|              | 0 = Ena                                                                                                       | bles register read/write of Tin | ner1 in two 8-bit operations                    |                               |  |  |  |  |  |  |  |  |

| bit 6        | T1RUN:                                                                                                        | Timer1 System Clock Status      | bit                                             |                               |  |  |  |  |  |  |  |  |

|              |                                                                                                               | rice clock is derived from Time |                                                 |                               |  |  |  |  |  |  |  |  |

|              |                                                                                                               | rice clock is derived from anot |                                                 |                               |  |  |  |  |  |  |  |  |

| bit 5-4      | T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits                                                      |                                 |                                                 |                               |  |  |  |  |  |  |  |  |

|              | 11 = 1:8 Prescale value                                                                                       |                                 |                                                 |                               |  |  |  |  |  |  |  |  |

|              | 10 = 1:4 Prescale value<br>01 = 1:2 Prescale value                                                            |                                 |                                                 |                               |  |  |  |  |  |  |  |  |

|              |                                                                                                               | Prescale value                  |                                                 |                               |  |  |  |  |  |  |  |  |

| bit 3        | T1OSCEN: Timer1 Oscillator Enable bit                                                                         |                                 |                                                 |                               |  |  |  |  |  |  |  |  |

|              | 1 = Time                                                                                                      | er1 oscillator is enabled       |                                                 |                               |  |  |  |  |  |  |  |  |

|              |                                                                                                               | er1 oscillator is shut off      |                                                 |                               |  |  |  |  |  |  |  |  |

|              |                                                                                                               | -                               | esistor are turned off to elimin                | ate power drain.              |  |  |  |  |  |  |  |  |

| bit 2        |                                                                                                               | : Timer1 External Clock Inpu    | t Synchronization Select bit                    |                               |  |  |  |  |  |  |  |  |

|              | -                                                                                                             | $\frac{MR1CS = 1}{2}$           | - inn4                                          |                               |  |  |  |  |  |  |  |  |

|              | <ul> <li>1 = Do not synchronize external clock input</li> <li>0 = Synchronize external clock input</li> </ul> |                                 |                                                 |                               |  |  |  |  |  |  |  |  |

|              | When TMR1CS = $0$ :                                                                                           |                                 |                                                 |                               |  |  |  |  |  |  |  |  |

|              | This bit is ignored. Timer1 uses the internal clock when TMR1CS = $0.$                                        |                                 |                                                 |                               |  |  |  |  |  |  |  |  |

| bit 1        | TMR1CS                                                                                                        | S: Timer1 Clock Source Select   | ct bit                                          |                               |  |  |  |  |  |  |  |  |

|              | 1 = Exte                                                                                                      | ernal clock from T1OSO/T1Cl     | <i (on="" edge)<sup="" rising="" the="">(1)</i> |                               |  |  |  |  |  |  |  |  |

|              | 0 = Inte                                                                                                      | rnal clock (Fosc/4)             |                                                 |                               |  |  |  |  |  |  |  |  |

| bit 0        | TMR10                                                                                                         | N: Timer1 On bit                |                                                 |                               |  |  |  |  |  |  |  |  |

|              |                                                                                                               | ıbles Timer1<br>os Timer1       |                                                 |                               |  |  |  |  |  |  |  |  |

| Note 1. Pla  | coment of T1                                                                                                  | OSI and T1OSO/T1CKI depen       | ids on the value of the Configur                | ation bit. T1OSCMX. of CONFIG |  |  |  |  |  |  |  |  |

Note 1: Placement of T1OSI and T1OSO/T1CKI depends on the value of the Configuration bit, T1OSCMX, of CONFIG3H.

# FIGURE 14-21: PWM OUTPUT OVERRIDE EXAMPLE #1

| -            |   |   |   | · <b></b> " | - |   |      |

|--------------|---|---|---|-------------|---|---|------|

|              | 1 | 2 | 3 | 4           | 5 | 6 |      |

| PWM5         |   |   |   |             |   |   | <br> |

| PWM4<br>PWM3 |   |   |   |             |   |   | <br> |

| PWM2         |   |   |   |             |   |   |      |

| PWM1         |   |   |   |             |   |   |      |

|              |   |   |   |             |   | • | •    |

# TABLE 14-4:PWM OUTPUT OVERRIDEEXAMPLE #1

| State | OVDCOND (POVD) | OVDCONS (POUT) |

|-------|----------------|----------------|

| 1     | 0000000b       | 00100100b      |

| 2     | d0000000b      | 00100001b      |

| 3     | d0000000b      | 00001001b      |

| 4     | d0000000b      | 00011000b      |

| 5     | d0000000b      | 00010010b      |

| 6     | d0000000b      | 00000110b      |

# TABLE 14-5:PWM OUTPUT OVERRIDEEXAMPLE #2

| State | OVDCOND (POVD) | OVDCONS (POUT) |

|-------|----------------|----------------|

| 1     | 00000011b      | d0000000b      |

| 2     | 00110000b      | d0000000b      |

| 3     | 00111100b      | d0000000b      |

| 4     | 00001111b      | d0000000b      |

### FIGURE 14-22: PWM OUTPUT OVERRIDE EXAMPLE #2

# 14.11 PWM Output and Polarity Control

There are three device Configuration bits associated with the PWM module that provide PWM output pin control defined in the CONFIG3L register. They are:

- HPOL

- LPOL

- PWMPIN

These three Configuration bits work in conjunction with the three PWM Enable bits (PWMEN2:PWMEN0) in the PWMCON0 register. The Configuration bits and PWM enable bits ensure that the PWM pins are in the correct states after a device Reset occurs.

## 14.11.1 OUTPUT PIN CONTROL

The PWMEN2:PWMEN0 control bits enable each PWM output pin as required in the application.

All PWM I/O pins are general purpose I/O. When a pair of pins is enabled for PWM output, the PORT and TRIS registers controlling the pins are disabled. Refer to Figure 14-23 for details.

### 14.11.2 OUTPUT POLARITY CONTROL

The polarity of the PWM I/O pins is set during device programming via the HPOL and LPOL Configuration bits in the CONFIG3L register. The HPOL Configuration bit sets the output polarity for the high side PWM outputs: PWM1, PWM3 and PWM5. The polarity is active-high when HPOL is set (= 1) and active-low when it is cleared (= 0).

The LPOL Configuration bit sets the output polarity for the low side PWM outputs: PWM0, PWM2 and PWM4. As with HPOL, they are active-high when LPOL is set and active-low when cleared.

All output signals generated by the PWM module are referenced to the polarity control bits, including those generated by Fault inputs or manual override (see **Section 14.10 "PWM Output Override"**).

The default polarity Configuration bits have the PWM I/O pins in active-high output polarity.

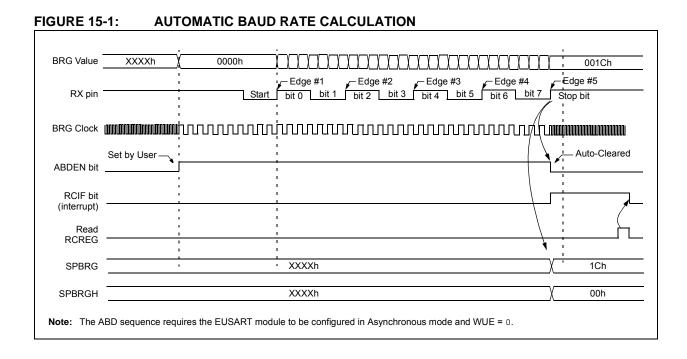

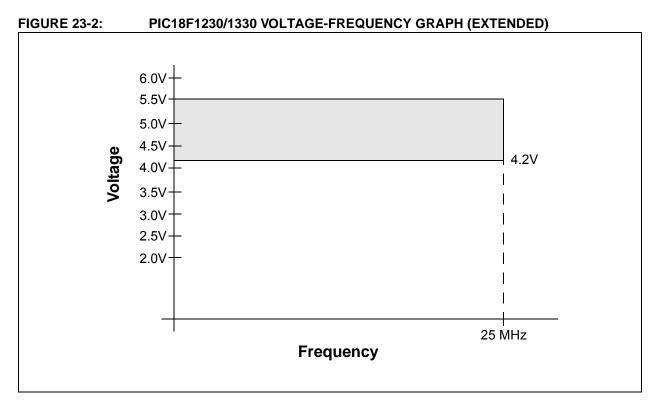

# 15.1 Baud Rate Generator (BRG)

The BRG is a dedicated 8-bit or 16-bit generator that supports both the Asynchronous and Synchronous modes of the EUSART. By default, the BRG operates in 8-bit mode; setting the BRG16 bit (BAUDCON<3>) selects 16-bit mode.

The SPBRGH:SPBRG register pair controls the period of a free-running timer. In Asynchronous mode, bits BRGH (TXSTA<2>) and BRG16 (BAUDCON<3>) also control the baud rate. In Synchronous mode, BRGH is ignored. Table 15-1 shows the formula for computation of the baud rate for different EUSART modes which only apply in Master mode (internally generated clock).

Given the desired baud rate and FOSC, the nearest integer value for the SPBRGH:SPBRG registers can be calculated using the formulas in Table 15-1. From this, the error in baud rate can be determined. An example calculation is shown in Example 15-1. Typical baud rates and error values for the various Asynchronous modes are shown in Table 15-2. It may be advantageous to use the high baud rate (BRGH = 1), or the 16-bit BRG to reduce the baud rate error, or achieve a slow baud rate for a fast oscillator frequency.

Writing a new value to the SPBRGH:SPBRG registers causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

| Note: | A BRG value of '0' is not supported. |

|-------|--------------------------------------|

|       |                                      |

### 15.1.1 OPERATION IN POWER-MANAGED MODES

The device clock is used to generate the desired baud rate. When one of the power-managed modes is entered, the new clock source may be operating at a different frequency. This may require an adjustment to the value in the SPBRG register pair.

### 15.1.2 SAMPLING

The data on the RX pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin when SYNC is clear or when both BRG16 and BRGH are not set. The data on the RX pin is sampled once when SYNC is set or when BRGH16 and BRGH are both set.

| C    | onfiguration B | its  | BRG/EUSART Mode     | Baud Rate Formula |  |  |

|------|----------------|------|---------------------|-------------------|--|--|

| SYNC | BRG16          | BRGH | BRG/EUSART Mode     | Baud Rate Formula |  |  |

| 0    | 0              | 0    | 8-bit/Asynchronous  | Fosc/[64 (n + 1)] |  |  |

| 0    | 0              | 1    | 8-bit/Asynchronous  |                   |  |  |

| 0    | 1              | 0    | 16-bit/Asynchronous | Fosc/[16 (n + 1)] |  |  |

| 0    | 1              | 1    | 16-bit/Asynchronous |                   |  |  |

| 1    | 0              | х    | 8-bit/Synchronous   | Fosc/[4 (n + 1)]  |  |  |

| 1    | 1              | x    | 16-bit/Synchronous  |                   |  |  |

### TABLE 15-1: BAUD RATE FORMULAS

**Legend:** x = Don't care, n = value of SPBRGH:SPBRG register pair

## EXAMPLE 15-1: CALCULATING BAUD RATE ERROR

| For a device with FOSC | of 1 | 6 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG: |

|------------------------|------|-----------------------------------------------------------------|

| Desired Baud Rate      | =    | Fosc/(64 ([SPBRGH:SPBRG] + 1))                                  |

| Solving for SPBRGH:S   | PBF  | RG:                                                             |

| Х                      | =    | ((FOSC/Desired Baud Rate)/64) – 1                               |

|                        | =    | ((1600000/9600)/64) - 1                                         |

|                        | =    | [25.042] = 25                                                   |

| Calculated Baud Rate   | =    | 16000000/(64 (25 + 1))                                          |

|                        | =    | 9615                                                            |

| Error                  | =    | (Calculated Baud Rate - Desired Baud Rate)/Desired Baud Rate    |

|                        | =    | (9615 - 9600)/9600 = 0.16%                                      |

|                        |      |                                                                 |

TABLE 15-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Name    | Bit 7    | Bit 6      | Bit 5       | Bit 4        | Bit 3  | Bit 2 | Bit 1 | Bit 0 | Reset Values<br>on Page: |

|---------|----------|------------|-------------|--------------|--------|-------|-------|-------|--------------------------|

| TXSTA   | CSRC     | TX9        | TXEN        | SYNC         | SENDB  | BRGH  | TRMT  | TX9D  | 48                       |

| RCSTA   | SPEN     | RX9        | SREN        | CREN         | ADDEN  | FERR  | OERR  | RX9D  | 48                       |

| BAUDCON | ABDOVF   | RCIDL      | RXDTP       | TXCKP        | BRG16  | —     | WUE   | ABDEN | 48                       |

| SPBRGH  | EUSART B | aud Rate G | Generator R | egister High | n Byte |       |       |       | 48                       |

| SPBRG   | EUSART B | aud Rate G | Generator R | egister Low  | Byte   |       |       |       | 48                       |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the BRG.

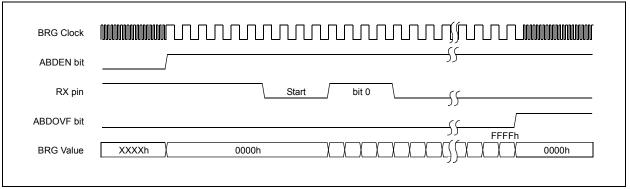

### FIGURE 15-2: BRG OVERFLOW SEQUENCE

### 15.2.4.1 Special Considerations Using Auto-Wake-up

Since auto-wake-up functions by sensing rising edge transitions on RX/DT, information with any state changes before the Stop bit may signal a false End-of-Character and cause data or framing errors. To work properly, therefore, the initial characters in the transmission must be all '0's. This can be 00h (8 bits) for standard RS-232 devices or 000h (12 bits) for LIN/J2602 bus.

Oscillator start-up time must also be considered, especially in applications using oscillators with longer start-up intervals (i.e., XT or HS mode). The Sync Break (or Wake-up Signal) character must be of sufficient length and be followed by a sufficient interval to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

# 15.2.4.2 Special Considerations Using the WUE Bit

The timing of WUE and RCIF events may cause some confusion when it comes to determining the validity of received data. As noted, setting the WUE bit places the EUSART in an Idle mode. The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared after this when a rising edge is seen on RX/DT. The interrupt condition is then cleared by reading the RCREG register. Ordinarily, the data in RCREG will be dummy data and should be discarded.

The fact that the WUE bit has been cleared (or is still set) and the RCIF flag is set should not be used as an indicator of the integrity of the data in RCREG. Users should consider implementing a parallel method in firmware to verify received data integrity.

To assure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

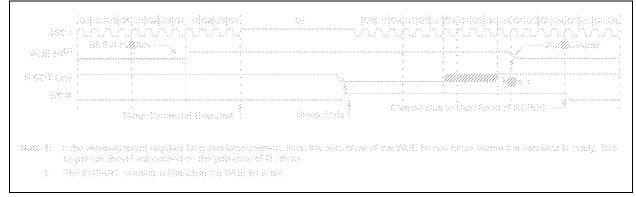

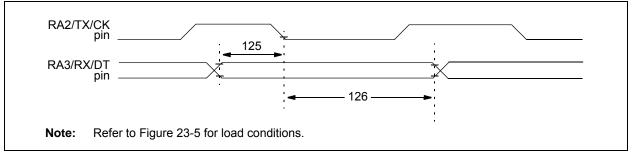

# FIGURE 15-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING NORMAL OPERATION

| 526162.0          |                                        | an an an an an<br>Seanna | an in ar ai | <br> | 111 111 111<br>1                        | ~~~   | / 317 317 31<br>1                     | ,<br>}  | , in the set   |              | and and an an | /          | e an an an an a<br>Communitation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | n an an a<br>Maranar                                                                                                                                                                                                              |

|-------------------|----------------------------------------|--------------------------|-------------|------|-----------------------------------------|-------|---------------------------------------|---------|----------------|--------------|---------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| and and the       | ) - BE Sor 64                          | 87.976                   |             |      |                                         |       | <u>.</u>                              | ;<br>;; |                | <u></u>      |               |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | atta a serie a serie da serie<br>Contra serie da serie |

| (al-stall 2001) 1 | ······································ |                          |             |      |                                         |       | *<br>*                                | 5       | ,              | 3            | <i>.</i>      | ; .        | zennen en e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | :                                                                                                                                                                                                                                 |

| X82733466         | <u>.</u>                               |                          |             |      | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | Mai   | *<br>\$********                       | ,<br>,  | -              | - 5<br>- 577 |               | à cont     | 4<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | i                                                                                                                                                                                                                                 |

|                   | * :                                    |                          |             | · .' |                                         | 77665 | · · · · · · · · · · · · · · · · · · · |         | ••••••         |              | :             | 1          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                   |

| 886385            | ,                                      |                          |             |      |                                         |       |                                       | <       |                |              | da            |            | series and the series of the s | es<br>Junior                                                                                                                                                                                                                      |

|                   | <                                      |                          |             |      |                                         |       |                                       | ł       | - Ce Maria (Cr | 92 X         | aillean anns  | <i>4 2</i> | \$200000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                   |

|                   | · · ·                                  |                          |             |      |                                         |       |                                       | *       |                |              | •             |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                   |

# FIGURE 15-9: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

# 19.0 LOW-VOLTAGE DETECT (LVD)

PIC18F1230/1330 devices have a Low-Voltage Detect module (LVD). This is a programmable circuit that allows the user to specify the device voltage trip point. If the device experiences an excursion past the trip point, an interrupt flag is set. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to the interrupt. The Low-Voltage Detect Control register (Register 19-1) completely controls the operation of the LVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

The block diagram for the LVD module is shown in Figure 19-1.

### REGISTER 19-1: LVDCON: LOW-VOLTAGE DETECT CONTROL REGISTER

| U-0   | U-0 | R-0   | R/W-0 | R/W-0                | R/W-1                | R/W-0                | R/W-1                |

|-------|-----|-------|-------|----------------------|----------------------|----------------------|----------------------|

|       | —   | IRVST | LVDEN | LVDL3 <sup>(1)</sup> | LVDL2 <sup>(1)</sup> | LVDL1 <sup>(1)</sup> | LVDL0 <sup>(1)</sup> |

| bit 7 |     |       |       |                      |                      |                      | bit 0                |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                                                           |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | IRVST: Internal Reference Voltage Stable Flag bit                                                                                                                                    |

|         | 1 = Indicates that the voltage detect logic will generate the interrupt flag at the specified voltage<br>trip point                                                                  |

|         | <ul> <li>Indicates that the voltage detect logic will not generate the interrupt flag at the specified voltage<br/>trip point and the LVD interrupt should not be enabled</li> </ul> |

| bit 4   | LVDEN: Low-Voltage Detect Power Enable bit                                                                                                                                           |

|         | 1 = LVD enabled                                                                                                                                                                      |

|         | 0 = LVD disabled                                                                                                                                                                     |

| bit 3-0 | LVDL3:LVDL0: Voltage Detection Limit bits <sup>(1)</sup>                                                                                                                             |

|         | 1111 = Reserved                                                                                                                                                                      |

|         | 1110 = Maximum setting                                                                                                                                                               |

|         | •                                                                                                                                                                                    |

|         | •                                                                                                                                                                                    |

|         | •                                                                                                                                                                                    |

|         | 0000 = Minimum setting                                                                                                                                                               |

| Note 1  | See Table 23.4 in Section 23.0 "Electrical Characteristics" for the specifications                                                                                                   |

**Note 1:** See Table 23-4 in **Section 23.0 "Electrical Characteristics**" for the specifications.

. .. - .

.. .

. . .

## 19.5 Applications

In many applications, the ability to detect a drop below a particular threshold is desirable.

For general battery applications, Figure 19-3 shows a possible voltage curve. Over time, the device voltage decreases. When the device voltage reaches voltage VA, the LVD logic generates an interrupt at time TA. The interrupt could cause the execution of an ISR, which would allow the application to perform "housekeeping tasks" and perform a controlled shutdown before the device voltage exits the valid operating range at TB. The LVD, thus, would give the application a time window, represented by the difference between TA and TB, to safely exit.

#

## **19.6 Operation During Sleep**

When enabled, the LVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the LVDIF bit will be set and the device will wakeup from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

## 19.7 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the LVD module to be turned off.

### TABLE 19-1: REGISTERS ASSOCIATED WITH LOW-VOLTAGE DETECT MODULE

| Name   | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0 | Reset<br>Values<br>on Page: |

|--------|----------|-----------|--------|--------|-------|--------|--------|-------|-----------------------------|

| LVDCON | _        |           | IRVST  | LVDEN  | LVDL3 | LVDL2  | LVDL1  | LVDL0 | 48                          |

| INTCON | GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF  | 47                          |

| PIR2   | OSCFIF   | —         | —      | EEIF   | _     | LVDIF  | _      | —     | 49                          |

| PIE2   | OSCFIE   | —         | —      | EEIE   | _     | LVDIE  | _      | —     | 49                          |

| IPR2   | OSCFIP   | _         |        | EEIP   | _     | LVDIP  | _      | _     | 49                          |

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the LVD module.

# 21.7 MPLAB ICE 2000 High-Performance In-Circuit Emulator

The MPLAB ICE 2000 In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers. Software control of the MPLAB ICE 2000 In-Circuit Emulator is advanced by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The architecture of the MPLAB ICE 2000 In-Circuit Emulator allows expansion to support new PIC microcontrollers.

The MPLAB ICE 2000 In-Circuit Emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows<sup>®</sup> 32-bit operating system were chosen to best make these features available in a simple, unified application.

# 21.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC<sup>®</sup> and MCU devices. It debugs and programs PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The MPLAB REAL ICE probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with the popular MPLAB ICD 2 system (RJ11) or with the new high speed, noise tolerant, lowvoltage differential signal (LVDS) interconnection (CAT5).

MPLAB REAL ICE is field upgradeable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added, such as software breakpoints and assembly code trace. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, real-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 21.9 MPLAB ICD 2 In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD 2, is a powerful, low-cost, run-time development tool, connecting to the host PC via an RS-232 or high-speed USB interface. This tool is based on the Flash PIC MCUs and can be used to develop for these and other PIC MCUs and dsPIC DSCs. The MPLAB ICD 2 utilizes the in-circuit debugging capability built into the Flash devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) protocol, offers costeffective, in-circuit Flash debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by setting breakpoints, single stepping and watching variables, and CPU status and peripheral registers. Running at full speed enables testing hardware and applications in real time. MPLAB ICD 2 also serves as a development programmer for selected PIC devices.

# 21.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an SD/MMC card for file storage and secure data applications.

## TABLE 22-1: OPCODE FIELD DESCRIPTIONS

| Field           | Description                                                                                                                                                     |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| a               | RAM access bit                                                                                                                                                  |

|                 | a = 0: RAM location in Access RAM (BSR register is ignored)                                                                                                     |

|                 | a = 1: RAM bank is specified by BSR register                                                                                                                    |

| bbb             | Bit address within an 8-bit file register (0 to 7).                                                                                                             |

| BSR             | Bank Select Register. Used to select the current RAM bank.                                                                                                      |

| C, DC, Z, OV, N | ALU Status bits: Carry, Digit Carry, Zero, Overflow, Negative.                                                                                                  |

| d               | Destination select bit                                                                                                                                          |

|                 | d = 0: store result in WREG                                                                                                                                     |

| -               | d = 1: store result in file register f                                                                                                                          |

| dest            | Destination: either the WREG register or the specified register file location.                                                                                  |

| f               | 8-bit Register file address (00h to FFh) or 2-bit FSR designator (0h to 3h).                                                                                    |

| f <sub>s</sub>  | 12-bit Register file address (000h to FFFh). This is the source address.                                                                                        |

| f <sub>d</sub>  | 12-bit Register file address (000h to FFFh). This is the destination address.                                                                                   |

| GIE             | Global Interrupt Enable bit.                                                                                                                                    |

| k               | Literal field, constant data or label (may be either an 8-bit, 12-bit or a 20-bit value).                                                                       |

| label           | Label name.                                                                                                                                                     |

| mm              | The mode of the TBLPTR register for the table read and table write instructions.                                                                                |

|                 | Only used with table read and table write instructions:                                                                                                         |

| *               | No change to register (such as TBLPTR with table reads and writes)                                                                                              |

| *+              | Post-Increment register (such as TBLPTR with table reads and writes)                                                                                            |

| *_              | Post-Decrement register (such as TBLPTR with table reads and writes)                                                                                            |

| +*              | Pre-Increment register (such as TBLPTR with table reads and writes)                                                                                             |

| n               | The relative address (2's complement number) for relative branch instructions or the direct address for                                                         |

|                 | Call/Branch and Return instructions.                                                                                                                            |

| PC              | Program Counter.                                                                                                                                                |

| PCL             | Program Counter Low Byte.                                                                                                                                       |

| PCH             | Program Counter High Byte.                                                                                                                                      |

| PCLATH          | Program Counter High Byte Latch.                                                                                                                                |

| PCLATU          | Program Counter Upper Byte Latch.                                                                                                                               |

| PD              | Power-Down bit.                                                                                                                                                 |

| PRODH           | Product of Multiply High Byte.                                                                                                                                  |

| PRODL           | Product of Multiply Low Byte.                                                                                                                                   |

| S               | Fast Call/Return mode select bit                                                                                                                                |

|                 | <ul> <li>s = 0: do not update into/from shadow registers</li> <li>s = 1: certain registers loaded into/from shadow registers (Fast mode)</li> </ul>             |

| משת זתש         | 21-bit Table Pointer (points to a program memory location).                                                                                                     |

| TBLPTR          |                                                                                                                                                                 |

| TABLAT          | 8-bit Table Latch.                                                                                                                                              |

| TO              | Time-out bit.                                                                                                                                                   |

| TOS             | Top-of-Stack.                                                                                                                                                   |

| u               | Unused or unchanged.                                                                                                                                            |

| WDT             | Watchdog Timer.                                                                                                                                                 |

| WREG            | Working register (accumulator).                                                                                                                                 |

| x               | Don't care ('0' or '1'). The assembler will generate code with $x = 0$ . It is the recommended form of use for compatibility with all Microchip software tools. |

|                 |                                                                                                                                                                 |

| z <sub>s</sub>  | 7-bit offset value for indirect addressing of register files (source).                                                                                          |

| z <sub>d</sub>  | 7-bit offset value for indirect addressing of register files (destination).                                                                                     |

| 1 J             | Optional argument. Indicates an indexed address.                                                                                                                |

| [text]          |                                                                                                                                                                 |

| (text)          | The contents of text.                                                                                                                                           |

| [expr] <n></n>  | Specifies bit n of the register indicated by the pointer expr.                                                                                                  |

| $\rightarrow$   | Assigned to.                                                                                                                                                    |

| < >             | Register bit field.                                                                                                                                             |

| €               | In the set of.                                                                                                                                                  |

| italics         | User-defined term (font is Courier New).                                                                                                                        |

| BNC                                           | Branch if                                                                 | Not Carry                                                                               |                                                      | BNN         | 1                                                       | Branch if                                                              | Not Negativ                                                                          | /e                                            |

|-----------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------|-------------|---------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------|

| Syntax:                                       | BNC n                                                                     |                                                                                         |                                                      | Synt        | ax:                                                     | BNN n                                                                  |                                                                                      |                                               |