Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 4x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f1330-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.7.1 OSCILLATOR CONTROL REGISTER

The OSCCON register (Register 3-2) controls several aspects of the device clock's operation, both in full power operation and in power-managed modes.

The System Clock Select bits, SCS1:SCS0, select the clock source. The available clock sources are the primary clock (defined by the FOSC3:FOSC0 Configuration bits), the secondary clock (Timer1 oscillator) and the internal oscillator block. The clock source changes immediately after one or more of the bits is written to, following a brief clock transition interval. The SCS bits are cleared on all forms of Reset.

The Internal Oscillator Frequency Select bits (IRCF2:IRCF0) select the frequency output of the internal oscillator block to drive the device clock. The choices are the INTRC source, the INTOSC source (8 MHz) or one of the frequencies derived from the INTOSC postscaler (31.25 kHz to 4 MHz). If the internal oscillator block is supplying the device clock, changing the states of these bits will have an immediate change on the internal oscillator's output. On device Resets, the default output frequency of the internal oscillator block is set at 1 MHz.

When a nominal output frequency of 31 kHz is selected (IRCF2:IRCF0 = 000), users may choose which internal oscillator acts as the source. This is done with the INTSRC bit in the OSCTUNE register (OSCTUNE<7>). Setting this bit selects INTOSC as a 31.25 kHz clock source by enabling the divide-by-256 output of the INTOSC postscaler. Clearing INTSRC selects INTRC (nominally 31 kHz) as the clock source.

This option allows users to select the tunable and more precise INTOSC as a clock source, while maintaining power savings with a very low clock speed. Regardless of the setting of INTSRC, INTRC always remains the clock source for features such as the Watchdog Timer and the Fail-Safe Clock Monitor.

The OSTS, IOFS and T1RUN bits indicate which clock source is currently providing the device clock. The OSTS bit indicates that the Oscillator Start-up Timer has timed out and the primary clock is providing the device clock in primary clock modes. The IOFS bit indicates when the internal oscillator block has stabilized and is providing the device clock in RC Clock modes. The T1RUN bit (T1CON<6>) indicates when the Timer1 oscillator is providing the device clock in secondary clock modes. In power-managed modes, only one of these three bits will be set at any time. If none of these bits are set, the INTRC is providing the clock or the internal oscillator block has just started and is not yet stable. The IDLEN bit determines if the device goes into Sleep mode or one of the Idle modes when the SLEEP instruction is executed.

The use of the flag and control bits in the OSCCON register is discussed in more detail in **Section 4.0** "**Power-Managed Modes**".

- Note 1: The Timer1 oscillator must be enabled to select the secondary clock source. The Timer1 oscillator is enabled by setting the T1OSCEN bit in the Timer1 Control register (T1CON<3>). If the Timer1 oscillator is not enabled, then any attempt to select a secondary clock source will be ignored.

- 2: It is recommended that the Timer1 oscillator be operating and stable before selecting the secondary clock source or a very long delay may occur while the Timer1 oscillator starts.

# 3.7.2 OSCILLATOR TRANSITIONS

PIC18F1230/1330 devices contain circuitry to prevent clock "glitches" when switching between clock sources. A short pause in the device clock occurs during the clock switch. The length of this pause is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Clock transitions are discussed in greater detail in **Section 4.1.2 "Entering Power-Managed Modes"**.

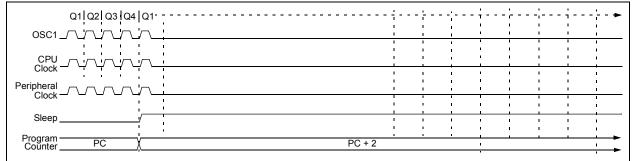

# 4.3 Sleep Mode

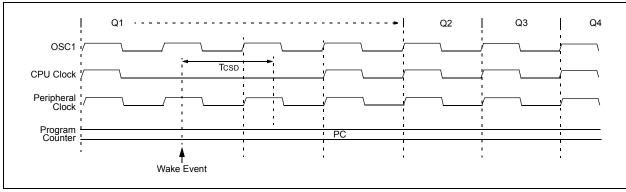

The power-managed Sleep mode in the PIC18F1230/ 1330 devices is identical to the legacy Sleep mode offered in all other PIC devices. It is entered by clearing the IDLEN bit (the default state on device Reset) and executing the SLEEP instruction. This shuts down the selected oscillator (Figure 4-5). All clock source status bits are cleared.

Entering the Sleep mode from any other mode does not require a clock switch. This is because no clocks are needed once the controller has entered Sleep. If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run.

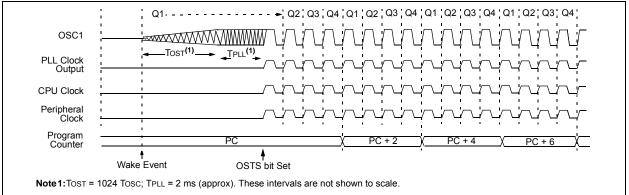

When a wake event occurs in Sleep mode (by interrupt, Reset or WDT time-out), the device will not be clocked until the clock source selected by the SCS1:SCS0 bits becomes ready (see Figure 4-6), or it will be clocked from the internal oscillator block if either the Two-Speed Start-up or the Fail-Safe Clock Monitor are enabled (see **Section 20.0 "Special Features of the CPU"**). In either case, the OSTS bit is set when the primary clock is providing the device clocks. The IDLEN and SCS bits are not affected by the wake-up.

## 4.4 Idle Modes

The Idle modes allow the controller's CPU to be selectively shut down while the peripherals continue to operate. Selecting a particular Idle mode allows users to further manage power consumption.

If the IDLEN bit is set to a '1' when a SLEEP instruction is executed, the peripherals will be clocked from the clock source selected using the SCS1:SCS0 bits; however, the CPU will not be clocked. The clock source status bits are not affected. Setting IDLEN and executing a SLEEP instruction provides a quick method of switching from a given Run mode to its corresponding Idle mode.

If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run.

Since the CPU is not executing instructions, the only exits from any of the Idle modes are by interrupt, WDT time-out or a Reset. When a wake event occurs, CPU execution is delayed by an interval of TCSD (parameter 38, Table 23-10) while it becomes ready to execute code. When the CPU begins executing code, it resumes with the same clock source for the current Idle mode. For example, when waking from RC\_IDLE mode, the internal oscillator block will clock the CPU and peripherals (in other words, RC\_RUN mode). The IDLEN and SCS bits are not affected by the wake-up.

While in any Idle mode or the Sleep mode, a WDT time-out will result in a WDT wake-up to the Run mode currently specified by the SCS1:SCS0 bits.

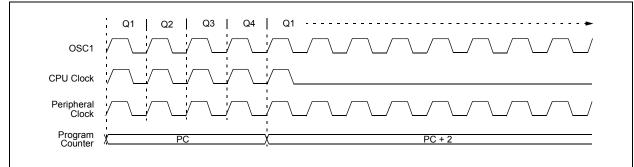

### 4.4.1 PRI\_IDLE MODE

This mode is unique among the three low-power Idle modes, in that it does not disable the primary device clock. For timing sensitive applications, this allows for the fastest resumption of device operation with its more accurate primary clock source, since the clock source does not have to "warm-up" or transition from another oscillator.

PRI\_IDLE mode is entered from PRI\_RUN mode by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, set IDLEN first, then clear the SCS bits and execute SLEEP. Although the CPU is disabled, the peripherals continue to be clocked from the primary clock source specified by the FOSC3:FOSC0 Configuration bits. The OSTS bit remains set (see Figure 4-7).

When a wake event occurs, the CPU is clocked from the primary clock source. A delay of interval TCSD is required between the wake event and when code execution starts. This is required to allow the CPU to become ready to execute instructions. After the wake-up, the OSTS bit remains set. The IDLEN and SCS bits are not affected by the wake-up (see Figure 4-8).

### 4.4.2 SEC\_IDLE MODE

In SEC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the Timer1 oscillator. This mode is entered from SEC\_RUN by

setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, set the IDLEN bit first, then set the SCS1:SCS0 bits to '01' and execute SLEEP. When the clock source is switched to the Timer1 oscillator, the primary oscillator is shut down, the OSTS bit is cleared and the T1RUN bit is set.

When a wake event occurs, the peripherals continue to be clocked from the Timer1 oscillator. After an interval of TCSD following the wake event, the CPU begins executing code being clocked by the Timer1 oscillator. The IDLEN and SCS bits are not affected by the wake-up; the Timer1 oscillator continues to run (see Figure 4-8).

Note: The Timer1 oscillator should already be running prior to entering SEC\_IDLE mode. If the T1OSCEN bit is not set when the SLEEP instruction is executed, the SLEEP instruction will be ignored and entry to SEC\_IDLE mode will not occur. If the Timer1 oscillator is enabled but not yet running, peripheral clocks will be delayed until the oscillator has started. In such situations, initial oscillator operation is far from stable and unpredictable operation may result.

## FIGURE 4-7: TRANSITION TIMING FOR ENTRY TO IDLE MODE

#### FIGURE 4-8: TRANSITION TIMING FOR WAKE FROM IDLE TO RUN MODE

| ABLE 5-4:           |      | LIZATIO       | N CONDITIONS FOR                   | ALL REGISTERS (CONT                                              |                                 |

|---------------------|------|---------------|------------------------------------|------------------------------------------------------------------|---------------------------------|

| Register            |      | cable<br>ices | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |

| INDF2               | 1230 | 1330          | N/A                                | N/A                                                              | N/A                             |

| POSTINC2            | 1230 | 1330          | N/A                                | N/A                                                              | N/A                             |

| POSTDEC2            | 1230 | 1330          | N/A                                | N/A                                                              | N/A                             |

| PREINC2             | 1230 | 1330          | N/A                                | N/A                                                              | N/A                             |

| PLUSW2              | 1230 | 1330          | N/A                                | N/A                                                              | N/A                             |

| FSR2H               | 1230 | 1330          | 0000                               | 0000                                                             | uuuu                            |

| FSR2L               | 1230 | 1330          | XXXX XXXX                          | uuuu uuuu                                                        | uuuu uuuu                       |

| STATUS              | 1230 | 1330          | x xxxx                             | u uuuu                                                           | u uuuu                          |

| TMR0H               | 1230 | 1330          | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |

| TMR0L               | 1230 | 1330          | XXXX XXXX                          | սսսս սսսս                                                        | uuuu uuuu                       |

| TOCON               | 1230 | 1330          | 1111 1111                          | 1111 1111                                                        | uuuu uuuu                       |

| OSCCON              | 1230 | 1330          | 0100 q000                          | 0100 q000                                                        | uuuu uuqu                       |

| LVDCON              | 1230 | 1330          | 00 0101                            | 00 0101                                                          | uu uuuu                         |

| WDTCON              | 1230 | 1330          | 0                                  | 0                                                                | u                               |

| RCON <sup>(4)</sup> | 1230 | 1330          | 0q-1 11q0                          | 0q-q qquu                                                        | uq-u qquu                       |

| TMR1H               | 1230 | 1330          | xxxx xxxx                          | սսսս սսսս                                                        | uuuu uuuu                       |

| TMR1L               | 1230 | 1330          | XXXX XXXX                          | սսսս սսսս                                                        | uuuu uuuu                       |

| T1CON               | 1230 | 1330          | 0000 0000                          | սՕսս սսսս                                                        | սսսս սսսս                       |

| ADRESH              | 1230 | 1330          | XXXX XXXX                          | սսսս սսսս                                                        | uuuu uuuu                       |

| ADRESL              | 1230 | 1330          | XXXX XXXX                          | սսսս սսսս                                                        | uuuu uuuu                       |

| ADCON0              | 1230 | 1330          | 0 0000                             | 0 0000                                                           | u uuuu                          |

| ADCON1              | 1230 | 1330          | 0 1111                             | 0 1111                                                           | u uuuu                          |

| ADCON2              | 1230 | 1330          | 0-00 0000                          | 0-00 0000                                                        | u-uu uuuu                       |

| BAUDCON             | 1230 | 1330          | 01-00 0-00                         | 01-00 0-00                                                       | uu-uu u-uu                      |

| CVRCON              | 1230 | 1330          | 0-00 0000                          | 0-00 0000                                                        | u-uu uuuu                       |

| CMCON               | 1230 | 1330          | 000000                             | 000000                                                           | uuuuuu                          |

| SPBRGH              | 1230 | 1330          | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |

| SPBRG               | 1230 | 1330          | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |

| RCREG               | 1230 | 1330          | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |

| TXREG               | 1230 | 1330          | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |

| TXSTA               | 1230 | 1330          | 0000 0010                          | 0000 0010                                                        | uuuu uuuu                       |

| RCSTA               | 1230 | 1330          | 0000 000x                          | 0000 000x                                                        | uuuu uuuu                       |

## TABLE 5-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- **2:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 5-3 for Reset value for specific condition.

- **5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read as '0'.

- 6: Reset condition of PWMEN bits depends on the PWMPIN Configuration bit of CONFIG3L.

### 6.3.4 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. SFRs start at the top of data memory (FFFh) and extend downward to occupy the top half of Bank 15 (F80h to FFFh). A list of these registers is given in Table 6-1 and Table 6-2. The SFRs can be classified into two sets: those associated with the "core" device functionality (ALU, Resets and interrupts) and those related to the peripheral functions. The Reset and Interrupt registers are described in their respective chapters, while the ALU's STATUS register is described later in this section. Registers related to the operation of a peripheral feature are described in the chapter for that peripheral.

The SFRs are typically distributed among the peripherals whose functions they control. Unused SFR locations are unimplemented and read as '0's.

| Address | Name                    | Address | Name                    | Address | Name                  | Address | Name      |

|---------|-------------------------|---------|-------------------------|---------|-----------------------|---------|-----------|

| FFFh    | TOSU                    | FDFh    | INDF2 <sup>(1)</sup>    | FBFh    | (2)                   | F9Fh    | IPR1      |

| FFEh    | TOSH                    | FDEh    | POSTINC2 <sup>(1)</sup> | FBEh    | (2)                   | F9Eh    | PIR1      |

| FFDh    | TOSL                    | FDDh    | POSTDEC2 <sup>(1)</sup> | FBDh    | (2)                   | F9Dh    | PIE1      |

| FFCh    | STKPTR                  | FDCh    | PREINC2 <sup>(1)</sup>  | FBCh    | (2)                   | F9Ch    | (2)       |

| FFBh    | PCLATU                  | FDBh    | PLUSW2 <sup>(1)</sup>   | FBBh    | (2)                   | F9Bh    | OSCTUNE   |

| FFAh    | PCLATH                  | FDAh    | FSR2H                   | FBAh    | (2)                   | F9Ah    | PTCON0    |

| FF9h    | PCL                     | FD9h    | FSR2L                   | FB9h    | (2)                   | F99h    | PTCON1    |

| FF8h    | TBLPTRU                 | FD8h    | STATUS                  | FB8h    | BAUDCON               | F98h    | PTMRL     |

| FF7h    | TBLPTRH                 | FD7h    | TMR0H                   | FB7h    | (2)                   | F97h    | PTMRH     |

| FF6h    | TBLPTRL                 | FD6h    | TMR0L                   | FB6h    | (2)                   | F96h    | PTPERL    |

| FF5h    | TABLAT                  | FD5h    | T0CON                   | FB5h    | CVRCON                | F95h    | PTPERH    |

| FF4h    | PRODH                   | FD4h    | (2)                     | FB4h    | CMCON                 | F94h    | (2)       |

| FF3h    | PRODL                   | FD3h    | OSCCON                  | FB3h    | (2)                   | F93h    | TRISB     |

| FF2h    | INTCON                  | FD2h    | LVDCON                  | FB2h    | (2)                   | F92h    | TRISA     |

| FF1h    | INTCON2                 | FD1h    | WDTCON                  | FB1h    | (2)                   | F91h    | PDC0L     |

| FF0h    | INTCON3                 | FD0h    | RCON                    | FB0h    | SPBRGH                | F90h    | PDC0H     |

| FEFh    | INDF0 <sup>(1)</sup>    | FCFh    | TMR1H                   | FAFh    | SPBRG                 | F8Fh    | PDC1L     |

| FEEh    | POSTINC0 <sup>(1)</sup> | FCEh    | TMR1L                   | FAEh    | RCREG                 | F8Eh    | PDC1H     |

| FEDh    | POSTDEC0 <sup>(1)</sup> | FCDh    | T1CON                   | FADh    | TXREG                 | F8Dh    | PDC2L     |

| FECh    | PREINC0 <sup>(1)</sup>  | FCCh    | (2)                     | FACh    | TXSTA                 | F8Ch    | PDC2H     |

| FEBh    | PLUSW0 <sup>(1)</sup>   | FCBh    | (2)                     | FABh    | RCSTA                 | F8Bh    | FLTCONFIG |

| FEAh    | FSR0H                   | FCAh    | (2)                     | FAAh    | (2)                   | F8Ah    | LATB      |

| FE9h    | FSR0L                   | FC9h    | (2)                     | FA9h    | EEADR                 | F89h    | LATA      |

| FE8h    | WREG                    | FC8h    | (2)                     | FA8h    | EEDATA                | F88h    | SEVTCMPL  |

| FE7h    | INDF1 <sup>(1)</sup>    | FC7h    | (2)                     | FA7h    | EECON2 <sup>(1)</sup> | F87h    | SEVTCMPH  |

| FE6h    | POSTINC1 <sup>(1)</sup> | FC6h    | (2)                     | FA6h    | EECON1                | F86h    | PWMCON0   |

| FE5h    | POSTDEC1 <sup>(1)</sup> | FC5h    | (2)                     | FA5h    | IPR3                  | F85h    | PWMCON1   |

| FE4h    | PREINC1 <sup>(1)</sup>  | FC4h    | ADRESH                  | FA4h    | PIR3                  | F84h    | DTCON     |

| FE3h    | PLUSW1 <sup>(1)</sup>   | FC3h    | ADRESL                  | FA3h    | PIE3                  | F83h    | OVDCOND   |

| FE2h    | FSR1H                   | FC2h    | ADCON0                  | FA2h    | IPR2                  | F82h    | OVDCONS   |

| FE1h    | FSR1L                   | FC1h    | ADCON1                  | FA1h    | PIR2                  | F81h    | PORTB     |

| FE0h    | BSR                     | FC0h    | ADCON2                  | FA0h    | PIE2                  | F80h    | PORTA     |

TABLE 6-1:SPECIAL FUNCTION REGISTER MAP FOR PIC18F1230/1330 DEVICES

**Note 1:** This is not a physical register.

2: Unimplemented registers are read as '0'.

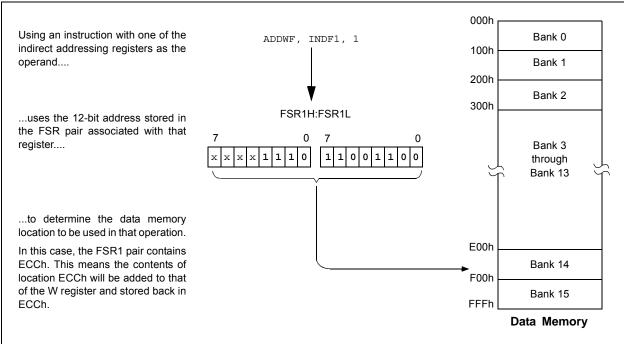

# 6.4.3.1 FSR Registers and the INDF Operand

At the core of Indirect Addressing are three sets of registers: FSR0, FSR1 and FSR2. Each represents a pair of 8-bit registers, FSRnH and FSRnL. The four upper bits of the FSRnH register are not used so each FSR pair holds a 12-bit value. This represents a value that can address the entire range of the data memory in a linear fashion. The FSR register pairs, then, serve as pointers to data memory locations.

Indirect Addressing is accomplished with a set of Indirect File Operands, INDF0 through INDF2. These can be thought of as "virtual" registers: they are mapped in the SFR space but are not physically implemented. Reading or writing to a particular INDF register actually accesses its corresponding FSR register pair. A read from INDF1, for example, reads the data at the address indicated by FSR1H:FSR1L. Instructions that use the INDF registers as operands actually use the contents of their corresponding FSR as a pointer to the instruction's target. The INDF operand is just a convenient way of using the pointer.

Because Indirect Addressing uses a full 12-bit address, data RAM banking is not necessary. Thus, the current contents of the BSR and the Access RAM bit have no effect on determining the target address.

## 6.4.3.2 FSR Registers and POSTINC, POSTDEC, PREINC and PLUSW

In addition to the INDF operand, each FSR register pair also has four additional indirect operands. Like INDF, these are "virtual" registers that cannot be indirectly read or written to. Accessing these registers actually accesses the associated FSR register pair, but also performs a specific action on its stored value. They are:

- POSTDEC: accesses the FSR value, then automatically decrements it by 1 afterwards

- POSTINC: accesses the FSR value, then automatically increments it by 1 afterwards

- PREINC: increments the FSR value by 1, then uses it in the operation

- PLUSW: adds the signed value of the W register (range of -127 to 128) to that of the FSR and uses the new value in the operation.

In this context, accessing an INDF register uses the value in the FSR registers without changing them. Similarly, accessing a PLUSW register gives the FSR value offset by that in the W register; neither value is actually changed in the operation. Accessing the other virtual registers changes the value of the FSR registers.

Operations on the FSRs with POSTDEC, POSTINC and PREINC affect the entire register pair; that is, rollovers of the FSRnL register from FFh to 00h carry over to the FSRnH register. On the other hand, results of these operations do not change the value of any flags in the STATUS register (e.g., Z, N, OV, etc.).

## FIGURE 6-7: INDIRECT ADDRESSING

| R/W-x         | R/W-x                | U-0                                                                               | R/W-0                        | R/W-x                | R/W-0            | R/S-0           | R/S-0           |

|---------------|----------------------|-----------------------------------------------------------------------------------|------------------------------|----------------------|------------------|-----------------|-----------------|

| EEPGD         | CFGS                 |                                                                                   | FREE                         | WRERR <sup>(1)</sup> | WREN             | WR              | RD              |

| bit 7         |                      |                                                                                   |                              |                      |                  |                 | bit 0           |

| Legend:       |                      | S = Settable                                                                      | oit                          |                      |                  |                 |                 |

| R = Readable  | e bit                | W = Writable                                                                      | bit                          | U = Unimpler         | nented bit, read | d as '0'        |                 |

| -n = Value at | POR                  | '1' = Bit is set                                                                  |                              | '0' = Bit is cle     | ared             | x = Bit is unkr | nown            |

| bit 7         |                      | ash Program or I                                                                  |                              | M Memory Sele        | ct bit           |                 |                 |

|               |                      | Flash program                                                                     | •                            |                      |                  |                 |                 |

| bit 6         | CFGS: Flas           | h Program/Data                                                                    | EEPROM or                    | Configuration S      | Select bit       |                 |                 |

|               |                      | Configuration re<br>Flash program                                                 |                              | ROM memory           |                  |                 |                 |

| bit 5         | Unimpleme            | ented: Read as '                                                                  | 0'                           | -                    |                  |                 |                 |

| bit 4         | FREE: Flas           | h Row Erase En                                                                    | able bit                     |                      |                  |                 |                 |

|               |                      | he program mer<br>d by completion<br>n write-only                                 |                              |                      | TR on the nex    | t WR command    |                 |

| bit 3         |                      | EPROM Error FI                                                                    | ag bit <sup>(1)</sup>        |                      |                  |                 |                 |

|               | 1 = A write<br>(MCLR | operation is pre<br>or WDT Reset of<br>ite operation con                          | maturely term                |                      | gram operation   | n)              |                 |

| bit 2         |                      | se/Write Enable                                                                   |                              |                      |                  |                 |                 |

|               |                      | erase/write cycle<br>erase/write cycl                                             |                              |                      |                  |                 |                 |

| bit 1         | WR: Write            | Control bit                                                                       |                              |                      |                  |                 |                 |

|               | (The op<br>The Wi    | s a data EEPROI<br>peration is self-tin<br>R bit can only be<br>ycle to is comple | ned and the<br>set (not clea | bit is cleared by    | hardware once    |                 |                 |

| bit 0         | RD: Read C           |                                                                                   |                              |                      |                  |                 |                 |

|               | 1 = Initiates        | s a memory read.<br>t cleared) in softw                                           |                              |                      |                  |                 | bit can only be |

|               |                      | t cleared) in softw                                                               |                              |                      |                  |                 |                 |

#### REGISTER 8-1: EECON1: EEPROM CONTROL REGISTER 1

Note 1: When a WRERR occurs, the EEPGD or FREE bit is not cleared. This allows tracing of the error condition.

# TABLE 10-1: PORTA I/O SUMMARY

| Pin             | Function             | TRIS<br>Setting | I/O | I/O<br>Type | Description                                                                                         |

|-----------------|----------------------|-----------------|-----|-------------|-----------------------------------------------------------------------------------------------------|

| RA0/AN0/INT0/   | RA0                  | 0               | 0   | DIG         | LATA<0> data output; not affected by analog input.                                                  |

| KBI0/CMP0       |                      | 1               | I   | TTL         | PORTA<0> data input; disabled when analog input enabled.                                            |

|                 | AN0                  | 1               | I   | ANA         | Analog input 0.                                                                                     |

|                 | INT0                 | 1               | I   | ST          | External interrupt 0.                                                                               |

|                 | KBI0                 | 1               | I   | TTL         | Interrupt-on-change pin.                                                                            |

|                 | CMP0                 | 1               | I   | ANA         | Comparator 0 input.                                                                                 |

| RA1/AN1/INT1/   | RA1                  | 0               | 0   | DIG         | LATA<1> data output; not affected by analog input.                                                  |

| KBI1            |                      | 1               | I   | TTL         | PORTA<1> data input; disabled when analog input enabled.                                            |

|                 | AN1                  | 1               | I   | ANA         | Analog input 1.                                                                                     |

|                 | INT1                 | 1               | I   | ST          | External interrupt 1.                                                                               |

|                 | KBI1                 | 1               | Ι   | TTL         | Interrupt-on-change pin.                                                                            |

| RA2/TX/CK       | RA2                  | 0               | 0   | DIG         | LATA<2> data output; not affected by analog input. Disabled when CVREF output enabled.              |

|                 |                      | 1               | Ι   | TTL         | PORTA<2> data input. Disabled when analog functions enabled;<br>disabled when CVREF output enabled. |

|                 | TX                   | 0               | 0   | DIG         | EUSART asynchronous transmit.                                                                       |

|                 | СК                   | 0               | 0   | DIG         | EUSART synchronous clock.                                                                           |

|                 |                      | 1               | Ι   | ST          |                                                                                                     |

| RA3/RX/DT       | RA3                  | 0               | 0   | DIG         | LATA<3> data output; not affected by analog input.                                                  |

|                 |                      | 1               | Ι   | TTL         | PORTA<3> data input; disabled when analog input enabled.                                            |

| -               | RX                   | 1               | Ι   | ANA         | EUSART asynchronous receive.                                                                        |

|                 | DT                   | 0               | 0   | DIG         | EUSART synchronous data.                                                                            |

|                 |                      | 1               | Ι   | TTL         |                                                                                                     |

| RA4/T0CKI/AN2/  | RA4                  | 0               | 0   | DIG         | LATA<4> data output.                                                                                |

| VREF+           |                      | 1               | I   | ST          | PORTA<4> data input; default configuration on POR.                                                  |

|                 | TOCKI                | 1               | Ι   | ST          | Timer0 external clock input.                                                                        |

|                 | AN2                  | 1               | Ι   | ANA         | Analog input 2.                                                                                     |

|                 | VREF+                | 1               | Ι   | ANA         | A/D reference voltage (high) input.                                                                 |

| MCLR/Vpp/RA5/   | MCLR                 | 1               | Ι   | ST          | Master Clear (Reset) input. This pin is an active-low Reset to the device                           |

| FLTA            | Vpp                  | 1               | I   | ANA         | Programming voltage input.                                                                          |

|                 | RA5                  | 1               | Ι   | ST          | Digital input.                                                                                      |

|                 | FLTA <sup>(1)</sup>  | 1               | I   | ST          | Fault detect input for PWM.                                                                         |

| RA6/OSC2/CLKO/  | RA6                  | 0               | 0   | DIG         | LATA<6> data output. Enabled in RCIO, INTIO2 and ECIO modes only                                    |

| T1OSO/T1CKI/AN3 |                      | 1               | I   | ST          | PORTA<6> data input. Enabled in RCIO, INTIO2 and ECIO modes only                                    |

|                 | OSC2                 | 0               | 0   | ANA         | Oscillator crystal output or external clock source output.                                          |

|                 | CLKO                 | 0               | 0   | ANA         | Oscillator crystal output.                                                                          |

|                 | T10SO <sup>(2)</sup> | 0               | 0   | ANA         | Timer1 oscillator output.                                                                           |

|                 | T1CKI <sup>(2)</sup> | 1               | I   | ST          | Timer1 clock input.                                                                                 |

|                 | AN3                  | 1               | I   | ANA         | Analog input 3.                                                                                     |

| RA7/OSC1/CLKI/  | RA7                  | 0               | 0   | DIG         | LATA<7> data output. Disabled in external oscillator modes.                                         |

| T1OSI/FLTA      |                      | 1               | I   | TTL         | PORTA<7> data input. Disabled in external oscillator modes.                                         |

|                 | OSC1                 | 1               | I   | ANA         | Oscillator crystal input or external clock source input.                                            |

|                 | CLKI                 | 1               | I   | ANA         | External clock source input.                                                                        |

|                 | T10SI <sup>(2)</sup> | 1               | I   | ANA         | Timer1 oscillator input.                                                                            |

|                 | FLTA <sup>(1)</sup>  |                 |     | 1           |                                                                                                     |

Legend: DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: Placement of FLTA depends on the value of Configuration bit, FLTAMX, of CONFIG3H.

2: Placement of T1OSI and T1OSO/T1CKI depends on the value of Configuration bit, T1OSCMX, of CONFIG3H.

# 13.0 TIMER1 MODULE

The Timer1 timer/counter module has the following features:

- 16-bit timer/counter (two 8-bit registers; TMR1H and TMR1L)

- Readable and writable (both registers)

- · Internal or external clock select

- Interrupt on overflow from FFFFh to 0000h

- · Status of system clock operation

Figure 13-1 is a simplified block diagram of the Timer1 module.

Register 13-1 details the Timer1 Control register. This register controls the operating mode of the Timer1 module and contains the Timer1 Oscillator Enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

The Timer1 oscillator can be used as a secondary clock source in power-managed modes. When the T1RUN bit is set, the Timer1 oscillator provides the system clock. If the Fail-Safe Clock Monitor is enabled and the Timer1 oscillator fails while providing the system clock, polling the T1RUN bit will indicate whether the clock is being provided by the Timer1 oscillator or another source.

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

### REGISTER 13-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0 | R-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|---------|---------|---------|--------|--------|--------|

| RD16  | T1RUN | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |       |         |         |         |        |        | bit 0  |

| Legend:      |                |                                                                |                                                 |                               |

|--------------|----------------|----------------------------------------------------------------|-------------------------------------------------|-------------------------------|

| R = Readab   | le bit         | W = Writable bit                                               | U = Unimplemented bit,                          | read as '0'                   |

| -n = Value a | t POR          | '1' = Bit is set                                               | '0' = Bit is cleared                            | x = Bit is unknown            |

| bit 7        | <b>RD16:</b> 1 | 6-Bit Read/Write Mode Enabl                                    | le bit                                          |                               |

|              | 1 = Ena        | bles register read/write of Tin                                | ner1 in one 16-bit operation                    |                               |

|              | 0 = Ena        | bles register read/write of Tin                                | ner1 in two 8-bit operations                    |                               |

| bit 6        | T1RUN:         | Timer1 System Clock Status                                     | bit                                             |                               |

|              |                | rice clock is derived from Time                                |                                                 |                               |

|              |                | rice clock is derived from anot                                |                                                 |                               |

| bit 5-4      |                | S1:T1CKPS0: Timer1 Input C                                     | lock Prescale Select bits                       |                               |

|              |                | Prescale value                                                 |                                                 |                               |

|              |                | Prescale value<br>Prescale value                               |                                                 |                               |

|              |                | Prescale value                                                 |                                                 |                               |

| bit 3        | T1OSCE         | EN: Timer1 Oscillator Enable                                   | bit                                             |                               |

|              | 1 = Time       | er1 oscillator is enabled                                      |                                                 |                               |

|              |                | er1 oscillator is shut off                                     |                                                 |                               |

|              |                | -                                                              | esistor are turned off to elimin                | ate power drain.              |

| bit 2        |                | : Timer1 External Clock Inpu                                   | t Synchronization Select bit                    |                               |

|              | -              | $\frac{MR1CS = 1}{2}$                                          | - inn4                                          |                               |

|              |                | ot synchronize external clock<br>chronize external clock input | input                                           |                               |

|              |                | MR1CS = 0:                                                     |                                                 |                               |

|              | This bit i     | s ignored. Timer1 uses the in                                  | ternal clock when TMR1CS =                      | 0.                            |

| bit 1        | TMR1CS         | S: Timer1 Clock Source Select                                  | ct bit                                          |                               |

|              | 1 = Exte       | ernal clock from T1OSO/T1Cl                                    | <i (on="" edge)<sup="" rising="" the="">(1)</i> |                               |

|              | 0 = Inte       | rnal clock (Fosc/4)                                            |                                                 |                               |

| bit 0        | TMR10          | N: Timer1 On bit                                               |                                                 |                               |

|              |                | ıbles Timer1<br>os Timer1                                      |                                                 |                               |

| Note 1. Pla  | coment of T1   | OSI and T1OSO/T1CKI depen                                      | ids on the value of the Configur                | ation bit. T1OSCMX. of CONFIG |

Note 1: Placement of T1OSI and T1OSO/T1CKI depends on the value of the Configuration bit, T1OSCMX, of CONFIG3H.

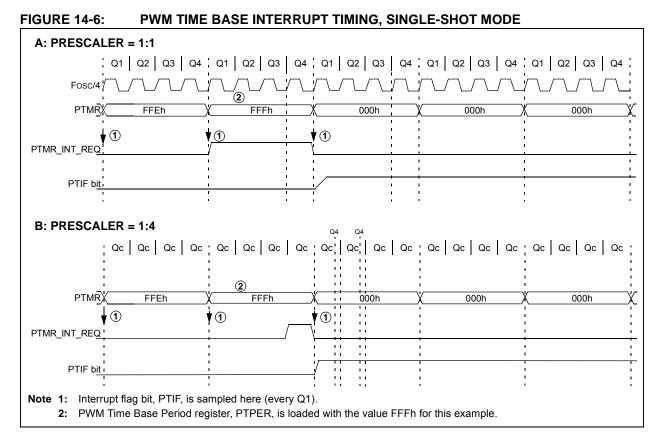

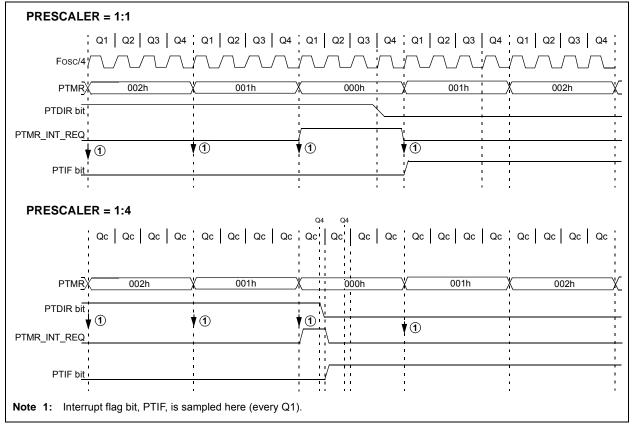

#### FIGURE 14-7: PWM TIME BASE INTERRUPTS, CONTINUOUS UP/DOWN COUNT MODE

© 2009 Microchip Technology Inc.

### 14.10.3 OUTPUT OVERRIDE EXAMPLES

Figure 14-21 shows an example of a waveform that might be generated using the PWM output override feature. The figure shows a six-step commutation sequence for a BLDC motor. The motor is driven through a 3-phase inverter as shown in Figure 14-16. When the appropriate rotor position is detected, the PWM outputs are switched to the next commutation state in the sequence. In this example, the PWM outputs are driven to specific logic states. The OVDCOND and OVDCONS register values used to generate the signals in Figure 14-21 are given in Table 14-4. The PWM Duty Cycle registers may be used in conjunction with the OVDCOND and OVDCONS registers. The Duty Cycle registers control the average voltage across the load and the OVDCOND and OVDCONS registers control the commutation sequence. Figure 14-22 shows the waveforms, while Table 14-4 and Table 14-5 show the OVDCOND and OVDCONS register values used to generate the signals.

# REGISTER 14-6: OVDCOND: OUTPUT OVERRIDE CONTROL REGISTER

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| _     | —   | POVD5 | POVD4 | POVD3 | POVD2 | POVD1 | POVD0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0 POVD5:POVD0: PWM Output Override bits

1 = Output on PWM I/O pin is controlled by the value in the Duty Cycle register and the PWM time base 0 = Output on PWM I/O pin is controlled by the value in the corresponding POUTx bit

## REGISTER 14-7: OVDCONS: OUTPUT STATE REGISTER

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0 POUT5:POUT0: PWM Manual Output bits<sup>(1)</sup>

1 = Output on PWM I/O pin is active when the corresponding PWM output override bit is cleared 0 = Output on PWM I/O pin is inactive when the corresponding PWM output override bit is cleared

**Note 1:** With PWMs configured in complementary mode, even PWM (PWM0, 2, 4) outputs will be complementary of the odd PWM (PWM1, 3, 5) outputs, irrespective of the POUT bit setting.

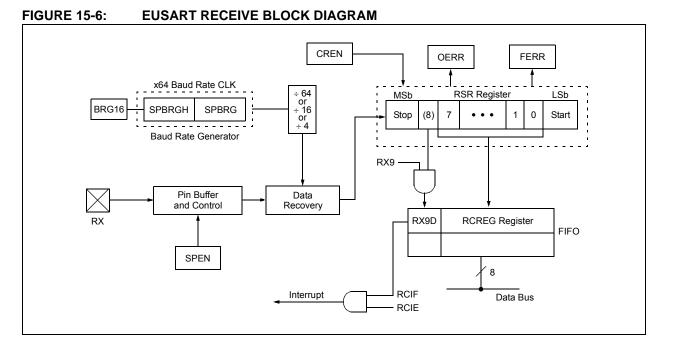

### 15.2.2 EUSART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 15-6. The data is received on the RX pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc. This mode would typically be used in RS-232 systems.

To set up an Asynchronous Reception:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, set enable bit RCIE.

- 4. If 9-bit reception is desired, set bit RX9.

- 5. Enable the reception by setting bit CREN.

- Flag bit, RCIF, will be set when reception is complete and an interrupt will be generated if enable bit, RCIE, was set.

- Read the RCSTA register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

- 10. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

# 15.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are required, set the RCEN bit and select the desired priority level with the RCIP bit.

- 4. Set the RX9 bit to enable 9-bit reception.

- 5. Set the ADDEN bit to enable address detect.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF bit will be set when reception is complete. The interrupt will be Acknowledged if the RCIE and GIE bits are set.

- 8. Read the RCSTA register to determine if any error occurred during reception, as well as read bit 9 of data (if applicable).

- 9. Read RCREG to determine if the device is being addressed.

- 10. If any error occurred, clear the CREN bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and interrupt the CPU.

# 17.0 COMPARATOR MODULE

The analog comparator module contains three comparators. The inputs can be selected from the analog inputs multiplexed with pins RA0, RB2 and RB3, as well as the on-chip voltage reference (see

Section 18.0 "Comparator Voltage Reference Module"). The digital outputs are not available at the pin level and can only be read through the control register, CMCON (Register 17-1). CMCON also selects the comparator input.

#### REGISTER 17-1: CMCON: COMPARATOR CONTROL REGISTER

| R-0   | R-0   | R-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----|-----|-------|-------|-------|

| C2OUT | C1OUT | COOUT | —   | —   | CMEN2 | CMEN1 | CMEN0 |

| bit 7 |       |       |     |     |       |       | bit 0 |

| Legend:    |          |                                                                            |                        |                    |

|------------|----------|----------------------------------------------------------------------------|------------------------|--------------------|

| R = Read   | able bit | W = Writable bit                                                           | U = Unimplemented bit, | read as '0'        |

| -n = Value | at POR   | '1' = Bit is set                                                           | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7      | 1 = C2 V | Comparator 2 Output bit<br>IN+ > C2 VIN- (CVREF)<br>IN+ < C2 VIN- (CVREF)  |                        |                    |

| bit 6      | 1 = C1 V | Comparator 1 Output bit<br>IN+ > C1 VIN- (CVREF)<br>IN+ < C1 VIN- (CVREF)- |                        |                    |

| hit E      | COOLIT   | Comporator 0 Output hit                                                    |                        |                    |

| bit 5   | COOUT: Comparator 0 Output bit  |

|---------|---------------------------------|

|         | 1 = CO VIN+ > CO VIN- (CVREF)   |

|         | 0 = C0 VIN + < C0 VIN - (CVREF) |

| bit 4-3 | Unimplemented: Read as '0'      |

| bit 2   | CMEN2: Comparator 2 Enable bit  |

|         | 1 = Comparator 2 is enabled     |

|         | 0 = Comparator 2 is disabled    |

| bit 1   | CMEN1: Comparator 1 Enable bit  |

|         | 1 = Comparator 1 is enabled     |

|         | 0 = Comparator 1 is disabled    |

| bit 0   | CMEN0: Comparator 0 Enable bit  |

|         |                                 |

- 1 =Comparator 0 is enabled

- 0 = Comparator 0 is disabled

| MULLW                                                          | Multiply                                                                                                       | Literal wit                                                                                                                                                    | h W                                                                         |                                                                     |   | MULWF                                                  |

|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------|---|--------------------------------------------------------|

| Syntax:                                                        | MULLW                                                                                                          | k                                                                                                                                                              |                                                                             |                                                                     |   | Syntax:                                                |

| Operands:                                                      | $0 \le k \le 25$                                                                                               | 5                                                                                                                                                              |                                                                             |                                                                     |   | Operands:                                              |

| Operation:                                                     | (W) x k $\rightarrow$                                                                                          | PRODH:PR                                                                                                                                                       | ODL                                                                         |                                                                     |   |                                                        |

| Status Affected:                                               | None                                                                                                           |                                                                                                                                                                |                                                                             |                                                                     |   | Operation:                                             |

| Encoding:                                                      | 0000                                                                                                           | 1101 }                                                                                                                                                         | kkk                                                                         | kkkk                                                                |   | Status Affected:                                       |

| Description:                                                   | out betwee<br>8-bit litera<br>placed in t<br>pair. PROI<br>W is unch<br>None of th<br>Note that<br>possible in | ed multiplica<br>en the conte<br>I 'k'. The 16-<br>the PRODH:<br>DH contains<br>anged.<br>ne Status flag<br>neither Over<br>n this operations<br>but not deter | nts of V<br>bit resu<br>PRODL<br>the hig<br>as are a<br>flow no<br>on. A Zo | V and the<br>lt is<br>register<br>h byte.<br>ffected.<br>r Carry is |   | Encoding:<br>Description:                              |

| Words:                                                         | 1                                                                                                              |                                                                                                                                                                |                                                                             |                                                                     |   |                                                        |

| Cycles:                                                        | 1                                                                                                              |                                                                                                                                                                |                                                                             |                                                                     |   |                                                        |

| Q Cycle Activity:                                              |                                                                                                                |                                                                                                                                                                |                                                                             |                                                                     |   |                                                        |

| Q1                                                             | Q2                                                                                                             | Q3                                                                                                                                                             |                                                                             | Q4                                                                  | 1 |                                                        |

| Decode                                                         | Read<br>literal 'k'                                                                                            | Process<br>Data                                                                                                                                                | re<br>Pl                                                                    | Write<br>egisters<br>RODH:<br>PRODL                                 |   |                                                        |

| Example:                                                       | MULLW                                                                                                          | 0C4h                                                                                                                                                           |                                                                             |                                                                     |   |                                                        |

| Before Instruc                                                 | tion                                                                                                           |                                                                                                                                                                |                                                                             |                                                                     |   |                                                        |

| W<br>PRODH<br>PRODL<br>After Instructio<br>W<br>PRODH<br>PRODL | = E<br>= ?<br>= ?<br>on<br>= E<br>= A                                                                          | 2h<br>2h<br>Dh<br>8h                                                                                                                                           |                                                                             |                                                                     |   | Words:<br>Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode |

|                                                                |                                                                                                                |                                                                                                                                                                |                                                                             |                                                                     |   | Example:                                               |

Multiply W with f MULWF f {,a}  $0 \leq f \leq 255$  $a \in [0,1]$ (W) x (f)  $\rightarrow$  PRODH:PRODL None ffff ffff 0000 001a An unsigned multiplication is carried out between the contents of W and the register file location 'f'. The 16-bit result is stored in the PRODH:PRODL register pair. PRODH contains the high byte. Both W and 'f' are unchanged. None of the Status flags are affected. Note that neither Overflow nor Carry is possible in this operation. A Zero result is possible but not detected. If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the GPR bank. If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See **Section 22.2.3** "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details. 1 1 Q2 Q3 Q4 Read Process Write register 'f' registers Data PRODH: PRODL REG, 1 MULWF **Before Instruction** W C4h = B5h ? REG = PRODH = PRODL = ? After Instruction W = C4h

B5h

8Ah

94h

=

=

=

REG

PRODH PRODL

# 22.2.5 SPECIAL CONSIDERATIONS WITH MICROCHIP MPLAB<sup>®</sup> IDE TOOLS

The latest versions of Microchip's software tools have been designed to fully support the extended instruction set of the PIC18F1230/1330 family of devices. This includes the MPLAB C18 C Compiler, MPASM Assembly language and MPLAB Integrated Development Environment (IDE).

When selecting a target device for software development, MPLAB IDE will automatically set default Configuration bits for that device. The default setting for the XINST Configuration bit is '0', disabling the extended instruction set and Indexed Literal Offset Addressing mode. For proper execution of applications developed to take advantage of the extended instruction set, XINST must be set during programming.

To develop software for the extended instruction set, the user must enable support for the instructions and the Indexed Addressing mode in their language tool(s). Depending on the environment being used, this may be done in several ways:

- A menu option, or dialog box within the environment, that allows the user to configure the language tool and its settings for the project

- · A command line option

- · A directive in the source code

These options vary between different compilers, assemblers and development environments. Users are encouraged to review the documentation accompanying their development systems for the appropriate information.

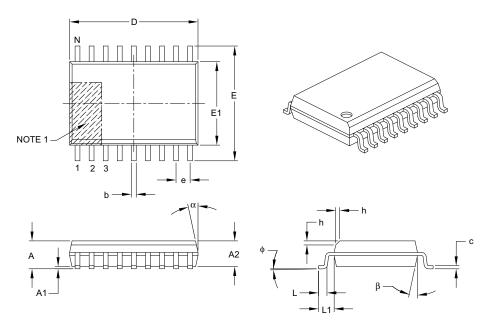

# 18-Lead Plastic Small Outline (SO) – Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |           | MILLIMETERS | 6    |

|--------------------------|------------------|-----------|-------------|------|

|                          | Dimension Limits | MIN       | NOM         | MAX  |

| Number of Pins           | N                |           | 18          |      |

| Pitch                    | е                |           | 1.27 BSC    |      |

| Overall Height           | А                | -         | -           | 2.65 |

| Molded Package Thickness | A2               | 2.05      | -           | -    |

| Standoff §               | A1               | 0.10      | -           | 0.30 |

| Overall Width            | E                |           | 10.30 BSC   |      |

| Molded Package Width     | E1               | 7.50 BSC  |             |      |

| Overall Length           | D                | 11.55 BSC |             |      |

| Chamfer (optional)       | h                | 0.25      | -           | 0.75 |

| Foot Length              | L                | 0.40      | -           | 1.27 |

| Footprint                | L1               | 1.40 REF  |             |      |

| Foot Angle               | φ                | 0°        | -           | 8°   |

| Lead Thickness           | С                | 0.20      | _           | 0.33 |

| Lead Width               | b                | 0.31      | -           | 0.51 |

| Mold Draft Angle Top     | α                | 5°        | -           | 15°  |

| Mold Draft Angle Bottom  | β                | 5°        | -           | 15°  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-051B

# APPENDIX B: DEVICE DIFFERENCES

The differences between the devices listed in this data sheet are shown in Table B-1.

# TABLE B-1: DEVICE DIFFERENCES

| Features                      | PIC18F1230                                              | PIC18F1330                                              |

|-------------------------------|---------------------------------------------------------|---------------------------------------------------------|

| Program Memory (Bytes)        | 4096                                                    | 8192                                                    |

| Program Memory (Instructions) | 2048                                                    | 4096                                                    |

| Packages                      | 18-Pin PDIP<br>18-Pin SOIC<br>20-Pin SSOP<br>28-Pin QFN | 18-Pin PDIP<br>18-Pin SOIC<br>20-Pin SSOP<br>28-Pin QFN |

| MOVLW                                         |     |

|-----------------------------------------------|-----|

| MOVWF                                         |     |

| MULLW                                         |     |

| MULWF                                         |     |

| NEGF                                          |     |

| NOP                                           |     |

| Opcode Field Descriptions                     |     |

| POP                                           | 244 |

| PUSH                                          |     |

| RCALL                                         |     |

| RESET                                         |     |

| RETFIE                                        |     |

| RETLW                                         |     |

| RETURN                                        | 247 |

| RLCF                                          |     |

| RLNCF                                         |     |

| RRCF                                          |     |

| RRNCF                                         |     |

| SETF                                          |     |

| SETF (Indexed Literal Offset Mode)            |     |

| SLEEP                                         |     |

| Standard Instructions                         |     |

| SUBFWB                                        |     |

| SUBLW                                         |     |

| SUBWF                                         |     |

| SUBWFB                                        |     |

| SWAPF                                         |     |

| TBLRD                                         |     |

| TBLWT                                         |     |

| TSTFSZ                                        |     |

| XORLW                                         |     |

| XORWF                                         |     |

| INTCON Registers                              |     |

| Internal Oscillator Block                     | 24  |

| Adjustment                                    | 24  |

| INTIO Modes                                   |     |

| INTOSC Frequency Drift                        |     |

| INTOSC Output Frequency                       |     |

| OSCTUNE Register                              |     |

| PLL in INTOSC Modes                           |     |

| Internal RC Oscillator                        |     |

| Use with WDT                                  |     |

| Internet Address                              |     |

| Interrupt Sources                             |     |

| A/D Conversion Complete                       |     |

| INTx Pin                                      |     |

| PORTB, Interrupt-on-Change                    |     |

| TMR0                                          |     |

| TMR1 Overflow                                 |     |

| Interrupts                                    |     |

| Interrupts, Flag Bits                         |     |

| Interrupt-on-Change Flag (RBIF Bit)           | 90  |

| INTOSC, INTRC. See Internal Oscillator Block. |     |

| IORLW                                         | 228 |

| IORWF                                         |     |

| IPR Registers                                 |     |

|                                               |     |

# L

| LFSR                                                | 220  |

|-----------------------------------------------------|------|

| Low-Voltage Detect                                  |      |

| Applications                                        |      |

|                                                     |      |

| Associated Registers                                |      |

| Characteristics                                     |      |

| Current Consumption                                 |      |

| Effects of a Reset                                  |      |

| Operation                                           |      |

| During Sleep                                        |      |

| Setup                                               |      |

| Start-up Time                                       |      |

| Typical Application                                 |      |

| Low-Voltage ICSP Programming. See Single-Supply     | ICSP |

| Programming                                         |      |

| LVD. See Low-Voltage Detect                         | 187  |

|                                                     |      |

| M                                                   |      |

| Master Clear (MCLR)                                 | 41   |

| Memory Organization                                 | 51   |

| Data Memory                                         | 57   |

| Program Memory                                      | 51   |

| Memory Programming Requirements                     | 281  |

| Microchip Internet Web Site                         |      |

| Migration from Baseline to Enhanced Devices         |      |

| Migration from High-End to Enhanced Devices         |      |

| Migration from Mid-Range to Enhanced Devices        |      |

| MOVF                                                |      |