Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 4x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

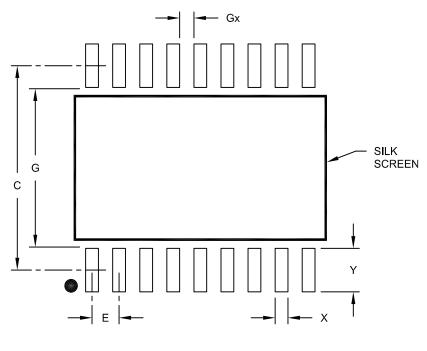

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f1330-e-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, PIC<sup>32</sup> logo, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2009, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL00® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

|                      | Pin Number                           |         |             | Pin     | Buffer |                                                     |

|----------------------|--------------------------------------|---------|-------------|---------|--------|-----------------------------------------------------|

| Pin Name             | Pin Name PDIP,<br>SOIC SSOP QFN Type |         | Description |         |        |                                                     |

| MCLR/Vpp/RA5/FLTA    | 4                                    | 4       | 1           |         |        | Master Clear (input), programming voltage (input)   |

|                      |                                      |         |             |         |        | or Fault detect input.                              |

| MCLR                 |                                      |         |             | I       | ST     | Master Clear (Reset) input. This pin is an          |

|                      |                                      |         |             |         |        | active-low Reset to the device.                     |

| VPP                  |                                      |         |             | I       | Analog | Programming voltage input.                          |

| RA5                  |                                      |         |             | I       | ST     | Digital input.                                      |

| FLTA <sup>(1)</sup>  |                                      |         |             | I       | ST     | Fault detect input for PWM.                         |

| RA7/OSC1/CLKI/       | 16                                   | 18      | 21          |         |        | Oscillator crystal, external clock input, Timer1    |

| T1OSI/FLTA           |                                      |         |             |         |        | oscillator input or Fault detect input.             |

| RA7                  |                                      |         |             | I/O     | ST     | Digital I/O.                                        |

| OSC1                 |                                      |         |             | I       | Analog | Oscillator crystal input or external clock source   |

|                      |                                      |         |             |         |        | input.                                              |

| CLKI                 |                                      |         |             | I       | —      | External clock source input.                        |

| T10SI <sup>(2)</sup> |                                      |         |             | I       | Analog | Timer1 oscillator input.                            |

| FLTA <sup>(1)</sup>  |                                      |         |             | I       | ST     | Fault detect input for PWM.                         |

| RA6/OSC2/CLKO/       | 15                                   | 17      | 20          |         |        | Oscillator crystal, clock output, Timer1 oscillator |

| T1OSO/T1CKI/AN3      |                                      |         |             |         |        | output or analog input.                             |

| RA6                  |                                      |         |             | I/O     | ST     | Digital I/O.                                        |

| OSC2                 |                                      |         |             | 0       | —      | Oscillator crystal output or external clock         |

|                      |                                      |         |             |         |        | source input.                                       |

| CLKO                 |                                      |         |             | 0       | —      | External clock source output.                       |

| T1OSO <sup>(2)</sup> |                                      |         |             | 0       | —      | Timer1 oscillator output.                           |

| TICKI <sup>(2)</sup> |                                      |         |             | I       | ST     | Timer1 clock input.                                 |

| AN3                  |                                      |         |             |         | Analog | Analog input 3.                                     |

| Legend: TTL = TTL co | ompatible                            | e input |             |         | СМС    | DS = CMOS compatible input or output                |

| ST = Schmit          | tt Trigger                           | input w | ith CMO     | S level | s I    | = Input                                             |

| O = Output           | t                                    |         |             |         | Р      | = Power                                             |

| TABLE 1-2: | PIC18F1230/1330 PINOUT I/O DESCRIPTIONS |

|------------|-----------------------------------------|

|            |                                         |

**Note 1:** Placement of FLTA depends on the value of Configuration bit, FLTAMX, of CONFIG3H.

2: Placement of T1OSI and T1OSO/T1CKI depends on the value of Configuration bit, T1OSCMX, of CONFIG3H.

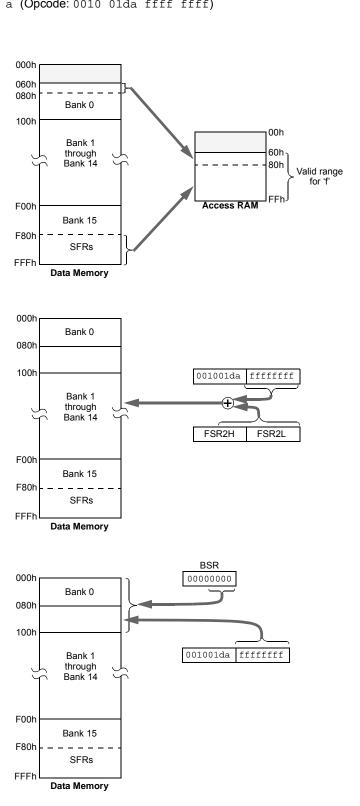

#### FIGURE 6-8: COMPARING ADDRESSING OPTIONS FOR BIT-ORIENTED AND BYTE-ORIENTED INSTRUCTIONS (EXTENDED INSTRUCTION SET ENABLED)

**EXAMPLE INSTRUCTION:** ADDWF, f, d, a (Opcode: 0010 01da ffff ffff)

#### When 'a' = 0 and $f \ge 60h$ :

The instruction executes in Direct Forced mode. 'f' is interpreted as a location in the Access RAM between 060h and 0FFh. This is the same as locations 060h to 07Fh (Bank 0) and F80h to FFFh (Bank 15) of data memory.

Locations below 60h are not available in this addressing mode.

#### When 'a' = 0 and $f \le 5Fh$ :

The instruction executes in Indexed Literal Offset mode. 'f' is interpreted as an offset to the address value in FSR2. The two are added together to obtain the address of the target register for the instruction. The address can be anywhere in the data memory space.

Note that in this mode, the correct syntax is now: ADDWF [k], d where 'k' is the same as 'f'.

#### When 'a' = 1 (all values of f):

The instruction executes in Direct mode (also known as Direct Long mode). 'f' is interpreted as a location in one of the 16 banks of the data memory space. The bank is designated by the Bank Select Register (BSR). The address can be in any implemented bank in the data memory space.

### 7.2.2 TABLAT – TABLE LATCH REGISTER

The Table Latch (TABLAT) is an 8-bit register mapped into the SFR space. The Table Latch register is used to hold 8-bit data during data transfers between program memory and data RAM.

#### 7.2.3 TBLPTR – TABLE POINTER REGISTER

The Table Pointer (TBLPTR) register addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL). These three registers join to form a 22-bit wide pointer. The low-order 21 bits allow the device to address up to 2 Mbytes of program memory space. The 22nd bit allows access to the device ID, the user ID and the Configuration bits.

The Table Pointer register, TBLPTR, is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways based on the table operation. These operations are shown in Table 7-1. These operations on the TBLPTR only affect the low-order 21 bits.

#### 7.2.4 TABLE POINTER BOUNDARIES

TBLPTR is used in reads, writes and erases of the Flash program memory.

When a TBLRD is executed, all 22 bits of the TBLPTR determine which byte is read from program memory into TABLAT.

When the timed write to program memory begins (via the WR bit), the 19 MSbs of the TBLPTR (TBLPTR<21:3>) determine which program memory block of 8 bytes is written to. The Table Pointer register's three LSBs (TBLPTR<2:0>) are ignored. For more detail, see Section 7.5 "Writing to Flash Program Memory".

When an erase of program memory is executed, the 16 MSbs of the Table Pointer register (TBLPTR<21:6>) point to the 64-byte block that will be erased. The Least Significant bits (TBLPTR<5:0>) are ignored.

Figure 7-3 describes the relevant boundaries of TBLPTR based on Flash program memory operations.

| TABLE 7-1: | TABLE POINTER OPERATIONS WITH TBLRD AND TBLWT INSTRUCTIONS |

|------------|------------------------------------------------------------|

|------------|------------------------------------------------------------|

| Example            | Operation on Table Pointer                  |

|--------------------|---------------------------------------------|

| TBLRD*<br>TBLWT*   | TBLPTR is not modified                      |

| TBLRD*+<br>TBLWT*+ | TBLPTR is incremented after the read/write  |

| TBLRD*-<br>TBLWT*- | TBLPTR is decremented after the read/write  |

| TBLRD+*<br>TBLWT+* | TBLPTR is incremented before the read/write |

#### FIGURE 7-3: TABLE POINTER BOUNDARIES BASED ON OPERATION

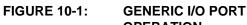

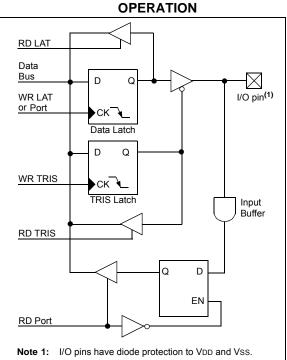

## 10.0 I/O PORTS

Depending on the device selected and features enabled, there are up to five ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three registers for its operation. These registers are:

- TRIS register (Data Direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (Output Latch register)

The Output Latch (LAT register) is useful for readmodify-write operations on the value that the I/O pins are driving.

A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 10-1.

## 10.1 PORTA, TRISA and LATA Registers

PORTA is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it, will write to the port latch.

The Output Latch (LATA) register is also memory mapped. Read-modify-write operations on the LATA register read and write the latched output value for PORTA.

Pins RA6 and RA7 are multiplexed with the main oscillator pins; they are enabled as oscillator or I/O pins by the selection of the main oscillator in the Configuration register (see **Section 20.1 "Configuration Bits"** for details). When they are not used as port pins, RA6 and RA7 and their associated TRIS and LAT bits are read as '0'.

The RA0 pin is multiplexed with one of the analog inputs, one of the external interrupt inputs, one of the interrupt-on-change inputs and one of the analog comparator inputs to become RA0/AN0/INT0/KBI0/CMP0 pin.

The RA1 pin is multiplexed with one of the analog inputs, one of the external interrupt inputs and one of the interrupt-on-change inputs to become RA1/AN1/ INT1/KBI1 pin.

Pins RA2 and RA3 are multiplexed with the Enhanced USART transmission and reception input (see **Section 20.1 "Configuration Bits"** for details).

The RA4 pin is multiplexed with the Timer0 module clock input, one of the analog inputs and the analog VREF+ input to become the RA4/T0CKI/AN2/VREF+ pin.

The Fault detect input for PWM FLTA is multiplexed with pins RA5 and RA7. Its placement is decided by clearing or setting the FLTAMX bit of Configuration Register 3H.

Note: On a Power-on Reset, RA0, RA1, RA4 and RA5 are configured as analog inputs and read as '0'. RA2 and RA3 are configured as digital inputs.

The TRISA register controls the direction of the PORTA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### EXAMPLE 10-1: INITIALIZING PORTA

| CLRF  | PORTA  | ; Initialize PORTA by<br>; clearing output |

|-------|--------|--------------------------------------------|

|       |        |                                            |

|       |        | ; data latches                             |

| CLRF  | LATA   | ; Alternate method                         |

|       |        | ; to clear output                          |

|       |        | ; data latches                             |

| MOVLW | 07h    | ; Configure A/D                            |

| MOVWF | ADCON1 | ; for digital inputs                       |

| MOVWF | 07h    | ; Configure comparators                    |

| MOVWF | CMCON  | ; for digital input                        |

| MOVLW | OCFh   | ; Value used to                            |

|       |        | ; initialize data                          |

|       |        | ; direction                                |

| MOVWF | TRISA  | ; Set RA<7:6,3:0> as inputs                |

|       |        | ; RA<5:4> as outputs                       |

|       |        |                                            |

## TABLE 10-1: PORTA I/O SUMMARY

| Pin             | Function             | TRIS<br>Setting | I/O | I/O<br>Type | Description                                                                                         |  |  |  |  |

|-----------------|----------------------|-----------------|-----|-------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|

| RA0/AN0/INT0/   | RA0                  | 0               | 0   | DIG         | LATA<0> data output; not affected by analog input.                                                  |  |  |  |  |

| KBI0/CMP0       |                      | 1               | I   | TTL         | PORTA<0> data input; disabled when analog input enabled.                                            |  |  |  |  |

|                 | AN0                  | 1               | I   | ANA         | Analog input 0.                                                                                     |  |  |  |  |

|                 | INT0                 | 1               | I   | ST          | External interrupt 0.                                                                               |  |  |  |  |

|                 | KBI0                 | 1               | I   | TTL         | Interrupt-on-change pin.                                                                            |  |  |  |  |

|                 | CMP0                 | 1               | I   | ANA         | Comparator 0 input.                                                                                 |  |  |  |  |

| RA1/AN1/INT1/   | RA1                  | 0               | 0   | DIG         | LATA<1> data output; not affected by analog input.                                                  |  |  |  |  |

| KBI1            |                      | 1               | I   | TTL         | PORTA<1> data input; disabled when analog input enabled.                                            |  |  |  |  |

|                 | AN1                  | 1               | I   | ANA         | Analog input 1.                                                                                     |  |  |  |  |

|                 | INT1                 | 1               | I   | ST          | External interrupt 1.                                                                               |  |  |  |  |

|                 | KBI1                 | 1               | Ι   | TTL         | Interrupt-on-change pin.                                                                            |  |  |  |  |

| RA2/TX/CK       | RA2                  | 0               | 0   | DIG         | LATA<2> data output; not affected by analog input. Disabled when CVREF output enabled.              |  |  |  |  |

|                 |                      | 1               | Ι   | TTL         | PORTA<2> data input. Disabled when analog functions enabled;<br>disabled when CVREF output enabled. |  |  |  |  |

|                 | TX                   | 0               | 0   | DIG         | EUSART asynchronous transmit.                                                                       |  |  |  |  |

|                 | СК                   | 0               | 0   | DIG         | EUSART synchronous clock.                                                                           |  |  |  |  |

|                 |                      | 1               | Ι   | ST          |                                                                                                     |  |  |  |  |

| RA3/RX/DT       | RA3                  | 0               | 0   | DIG         | LATA<3> data output; not affected by analog input.                                                  |  |  |  |  |

|                 |                      | 1               | Ι   | TTL         | PORTA<3> data input; disabled when analog input enabled.                                            |  |  |  |  |

|                 | RX                   | 1               | Ι   | ANA         | EUSART asynchronous receive.                                                                        |  |  |  |  |

|                 | DT                   | 0               | 0   | DIG         | EUSART synchronous data.                                                                            |  |  |  |  |

|                 |                      | 1               | Ι   | TTL         |                                                                                                     |  |  |  |  |

| RA4/T0CKI/AN2/  | RA4                  | 0               | 0   | DIG         | LATA<4> data output.                                                                                |  |  |  |  |

| VREF+           |                      | 1               | I   | ST          | PORTA<4> data input; default configuration on POR.                                                  |  |  |  |  |

|                 | TOCKI                | 1               | Ι   | ST          | Timer0 external clock input.                                                                        |  |  |  |  |

|                 | AN2                  | 1               | Ι   | ANA         | Analog input 2.                                                                                     |  |  |  |  |

|                 | VREF+                | 1               | Ι   | ANA         | A/D reference voltage (high) input.                                                                 |  |  |  |  |

| MCLR/Vpp/RA5/   | MCLR                 | 1               | Ι   | ST          | Master Clear (Reset) input. This pin is an active-low Reset to the device                           |  |  |  |  |

| FLTA            | Vpp                  | 1               | I   | ANA         | Programming voltage input.                                                                          |  |  |  |  |

|                 | RA5                  | 1               | Ι   | ST          | Digital input.                                                                                      |  |  |  |  |

|                 | FLTA <sup>(1)</sup>  | 1               | I   | ST          | Fault detect input for PWM.                                                                         |  |  |  |  |

| RA6/OSC2/CLKO/  | RA6                  | 0               | 0   | DIG         | LATA<6> data output. Enabled in RCIO, INTIO2 and ECIO modes only                                    |  |  |  |  |

| T1OSO/T1CKI/AN3 |                      | 1               | I   | ST          | PORTA<6> data input. Enabled in RCIO, INTIO2 and ECIO modes only                                    |  |  |  |  |

|                 | OSC2                 | 0               | 0   | ANA         | Oscillator crystal output or external clock source output.                                          |  |  |  |  |

|                 | CLKO                 | 0               | 0   | ANA         | Oscillator crystal output.                                                                          |  |  |  |  |

|                 | T10SO <sup>(2)</sup> | 0               | 0   | ANA         | Timer1 oscillator output.                                                                           |  |  |  |  |

|                 | T1CKI <sup>(2)</sup> | 1               | I   | ST          | Timer1 clock input.                                                                                 |  |  |  |  |

|                 | AN3                  | 1               | I   | ANA         | Analog input 3.                                                                                     |  |  |  |  |

| RA7/OSC1/CLKI/  | RA7                  | 0               | 0   | DIG         | LATA<7> data output. Disabled in external oscillator modes.                                         |  |  |  |  |

| T1OSI/FLTA      |                      | 1               | I   | TTL         | PORTA<7> data input. Disabled in external oscillator modes.                                         |  |  |  |  |

|                 | OSC1                 | 1               | I   | ANA         | Oscillator crystal input or external clock source input.                                            |  |  |  |  |

|                 | CLKI                 | 1               | I   | ANA         | External clock source input.                                                                        |  |  |  |  |

|                 | T10SI <sup>(2)</sup> | 1               | I   | ANA         | Timer1 oscillator input.                                                                            |  |  |  |  |

|                 | FLTA <sup>(1)</sup>  |                 |     | 1           |                                                                                                     |  |  |  |  |

Legend: DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: Placement of FLTA depends on the value of Configuration bit, FLTAMX, of CONFIG3H.

2: Placement of T1OSI and T1OSO/T1CKI depends on the value of Configuration bit, T1OSCMX, of CONFIG3H.

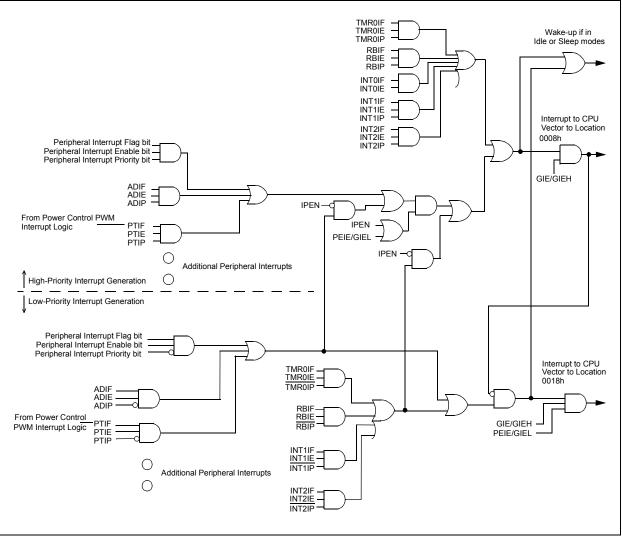

### 13.1 Timer1 Operation

Timer1 can operate in one of these modes:

- As a timer

- As a synchronous counter

- As an asynchronous counter

The operating mode is determined by the Clock Select bit, TMR1CS (T1CON<1>).

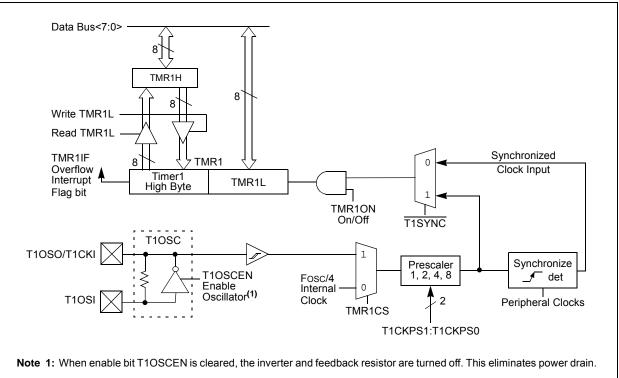

### FIGURE 13-1: TIMER1 BLOCK DIAGRAM

When TMR1CS = 0, Timer1 increments every instruction cycle. When TMR1CS = 1, Timer1 increments on every rising edge of the external clock input or the Timer1 oscillator, if enabled.

When the Timer1 oscillator is enabled (T1OSCEN is set), the T1OSI and T1OSO/T1CKI pins become inputs. That is, the corresponding TRISA bit value is ignored, and the pins are read as '0'.

### FIGURE 13-2: TIMER1 BLOCK DIAGRAM: 16-BIT READ/WRITE MODE

| RTCinit |        |              |                                               |

|---------|--------|--------------|-----------------------------------------------|

|         | MOVLW  | 0x80         | ; Preload TMR1 register pair                  |

|         | MOVWF  | TMR1H        | ; for 1 second overflow                       |

|         | CLRF   | TMR1L        |                                               |

|         | MOVLW  | b'00001111'  | ; Configure for external clock,               |

|         | MOVWF  | T1CON        | ; Asynchronous operation, external oscillator |

|         | CLRF   | secs         | ; Initialize timekeeping registers            |

|         | CLRF   | mins         | ;                                             |

|         | MOVLW  | .12          |                                               |

|         | MOVWF  | hours        |                                               |

|         | BSF    | PIE1, TMR1IE | ; Enable Timer1 interrupt                     |

|         | RETURN |              |                                               |

| RTCisr  |        |              |                                               |

|         | BSF    | TMR1H, 7     | ; Preload for 1 sec overflow                  |

|         | BCF    | PIR1, TMR11F | ; Clear interrupt flag                        |

|         | INCF   | secs, F      | ; Increment seconds                           |

|         | MOVLW  | .59          | ; 60 seconds elapsed?                         |

|         | CPFSGT | secs         |                                               |

|         | RETURN |              | ; No, done                                    |

|         | CLRF   | secs         | ; Clear seconds                               |

|         | INCF   | mins, F      | ; Increment minutes                           |

|         | MOVLW  | .59          | ; 60 minutes elapsed?                         |

|         | CPFSGT | mins         |                                               |

|         | RETURN |              | ; No, done                                    |

|         | CLRF   | mins         | ; clear minutes                               |

|         | INCF   | hours, F     | ; Increment hours                             |

|         | MOVLW  | .23          | ; 24 hours elapsed?                           |

|         | CPFSGT | hours        |                                               |

|         | RETURN |              | ; No, done                                    |

|         | MOVLW  | .01          | ; Reset hours to 1                            |

|         | MOVWF  | hours        |                                               |

|         | RETURN |              | ; Done                                        |

|         |        |              |                                               |

## EXAMPLE 13-1: IMPLEMENTING A REAL-TIME CLOCK USING A TIMER1 INTERRUPT SERVICE

## TABLE 13-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Name   | Bit 7                     | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values on<br>Page: |

|--------|---------------------------|-----------|---------|---------|---------|--------|--------|--------|-----------------------------|

| INTCON | GIE/GIEH                  | PEIE/GIEL | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF | RBIF   | 47                          |

| PIR1   | _                         | ADIF      | RCIF    | TXIF    | CMP2IF  | CMP1IF | CMP0IF | TMR1IF | 49                          |

| PIE1   | —                         | ADIE      | RCIE    | TXIE    | CMP2IE  | CMP1IE | CMP0IE | TMR1IE | 49                          |

| IPR1   | —                         | ADIP      | RCIP    | TXIP    | CMP2IP  | CMP1IP | CMP0IP | TMR1IP | 49                          |

| TMR1L  | Timer1 Register Low Byte  |           |         |         |         |        |        | 48     |                             |

| TMR1H  | Timer1 Register High Byte |           |         |         |         |        | 48     |        |                             |

| T1CON  | RD16                      | T1RUN     | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 48                          |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

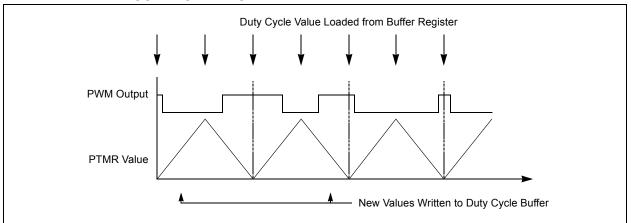

## FIGURE 14-14: DUTY CYCLE UPDATE TIMES IN CONTINUOUS UP/DOWN COUNT MODE WITH DOUBLE UPDATES

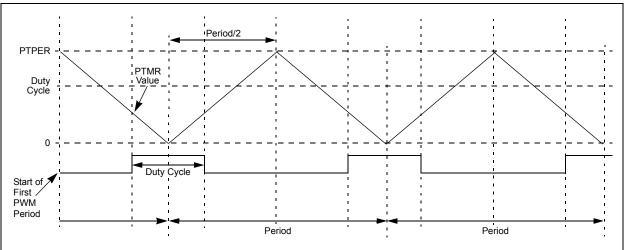

#### 14.6.4 CENTER-ALIGNED PWM

Center-aligned PWM signals are produced by the module when the PWM time base is configured in a Continuous Up/Down Count mode (see Figure 14-15). The PWM compare output is driven to the active state when the value of the Duty Cycle register matches the value of PTMR and the PWM time base is counting downwards (PTDIR = 1). The PWM compare output will be driven to the inactive state when the PWM time base is counting upwards (PTDIR = 0) and the value in the PTMR register matches the duty cycle value. If the value in a particular Duty Cycle register is zero, then the output on the corresponding PWM pin will be

inactive for the entire PWM period. In addition, the output on the PWM pin will be active for the entire PWM period if the value in the Duty Cycle register is equal to or greater than the value in the PTPER register.

Note: When the PWM is started in Center-Aligned mode, the PWM Time Base Period register (PTPER) is loaded into the PWM Time Base register (PTMR) and the PTMR is configured automatically to start down counting. This is done to ensure that all the PWM signals don't start at the same time.

#### FIGURE 14-15: START OF CENTER-ALIGNED PWM

## 16.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) Converter module has 4 inputs for the 18/20/28-pin devices. This module allows conversion of an analog input signal to a corresponding 10-bit digital number in PIC18F1230/ 1330 devices.

The module has five registers:

- A/D Result Register High Byte (ADRESH)

- A/D Result Register Low Byte (ADRESL)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

- A/D Control Register 2 (ADCON2)

The ADCON0 register, shown in Register 16-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 16-2, configures the functions of the port pins. The ADCON2 register, shown in Register 16-3, configures the A/D clock source, programmed acquisition time and justification.

| R/W-0  | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 |

|--------|-----|-----|-----|-------|-------|---------|-------|

| SEVTEN | _   | _   | _   | CHS1  | CHS0  | GO/DONE | ADON  |

| bit 7  |     |     |     |       |       |         | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| h:+ 7   | SEVITEN: Openial Event Trianer Enable bit                                     |

|---------|-------------------------------------------------------------------------------|

| bit 7   | SEVTEN: Special Event Trigger Enable bit                                      |

|         | 1 = Special Event Trigger from Power Control PWM module is enabled            |

|         | 0 = Special Event Trigger from Power Control PWM module is disabled (default) |

| bit 6-4 | Unimplemented: Read as '0'                                                    |

| bit 3-2 | CHS1:CHS0: Analog Channel Select bits                                         |

|         | 00 = Channel 0 (AN0)                                                          |

|         | 01 = Channel 1 (AN1)                                                          |

|         | 10 = Channel 2 (AN2)                                                          |

|         | 11 = Channel 3 (AN3)                                                          |

| bit 1   | GO/DONE: A/D Conversion Status bit                                            |

|         | When ADON = 1:                                                                |

|         | 1 = A/D conversion in progress                                                |

|         | 0 = A/D Idle                                                                  |

| bit 0   | ADON: A/D On bit                                                              |

|         | 1 = A/D Converter module is enabled                                           |

|         | 0 = A/D Converter module is disabled                                          |

|         |                                                                               |

|         |                                                                               |

## REGISTER 16-1: ADCON0: A/D CONTROL REGISTER 0

## 17.0 COMPARATOR MODULE

The analog comparator module contains three comparators. The inputs can be selected from the analog inputs multiplexed with pins RA0, RB2 and RB3, as well as the on-chip voltage reference (see

Section 18.0 "Comparator Voltage Reference Module"). The digital outputs are not available at the pin level and can only be read through the control register, CMCON (Register 17-1). CMCON also selects the comparator input.

#### REGISTER 17-1: CMCON: COMPARATOR CONTROL REGISTER

| R-0   | R-0   | R-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----|-----|-------|-------|-------|

| C2OUT | C1OUT | COOUT | —   | —   | CMEN2 | CMEN1 | CMEN0 |

| bit 7 |       |       |     |     |       |       | bit 0 |

| Legend:    |          |                                                                            |                                    |                    |  |  |  |

|------------|----------|----------------------------------------------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Read   | able bit | W = Writable bit                                                           | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value | at POR   | '1' = Bit is set                                                           | '0' = Bit is cleared               | x = Bit is unknowr |  |  |  |

| bit 7      | 1 = C2 V | Comparator 2 Output bit<br>IN+ > C2 VIN- (CVREF)<br>IN+ < C2 VIN- (CVREF)  |                                    |                    |  |  |  |

| bit 6      | 1 = C1 V | Comparator 1 Output bit<br>IN+ > C1 VIN- (CVREF)<br>IN+ < C1 VIN- (CVREF)- |                                    |                    |  |  |  |

| hit E      | COOLIT   | Comporator 0 Output hit                                                    |                                    |                    |  |  |  |

| bit 5   | COOUT: Comparator 0 Output bit  |

|---------|---------------------------------|

|         | 1 = CO VIN + > CO VIN - (CVREF) |

|         | 0 = C0 VIN + < C0 VIN - (CVREF) |

| bit 4-3 | Unimplemented: Read as '0'      |

| bit 2   | CMEN2: Comparator 2 Enable bit  |

|         | 1 = Comparator 2 is enabled     |

|         | 0 = Comparator 2 is disabled    |

| bit 1   | CMEN1: Comparator 1 Enable bit  |

|         | 1 = Comparator 1 is enabled     |

|         | 0 = Comparator 1 is disabled    |

| bit 0   | CMEN0: Comparator 0 Enable bit  |

|         |                                 |

- 1 =Comparator 0 is enabled

- 0 = Comparator 0 is disabled

## REGISTER 20-7: CONFIG5L: CONFIGURATION REGISTER 5 LOW (BYTE ADDRESS 300008h)

| U-0                                | U-0 | U-0 | U-0   | U-0                                | U-0 | R/C-1 | R/C-1 |  |

|------------------------------------|-----|-----|-------|------------------------------------|-----|-------|-------|--|

| —                                  | _   | —   | _     | —                                  | —   | CP1   | CP0   |  |

| bit 7                              |     |     |       |                                    |     |       | bit 0 |  |

|                                    |     |     |       |                                    |     |       |       |  |

| Legend:                            |     |     |       |                                    |     |       |       |  |

| R = Readable bit C = Clearable bit |     |     | e bit | U = Unimplemented bit, read as '0' |     |       |       |  |

| R = Readable bit       | C = Clearable bit | U = Unimplemented bit, read as '0'  |

|------------------------|-------------------|-------------------------------------|

| -n = Value when device | e is unprogrammed | u = Unchanged from programmed state |

| bit 7-2 | Unimplemented: Read as '0'                                                                |

|---------|-------------------------------------------------------------------------------------------|

| bit 1   | CP1: Code Protection bit (Block 1 Code Memory Area)                                       |

|         | <ul><li>1 = Block 1 is not code-protected</li><li>0 = Block 1 is code-protected</li></ul> |

| bit 0   | CP0: Code Protection bit (Block 0 Code Memory Area)                                       |

|         | <ul><li>1 = Block 0 is not code-protected</li><li>0 = Block 0 is code-protected</li></ul> |

## REGISTER 20-8: CONFIG5H: CONFIGURATION REGISTER 5 HIGH (BYTE ADDRESS 300009h)

| R/C-1 | R/C-1 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

| CPD   | СРВ   | —   | —   | —   | —   | —   | —     |

| bit 7 |       |     |     |     |     |     | bit 0 |

| Legend:                                                                      |                                                                                                           |                                     |

|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------|

| R = Readable bit C = Clearable bit<br>-n = Value when device is unprogrammed |                                                                                                           | U = Unimplemented bit, read as '0'  |

|                                                                              |                                                                                                           | u = Unchanged from programmed state |

| bit 7                                                                        | <b>CPD:</b> Code Protection bit (Data B<br>1 = Data EEPROM is not code-p<br>0 = Data EEPROM is code-prote | rotected                            |

|                                                                              |                                                                                                           |                                     |

| DIT 6 | CPB: Code Protection bit (Boot Block Memory Are |

|-------|-------------------------------------------------|

|       | 1 = Boot Block is not code-protected            |

|       |                                                 |

0 = Boot Block is code-protected

bit 5-0 Unimplemented: Read as '0'

### REGISTER 20-15: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| U-0                                                                  | U-0 | U-0              | U-0 | U-0                                     | U-0 | U-0 | R/W-0                 |

|----------------------------------------------------------------------|-----|------------------|-----|-----------------------------------------|-----|-----|-----------------------|

| —                                                                    | _   | —                | _   | —                                       | —   | —   | SWDTEN <sup>(1)</sup> |

| bit 7                                                                |     |                  |     |                                         |     |     | bit 0                 |

|                                                                      |     |                  |     |                                         |     |     |                       |

| Legend:                                                              |     |                  |     |                                         |     |     |                       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |                  |     |                                         |     |     |                       |

| -n = Value at P                                                      | OR  | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |     |     |                       |

| bit 7-1 | Unimplemented: Read as '0'                                           |

|---------|----------------------------------------------------------------------|

| bit 0   | SWDTEN: Software Controlled Watchdog Timer Enable bit <sup>(1)</sup> |

|         | 1 = Watchdog Timer is on                                             |

|         | 0 = Watchdog Timer is off                                            |

Note 1: This bit has no effect if the Configuration bit, WDTEN, is enabled.

### TABLE 20-2: SUMMARY OF WATCHDOG TIMER REGISTERS

| Name   | Bit 7 | Bit 6                 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0                 | Reset<br>Values<br>on Page: |

|--------|-------|-----------------------|-------|-------|-------|-------|-------|-----------------------|-----------------------------|

| RCON   | IPEN  | SBOREN <sup>(1)</sup> |       | RI    | TO    | PD    | POR   | BOR                   | 48                          |

| WDTCON |       | —                     | —     |       |       |       | _     | SWDTEN <sup>(2)</sup> | 48                          |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Watchdog Timer.

Note 1: The SBOREN bit is only available when the BOREN1:BOREN0 Configuration bits = 01; otherwise, it is disabled and reads as '0'. See Section 5.4 "Brown-out Reset (BOR)".

2: This bit has no effect if the Configuration bit, WDTEN, is enabled.

| BNC                                           | Branch if                                                                 | Not Carry                                                                               |                                                      | BNN         | 1                                                       | Branch if                                                              | Not Negativ                                                                          | /e                                            |

|-----------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------|-------------|---------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------|

| Syntax:                                       | BNC n                                                                     |                                                                                         |                                                      | Synt        | ax:                                                     | BNN n                                                                  |                                                                                      |                                               |

| Operands:                                     | -128 ≤ n ≤ ′                                                              | 127                                                                                     |                                                      | Oper        | ands:                                                   | -128 ≤ n ≤                                                             | 127                                                                                  |                                               |

| Operation:                                    | if Carry bit i<br>(PC) + 2 + 2                                            |                                                                                         |                                                      | Oper        | ation:                                                  | if Negative<br>(PC) + 2 +                                              |                                                                                      |                                               |

| Status Affected:                              | None                                                                      |                                                                                         |                                                      | Statu       | is Affected:                                            | None                                                                   |                                                                                      |                                               |

| Encoding:                                     | 1110                                                                      | 0011 nn                                                                                 | nn nnnn                                              | Enco        | oding:                                                  | 1110                                                                   | 0111 nn:                                                                             | nn n                                          |

| Description:                                  | will branch.<br>The 2's con<br>added to the<br>incremente<br>instruction, | nplement num<br>e PC. Since th<br>d to fetch the i<br>the new addre<br>n. This instruct | ber '2n' is<br>e PC will have<br>next<br>ess will be | Desc        | ription:                                                | program wi<br>The 2's cor<br>added to th<br>incremente<br>instruction, | mplement num<br>e PC. Since th<br>d to fetch the<br>the new addre<br>n. This instruc | ber '2n' i<br>e PC will<br>next<br>ess will b |

| Words:                                        | 1                                                                         |                                                                                         |                                                      | Word        | ls:                                                     | 1                                                                      |                                                                                      |                                               |

| Cycles:                                       | 1(2)                                                                      |                                                                                         |                                                      | Cycle       | es:                                                     | 1(2)                                                                   |                                                                                      |                                               |

| Q Cycle Activity<br>If Jump:                  | :                                                                         |                                                                                         |                                                      |             | ycle Activity:<br>imp:                                  |                                                                        |                                                                                      |                                               |

| Q1                                            | Q2                                                                        | Q3                                                                                      | Q4                                                   | _           | Q1                                                      | Q2                                                                     | Q3                                                                                   | Q4                                            |

| Decode                                        | Read literal<br>'n'                                                       | Process<br>Data                                                                         | Write to<br>PC                                       |             | Decode                                                  | Read literal<br>'n'                                                    | Process<br>Data                                                                      | Write<br>PC                                   |

| No<br>operation                               | No<br>operation                                                           | No<br>operation                                                                         | No<br>operation                                      |             | No<br>operation                                         | No<br>operation                                                        | No<br>operation                                                                      | No<br>opera                                   |

| If No Jump:                                   | •                                                                         |                                                                                         |                                                      | lf No       | o Jump:                                                 |                                                                        |                                                                                      |                                               |

| Q1                                            | Q2                                                                        | Q3                                                                                      | Q4                                                   | 1           | Q1                                                      | Q2                                                                     | Q3                                                                                   | Q4                                            |

| Decode                                        | Read literal<br>'n'                                                       | Process<br>Data                                                                         | No<br>operation                                      |             | Decode                                                  | Read literal<br>'n'                                                    | Process<br>Data                                                                      | No<br>opera                                   |

| Example:                                      | HERE                                                                      | BNC Jump                                                                                |                                                      | <u>Exar</u> | nple:                                                   | HERE                                                                   | BNN Jump                                                                             |                                               |

| Before Instr<br>PC<br>After Instruc<br>If Car | = ad                                                                      | dress (HERE                                                                             | )                                                    |             | Before Instruct<br>PC<br>After Instruction<br>If Negati | = ad                                                                   | ldress (here                                                                         | )                                             |

| P<br>If Ca                                    | rČ = ad<br>rry = 1;                                                       | dress (Jump<br>dress (HERE                                                              |                                                      |             | P<br>If Negati                                          | C = ad<br>ve = 1;                                                      | ldress (Jump<br>ldress (HERE                                                         |                                               |

ill branch. mplement number '2n' is e PC. Since the PC will have ed to fetch the next the new address will be n. This instruction is then a nstruction. Q3 Q4

nnnn

Write to PC

|    | No<br>operation                          | No<br>operation  |           | No<br>operation |        | No<br>operation |

|----|------------------------------------------|------------------|-----------|-----------------|--------|-----------------|

| No | o Jump:                                  |                  |           |                 |        |                 |

|    | Q1                                       | Q2               |           | (               | 23     | Q4              |

|    | Decode                                   | Read lite<br>'n' | ral       | Process<br>Data |        | No<br>operation |

| an | <u>iple:</u>                             | HERE             |           | BNN             | Jump   |                 |

|    | Before Instruc<br>PC<br>After Instructic | =                | ado       | lress           | (HERE) |                 |

|    | If Negativ<br>P(                         | C =              | 0;<br>add | lress           | (Jump) |                 |

| DEC         | FSZ                     | Decremer                                                                                                                                                                                                                                                     | nt f, Skip if                                                                                                                                           | 0                                                                                                                                                                                                                        | DCFSN         |

|-------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Synta       | ax:                     | DECFSZ f                                                                                                                                                                                                                                                     | <sup>;</sup> {,d {,a}}                                                                                                                                  |                                                                                                                                                                                                                          | Syntax:       |

| Oper        | ands:                   | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                          |                                                                                                                                                         |                                                                                                                                                                                                                          | Operand       |

| Oper        | ation:                  | (f) – 1 $\rightarrow$ de skip if result                                                                                                                                                                                                                      | -                                                                                                                                                       |                                                                                                                                                                                                                          | Operatio      |

| Statu       | is Affected:            | None                                                                                                                                                                                                                                                         |                                                                                                                                                         |                                                                                                                                                                                                                          | Status A      |

| Enco        | oding:                  | 0010                                                                                                                                                                                                                                                         | 11da ff                                                                                                                                                 | ff ffff                                                                                                                                                                                                                  | Encoding      |

| Desc        | sription:               | decremente<br>placed in W<br>placed back<br>If the result<br>which is alr<br>and a NOP i<br>it a two-cyc<br>If 'a' is '0', tl<br>If 'a' is '1', tl<br>GPR bank.<br>If 'a' is '0' a<br>set is enabl<br>in Indexed I<br>mode when<br>Section 22<br>Bit-Oriente | le instruction.<br>The Access Ba<br>The BSR is use<br>and the extend<br>ed, this instru<br>Literal Offset<br>rever $f \le 95$ (5<br><b>.2.3 "Byte-O</b> | the result is<br>he result is<br>it instruction,<br>is discarded<br>stead, making<br>nk is selected.<br>ed to select the<br>led instruction<br>ction operates<br>Addressing<br>iFh). See<br>riented and<br>hs in Indexed | Descripti     |

| Word        | ls:                     | 1                                                                                                                                                                                                                                                            |                                                                                                                                                         |                                                                                                                                                                                                                          |               |

| Cycle       | es:                     | 1(2)                                                                                                                                                                                                                                                         |                                                                                                                                                         |                                                                                                                                                                                                                          | Words:        |

| -           |                         |                                                                                                                                                                                                                                                              | cles if skip ar<br>2-word instru                                                                                                                        |                                                                                                                                                                                                                          | Cycles:       |

| QC          | ycle Activity:          |                                                                                                                                                                                                                                                              |                                                                                                                                                         |                                                                                                                                                                                                                          |               |

|             | Q1                      | Q2                                                                                                                                                                                                                                                           | Q3                                                                                                                                                      | Q4                                                                                                                                                                                                                       | Q Cycle       |

|             | Decode                  | Read<br>register 'f'                                                                                                                                                                                                                                         | Process<br>Data                                                                                                                                         | Write to destination                                                                                                                                                                                                     |               |

| lf sk       | -                       |                                                                                                                                                                                                                                                              |                                                                                                                                                         |                                                                                                                                                                                                                          | If align      |

| ĺ           | Q1                      | Q2                                                                                                                                                                                                                                                           | Q3                                                                                                                                                      | Q4                                                                                                                                                                                                                       | lf skip:<br>1 |

|             | No<br>operation         | No<br>operation                                                                                                                                                                                                                                              | No<br>operation                                                                                                                                         | No<br>operation                                                                                                                                                                                                          |               |

| lfsk        |                         | d by 2-word in:                                                                                                                                                                                                                                              |                                                                                                                                                         | operation                                                                                                                                                                                                                | ]   0         |

|             | Q1                      | Q2                                                                                                                                                                                                                                                           | Q3                                                                                                                                                      | Q4                                                                                                                                                                                                                       | lf skip a     |

| 1           | No                      | No                                                                                                                                                                                                                                                           | No                                                                                                                                                      | No                                                                                                                                                                                                                       | ]             |

|             | operation               | operation                                                                                                                                                                                                                                                    | operation                                                                                                                                               | operation                                                                                                                                                                                                                |               |

|             | No                      | No                                                                                                                                                                                                                                                           | No                                                                                                                                                      | No                                                                                                                                                                                                                       | 0             |

|             | operation               | operation                                                                                                                                                                                                                                                    | operation                                                                                                                                               | operation                                                                                                                                                                                                                |               |

| <u>Exan</u> | nple:                   | HERE                                                                                                                                                                                                                                                         | DECFSZ<br>GOTO                                                                                                                                          | CNT, 1, 1<br>LOOP                                                                                                                                                                                                        | <br>Example   |