Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 4x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f1330-e-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.2 Other Special Features

- Memory Endurance: The Enhanced Flash cells for both program memory and data EEPROM are rated to last for many thousands of erase/write cycles – up to 100,000 for program memory and 1,000,000 for EEPROM. Data retention without refresh is conservatively estimated to be greater than 40 years.

- Self-Programmability: These devices can write to their own program memory spaces under internal software control. By using a bootloader routine located in the protected Boot Block at the top of program memory, it becomes possible to create an application that can update itself in the field.

- Extended Instruction Set: The PIC18F1230/1330 family introduces an optional extension to the PIC18 instruction set, which adds eight new instructions and an Indexed Addressing mode. This extension, enabled as a device configuration option, has been specifically designed to optimize re-entrant application code originally developed in high-level languages, such as C.

- Power Control PWM Module: This module provides up to six modulated outputs for controlling half-bridge and full-bridge drivers. Other features include auto-shutdown on Fault detection and auto-restart to reactivate outputs once the condition has cleared.

- Enhanced Addressable USART: This serial communication module is capable of standard RS-232 operation and provides support for the LIN/J2602 bus protocol. Other enhancements include automatic Baud Rate Detection and a 16-bit Baud Rate Generator for improved resolution. When the microcontroller is using the internal oscillator block, the EUSART provides stable operation for applications that talk to the outside world without using an external crystal (or its accompanying power requirement).

- **10-Bit A/D Converter:** This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period and thus, reducing code overhead.

- Extended Watchdog Timer (WDT): This enhanced version incorporates a 16-bit prescaler, allowing an extended time-out range that is stable across operating voltage and temperature. See Section 23.0 "Electrical Characteristics" for time-out periods.

## 1.3 Details on Individual Family Members

Devices in the PIC18F1230/1330 family are available in 18-pin, 20-pin and 28-pin packages.

The devices are differentiated from each other in one way:

1. Flash program memory (4 Kbytes for PIC18F1230, 8 Kbytes for PIC18F1330).

All other features for devices in this family are identical. These are summarized in Table 1-1.

A block diagram of the PIC18F1220/1320 device architecture is provided in Figure 1-1. The pinouts for this device family are listed in Table 1-2.

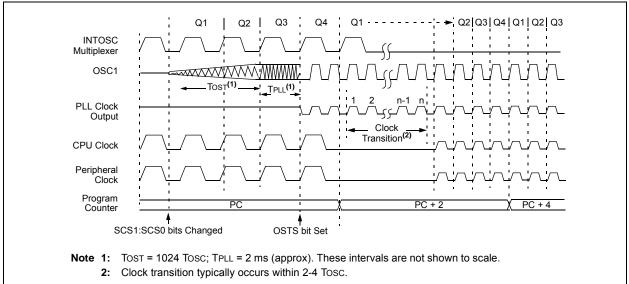

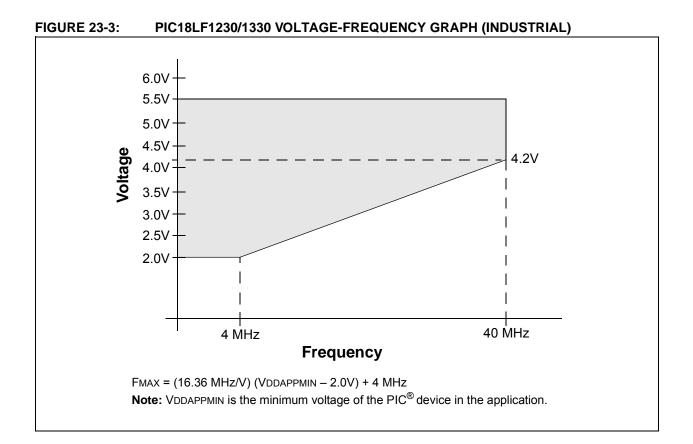

Like all Microchip PIC18 devices, members of the PIC18F1230/1330 family are available as both standard and low-voltage devices. Standard devices with Enhanced Flash memory, designated with an "F" in the part number (such as PIC18F1330), accommodate an operating VDD range of 4.2V to 5.5V. Low-voltage parts, designated by "LF" (such as PIC18LF1330), function over an extended VDD range of 2.0V to 5.5V. If the IRCF bits and the INTSRC bit are all clear, the INTOSC output is not enabled and the IOFS bit will remain clear; there will be no indication of the current clock source. The INTRC source is providing the device clocks.

If the IRCF bits are changed from all clear (thus, enabling the INTOSC output), or if INTSRC is set, the IOFS bit becomes set after the INTOSC output becomes stable. Clocks to the device continue while the INTOSC source stabilizes after an interval of TIOBST.

If the IRCF bits were previously at a non-zero value, or if INTSRC was set before setting SCS1 and the INTOSC source was already stable, the IOFS bit will remain set.

PC

Note 1: Clock transition typically occurs within 2-4 Tosc.

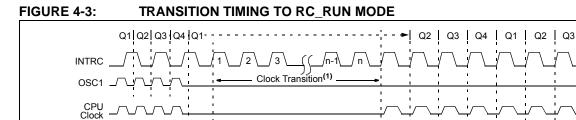

On transitions from RC\_RUN mode to PRI\_RUN mode, the device continues to be clocked from the INTOSC multiplexer while the primary clock is started. When the primary clock becomes ready, a clock switch to the primary clock occurs (see Figure 4-4). When the clock switch is complete, the IOFS bit is cleared, the OSTS bit is set and the primary clock is providing the device clock. The IDLEN and SCS bits are not affected by the switch. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

PC + 4

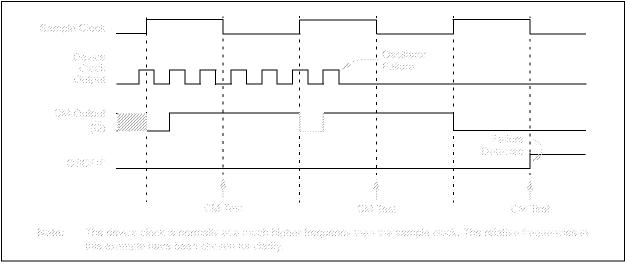

#### FIGURE 4-4: TRANSITION TIMING FROM RC\_RUN MODE TO PRI\_RUN MODE

PC + 2

Peripheral Clock Program Counter

## 5.6 Reset State of Registers

Most registers are unaffected by a Reset. Their status is unknown on POR and unchanged by all other Resets. The other registers are forced to a "Reset state" depending on the type of Reset that occurred.

Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register,  $\overline{RI}$ ,  $\overline{TO}$ ,  $\overline{PD}$ ,  $\overline{POR}$  and  $\overline{BOR}$ , are set or cleared differently in different Reset situations, as indicated in Table 5-3. These bits are used in software to determine the nature of the Reset. Table 5-4 describes the Reset states for all of the Special Function Registers. These are categorized by Power-on and Brown-out Resets, Master Clear and WDT Resets and WDT wake-ups.

| Condition                                                   | Program               |                  | RCC |    | STKPTR Register |     |     |        |        |

|-------------------------------------------------------------|-----------------------|------------------|-----|----|-----------------|-----|-----|--------|--------|

| Condition                                                   | Counter               | SBOREN           | RI  | то | PD              | POR | BOR | STKFUL | STKUNF |

| Power-on Reset                                              | 0000h                 | 1                | 1   | 1  | 1               | 0   | 0   | 0      | 0      |

| RESET Instruction                                           | 0000h                 | u <b>(2)</b>     | 0   | u  | u               | u   | u   | u      | u      |

| Brown-out Reset                                             | 0000h                 | u <b>(2)</b>     | 1   | 1  | 1               | u   | 0   | u      | u      |

| MCLR during Power-Managed<br>Run Modes                      | 0000h                 | <sub>ປ</sub> (2) | u   | 1  | u               | u   | u   | u      | u      |

| MCLR during Power-Managed Idle Modes and Sleep Mode         | 0000h                 | <sub>ປ</sub> (2) | u   | 1  | 0               | u   | u   | u      | u      |

| WDT Time-out during Full Power<br>or Power-Managed Run Mode | 0000h                 | ս <b>(2)</b>     | u   | 0  | u               | u   | u   | u      | u      |

| MCLR during Full Power<br>Execution                         | 0000h                 | ս <b>(2)</b>     | u   | u  | u               | u   | u   | u      | u      |

| Stack Full Reset (STVREN = 1)                               | 0000h                 | u <b>(2)</b>     | u   | u  | u               | u   | u   | 1      | u      |

| Stack Underflow Reset<br>(STVREN = 1)                       | 0000h                 | ս <b>(2)</b>     | u   | u  | u               | u   | u   | u      | 1      |

| Stack Underflow Error (not an actual Reset, STVREN = 0)     | 0000h                 | ս <b>(2)</b>     | u   | u  | u               | u   | u   | u      | 1      |

| WDT Time-out during<br>Power-Managed Idle or<br>Sleep Modes | PC + 2                | u <b>(2)</b>     | u   | 0  | 0               | u   | u   | u      | u      |

| Interrupt Exit from<br>Power-Managed Modes                  | PC + 2 <sup>(1)</sup> | u <b>(2)</b>     | u   | u  | 0               | u   | u   | u      | u      |

#### TABLE 5-3: STATUS BITS, THEIR SIGNIFICANCE AND THE INITIALIZATION CONDITION FOR RCON REGISTER

Legend: u = unchanged

**Note 1:** When the wake-up is due to an interrupt and the GIEH or GIEL bit is set, the PC is loaded with the interrupt vector (008h or 0018h).

2: Reset state is '1' for POR and unchanged for all other Resets when software BOR is enabled (BOREN1:BOREN0 Configuration bits = 01 and SBOREN = 1); otherwise, the Reset state is '0'.

| TABLE 5-4: | INITIA                      | ALIZATION CONDITIONS FOR ALL REGISTERS |                                    |                                                                  |                                 |  |  |  |  |  |  |

|------------|-----------------------------|----------------------------------------|------------------------------------|------------------------------------------------------------------|---------------------------------|--|--|--|--|--|--|

| Register   | Register Applicable Devices |                                        | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |  |  |  |  |  |

| TOSU       | 1230                        | 1330                                   | 0 0000                             | 0 0000                                                           | 0 uuuu <b>(3)</b>               |  |  |  |  |  |  |

| TOSH       | 1230                        | 1330                                   | 0000 0000                          | 0000 0000                                                        | uuuu uuuu <b>(3)</b>            |  |  |  |  |  |  |

| TOSL       | 1230                        | 1330                                   | 0000 0000                          | 0000 0000                                                        | uuuu uuuu <sup>(3)</sup>        |  |  |  |  |  |  |

| STKPTR     | 1230                        | 1330                                   | 00-0 0000                          | uu-0 0000                                                        | uu-u uuuu <b>(3)</b>            |  |  |  |  |  |  |

| PCLATU     | 1230                        | 1330                                   | 0 0000                             | 0 0000                                                           | u uuuu                          |  |  |  |  |  |  |

| PCLATH     | 1230                        | 1330                                   | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |  |  |  |  |  |

| PCL        | 1230                        | 1330                                   | 0000 0000                          | 0000 0000                                                        | PC + 2 <sup>(2)</sup>           |  |  |  |  |  |  |

| TBLPTRU    | 1230                        | 1330                                   | 00 0000                            | 00 0000                                                          | uu uuuu                         |  |  |  |  |  |  |

| TBLPTRH    | 1230                        | 1330                                   | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |  |  |  |  |  |

| TBLPTRL    | 1230                        | 1330                                   | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |  |  |  |  |  |

| TABLAT     | 1230                        | 1330                                   | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |  |  |  |  |  |

| PRODH      | 1230                        | 1330                                   | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |  |  |

| PRODL      | 1230                        | 1330                                   | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |  |  |

| INTCON     | 1230                        | 1330                                   | 0000 000x                          | 0000 000u                                                        | uuuu uuuu <b>(1)</b>            |  |  |  |  |  |  |

| INTCON2    | 1230                        | 1330                                   | 1111 1111                          | 1111 1111                                                        | uuuu uuuu <b>(1)</b>            |  |  |  |  |  |  |

| INTCON3    | 1230                        | 1330                                   | 1100 0000                          | 1100 0000                                                        | uuuu uuuu <b>(1)</b>            |  |  |  |  |  |  |

| INDF0      | 1230                        | 1330                                   | N/A                                | N/A                                                              | N/A                             |  |  |  |  |  |  |

| POSTINC0   | 1230                        | 1330                                   | N/A                                | N/A                                                              | N/A                             |  |  |  |  |  |  |

| POSTDEC0   | 1230                        | 1330                                   | N/A                                | N/A                                                              | N/A                             |  |  |  |  |  |  |

| PREINC0    | 1230                        | 1330                                   | N/A                                | N/A                                                              | N/A                             |  |  |  |  |  |  |

| PLUSW0     | 1230                        | 1330                                   | N/A                                | N/A                                                              | N/A                             |  |  |  |  |  |  |

| FSR0H      | 1230                        | 1330                                   | 0000                               | 0000                                                             | uuuu                            |  |  |  |  |  |  |

| FSR0L      | 1230                        | 1330                                   | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |  |  |

| WREG       | 1230                        | 1330                                   | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |  |  |

| INDF1      | 1230                        | 1330                                   | N/A                                | N/A                                                              | N/A                             |  |  |  |  |  |  |

| POSTINC1   | 1230                        | 1330                                   | N/A                                | N/A                                                              | N/A                             |  |  |  |  |  |  |

| POSTDEC1   | 1230                        | 1330                                   | N/A                                | N/A                                                              | N/A                             |  |  |  |  |  |  |

| PREINC1    | 1230                        | 1330                                   | N/A                                | N/A                                                              | N/A                             |  |  |  |  |  |  |

| PLUSW1     | 1230                        | 1330                                   | N/A                                | N/A                                                              | N/A                             |  |  |  |  |  |  |

| FSR1H      | 1230                        | 1330                                   | 0000                               | 0000                                                             | uuuu                            |  |  |  |  |  |  |

| FSR1L      | 1230                        | 1330                                   | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |  |  |

| BSR        | 1230                        | 1330                                   | 0000                               | 0000                                                             | uuuu                            |  |  |  |  |  |  |

TABLE 5-4:

INITIALIZATION CONDITIONS FOR ALL REGISTERS

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- **2:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 5-3 for Reset value for specific condition.

- **5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read as '0'.

- 6: Reset condition of PWMEN bits depends on the PWMPIN Configuration bit of CONFIG3L.

#### 6.1.2.2 Return Stack Pointer (STKPTR)

The STKPTR register (Register 6-1) contains the Stack Pointer value, the STKFUL (Stack Full) status bit and the STKUNF (Stack Underflow) status bits. The value of the Stack Pointer can be 0 through 31. The Stack Pointer increments before values are pushed onto the stack and decrements after values are popped off the stack. On Reset, the Stack Pointer value will be zero. The user may read and write the Stack Pointer value. This feature can be used by a Real-Time Operating System (RTOS) for return stack maintenance.

After the PC is pushed onto the stack 31 times (without popping any values off the stack), the STKFUL bit is set. The STKFUL bit is cleared by software or by a POR.

The action that takes place when the stack becomes full depends on the state of the STVREN (Stack Overflow Reset Enable) Configuration bit. (Refer to **Section 20.1 "Configuration Bits"** for a description of the device Configuration bits.) If STVREN is set (default), the 31st push will push the (PC + 2) value onto the stack, set the STKFUL bit and reset the device. The STKFUL bit will remain set and the Stack Pointer will be set to zero.

If STVREN is cleared, the STKFUL bit will be set on the 31st push and the Stack Pointer will increment to 31. Any additional pushes will not overwrite the 31st push and STKPTR will remain at 31.

When the stack has been popped enough times to unload the stack, the next pop will return a value of zero to the PC and sets the STKUNF bit, while the Stack Pointer remains at zero. The STKUNF bit will remain set until cleared by software or until a POR occurs.

| Note: | Returning a value of zero to the PC on an<br>underflow has the effect of vectoring the |  |  |  |  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

|       | program to the Reset vector, where the                                                 |  |  |  |  |  |  |  |  |

|       | stack conditions can be verified and                                                   |  |  |  |  |  |  |  |  |

|       | appropriate actions can be taken. This is                                              |  |  |  |  |  |  |  |  |

|       | not the same as a Reset, as the contents of the SFRs are not affected.                 |  |  |  |  |  |  |  |  |

#### 6.1.2.3 PUSH and POP Instructions

Since the Top-of-Stack is readable and writable, the ability to push values onto the stack and pull values off the stack, without disturbing normal program execution, is a desirable feature. The PIC18 instruction set includes two instructions, PUSH and POP, that permit the TOS to be manipulated under software control. TOSU, TOSH and TOSL can be modified to place data or a return address on the stack.

The PUSH instruction places the current PC value onto the stack. This increments the Stack Pointer and loads the current PC value onto the stack.

The POP instruction discards the current TOS by decrementing the Stack Pointer. The previous value pushed onto the stack then becomes the TOS value.

### REGISTER 6-1: STKPTR: STACK POINTER REGISTER

| REGISTER 6            | -1: SIKP              | IR: STACK P                                              | OINTER RE  | GISTER           |                  |                    |       |  |

|-----------------------|-----------------------|----------------------------------------------------------|------------|------------------|------------------|--------------------|-------|--|

| R/C-0                 | R/C-0                 | U-0                                                      | R/W-0      | R/W-0            | R/W-0            | R/W-0              | R/W-0 |  |

| STKFUL <sup>(1)</sup> | STKUNF <sup>(1)</sup> | —                                                        | SP4        | SP3              | SP2              | SP1                | SP0   |  |

| bit 7                 |                       |                                                          |            |                  |                  |                    | bit 0 |  |

|                       |                       |                                                          |            |                  |                  |                    |       |  |

| Legend:               |                       | C = Clearable                                            | bit        |                  |                  |                    |       |  |

| R = Readable          | bit                   | W = Writable                                             | bit        | U = Unimpler     | mented bit, read | as '0'             |       |  |

| -n = Value at F       | POR                   | '1' = Bit is set                                         |            | '0' = Bit is cle | ared             | x = Bit is unknown |       |  |

| bit 7                 | 1 = Stack bec         | ck Full Flag bit<br>came full or ove<br>not become fu    | rflowed    | ed               |                  |                    |       |  |

| bit 6                 | 1 = Stack und         | ack Underflow F<br>derflow occurred<br>derflow did not d | d          |                  |                  |                    |       |  |

| bit 5                 | Unimplemen            | ted: Read as 'o                                          | כ'         |                  |                  |                    |       |  |

| bit 4-0               | SP4:SP0: Sta          | ack Pointer Loc                                          | ation bits |                  |                  |                    |       |  |

|                       |                       |                                                          |            |                  |                  |                    |       |  |

**Note 1:** Bit 7 and bit 6 are cleared by user software or by a POR.

#### EXAMPLE 7-3: WRITING TO FLASH PROGRAM MEMORY

| EAAWIFLE 7-3.  | VVNI       | TING TO FLASH PROG           |                                                           |

|----------------|------------|------------------------------|-----------------------------------------------------------|

|                | MOVLW      | D'88                         | ; number of bytes in erase block                          |

|                | MOVWF      | COUNTER                      |                                                           |

|                | MOVLW      | BUFFER_ADDR_HIGH             | ; point to buffer                                         |

|                | MOVWF      | FSROH                        |                                                           |

|                | MOVLW      | BUFFER_ADDR_LOW              |                                                           |

|                | MOVWF      | FSROL                        |                                                           |

|                | MOVLW      | CODE_ADDR_UPPER              | ; Load TBLPTR with the base                               |

|                | MOVWF      | TBLPTRU                      | ; address of the memory block                             |

|                | MOVLW      | CODE_ADDR_HIGH               |                                                           |

|                | MOVWF      | TBLPTRH                      |                                                           |

|                | MOVLW      | CODE_ADDR_LOW                |                                                           |

|                | MOVWF      | TBLPTRL                      |                                                           |

| READ_BLOCK     |            |                              |                                                           |

|                | TBLRD*+    |                              | ; read into TABLAT, and inc                               |

|                | MOVF       | TABLAT, W                    | ; get data                                                |

|                | MOVWF      | POSTINC0                     | ; store data                                              |

|                |            | COUNTER                      | ; done?                                                   |

|                | BRA        | READ_BLOCK                   | ; repeat                                                  |

| MODIFY_WORD    |            |                              |                                                           |

|                | MOVLW      | DATA_ADDR_HIGH               | ; point to buffer                                         |

|                | MOVWF      | FSROH                        |                                                           |

|                | MOVLW      | DATA_ADDR_LOW                |                                                           |

|                | MOVWF      | FSROL                        |                                                           |

|                | MOVLW      | NEW_DATA_LOW                 | ; update buffer word                                      |

|                | MOVWF      | POSTINC0                     |                                                           |

|                | MOVLW      | NEW_DATA_HIGH                |                                                           |

|                | MOVWF      | INDF0                        |                                                           |

| ERASE_BLOCK    |            |                              |                                                           |

|                | MOVLW      | CODE_ADDR_UPPER              | ; load TBLPTR with the base                               |

|                | MOVWF      | TBLPTRU                      | ; address of the memory block                             |

|                | MOVLW      | CODE_ADDR_HIGH               |                                                           |

|                | MOVWF      | TBLPTRH                      |                                                           |

|                | MOVLW      | CODE_ADDR_LOW                |                                                           |

|                | MOVWF      | TBLPTRL                      | · reint to plack measure memory                           |

|                | BSF<br>BCF | EECON1, EEPGD                | ; point to Flash program memory                           |

|                | BSF        | EECON1, CFGS<br>EECON1, WREN | ; access Flash program memory<br>; enable write to memory |

|                | BSF        | EECONI, WREN<br>EECON1, FREE | ; enable Row Erase operation                              |

|                | BCF        | INTCON, GIE                  | ; disable interrupts                                      |

|                | MOVLW      | 55h                          | , arounte interrupto                                      |

| Required       | MOVIN      | EECON2                       | ; write 55h                                               |

| Sequence       | MOVLW      | 0AAh                         | / WIICE JJII                                              |

| bequence       | MOVE       | EECON2                       | ; write OAAh                                              |

|                | BSF        | EECON1, WR                   | ; start erase (CPU stall)                                 |

|                | BSF        | INTCON, GIE                  | ; re-enable interrupts                                    |

|                | TBLRD*-    |                              | ; dummy read decrement                                    |

|                | MOVLW      | BUFFER_ADDR_HIGH             | ; point to buffer                                         |

|                | MOVLW      | FSROH                        | . point to baller                                         |

|                | MOVLW      | BUFFER_ADDR_LOW              |                                                           |

|                | MOVE       | FSROL                        |                                                           |

| WRITE_BUFFER_E |            |                              |                                                           |

|                | MOVLW      | D'8                          | ; number of bytes in holding register                     |

|                | MOVE       | COUNTER                      |                                                           |

| WRITE_BYTE_TO_ |            |                              |                                                           |

|                | MOVFF      | POSTINC0, WREG               | ; get low byte of buffer data                             |

|                | MOVWF      | TABLAT                       | ; present data to table latch                             |

|                | TBLWT+*    |                              | ; write data, perform a short write                       |

|                |            |                              | ; to internal TBLWT holding register.                     |

|                | DECFSZ     | COUNTER                      | ; loop until buffers are full                             |

|                | BRA        | WRITE_WORD_TO_HREGS          | . Toop where parters are rain                             |

|                |            |                              |                                                           |

## TABLE 10-1: PORTA I/O SUMMARY

| Pin             | Function             | TRIS<br>Setting | I/O | I/O<br>Type | Description                                                                                         |

|-----------------|----------------------|-----------------|-----|-------------|-----------------------------------------------------------------------------------------------------|

| RA0/AN0/INT0/   | RA0                  | 0               | 0   | DIG         | LATA<0> data output; not affected by analog input.                                                  |

| KBI0/CMP0       |                      | 1               | I   | TTL         | PORTA<0> data input; disabled when analog input enabled.                                            |

|                 | AN0                  | 1               | I   | ANA         | Analog input 0.                                                                                     |

|                 | INT0                 | 1               | I   | ST          | External interrupt 0.                                                                               |

|                 | KBI0                 | 1               | I   | TTL         | Interrupt-on-change pin.                                                                            |

|                 | CMP0                 | 1               | I   | ANA         | Comparator 0 input.                                                                                 |

| RA1/AN1/INT1/   | RA1                  | 0               | 0   | DIG         | LATA<1> data output; not affected by analog input.                                                  |

| KBI1            |                      | 1               | I   | TTL         | PORTA<1> data input; disabled when analog input enabled.                                            |

|                 | AN1                  | 1               | I   | ANA         | Analog input 1.                                                                                     |

|                 | INT1                 | 1               | I   | ST          | External interrupt 1.                                                                               |

|                 | KBI1                 | 1               | Ι   | TTL         | Interrupt-on-change pin.                                                                            |

| RA2/TX/CK       | RA2                  | 0               | 0   | DIG         | LATA<2> data output; not affected by analog input. Disabled when CVREF output enabled.              |

|                 |                      | 1               | Ι   | TTL         | PORTA<2> data input. Disabled when analog functions enabled;<br>disabled when CVREF output enabled. |

|                 | TX                   | 0               | 0   | DIG         | EUSART asynchronous transmit.                                                                       |

|                 | СК                   | 0               | 0   | DIG         | EUSART synchronous clock.                                                                           |

|                 |                      | 1               | Ι   | ST          |                                                                                                     |

| RA3/RX/DT       | RA3                  | 0               | 0   | DIG         | LATA<3> data output; not affected by analog input.                                                  |

|                 |                      | 1               | Ι   | TTL         | PORTA<3> data input; disabled when analog input enabled.                                            |

|                 | RX                   | 1               | Ι   | ANA         | EUSART asynchronous receive.                                                                        |

|                 | DT                   | 0               | 0   | DIG         | EUSART synchronous data.                                                                            |

|                 |                      | 1               | Ι   | TTL         |                                                                                                     |

| RA4/T0CKI/AN2/  | RA4                  | 0               | 0   | DIG         | LATA<4> data output.                                                                                |

| VREF+           |                      | 1               | I   | ST          | PORTA<4> data input; default configuration on POR.                                                  |

|                 | TOCKI                | 1               | Ι   | ST          | Timer0 external clock input.                                                                        |

|                 | AN2                  | 1               | Ι   | ANA         | Analog input 2.                                                                                     |

|                 | VREF+                | 1               | Ι   | ANA         | A/D reference voltage (high) input.                                                                 |

| MCLR/Vpp/RA5/   | MCLR                 | 1               | Ι   | ST          | Master Clear (Reset) input. This pin is an active-low Reset to the device                           |

| FLTA            | Vpp                  | 1               | I   | ANA         | Programming voltage input.                                                                          |

|                 | RA5                  | 1               | Ι   | ST          | Digital input.                                                                                      |

|                 | FLTA <sup>(1)</sup>  | 1               | I   | ST          | Fault detect input for PWM.                                                                         |

| RA6/OSC2/CLKO/  | RA6                  | 0               | 0   | DIG         | LATA<6> data output. Enabled in RCIO, INTIO2 and ECIO modes only                                    |

| T1OSO/T1CKI/AN3 |                      | 1               | I   | ST          | PORTA<6> data input. Enabled in RCIO, INTIO2 and ECIO modes only                                    |

|                 | OSC2                 | 0               | 0   | ANA         | Oscillator crystal output or external clock source output.                                          |

|                 | CLKO                 | 0               | 0   | ANA         | Oscillator crystal output.                                                                          |

|                 | T10SO <sup>(2)</sup> | 0               | 0   | ANA         | Timer1 oscillator output.                                                                           |

|                 | T1CKI <sup>(2)</sup> | 1               | I   | ST          | Timer1 clock input.                                                                                 |

|                 | AN3                  | 1               | I   | ANA         | Analog input 3.                                                                                     |

| RA7/OSC1/CLKI/  | RA7                  | 0               | 0   | DIG         | LATA<7> data output. Disabled in external oscillator modes.                                         |

| T1OSI/FLTA      |                      | 1               | I   | TTL         | PORTA<7> data input. Disabled in external oscillator modes.                                         |

|                 | OSC1                 | 1               | I   | ANA         | Oscillator crystal input or external clock source input.                                            |

|                 | CLKI                 | 1               | I   | ANA         | External clock source input.                                                                        |

|                 | T10SI <sup>(2)</sup> | 1               | I   | ANA         | Timer1 oscillator input.                                                                            |

|                 | FLTA <sup>(1)</sup>  |                 |     | 1           |                                                                                                     |

Legend: DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: Placement of FLTA depends on the value of Configuration bit, FLTAMX, of CONFIG3H.

2: Placement of T1OSI and T1OSO/T1CKI depends on the value of Configuration bit, T1OSCMX, of CONFIG3H.

| R/W-0              | R/W-0                                   | R/W-0                                                  | R/W-0                            | R/W-0                                                                     | R/W-0                           | R/W-0             | R/W-0        |

|--------------------|-----------------------------------------|--------------------------------------------------------|----------------------------------|---------------------------------------------------------------------------|---------------------------------|-------------------|--------------|

| PTOPS3             | PTOPS2                                  | PTOPS1                                                 | PTOPS0                           | PTCKPS1                                                                   | PTCKPS0                         | PTMOD1            | PTMOD0       |

| bit 7              |                                         |                                                        |                                  |                                                                           |                                 |                   | bit 0        |

| Legend:            |                                         |                                                        |                                  |                                                                           |                                 |                   |              |

| R = Readable       | bit                                     | W = Writable                                           | bit                              | U = Unimpler                                                              | nented bit, read                | l as '0'          |              |

| -n = Value at P    |                                         | '1' = Bit is set                                       |                                  | '0' = Bit is cle                                                          | ,                               | x = Bit is unkr   | nown         |

| bit 7-4<br>bit 3-2 | 0000 = 1:1 Pc<br>0001 = 1:2 Pc          | ostscale<br>ostscale<br>Postscale<br><b>CKPS0:</b> PWM | I Time Base Ir                   | •                                                                         | scale Select bits               | 5                 |              |

|                    | 01 = PWM ti<br>10 = PWM ti              | me base input<br>me base input                         | clock is Fosc<br>clock is Fosc   | /4 (1:1 prescale<br>/16 (1:4 presca<br>/64 (1:16 presc<br>/256 (1:64 pres | ale)<br>cale)                   |                   |              |

| bit 1-0            | PTMOD1:PTI                              | NODO: PWM T                                            | ïme Base Mo                      | de Select bits                                                            |                                 |                   |              |

|                    | updates<br>10 = PWM tin<br>01 = PWM tin | s<br>me base opera<br>me base config                   | tes in a Conti<br>jured for Sing | nuous Up/Dow                                                              | n Count mode w<br>'n Count mode | ith interrupts fo | r double PWM |

## REGISTER 14-1: PTCON0: PWM TIMER CONTROL REGISTER 0

## REGISTER 14-2: PTCON1: PWM TIMER CONTROL REGISTER 1

| R/W-0 | R-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

| PTEN  | PTDIR | —   | _   | —   | —   | —   | —     |

| bit 7 |       |     |     |     |     |     | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

```

bit 7PTEN: PWM Time Base Timer Enable bit1 = PWM time base is on<br/>0 = PWM time base is offbit 6PTDIR: PWM Time Base Count Direction Status bit<br/>1 = PWM time base counts down<br/>0 = PWM time base counts upbit 5-0Unimplemented: Read as '0'

```

#### 14.6.5 COMPLEMENTARY PWM OPERATION

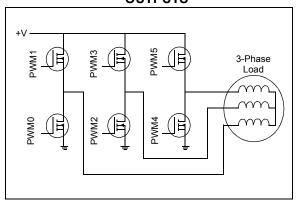

The Complementary mode of PWM operation is useful to drive one or more power switches in half-bridge configuration, as shown in Figure 14-16. This inverter topology is typical for a 3-phase induction motor, brushless DC motor or 3-phase Uninterruptible Power Supply (UPS) control applications.

Each upper/lower power switch pair is fed by a complementary PWM signal. Dead time may be optionally inserted during device switching, where both outputs are inactive for a short period (see **Section 14.7 "Dead-Time Generators"**).

In Complementary mode, the duty cycle comparison units are assigned to the PWM outputs as follows:

- · PDC0 register controls PWM1/PWM0 outputs

- · PDC1 register controls PWM3/PWM2 outputs

- PDC2 register controls PWM5/PWM4 outputs

PWM1/3/5 are the main PWMs that are controlled by the PDCx registers and PWM0/2/4 are the complemented outputs. When using the PWMs to control the half-bridge, the odd number PWMs can be used to control the upper power switch and the even numbered PWMs can be used for the lower switches.

#### FIGURE 14-16: TYPICAL LOAD FOR COMPLEMENTARY PWM OUTPUTS

The Complementary mode is selected for each PWM I/O pin pair by clearing the appropriate PMODx bit in the PWMCON0 register. The PWM I/O pins are set to Complementary mode by default upon all kinds of device Resets.

| Bit 7                                                | Bit 6                                                           | Bit 5                                                                                          | Bit 4                                                                                                                                                          | Bit 3                                                                                                                                                                                                                  | Bit 2                                                                                                                                                               | Bit 1                                                                                                                                                                                                                            | Bit 0                                                                                                                                                                                                                                                                             | Reset<br>Values<br>on Page:                                                                                                                                                                                                                                                                                              |

|------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GIE/GIEH                                             | PEIE/GIEL                                                       | TMR0IE                                                                                         | INT0IE                                                                                                                                                         | RBIE                                                                                                                                                                                                                   | TMR0IF                                                                                                                                                              | INT0IF                                                                                                                                                                                                                           | RBIF                                                                                                                                                                                                                                                                              | 47                                                                                                                                                                                                                                                                                                                       |

| _                                                    | ADIF                                                            | RCIF                                                                                           | TXIF                                                                                                                                                           | CMP2IF                                                                                                                                                                                                                 | CMP1IF                                                                                                                                                              | CMP0IF                                                                                                                                                                                                                           | TMR1IF                                                                                                                                                                                                                                                                            | 49                                                                                                                                                                                                                                                                                                                       |

| _                                                    | ADIE                                                            | RCIE                                                                                           | TXIE                                                                                                                                                           | CMP2IE                                                                                                                                                                                                                 | CMP1IE                                                                                                                                                              | CMP0IE                                                                                                                                                                                                                           | TMR1IE                                                                                                                                                                                                                                                                            | 49                                                                                                                                                                                                                                                                                                                       |

| _                                                    | ADIP                                                            | RCIP                                                                                           | TXIP                                                                                                                                                           | CMP2IP                                                                                                                                                                                                                 | CMP1IP                                                                                                                                                              | CMP0IP                                                                                                                                                                                                                           | TMR1IP                                                                                                                                                                                                                                                                            | 49                                                                                                                                                                                                                                                                                                                       |

| SPEN                                                 | RX9                                                             | SREN                                                                                           | CREN                                                                                                                                                           | ADDEN                                                                                                                                                                                                                  | FERR                                                                                                                                                                | OERR                                                                                                                                                                                                                             | RX9D                                                                                                                                                                                                                                                                              | 48                                                                                                                                                                                                                                                                                                                       |

| EUSART T                                             | ransmit Reg                                                     | ister                                                                                          |                                                                                                                                                                |                                                                                                                                                                                                                        |                                                                                                                                                                     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                   | 48                                                                                                                                                                                                                                                                                                                       |

| CSRC                                                 | TX9                                                             | TXEN                                                                                           | SYNC                                                                                                                                                           | SENDB                                                                                                                                                                                                                  | BRGH                                                                                                                                                                | TRMT                                                                                                                                                                                                                             | TX9D                                                                                                                                                                                                                                                                              | 48                                                                                                                                                                                                                                                                                                                       |

| ABDOVF                                               | RCIDL                                                           | RXDTP                                                                                          | TXCKP                                                                                                                                                          | BRG16                                                                                                                                                                                                                  | —                                                                                                                                                                   | WUE                                                                                                                                                                                                                              | ABDEN                                                                                                                                                                                                                                                                             | 48                                                                                                                                                                                                                                                                                                                       |

| SPBRGH EUSART Baud Rate Generator Register High Byte |                                                                 |                                                                                                |                                                                                                                                                                |                                                                                                                                                                                                                        |                                                                                                                                                                     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                          |

| EUSART B                                             | aud Rate G                                                      | enerator Re                                                                                    | gister Low                                                                                                                                                     | Byte                                                                                                                                                                                                                   |                                                                                                                                                                     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                   | 48                                                                                                                                                                                                                                                                                                                       |

|                                                      | GIE/GIEH<br>—<br>SPEN<br>EUSART T<br>CSRC<br>ABDOVF<br>EUSART B | GIE/GIEHPEIE/GIEL—ADIF—ADIE—ADIPSPENRX9EUSART Transmit RegCSRCTX9ABDOVFRCIDLEUSART Baud Rate G | GIE/GIEHPEIE/GIELTMR0IE—ADIFRCIF—ADIERCIE—ADIPRCIPSPENRX9SRENEUSART Transmit RegisterCSRCTX9CSRCTX9TXENABDOVFRCIDLRXDTPEUSART Baud Rate Generator RegisterCSRC | GIE/GIEHPEIE/GIELTMR0IEINT0IEOIE/GIEHPEIE/GIELTMR0IEINT0IEOIEADIFRCIFTXIFOIEADIERCIPTXIPOIEADIPRCIPTXIPSPENRX9SRENCRENEUSART Transmit RegisterCRENSYNCABDOVFRCIDLRXDTPTXCKPEUSART Bud Rate Generator Register HighCREN | GIE/GIEHPEIE/GIELTMR0IEINT0IERBIEADIFRCIFTXIFCMP2IFADIERCIETXIECMP2IEADIPRCIPTXIPCMP2IPSPENRX9SRENCRENADDENEUSARTTansmit RejsterSYNCSENDBABDOVFRCIDLRXDTPTXCKPBRG16 | GIE/GIEHPEIE/GIELTMROIEINTOIERBIETMROIFADIFRCIFTXIFCMP2IFCMP1IFADIERCIETXIECMP2IECMP1IEADIPRCIPTXIPCMP2IPCMP1IPSPENRX9SRENCRENADDENFERREUSART Transmit RegisterSYNCSENDBBRGHABDOVFRCIDLRXDTPTXCKPBRG16EUSART BULRATESHARSHARSHAR | GIE/GIEHPEIE/GIELTMR0IEINT0IERBIETMR0IFINT0IFADIFRCIFTXIFCMP2IFCMP1IFCMP0IFADIERCIETXIECMP2IECMP1IECMP0IEADIPRCIPTXIPCMP2IPCMP1IPCMP0IPSPENRX9SRENCRENADDENFERROERREUSART Transmit RegisterSYNCSENDBBRGHTRMTABDOVFRCIDLRXDTPTXCKPBRG16WUEEUSART BUTSUBARTSUBARTSUBARTSUBARTSUBART | GIE/GIEHPEIE/GIELTMROIEINTOIERBIETMROIFINTOIFRBIFADIFRCIFTXIFCMP2IFCMP1IFCMP0IFTMR1IFADIERCIETXIECMP2IECMP1IECMP0IETMR1IFADIPRCIPTXIPCMP2IPCMP1IPCMP0IPTMR1IPSPENRX9SRENCRENADDENFERROERRRX9DEUSART Transmit RegisterSYNCSENDBBRGHTRMTTX9DABDOVFRCIDLRXDTPTXCKPBRG16WUEABDENEUSART But Rate Generator Register High Byte |

#### TABLE 15-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

**Legend:** — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

#### 15.3.2 EUSART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either the Single Receive Enable bit, SREN (RCSTA<5>), or the Continuous Receive Enable bit, CREN (RCSTA<4>). Data is sampled on the RX pin on the falling edge of the clock.

If enable bit, SREN, is set, only a single word is received. If enable bit, CREN, is set, the reception is continuous until CREN is cleared. If both bits are set, then CREN takes precedence.

To set up a Synchronous Master Reception:

FIGURE 15-13:

- 1. If any error occurred, clear the error by clearing bit, CREN.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

- 3. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 4. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 5. Ensure bits, CREN and SREN, are clear.

- 6. If the signal from the CK pin is to be inverted, set the TXCKP bit.

- 7. If interrupts are desired, set enable bit, RCIE.

- 8. If 9-bit reception is desired, set bit, RX9.

- 9. If a single reception is required, set bit, SREN. For continuous reception, set bit, CREN.

- 10. Interrupt flag bit, RCIF, will be set when reception is complete and an interrupt will be generated if the enable bit, RCIE, was set.

- 11. Read the RCSTA register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 12. Read the 8-bit received data by reading the RCREG register.

| Q2 Q3 C                  | 14 Q1 Q2 Q3 Q4 | Q1 Q2 Q3 (             | Q4 Q1 Q2 Q3 Q4 | 4 Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4      | Q1 Q2 Q3 Q4   | Q1 Q2 Q3 Q4 | 1 Q1 Q2 Q3 Q4 | 4 Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4    |

|--------------------------|----------------|------------------------|----------------|---------------|------------------|---------------|-------------|---------------|---------------|----------------|

| RA3/RX/DT<br>pin         | :X             | bit 0                  | bit 1          | bit 2         | bit 3            | bit 4         | bit 5       | bit 6         | bit 7         |                |

| RA2/TX/CK pin<br>(TXCKP) | Ļ              |                        | ÷              | ;<br>         | ÷                | $\frac{1}{2}$ | :<br>:<br>  | $\frac{1}{2}$ | ;             | <br> <br> <br> |

| Write to<br>bit SREN     |                | 1<br><del>1</del><br>1 | •<br>•         | 1<br>1<br>1   | 1<br>+<br>1<br>1 | 1<br>1<br>1   | 1<br>1<br>1 | 1<br>         | 1<br>1<br>1   | •<br>•<br>•    |

| SREN bit                 |                |                        | ;              | •             | <u>,</u>         | •             | •           | ;             | ;             |                |

| CREN bit <u>'0'</u>      | 1              | 1<br>1                 | 1              | 1             | 1                | 1<br>1        | 1           | 1             | 1             | ʻ0'            |

| RCIF bit<br>(Interrupt)  | ,<br>,<br>,    | ,<br>,<br>,            |                | ,<br>,<br>,   | ,<br>,<br>,      | ,<br>,<br>,   | ,<br>,<br>, | ,<br>,<br>,   | ;<br>;        |                |

| Read<br>RXREG            | 1<br>1         | 1<br>1<br>1            | 1<br>1<br>1    | 1<br>7<br>1   | 1<br>1<br>1      | ,<br>,<br>,   | 1<br>1<br>1 | 1<br>1<br>1   | 1<br>1<br>1   |                |

|                          | 1              | 1<br>1                 | 1<br>1         |               | 1<br>1<br>1      |               | 1<br>1<br>1 | 1             | 1<br>1<br>1   |                |

| Note: Timing diagram     | demonstrate    | es Sync Ma             | aster mode w   | ith bit SREN  | = 1 and bit      | BRGH = 0.     |             |               |               |                |

SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

#### TABLE 15-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

| Name      | Bit 7                                           | Bit 6       | Bit 5         | Bit 4        | Bit 3       | Bit 2        | Bit 1      | Bit 0      | Reset<br>Values<br>on Page: |

|-----------|-------------------------------------------------|-------------|---------------|--------------|-------------|--------------|------------|------------|-----------------------------|

| INTCON    | GIE/GIEH                                        | PEIE/GIEL   | TMR0IE        | INT0IE       | RBIE        | TMR0IF       | INT0IF     | RBIF       | 47                          |

| PIR1      | _                                               | ADIF        | RCIF          | TXIF         | CMP2IF      | CMP1IF       | CMP0IF     | TMR1IF     | 49                          |

| PIE1      | —                                               | ADIE        | RCIE          | TXIE         | CMP2IE      | CMP1IE       | CMP0IE     | TMR1IE     | 49                          |

| IPR1      | —                                               | ADIP        | RCIP          | TXIP         | CMP2IP      | CMP1IP       | CMP0IP     | TMR1IP     | 49                          |

| RCSTA     | SPEN                                            | RX9         | SREN          | CREN         | ADDEN       | FERR         | OERR       | RX9D       | 48                          |

| RCREG     | EUSART Receive Register                         |             |               |              |             |              |            | 48         |                             |

| TXSTA     | CSRC                                            | TX9         | TXEN          | SYNC         | SENDB       | BRGH         | TRMT       | TX9D       | 48                          |

| BAUDCON   | ABDOVF                                          | RCIDL       | RXDTP         | TXCKP        | BRG16       | _            | WUE        | ABDEN      | 48                          |

| SPBRGH    | H EUSART Baud Rate Generator Register High Byte |             |               |              |             |              |            | 48         |                             |

| SPBRG     | G EUSART Baud Rate Generator Register Low Byte  |             |               |              |             |              |            | 48         |                             |

| Legend: - |                                                 | mented, rea | d as '0'. Sha | aded cells a | re not used | for synchror | ous master | reception. | •                           |

## REGISTER 20-2: CONFIG2L: CONFIGURATION REGISTER 2 LOW (BYTE ADDRESS 300002h)

|                                                                          |                             |                |                           |                          | •                     |                       | ,                     |

|--------------------------------------------------------------------------|-----------------------------|----------------|---------------------------|--------------------------|-----------------------|-----------------------|-----------------------|

| U-0                                                                      | U-0                         | U-0            | R/P-1                     | R/P-1                    | R/P-1                 | R/P-1                 | R/P-1                 |

| _                                                                        |                             | —              | BORV1 <sup>(1)</sup>      | BORV0 <sup>(1)</sup>     | BOREN1 <sup>(2)</sup> | BOREN0 <sup>(2)</sup> | PWRTEN <sup>(2)</sup> |

| bit 7                                                                    | ·                           |                |                           |                          |                       |                       | bit 0                 |

|                                                                          |                             |                |                           |                          |                       |                       |                       |

| Legend:                                                                  |                             |                |                           |                          |                       |                       |                       |

| R = Readable bit P = Programmable bit U = Unimplemented bit, read as '0' |                             |                |                           |                          |                       |                       |                       |