Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 4x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f1330-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC18F1230 PIC18F1330

- PIC18LF1230 PIC18LF1330

This family offers the advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price – with the addition of highendurance Enhanced Flash program memory. On top of these features, the PIC18F1230/1330 family introduces design enhancements that make these microcontrollers a logical choice for many high-performance, power control and motor control applications.

Peripheral highlights include:

- 14-bit resolution Power Control PWM module

- (PCPWM) with programmable dead-time insertion

The PCPWM can generate up to six complementary PWM outputs with dead-band time insertion. Overdrive current is detected by off-chip analog comparators or the digital Fault input (FLTA).

PIC18F1230/1330 devices also feature Flash program memory and an internal RC oscillator.

## 1.1 New Core Features

#### 1.1.1 nanoWatt TECHNOLOGY

All of the devices in the PIC18F1230/1330 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the internal oscillator block, power consumption during code execution can be reduced by as much as 90%.

- **Multiple Idle Modes:** The controller can also run with its CPU core disabled but the peripherals still active. In these states, power consumption can be reduced even further, to as little as 4% of normal operation requirements.

- **On-the-Fly Mode Switching:** The power-managed modes are invoked by user code during operation, allowing the user to incorporate power-saving ideas into their application's software design.

- Low Consumption in Key Modules: The power requirements for both Timer1 and the Watchdog Timer are minimized. See Section 23.0 "Electrical Characteristics" for values.

## 1.1.2 MULTIPLE OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18F1230/1330 family offer ten different oscillator options, allowing users a wide range of choices in developing application hardware. These include:

- Four Crystal modes, using crystals or ceramic resonators.

- Two External Clock modes, offering the option of using two pins (oscillator input and a divide-by-4 clock output) or one pin (oscillator input, with the second pin reassigned as general I/O).

- Two External RC Oscillator modes with the same pin options as the External Clock modes.

- An internal oscillator block which provides an 8 MHz clock and an INTRC source (approximately 31 kHz), as well as a range of six user-selectable clock frequencies, between 125 kHz to 4 MHz, for a total of eight clock frequencies. This option frees the two oscillator pins for use as additional general purpose I/Os.

- A Phase Lock Loop (PLL) frequency multiplier, available to both the High-Speed Crystal and Internal Oscillator modes, which allows clock speeds of up to 40 MHz. Used with the internal oscillator, the PLL gives users a complete selection of clock speeds, from 31 kHz to 32 MHz, all without using an external crystal or clock circuit.

Besides its availability as a clock source, the internal oscillator block provides a stable reference source that gives the family additional features for robust operation:

- Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the internal oscillator. If a clock failure occurs, the controller is switched to the internal oscillator block, allowing for continued low-speed operation or a safe application shutdown.

- **Two-Speed Start-up:** This option allows the internal oscillator to serve as the clock source from Power-on Reset, or wake-up from Sleep mode, until the primary clock source is available.

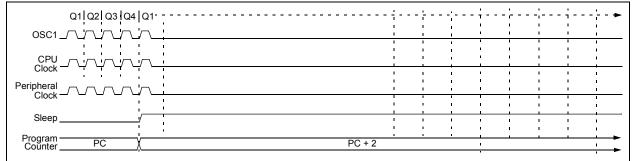

## 4.3 Sleep Mode

The power-managed Sleep mode in the PIC18F1230/ 1330 devices is identical to the legacy Sleep mode offered in all other PIC devices. It is entered by clearing the IDLEN bit (the default state on device Reset) and executing the SLEEP instruction. This shuts down the selected oscillator (Figure 4-5). All clock source status bits are cleared.

Entering the Sleep mode from any other mode does not require a clock switch. This is because no clocks are needed once the controller has entered Sleep. If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run.

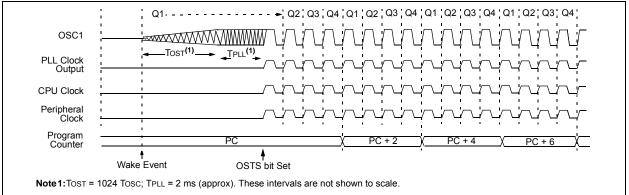

When a wake event occurs in Sleep mode (by interrupt, Reset or WDT time-out), the device will not be clocked until the clock source selected by the SCS1:SCS0 bits becomes ready (see Figure 4-6), or it will be clocked from the internal oscillator block if either the Two-Speed Start-up or the Fail-Safe Clock Monitor are enabled (see **Section 20.0 "Special Features of the CPU"**). In either case, the OSTS bit is set when the primary clock is providing the device clocks. The IDLEN and SCS bits are not affected by the wake-up.

## 4.4 Idle Modes

The Idle modes allow the controller's CPU to be selectively shut down while the peripherals continue to operate. Selecting a particular Idle mode allows users to further manage power consumption.

If the IDLEN bit is set to a '1' when a SLEEP instruction is executed, the peripherals will be clocked from the clock source selected using the SCS1:SCS0 bits; however, the CPU will not be clocked. The clock source status bits are not affected. Setting IDLEN and executing a SLEEP instruction provides a quick method of switching from a given Run mode to its corresponding Idle mode.

If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run.

Since the CPU is not executing instructions, the only exits from any of the Idle modes are by interrupt, WDT time-out or a Reset. When a wake event occurs, CPU execution is delayed by an interval of TCSD (parameter 38, Table 23-10) while it becomes ready to execute code. When the CPU begins executing code, it resumes with the same clock source for the current Idle mode. For example, when waking from RC\_IDLE mode, the internal oscillator block will clock the CPU and peripherals (in other words, RC\_RUN mode). The IDLEN and SCS bits are not affected by the wake-up.

While in any Idle mode or the Sleep mode, a WDT time-out will result in a WDT wake-up to the Run mode currently specified by the SCS1:SCS0 bits.

## 5.4 Brown-out Reset (BOR)

PIC18F1230/1330 devices implement a BOR circuit that provides the user with a number of configuration and power-saving options. The BOR is controlled by the BORV1:BORV0 and BOREN1:BOREN0 Configuration bits. There are a total of four BOR configurations which are summarized in Table 5-1.

The BOR threshold is set by the BORV1:BORV0 bits. If BOR is enabled (any values of BOREN1:BOREN0 except '00'), any drop of VDD below VBOR (parameter D005) for greater than TBOR (parameter 35) will reset the device. A Reset may or may not occur if VDD falls below VBOR for less than TBOR. The chip will remain in Brown-out Reset until VDD rises above VBOR.

If the Power-up Timer is enabled, it will be invoked after VDD rises above VBOR; it then will keep the chip in Reset for an additional time delay, TPWRT (parameter 33). If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above VBOR, the Power-up Timer will execute the additional time delay.

BOR and the Power-on Timer (PWRT) are independently configured. Enabling Brown-out Reset does not automatically enable the PWRT.

### 5.4.1 SOFTWARE ENABLED BOR

When BOREN1:BOREN0 = 01, the BOR can be enabled or disabled by the user in software. This is done with the control bit, SBOREN (RCON<6>). Setting SBOREN enables the BOR to function as previously described. Clearing SBOREN disables the BOR entirely. The SBOREN bit operates only in this mode; otherwise it is read as '0'.

Placing the BOR under software control gives the user the additional flexibility of tailoring the application to its environment without having to reprogram the device to change BOR configuration. It also allows the user to tailor device power consumption in software by eliminating the incremental current that the BOR consumes. While the BOR current is typically very small, it may have some impact in low-power applications.

| Note: | Even when BOR is under software control,   |

|-------|--------------------------------------------|

|       | the Brown-out Reset voltage level is still |

|       | set by the BORV1:BORV0 Configuration       |

|       | bits. It cannot be changed in software.    |

### 5.4.2 DETECTING BOR

When Brown-out Reset is enabled, the BOR bit always resets to '0' on any Brown-out Reset or Power-on Reset event. This makes it difficult to determine if a Brown-out Reset event has occurred just by reading the state of BOR alone. A more reliable method is to simultaneously check the state of both POR and BOR. This assumes that the POR bit is reset to '1' in software immediately after any Power-on Reset event. If BOR is '0' while POR is '1', it can be reliably assumed that a Brown-out Reset event has occurred.

## 5.4.3 DISABLING BOR IN SLEEP MODE

When BOREN1:BOREN0 = 10, the BOR remains under hardware control and operates as previously described. Whenever the device enters Sleep mode, however, the BOR is automatically disabled. When the device returns to any other operating mode, BOR is automatically re-enabled.

This mode allows for applications to recover from brown-out situations, while actively executing code, when the device requires BOR protection the most. At the same time, it saves additional power in Sleep mode by eliminating the small incremental BOR current.

| BOR Con | BOR Configuration Statu |                     |                                                                                    |

|---------|-------------------------|---------------------|------------------------------------------------------------------------------------|

| BOREN1  | BOREN0                  | SBOREN<br>(RCON<6>) | BOR Operation                                                                      |

| 0       | 0                       | Unavailable         | BOR disabled; must be enabled by reprogramming the Configuration bits.             |

| 0       | 1                       | Available           | BOR enabled in software; operation controlled by SBOREN.                           |

| 1       | 0                       | Unavailable         | BOR enabled in hardware in Run and Idle modes, disabled during Sleep mode.         |

| 1       | 1                       | Unavailable         | BOR enabled in hardware; must be disabled by reprogramming the Configuration bits. |

TABLE 5-1:BOR CONFIGURATIONS

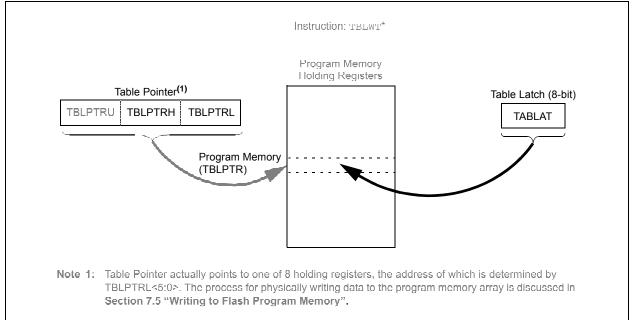

## FIGURE 7-2: TABLE WRITE OPERATION

## 7.2 Control Registers

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. These include the:

- EECON1 register

- EECON2 register

- TABLAT register

- TBLPTR registers

## 7.2.1 EECON1 AND EECON2 REGISTERS

The EECON1 register (Register 7-1) is the control register for memory accesses. The EECON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

The EEPGD control bit determines if the access will be a program or data EEPROM memory access. When clear, any subsequent operations will operate on the data EEPROM memory. When set, any subsequent operations will operate on the program memory.

The CFGS control bit determines if the access will be to the Configuration/Calibration registers or to program memory/data EEPROM memory. When set, subsequent operations will operate on Configuration registers regardless of EEPGD (see **Section 20.0 "Special Features of the CPU"**). When clear, memory selection access is determined by EEPGD. The FREE bit, when set, will allow a program memory erase operation. When FREE is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WR bit is set and cleared when the internal programming timer expires and the write operation is complete.

| Note: | During normal operation, the WRERR         |

|-------|--------------------------------------------|

|       | may read as '1'. This can indicate that a  |

|       | write operation was prematurely termi-     |

|       | nated by a Reset, or a write operation was |

|       | attempted improperly.                      |

The WR control bit initiates write operations. The bit cannot be cleared, only set, in software; it is cleared in hardware at the completion of the write operation.

**Note:** The EEIF interrupt flag bit (PIR2<4>) is set when the write is complete. It must be cleared in software.

| TABLE 10-4: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTB |

|-------------|--------------------------------------------|

|-------------|--------------------------------------------|

| Name    | Bit 7                                                      | Bit 6         | Bit 5        | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|---------|------------------------------------------------------------|---------------|--------------|---------|---------|--------|--------|--------|-----------------------------|

| PORTB   | RB7                                                        | RB6           | RB5          | RB4     | RB3     | RB2    | RB1    | RB0    | 50                          |

| LATB    | PORTB Output Latch Register (Read and Write to Data Latch) |               |              |         |         |        |        |        | 49                          |

| TRISB   | PORTB Dat                                                  | a Direction C | control Regi | ster    |         |        |        |        | 49                          |

| INTCON  | GIE/GIEH PEIE/GIEL TMROIE INTOIE RBIE TMROIF INTOIF RBIF   |               |              |         |         |        |        | 47     |                             |

| INTCON2 | RBPU                                                       | INTEDG0       | INTEDG1      | INTEDG2 | INTEDG3 | TMR0IP | INT3IP | RBIP   | 47                          |

| INTCON3 | INT2IP                                                     | INT1IP        | INT3IE       | INT2IE  | INT1IE  | INT3IF | INT2IF | INT1IF | 47                          |

| CMCON   | C2OUT                                                      | C10UT         | COOUT        | _       | —       | CMEN2  | CMEN1  | CMEN0  | 48                          |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTB.

## 11.1 INTCON Registers

The INTCON registers are readable and writable registers, which contain various enable, priority and flag bits.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

#### REGISTER 11-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0    | R/W-0     | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-x               |

|----------|-----------|--------|--------|-------|--------|--------|---------------------|

| GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF <sup>(1)</sup> |

| bit 7    |           |        |        |       |        |        | bit 0               |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | GIE/GIEH: Global Interrupt Enable bit<br>When IPEN = 0:<br>1 = Enables all unmasked interrupts<br>0 = Disables all interrupts<br>When IPEN = 1:<br>1 = Enables all high-priority interrupts<br>0 = Disables all interrupts                                                                            |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | PEIE/GIEL: Peripheral Interrupt Enable bit<br><u>When IPEN = 0:</u><br>1 = Enables all unmasked peripheral interrupts<br>0 = Disables all peripheral interrupts<br><u>When IPEN = 1:</u><br>1 = Enables all low-priority peripheral interrupts<br>0 = Disables all low-priority peripheral interrupts |

| bit 5 | TMR0IE: TMR0 Overflow Interrupt Enable bit<br>1 = Enables the TMR0 overflow interrupt<br>0 = Disables the TMR0 overflow interrupt                                                                                                                                                                     |

| bit 4 | INTOIE: INTO External Interrupt Enable bit<br>1 = Enables the INTO external interrupt<br>0 = Disables the INTO external interrupt                                                                                                                                                                     |

| bit 3 | <b>RBIE:</b> RB Port Change Interrupt Enable bit<br>1 = Enables the RB port change interrupt<br>0 = Disables the RB port change interrupt                                                                                                                                                             |

| bit 2 | <b>TMR0IF:</b> TMR0 Overflow Interrupt Flag bit<br>1 = TMR0 register has overflowed (must be cleared in software)<br>0 = TMR0 register did not overflow                                                                                                                                               |

| bit 1 | INTOIF: INTO External Interrupt Flag bit<br>1 = The INTO external interrupt occurred (must be cleared in software)<br>0 = The INTO external interrupt did not occur                                                                                                                                   |

| bit 0 | <b>RBIF:</b> RB Port Change Interrupt Flag bit <sup>(1)</sup><br>1 = At least one of the RB7:RB4 pins changed state (must be cleared in software)<br>0 = None of the RB7:RB4 pins have changed state                                                                                                  |

|       |                                                                                                                                                                                                                                                                                                       |

**Note 1:** A mismatch condition will continue to set this bit. Reading PORTB will end the mismatch condition and allow the bit to be cleared.

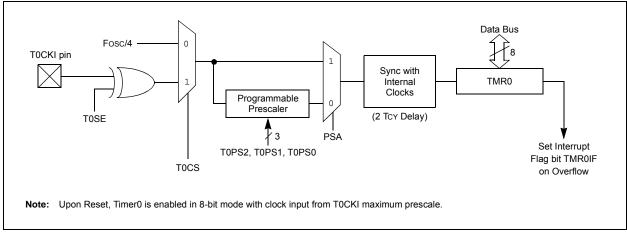

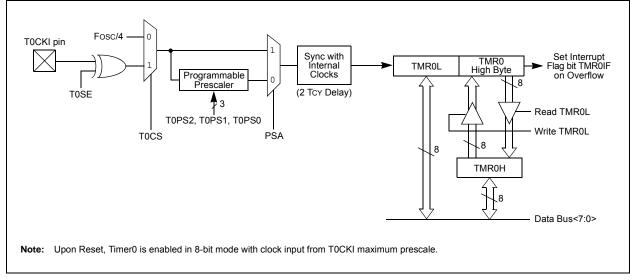

## FIGURE 12-1: TIMER0 BLOCK DIAGRAM IN 8-BIT MODE

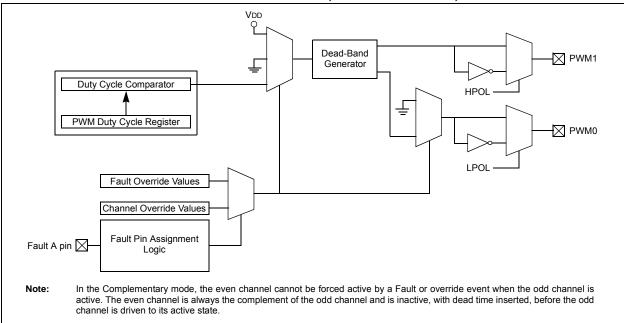

#### FIGURE 14-2: PWM MODULE BLOCK DIAGRAM, ONE OUTPUT PAIR, COMPLEMENTARY MODE

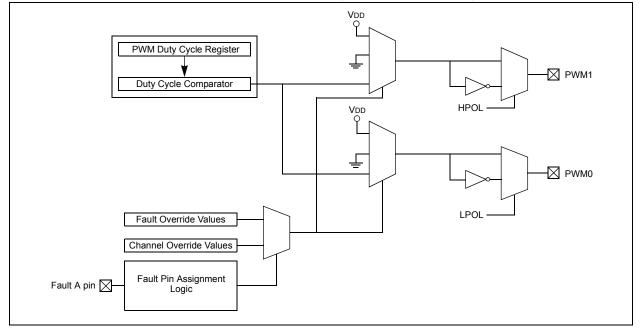

#### FIGURE 14-3: PWM MODULE BLOCK DIAGRAM, ONE OUTPUT PAIR, INDEPENDENT MODE

This module contains three duty cycle generators, numbered 0 through 2. The module has six PWM output pins, numbered 0 through 5. The six PWM outputs are grouped into output pairs of even and odd numbered outputs. In Complementary modes, the even PWM pins must always be the complement of the corresponding odd PWM pins. For example, PWM0 will be the complement of PWM1 and PWM2 will be the complement of PWM3. The dead-time generator inserts an OFF period called "dead time" between the going OFF of one pin to the going ON of the complementary pin of the paired pins. This is to prevent damage to the power switching devices that will be connected to the PWM output pins.

The time base for the PWM module is provided by its own 12-bit timer, which also incorporates selectable prescaler and postscaler options.

<sup>© 2009</sup> Microchip Technology Inc.

NOTES:

| R/W-0                         | R/W-0                                             | R/W-0                                                   | R/W-0         | R/W-0            | R/W-0           | R-1             | R/W-0 |

|-------------------------------|---------------------------------------------------|---------------------------------------------------------|---------------|------------------|-----------------|-----------------|-------|

| CSRC                          | TX9                                               | TXEN <sup>(1)</sup>                                     | SYNC          | SENDB            | BRGH            | TRMT            | TX9D  |

| bit 7                         |                                                   |                                                         |               |                  |                 |                 | bit   |

|                               |                                                   |                                                         |               |                  |                 |                 |       |

| <b>Legend:</b><br>R = Readabl | e hit                                             | W = Writable                                            | hit           | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value at                 |                                                   | '1' = Bit is set                                        |               | '0' = Bit is cle |                 | x = Bit is unki | nown  |

|                               |                                                   |                                                         |               | 0 200000         |                 |                 |       |

| bit 7                         | CSRC: Clock                                       | k Source Select                                         | bit           |                  |                 |                 |       |

|                               | <u>Asynchronou</u><br>Don't care.                 | <u>us mode:</u>                                         |               |                  |                 |                 |       |

|                               |                                                   | <u>s mode:</u><br>node (clock gene<br>ode (clock from o |               |                  |                 |                 |       |

| bit 6                         |                                                   | ansmit Enable b                                         |               |                  |                 |                 |       |

|                               |                                                   | 9-bit transmissio<br>3-bit transmissio                  |               |                  |                 |                 |       |

| bit 5                         | TXEN: Trans                                       | smit Enable bit <sup>(1</sup>                           | )             |                  |                 |                 |       |

|                               | 1 = Transmit<br>0 = Transmit                      |                                                         |               |                  |                 |                 |       |

| bit 4                         | SYNC: EUS                                         | ART Mode Sele                                           | ct bit        |                  |                 |                 |       |

|                               | 1 = Synchroi<br>0 = Asynchro                      |                                                         |               |                  |                 |                 |       |

| bit 3                         | SENDB: Ser                                        | nd Break Charad                                         | cter bit      |                  |                 |                 |       |

|                               |                                                   | <u>us mode:</u><br>nc Break on ne»<br>eak transmissior  |               | n (cleared by h  | ardware upon    | completion)     |       |

|                               | Synchronous<br>Don't care.                        | <u>s mode:</u>                                          |               |                  |                 |                 |       |

| bit 2                         | BRGH: High                                        | Baud Rate Sele                                          | ect bit       |                  |                 |                 |       |

|                               | <u>Asynchronou</u><br>1 = High spe<br>0 = Low spe | ed                                                      |               |                  |                 |                 |       |

|                               | Synchronous<br>Unused in th                       | <u>s mode:</u>                                          |               |                  |                 |                 |       |

| bit 1                         | TRMT: Trans                                       | smit Shift Regist                                       | er Status bit |                  |                 |                 |       |

|                               | 1 = TSR emp<br>0 = TSR full                       | oty                                                     |               |                  |                 |                 |       |

| bit 0                         | TX9D: 9th bi                                      | t of Transmit Da                                        | ita           |                  |                 |                 |       |

|                               | Can be addr                                       | ess/data bit or a                                       | parity bit.   |                  |                 |                 |       |

| Note 1. S                     | REN/CREN ove                                      | rrides TXEN in 9                                        | Sync mode     |                  |                 |                 |       |

### REGISTER 15-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER

Note 1: SREN/CREN overrides TXEN in Sync mode.

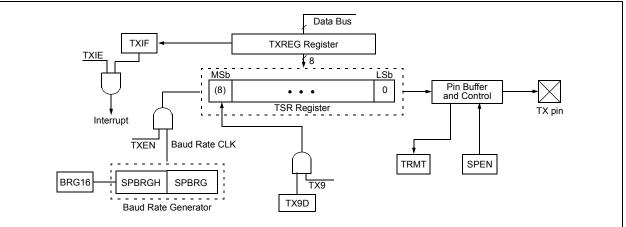

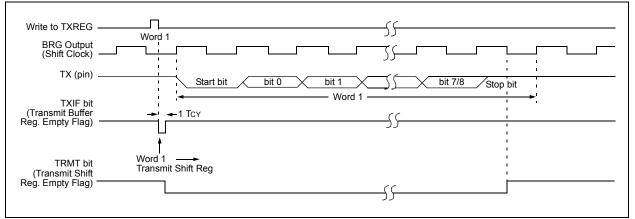

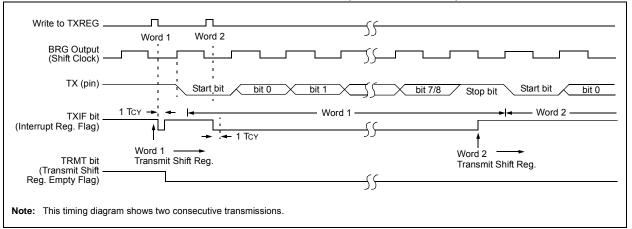

## FIGURE 15-3: EUSART TRANSMIT BLOCK DIAGRAM

## FIGURE 15-5: ASYNCHRONOUS TRANSMISSION (BACK-TO-BACK)

### 15.2.2 EUSART ASYNCHRONOUS RECEIVER

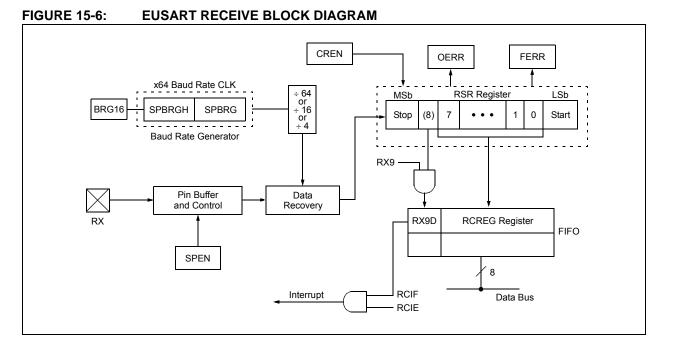

The receiver block diagram is shown in Figure 15-6. The data is received on the RX pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc. This mode would typically be used in RS-232 systems.

To set up an Asynchronous Reception:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, set enable bit RCIE.

- 4. If 9-bit reception is desired, set bit RX9.

- 5. Enable the reception by setting bit CREN.

- Flag bit, RCIF, will be set when reception is complete and an interrupt will be generated if enable bit, RCIE, was set.

- Read the RCSTA register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

- 10. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

# 15.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are required, set the RCEN bit and select the desired priority level with the RCIP bit.

- 4. Set the RX9 bit to enable 9-bit reception.

- 5. Set the ADDEN bit to enable address detect.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF bit will be set when reception is complete. The interrupt will be Acknowledged if the RCIE and GIE bits are set.

- 8. Read the RCSTA register to determine if any error occurred during reception, as well as read bit 9 of data (if applicable).

- 9. Read RCREG to determine if the device is being addressed.

- 10. If any error occurred, clear the CREN bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and interrupt the CPU.

## REGISTER 20-6: CONFIG4L: CONFIGURATION REGISTER 4 LOW (BYTE ADDRESS 300006h)

| R/P-1                                                             | R/P-0                     | R/P-0                         | R/P-0          | U-0           | U-0                                 | U-0         | R/P-1  |  |  |

|-------------------------------------------------------------------|---------------------------|-------------------------------|----------------|---------------|-------------------------------------|-------------|--------|--|--|

| BKBUG                                                             | XINST                     | BBSIZ1                        | BBSIZ0         |               | _                                   | _           | STVREN |  |  |

| bit 7                                                             |                           |                               |                |               |                                     |             | bit C  |  |  |

|                                                                   |                           |                               |                |               |                                     |             |        |  |  |

| Legend:                                                           |                           |                               |                |               |                                     |             |        |  |  |

| R = Readable                                                      | bit                       | P = Program                   | mable bit      | U = Unimpler  | mented bit, read                    | as '0'      |        |  |  |

| -n = Value whe                                                    | en device is unp          | programmed                    |                | u = Unchang   | ed from progran                     | nmed state  |        |  |  |

|                                                                   |                           |                               |                |               |                                     |             |        |  |  |

| bit 7                                                             |                           | kground Debu                  | 00             |               |                                     |             |        |  |  |

|                                                                   |                           |                               |                |               | gured as genera<br>edicated to In-C |             | pins   |  |  |

| bit 6                                                             | •                         | ded Instruction               |                |               |                                     | I can Debug |        |  |  |

| 1 = Instruction set extension and Indexed Addressing mode enabled |                           |                               |                |               |                                     |             |        |  |  |

|                                                                   |                           |                               |                | Addressing me |                                     |             |        |  |  |

| bit 5-4                                                           | BBSIZ<1:0>:               | Boot Block Siz                | ze Select bits |               |                                     |             |        |  |  |

|                                                                   | For PIC18F1               |                               |                |               |                                     |             |        |  |  |

|                                                                   | 11 = 1  kW Bc             |                               |                |               |                                     |             |        |  |  |

|                                                                   | 10 = 1 kW Bc              | oot Block size                |                |               |                                     |             |        |  |  |

|                                                                   |                           | oot Block size                |                |               |                                     |             |        |  |  |

|                                                                   | For PIC18F12              | 230 device:                   |                |               |                                     |             |        |  |  |

|                                                                   | 11 = 512W Boot Block size |                               |                |               |                                     |             |        |  |  |

|                                                                   | 10 = 512W Boot Block size |                               |                |               |                                     |             |        |  |  |

|                                                                   |                           | oot Block size oot Block size |                |               |                                     |             |        |  |  |

| bit 3                                                             |                           | ted: Maintain                 | ae '0'         |               |                                     |             |        |  |  |

| bit 2-1                                                           |                           | ted: Read as '                |                |               |                                     |             |        |  |  |

| bit 0                                                             | •                         | ack Overflow/U                |                | et Enable bit |                                     |             |        |  |  |

| ~                                                                 |                           | stack overflow                |                |               |                                     |             |        |  |  |

|                                                                   |                           |                               |                |               |                                     |             |        |  |  |

| ADDWFC      | )                        | ADD W a                   | ANDL                                      |                         |        |

|-------------|--------------------------|---------------------------|-------------------------------------------|-------------------------|--------|

| Syntax:     |                          | ADDWFC                    | f {,d {,a}}                               |                         | Syntax |

| Operands:   |                          | $0 \leq f \leq 255$       |                                           |                         | Opera  |

|             |                          | d ∈ [0,1]<br>a ∈ [0,1]    |                                           |                         | Opera  |

| Operation:  |                          | a ∈ [0,1]<br>(W) + (f) +  |                                           |                         | Status |

| Status Affe |                          | (W) + (I) +<br>N,OV, C, D | . ,                                       |                         | Encod  |

| Encoding:   | cieu.                    | 0010                      | 00da ff:                                  | ff ffff                 | Descri |

| Description | <b>.</b> .               |                           | Carry flag and                            |                         | ]      |

| Description | 1.                       |                           | If 'd' is '0', the                        |                         | words  |

|             |                          | •                         | /. If 'd' is '1', th                      |                         | Cycles |

|             |                          |                           | ata memory lo<br>he Access Ba             |                         | Q Cyc  |

|             |                          |                           | he BSR is use                             |                         |        |

|             |                          | GPR bank.                 | nd the extend                             | ad instruction          |        |

|             |                          |                           | led, this instru                          |                         | . L    |

|             |                          |                           | Literal Offset /                          | 0                       | Examp  |

|             |                          |                           | never f ≤ 95 (5<br>2. <b>2.3 "Byte-Or</b> | ,                       | В      |

|             |                          |                           | ed Instruction                            |                         |        |

|             |                          | Literal Offs              | set Mode" for                             | details.                | A      |

| Words:      |                          | 1                         |                                           |                         |        |

| Cycles:     |                          | 1                         |                                           |                         |        |

| Q Cycle A   | -                        |                           |                                           |                         |        |

|             | Q1                       | Q2                        | Q3                                        | Q4                      | 7      |

| De          | ecode                    | Read<br>register 'f'      | Process<br>Data                           | Write to<br>destination |        |

|             |                          | regiotor r                | Data                                      | dootination             | 1      |

| Example:    |                          | ADDWFC                    | REG, 0,                                   | 1                       |        |

| Befor       | e Instruc                | tion                      |                                           |                         |        |

|             | Carry bit<br>REG         | = 1<br>= 02h              |                                           |                         |        |

|             | W                        | = 4Dh                     |                                           |                         |        |

|             | Instruction<br>Carry bit |                           |                                           |                         |        |

|             | REŚ                      | = 02h                     |                                           |                         |        |

|             | W                        | = 50h                     |                                           |                         |        |

| AND                            | DLW               | AND Lite                   | ral with | W               |    |            |  |

|--------------------------------|-------------------|----------------------------|----------|-----------------|----|------------|--|

| Synta                          | ax:               | ANDLW                      | k        |                 |    |            |  |

| Oper                           | ands:             | $0 \le k \le 25$           | 5        |                 |    |            |  |

| Oper                           | ation:            | (W) .AND.                  | $k\toW$  |                 |    |            |  |

| Statu                          | is Affected:      | N, Z                       |          |                 |    |            |  |

| Enco                           | oding:            | 0000                       | 1011     | kkk             | k  | kkkk       |  |

| Description:                   |                   | The conte<br>8-bit literal |          |                 |    |            |  |

| Word                           | ls:               | 1                          |          |                 |    |            |  |

| Cycle                          | es:               | 1                          |          |                 |    |            |  |

| QC                             | ycle Activity:    |                            |          |                 |    |            |  |

|                                | Q1                | Q2                         | Q        | 3               | Q4 |            |  |

|                                | Decode            | Read literal<br>'k'        |          | Process<br>Data |    | Write to W |  |

| Example:<br>Before Instruction |                   | ANDLW                      | 05Fh     |                 |    |            |  |

|                                | W                 | = A3h                      |          |                 |    |            |  |

|                                | After Instruction |                            |          |                 |    |            |  |

|                                |                   |                            |          |                 |    |            |  |

| BCF                                  | Bit Clear f                                                                                                                                                                                                                                                                                                   | BN                            | Branch if Negative                                                                                                                                                                                                                                                                         |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                              | BCF f, b {,a}                                                                                                                                                                                                                                                                                                 | Syntax:                       | BN n                                                                                                                                                                                                                                                                                       |

| Operands:                            | $0 \leq f \leq 255$                                                                                                                                                                                                                                                                                           | Operands:                     | $-128 \le n \le 127$                                                                                                                                                                                                                                                                       |

|                                      | $\begin{array}{l} 0 \leq b \leq 7 \\ a \in [0,1] \end{array}$                                                                                                                                                                                                                                                 | Operation:                    | if Negative bit is '1',<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                                                  |

| Operation:                           | $0 \rightarrow f \le b >$                                                                                                                                                                                                                                                                                     | Status Affected:              | None                                                                                                                                                                                                                                                                                       |

| Status Affected:                     | None                                                                                                                                                                                                                                                                                                          | Encoding:                     | 1110 0110 nnnn nnnn                                                                                                                                                                                                                                                                        |

| Encoding:<br>Description:            | 1001bbbaffffffffBit 'b' in register 'f' is cleared.If 'a' is '0', the Access Bank is selected.If 'a' is '1', the BSR is used to select theGPR bank.If 'a' is '0' and the extended instructionset is enabled, this instruction operatesin Indexed Literal Offset Addressingmode whenever $f \le 95$ (5Fh). See | Description:                  | If the Negative bit is '1', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two-cycle instruction. |

|                                      | Section 22.2.3 "Byte-Oriented and                                                                                                                                                                                                                                                                             | Words:                        | 1                                                                                                                                                                                                                                                                                          |

|                                      | Bit-Oriented Instructions in Indexed                                                                                                                                                                                                                                                                          | Cycles:                       | 1(2)                                                                                                                                                                                                                                                                                       |

| Words:                               | Literal Offset Mode" for details.                                                                                                                                                                                                                                                                             | Q Cycle Activity:<br>If Jump: |                                                                                                                                                                                                                                                                                            |

| Cycles:                              | 1                                                                                                                                                                                                                                                                                                             | Q1                            | Q2 Q3 Q4                                                                                                                                                                                                                                                                                   |

| Q Cycle Activity:                    |                                                                                                                                                                                                                                                                                                               | Decode                        | Read literalProcessWrite to'n'DataPC                                                                                                                                                                                                                                                       |

| Q1<br>Decode                         | Q2 Q3 Q4<br>Read Process Write                                                                                                                                                                                                                                                                                | No<br>operation               | No No No<br>operation operation                                                                                                                                                                                                                                                            |

|                                      | register 'f' Data register 'f'                                                                                                                                                                                                                                                                                | If No Jump:                   |                                                                                                                                                                                                                                                                                            |

| - ·                                  |                                                                                                                                                                                                                                                                                                               | Q1                            | Q2 Q3 Q4                                                                                                                                                                                                                                                                                   |

| Example:<br>Before Instruc           |                                                                                                                                                                                                                                                                                                               | Decode                        | Read literal Process No   'n' Data operation                                                                                                                                                                                                                                               |

| FLAG_R<br>After Instructio<br>FLAG_R | on                                                                                                                                                                                                                                                                                                            | If Negati                     | = address (HERE)<br>on<br>ve = 1;<br>C = address (Jump)                                                                                                                                                                                                                                    |

| DEC                       | FSZ                     | Decremer                                                                                                                                                                                                                                                     | nt f, Skip if                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                    | DCFSN         |  |  |

|---------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------|--|--|

| Synta                     | ax:                     | DECFSZ f                                                                                                                                                                                                                                                     | <sup>;</sup> {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      | Syntax:       |  |  |

| Oper                      | ands:                   | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      | Operand       |  |  |

| Oper                      | ation:                  | (f) – 1 $\rightarrow$ de skip if result                                                                                                                                                                                                                      | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      | Operatio      |  |  |

| Statu                     | is Affected:            | None                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      | Status A      |  |  |

| Enco                      | oding:                  | 0010                                                                                                                                                                                                                                                         | 11da ff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ff ffff              | Encoding      |  |  |

| Encoding:<br>Description: |                         | decremente<br>placed in W<br>placed back<br>If the result<br>which is alr<br>and a NOP i<br>it a two-cyc<br>If 'a' is '0', tl<br>If 'a' is '1', tl<br>GPR bank.<br>If 'a' is '0' a<br>set is enabl<br>in Indexed I<br>mode when<br>Section 22<br>Bit-Oriente | The contents of register 'f' are decremented. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is placed back in register 'f'.<br>If the result is '0', the next instruction, which is already fetched, is discarded and a NOP is executed instead, making it a two-cycle instruction.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the GPR bank.<br>If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever $f \le 95$ (5Fh). See <b>Section 22.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode"</b> for details. |                      |               |  |  |

| Word                      | ls:                     | 1                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |               |  |  |

| Cycle                     | es:                     | 1(2)                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      | Words:        |  |  |

| -                         |                         |                                                                                                                                                                                                                                                              | cles if skip ar<br>2-word instru                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      | Cycles:       |  |  |

| QC                        | ycle Activity:          |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |               |  |  |

|                           | Q1                      | Q2                                                                                                                                                                                                                                                           | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Q4                   | Q Cycle       |  |  |

|                           | Decode                  | Read<br>register 'f'                                                                                                                                                                                                                                         | Process<br>Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Write to destination |               |  |  |

| lf sk                     | •                       |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      | If align      |  |  |

| ĺ                         | Q1                      | Q2                                                                                                                                                                                                                                                           | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Q4                   | lf skip:<br>1 |  |  |

|                           | No<br>operation         | No<br>operation                                                                                                                                                                                                                                              | No<br>operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | No<br>operation      |               |  |  |

| lfsk                      |                         | d by 2-word in:                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | operation            | ]   0         |  |  |

|                           | Q1                      | Q2                                                                                                                                                                                                                                                           | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Q4                   | lf skip a     |  |  |