Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 4x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f1330-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

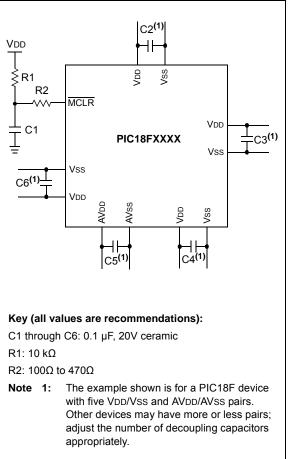

# 2.0 GUIDELINES FOR GETTING STARTED WITH PIC18F MICROCONTROLLERS

# 2.1 Basic Connection Requirements

Getting started with the PIC18F1230/1330 family of 8-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

These pins must also be connected if they are being used in the end application:

- PGC/PGD pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.4 "ICSP Pins"**)

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.5 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for analog modules is implemented

Note: The AVDD and AVSS pins must always be connected, regardless of whether any of the analog modules are being used.

The minimum mandatory connections are shown in Figure 2-1.

# FIGURE 2-1: RECOMMENDED

## MINIMUM CONNECTIONS

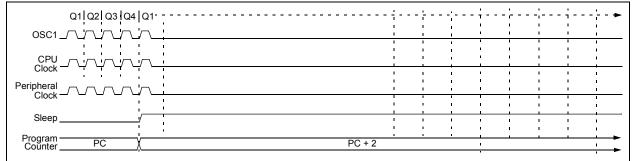

# 4.3 Sleep Mode

The power-managed Sleep mode in the PIC18F1230/ 1330 devices is identical to the legacy Sleep mode offered in all other PIC devices. It is entered by clearing the IDLEN bit (the default state on device Reset) and executing the SLEEP instruction. This shuts down the selected oscillator (Figure 4-5). All clock source status bits are cleared.

Entering the Sleep mode from any other mode does not require a clock switch. This is because no clocks are needed once the controller has entered Sleep. If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run.

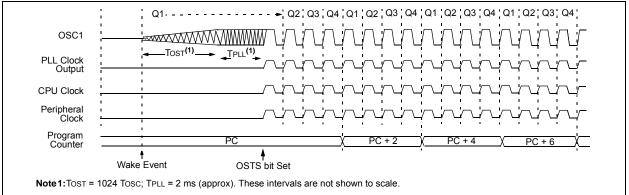

When a wake event occurs in Sleep mode (by interrupt, Reset or WDT time-out), the device will not be clocked until the clock source selected by the SCS1:SCS0 bits becomes ready (see Figure 4-6), or it will be clocked from the internal oscillator block if either the Two-Speed Start-up or the Fail-Safe Clock Monitor are enabled (see **Section 20.0 "Special Features of the CPU"**). In either case, the OSTS bit is set when the primary clock is providing the device clocks. The IDLEN and SCS bits are not affected by the wake-up.

# 4.4 Idle Modes

The Idle modes allow the controller's CPU to be selectively shut down while the peripherals continue to operate. Selecting a particular Idle mode allows users to further manage power consumption.

If the IDLEN bit is set to a '1' when a SLEEP instruction is executed, the peripherals will be clocked from the clock source selected using the SCS1:SCS0 bits; however, the CPU will not be clocked. The clock source status bits are not affected. Setting IDLEN and executing a SLEEP instruction provides a quick method of switching from a given Run mode to its corresponding Idle mode.

If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run.

Since the CPU is not executing instructions, the only exits from any of the Idle modes are by interrupt, WDT time-out or a Reset. When a wake event occurs, CPU execution is delayed by an interval of TCSD (parameter 38, Table 23-10) while it becomes ready to execute code. When the CPU begins executing code, it resumes with the same clock source for the current Idle mode. For example, when waking from RC\_IDLE mode, the internal oscillator block will clock the CPU and peripherals (in other words, RC\_RUN mode). The IDLEN and SCS bits are not affected by the wake-up.

While in any Idle mode or the Sleep mode, a WDT time-out will result in a WDT wake-up to the Run mode currently specified by the SCS1:SCS0 bits.

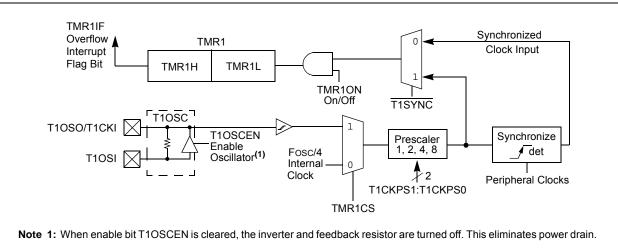

# 13.1 Timer1 Operation

Timer1 can operate in one of these modes:

- As a timer

- As a synchronous counter

- As an asynchronous counter

The operating mode is determined by the Clock Select bit, TMR1CS (T1CON<1>).

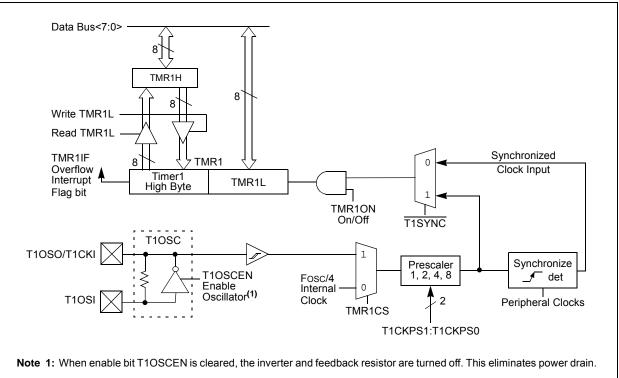

# FIGURE 13-1: TIMER1 BLOCK DIAGRAM

When TMR1CS = 0, Timer1 increments every instruction cycle. When TMR1CS = 1, Timer1 increments on every rising edge of the external clock input or the Timer1 oscillator, if enabled.

When the Timer1 oscillator is enabled (T1OSCEN is set), the T1OSI and T1OSO/T1CKI pins become inputs. That is, the corresponding TRISA bit value is ignored, and the pins are read as '0'.

# FIGURE 13-2: TIMER1 BLOCK DIAGRAM: 16-BIT READ/WRITE MODE

# 13.4 Timer1 Interrupt

The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The Timer1 interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing Timer1 interrupt enable bit, TMR1IE (PIE1<0>).

# 13.5 Timer1 16-Bit Read/Write Mode

Timer1 can be configured for 16-bit reads and writes (see Figure 13-2). When the RD16 control bit (T1CON<7>) is set, the address for TMR1H is mapped to a buffer register for the high byte of Timer1. A read from TMR1L will load the contents of the high byte of Timer1 into the Timer1 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, is valid due to a rollover between reads.

A write to the high byte of Timer1 must also take place through the TMR1H Buffer register. Timer1 high byte is updated with the contents of TMR1H when a write occurs to TMR1L. This allows a user to write all 16 bits to both the high and low bytes of Timer1 at once.

The high byte of Timer1 is not directly readable or writable in this mode. All reads and writes must take place through the Timer1 High Byte Buffer register. Writes to TMR1H do not clear the Timer1 prescaler. The prescaler is only cleared on writes to TMR1L.

# 13.6 Using Timer1 as a Real-Time Clock

Adding an external LP oscillator to Timer1 (such as the one described in **Section 13.2 "Timer1 Oscillator**"), gives users the option to include RTC functionality to their applications. This is accomplished with an inexpensive watch crystal to provide an accurate time base and several lines of application code to calculate the time. When operating in Sleep mode and using a battery or super capacitor as a power source, it can completely eliminate the need for a separate RTC device and battery backup.

The application code routine, RTCisr, shown in Example 13-1, demonstrates a simple method to increment a counter at one-second intervals using an Interrupt Service Routine. Incrementing the TMR1 register pair to overflow triggers the interrupt and calls the routine, which increments the seconds counter by one. Additional counters for minutes and hours are incremented as the previous counter overflow.

Since the register pair is 16 bits wide, counting up to overflow the register directly from a 32.768 kHz clock would take 2 seconds. To force the overflow at the required one-second intervals, it is necessary to preload it. The simplest method is to set the MSb of TMR1H with a BSF instruction. Note that the TMR1L register is never preloaded or altered; doing so may introduce cumulative error over many cycles.

For this method to be accurate, Timer1 must operate in Asynchronous mode and the Timer1 overflow interrupt must be enabled (PIE1<0> = 1), as shown in the routine, RTCinit. The Timer1 oscillator must also be enabled and running at all times.

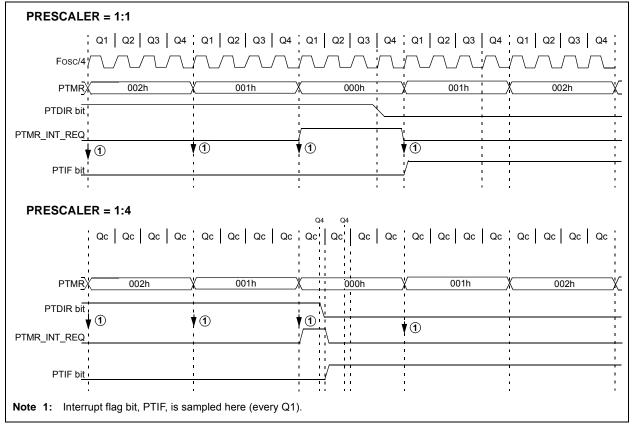

#### FIGURE 14-7: PWM TIME BASE INTERRUPTS, CONTINUOUS UP/DOWN COUNT MODE

© 2009 Microchip Technology Inc.

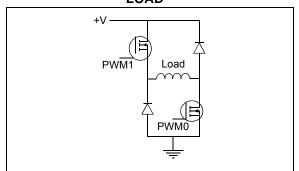

## 14.8.2 PWM CHANNEL OVERRIDE

PWM output may be manually overridden for each PWM channel by using the appropriate bits in the OVDCOND and OVDCONS registers. The user may select the following signal output options for each PWM output pin operating in the Independent PWM mode:

- I/O pin outputs PWM signal

- I/O pin inactive

- I/O pin active

Refer to **Section 14.10 "PWM Output Override"** for details for all the override functions.

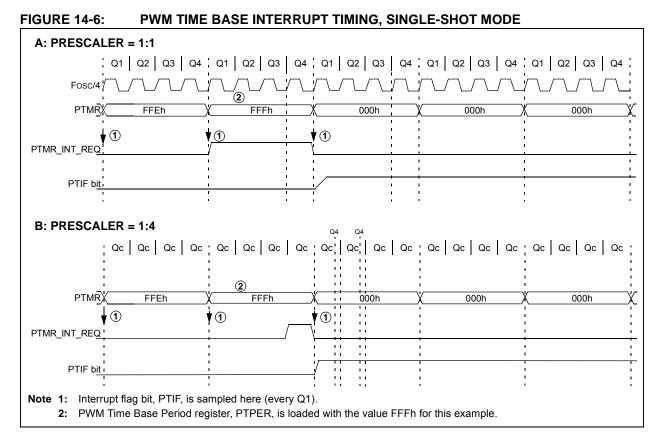

# 14.9 Single-Pulse PWM Operation

The single-pulse PWM operation is available only in Edge-Aligned mode. In this mode, the PWM module will produce single-pulse output. Single-pulse operation is configured when the PTMOD1:PTMOD0 bits are set to '01' in the PTCON0 register. This mode of operation is useful for driving certain types of ECMs.

In Single-Pulse mode, the PWM I/O pin(s) are driven to the active state when the PTEN bit is set. When the PWM timer match with Duty Cycle register occurs, the PWM I/O pin is driven to the inactive state. When the PWM timer match with the PTPER register occurs, the PTMR register is cleared, all active PWM I/O pins are driven to the inactive state, the PTEN bit is cleared and an interrupt is generated if the corresponding interrupt bit is set.

| Note: | PTPER and PDCx values are held as they     |

|-------|--------------------------------------------|

|       | are after the single-pulse output. To have |

|       | another cycle of single pulse, only PTEN   |

|       | has to be enabled.                         |

# 14.10 PWM Output Override

The PWM output override bits allow the user to manually drive the PWM I/O pins to specified logic states, independent of the duty cycle comparison units. The PWM override bits are useful when controlling various types of ECMs, like a BLDC motor.

OVDCOND and OVDCONS registers are used to define the PWM override options. The OVDCOND register contains six bits, POVD5:POVD0, that determine which PWM I/O pins will be overridden. The OVDCONS register contains six bits, POUT5:POUT0, that determine the state of the PWM I/O pins when a particular output is overridden via the POVD bits.

The POVD bits are active-low control bits. When the POVD bits are set, the corresponding POUT bit will have no effect on the PWM output. In other words, the pins corresponding to POVD bits that are set will have the duty PWM cycle set by the PDCx registers. When one of the POVD bits is cleared, the output on the corresponding PWM I/O pin will be determined by the state of the POUT bit. When a POUT bit is set, the PWM pin will be driven to its active state. When the POUT bit is cleared, the PWM pin will be driven to its inactive state.

### 14.10.1 COMPLEMENTARY OUTPUT MODE

The even numbered PWM I/O pins have override restrictions when a pair of PWM I/O pins are operating in the Complementary mode (PMODx = 0). In Complementary mode, if the even numbered pin is driven active by clearing the corresponding POVD bit and by setting the POUT bits in the OVDCOND and OVDCONS registers, the output signal is forced to be the complement of the odd numbered I/O pin in the pair (see Figure 14-2 for details).

#### 14.10.2 OVERRIDE SYNCHRONIZATION

If the OSYNC bit in the PWMCON1 register is set, all output overrides performed via the OVDCOND and OVDCONS registers will be synchronized to the PWM time base. Synchronous output overrides will occur on the following conditions:

- When the PWM is in Edge-Aligned mode, synchronization occurs when PTMR is zero.

- When the PWM is in Center-Aligned mode, synchronization occurs when PTMR is zero and when the value of PTMR matches PTPER.

- **Note 1:** In the Complementary mode, the even channel cannot be forced active by a Fault or override event when the odd channel is active. The even channel is always the complement of the odd channel, with dead-time inserted, before the odd channel can be driven to its active state as shown in Figure 14-20.

- 2: Dead time inserted in the PWM channels even when they are in Override mode.

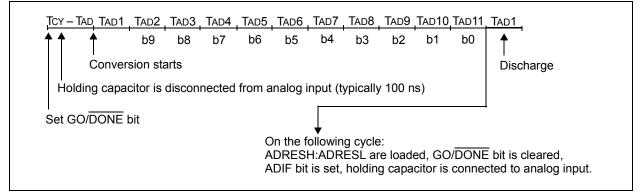

# 16.7 A/D Conversions

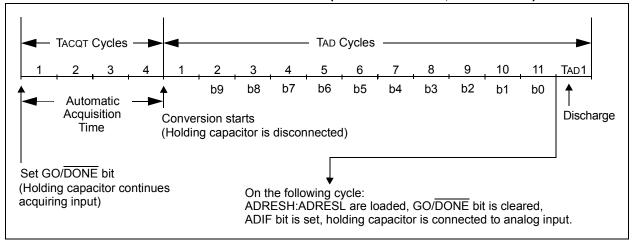

Figure 16-4 shows the operation of the A/D Converter after the GO/DONE bit has been set and the ACQT2:ACQT0 bits are cleared. A conversion is started after the following instruction to allow entry into Sleep mode before the conversion begins.

Figure 16-5 shows the operation of the A/D Converter after the GO/DONE bit has been set, the ACQT2:ACQT0 bits are set to '010' and a 4 TAD acquisition time is selected before the conversion starts.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D Result register pair will NOT be updated with the partially completed A/D conversion sample. This means that the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers). After the A/D conversion is completed or aborted, a 2 TAD wait is required before the next acquisition can be started. After this wait, acquisition on the selected channel is automatically started.

| Note: | The GO/DONE bit should NOT be set in        |

|-------|---------------------------------------------|

|       | the same instruction that turns on the A/D. |

# 16.8 Discharge

The discharge phase is used to initialize the value of the capacitor array. The array is discharged before every sample. This feature helps to optimize the unitygain amplifier, as the circuit always needs to charge the capacitor array, rather than charge/discharge based on previous measure values.

# FIGURE 16-4: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 000, TACQ = 0)

# FIGURE 16-5: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 010, TACQ = 4 TAD)

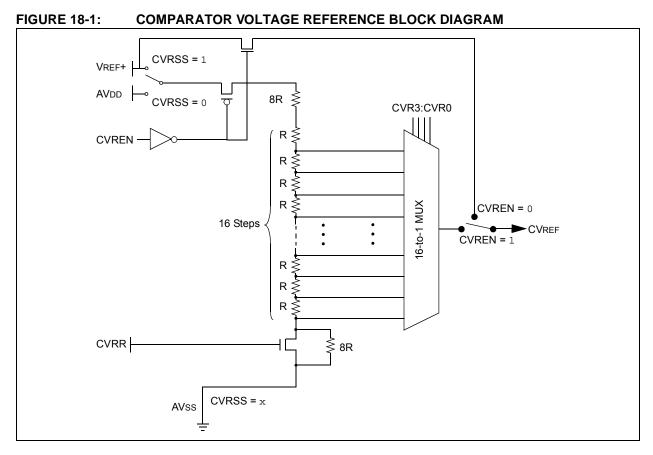

# 18.2 Voltage Reference Accuracy/Error

The full range of voltage reference cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 18-1) keep CVREF from approaching the reference source rails. The voltage reference is derived from the reference source; therefore, the CVREF output changes with fluctuations in that source. The tested absolute accuracy of the voltage reference can be found in **Section 23.0 "Electrical Characteristics"**.

# 18.3 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the CVRCON register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

# 18.4 Effects of a Reset

A device Reset disables the voltage reference by clearing bit, CVREN (CVRCON<7>). This Reset selects the highvoltage range by clearing bit, CVRR (CVRCON<5>). The CVR value select bits are also cleared.

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset<br>Values<br>on Page: |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------------|

| CVRCON | CVREN | _     | CVRR  | CVRSS | CVR3  | CVR2  | CVR1  | CVR0  | 48                          |

| CMCON  | C2OUT | C10UT | COOUT | _     | -     | CMEN2 | CMEN1 | CMEN0 | 48                          |

# TABLE 18-2: REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE

Legend: Shaded cells are not used with the comparator voltage reference.

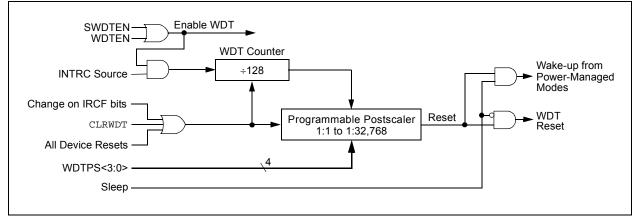

# 20.2 Watchdog Timer (WDT)

For PIC18F1230/1330 devices, the WDT is driven by the INTRC source. When the WDT is enabled, the clock source is also enabled. The nominal WDT period is 4 ms and has the same stability as the INTRC oscillator.

The 4 ms period of the WDT is multiplied by a 16-bit postscaler. Any output of the WDT postscaler is selected by a multiplexer, controlled by bits in Configuration Register 2H. Available periods range from 4 ms to 131.072 seconds (2.18 minutes). The WDT and postscaler are cleared when any of the following events occur: a SLEEP or CLRWDT instruction is executed, the IRCF bits (OSCCON<6:4>) are changed or a clock failure has occurred.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and postscaler counts when executed.

- 2: Changing the setting of the IRCF bits (OSCCON<6:4>) clears the WDT and postscaler counts.

- **3:** When a CLRWDT instruction is executed, the postscaler count will be cleared.

#### 20.2.1 CONTROL REGISTER

Register 20-15 shows the WDTCON register. This is a readable and writable register which contains a control bit that allows software to override the WDT enable Configuration bit, but only if the Configuration bit has disabled the WDT.

#### FIGURE 20-1: WDT BLOCK DIAGRAM

## REGISTER 20-15: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| U-0                                                                  | U-0 | U-0              | U-0 | U-0                                     | U-0 | U-0 | R/W-0                 |  |

|----------------------------------------------------------------------|-----|------------------|-----|-----------------------------------------|-----|-----|-----------------------|--|

| —                                                                    | _   | —                | _   | —                                       | —   | —   | SWDTEN <sup>(1)</sup> |  |

| bit 7                                                                |     |                  |     |                                         |     |     | bit 0                 |  |

|                                                                      |     |                  |     |                                         |     |     |                       |  |

| Legend:                                                              |     |                  |     |                                         |     |     |                       |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |                  |     |                                         |     |     |                       |  |

| -n = Value at P                                                      | OR  | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |     |     | known                 |  |

| bit 7-1 | Unimplemented: Read as '0'                                           |

|---------|----------------------------------------------------------------------|

| bit 0   | SWDTEN: Software Controlled Watchdog Timer Enable bit <sup>(1)</sup> |

|         | 1 = Watchdog Timer is on                                             |

|         | 0 = Watchdog Timer is off                                            |

Note 1: This bit has no effect if the Configuration bit, WDTEN, is enabled.

## TABLE 20-2: SUMMARY OF WATCHDOG TIMER REGISTERS

| Name   | Bit 7 | Bit 6                 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0                 | Reset<br>Values<br>on Page: |

|--------|-------|-----------------------|-------|-------|-------|-------|-------|-----------------------|-----------------------------|

| RCON   | IPEN  | SBOREN <sup>(1)</sup> | _     | RI    | TO    | PD    | POR   | BOR                   | 48                          |

| WDTCON | _     |                       |       |       | _     | _     | _     | SWDTEN <sup>(2)</sup> | 48                          |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Watchdog Timer.

Note 1: The SBOREN bit is only available when the BOREN1:BOREN0 Configuration bits = 01; otherwise, it is disabled and reads as '0'. See Section 5.4 "Brown-out Reset (BOR)".

2: This bit has no effect if the Configuration bit, WDTEN, is enabled.

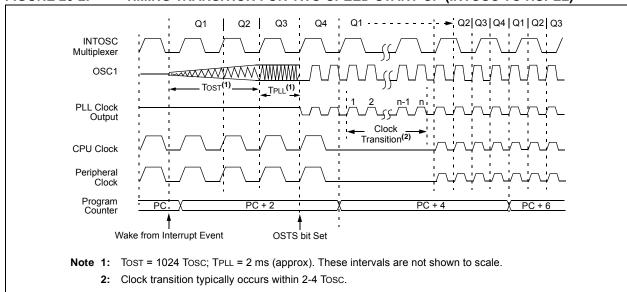

# 20.3 Two-Speed Start-up

The Two-Speed Start-up feature helps to minimize the latency period from oscillator start-up to code execution by allowing the microcontroller to use the INTOSC oscillator as a clock source until the primary clock source is available. It is enabled by setting the IESO Configuration bit.

Two-Speed Start-up should be enabled only if the primary oscillator mode is LP, XT, HS or HSPLL (crystal-based modes). Other sources do not require an OST start-up delay; for these, Two-Speed Start-up should be disabled.

When enabled, Resets and wake-ups from Sleep mode cause the device to configure itself to run from the internal oscillator block as the clock source, following the time-out of the Power-up Timer, after a Power-on Reset is enabled. This allows almost immediate code execution while the primary oscillator starts and the OST is running. Once the OST times out, the device automatically switches to PRI\_RUN mode.

To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits, IRCF2:IRCF0, immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting the IRCF2:IRCF0 bits prior to entering Sleep mode.

In all other power-managed modes, Two-Speed Start-up is not used. The device will be clocked by the currently selected clock source until the primary clock source becomes available. The setting of the IESO bit is ignored.

#### 20.3.1 SPECIAL CONSIDERATIONS FOR USING TWO-SPEED START-UP

While using the INTOSC oscillator in Two-Speed Start-up, the device still obeys the normal command sequences for entering power-managed modes, including multiple SLEEP instructions (refer to **Section 4.1.4 "Multiple Sleep Commands"**). In practice, this means that user code can change the SCS1:SCS0 bit settings or issue SLEEP instructions before the OST times out. This would allow an application to briefly wake-up, perform routine "housekeeping" tasks and return to Sleep before the device starts to operate from the primary oscillator.

User code can also check if the primary clock source is currently providing the device clocking by checking the status of the OSTS bit (OSCCON<3>). If the bit is set, the primary oscillator is providing the clock. Otherwise, the internal oscillator block is providing the clock during wake-up from Reset or Sleep mode.

# FIGURE 20-2: TIMING TRANSITION FOR TWO-SPEED START-UP (INTOSC TO HSPLL)

# 21.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C18 and MPLAB C30 C Compilers

- MPLINK™ Object Linker/

- MPLIB™ Object Librarian

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PICSTART<sup>®</sup> Plus Development Programmer

- MPLAB PM3 Device Programmer

- PICkit<sup>™</sup> 2 Development Programmer

- Low-Cost Demonstration and Development Boards and Evaluation Kits

# 21.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- · High-level source code debugging

- Visual device initializer for easy register initialization

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as HI-TECH Software C Compilers and IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- · Debug using:

- Source files (assembly or C)

- Mixed assembly and C

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

# 22.0 INSTRUCTION SET SUMMARY

PIC18F1230/1330 devices incorporate the standard set of 75 PIC18 core instructions, as well as an extended set of 8 new instructions for the optimization of code that is recursive or that utilizes a software stack. The extended set is discussed later in this section.

# 22.1 Standard Instruction Set

The standard PIC18 instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from these PIC MCU instruction sets. Most instructions are a single program memory word (16 bits), but there are four instructions that require two program memory locations.

Each single-word instruction is a 16-bit word divided into an opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into four basic categories:

- · Byte-oriented operations

- **Bit-oriented** operations

- · Literal operations

- · Control operations

The PIC18 instruction set summary in Table 22-2 lists **byte-oriented**, **bit-oriented**, **literal** and **control** operations. Table 22-1 shows the opcode field descriptions.

Most byte-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The destination of the result (specified by 'd')

- 3. The accessed memory (specified by 'a')

The file register designator 'f' specifies which file register is to be used by the instruction. The destination designator 'd' specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the WREG register. If 'd' is one, the result is placed in the file register specified in the instruction.

All bit-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The bit in the file register (specified by 'b')

- 3. The accessed memory (specified by 'a')

The bit field designator 'b' selects the number of the bit affected by the operation, while the file register designator 'f' represents the number of the file in which the bit is located. The **literal** instructions may use some of the following operands:

- A literal value to be loaded into a file register (specified by 'k')

- The desired FSR register to load the literal value into (specified by 'f')

- No operand required (specified by '—')

The **control** instructions may use some of the following operands:

- A program memory address (specified by 'n')

- The mode of the CALL or RETURN instructions (specified by 's')

- The mode of the table read and table write instructions (specified by 'm')

- No operand required (specified by '—')

All instructions are a single word, except for four double-word instructions. These instructions were made double-word to contain the required information in 32 bits. In the second word, the 4 MSbs are '1's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

All single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles, with the additional instruction cycle(s) executed as a NOP.

The double-word instructions execute in two instruction cycles.

One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Two-word branch instructions (if true) would take 3  $\mu$ s.

Figure 22-1 shows the general formats that the instructions can have. All examples use the convention 'nnh' to represent a hexadecimal number.

The Instruction Set Summary, shown in Table 22-2, lists the standard instructions recognized by the Microchip MPASM<sup>™</sup> Assembler.

Section 22.1.1 "Standard Instruction Set" provides a description of each instruction.

# PIC18F1230/1330

| ADDWFC      | )                        | ADD W a                   | ANDL                                      |                         |        |

|-------------|--------------------------|---------------------------|-------------------------------------------|-------------------------|--------|

| Syntax:     |                          | ADDWFC                    | f {,d {,a}}                               |                         | Syntax |

| Operands:   |                          | $0 \leq f \leq 255$       |                                           |                         | Opera  |

|             |                          | d ∈ [0,1]<br>a ∈ [0,1]    |                                           |                         | Opera  |

| Operation:  |                          | a ∈ [0,1]<br>(W) + (f) +  |                                           |                         | Status |

| Status Affe |                          | (W) + (I) +<br>N,OV, C, D | . ,                                       |                         | Encod  |

| Encoding:   | cieu.                    | 0010                      | 00da ff:                                  | ff ffff                 | Descri |

| Description | <b>.</b> .               |                           | Carry flag and                            |                         | ]      |

| Description | 11.                      |                           | If 'd' is '0', the                        |                         | words  |

|             |                          | •                         | /. If 'd' is '1', th                      |                         | Cycles |

|             |                          |                           | ata memory lo<br>he Access Ba             |                         | Q Cyc  |

|             |                          |                           | he BSR is use                             |                         |        |

|             |                          | GPR bank.                 | nd the extend                             | ad instruction          |        |

|             |                          |                           | led, this instru                          |                         | . L    |

|             |                          |                           | Literal Offset /                          | 0                       | Examp  |

|             |                          |                           | never f ≤ 95 (5<br>2. <b>2.3 "Byte-Or</b> | ,                       | В      |

|             |                          |                           | ed Instruction                            |                         |        |

|             |                          | Literal Offs              | set Mode" for                             | details.                | A      |

| Words:      |                          | 1                         |                                           |                         |        |

| Cycles:     |                          | 1                         |                                           |                         |        |

| Q Cycle A   | -                        |                           |                                           |                         |        |

|             | Q1                       | Q2                        | Q3                                        | Q4                      | 7      |

| De          | ecode                    | Read<br>register 'f'      | Process<br>Data                           | Write to<br>destination |        |

|             |                          | regiotor r                | Data                                      | dootination             | 1      |

| Example:    |                          | ADDWFC                    | REG, 0,                                   | 1                       |        |

| Befor       | e Instruc                | tion                      |                                           |                         |        |

|             | Carry bit<br>REG         | = 1<br>= 02h              |                                           |                         |        |

|             | W                        | = 4Dh                     |                                           |                         |        |

|             | Instruction<br>Carry bit |                           |                                           |                         |        |

|             | REŚ                      | = 02h                     |                                           |                         |        |

|             | W                        | = 50h                     |                                           |                         |        |

| AND                            | DLW            | AND Lite                   | AND Literal with W |     |    |           |  |  |  |

|--------------------------------|----------------|----------------------------|--------------------|-----|----|-----------|--|--|--|

| Synta                          | ax:            | ANDLW                      | k                  |     |    |           |  |  |  |

| Oper                           | ands:          | $0 \le k \le 25$           | 5                  |     |    |           |  |  |  |

| Oper                           | ation:         | (W) .AND.                  | $k\toW$            |     |    |           |  |  |  |

| Statu                          | is Affected:   | N, Z                       |                    |     |    |           |  |  |  |

| Enco                           | oding:         | 0000                       | 1011               | kkk | k  | kkkk      |  |  |  |

| Desc                           | cription:      | The conte<br>8-bit literal |                    |     |    |           |  |  |  |

| Word                           | ls:            | 1                          |                    |     |    |           |  |  |  |

| Cycle                          | es:            | 1                          |                    |     |    |           |  |  |  |

| QC                             | ycle Activity: |                            |                    |     |    |           |  |  |  |

|                                | Q1             | Q2                         | Q3                 | 3   |    | Q4        |  |  |  |

|                                | Decode         | Read literal<br>'k'        | Proce<br>Dat       |     | Wi | rite to W |  |  |  |

| Example:<br>Before Instruction |                | ANDLW                      | 05Fh               |     |    |           |  |  |  |

|                                | W              | = A3h                      |                    |     |    |           |  |  |  |

| After Instruction              |                |                            |                    |     |    |           |  |  |  |

|                                |                |                            |                    |     |    |           |  |  |  |

# PIC18F1230/1330

| ANDWF                                                           | AND W with f                                                                                                                                                                      |                                                                           | BC                                                                                                                                                                       |                                | Branch if                                                          | Branch if Carry                                                                    |                                                                                                          |                                                        |  |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--|

| Syntax:                                                         | ANDWF                                                                                                                                                                             | f {,d {,a}}                                                               |                                                                                                                                                                          | Synta                          | IX:                                                                | BC n                                                                               | BC n                                                                                                     |                                                        |  |

| Operands:                                                       | $0 \leq f \leq 255$                                                                                                                                                               |                                                                           |                                                                                                                                                                          | Opera                          | ands:                                                              | -128 ≤ n ≤ ′                                                                       | $-128 \le n \le 127$                                                                                     |                                                        |  |

|                                                                 | $\begin{array}{l} d \in [0,1] \\ a \in [0,1] \end{array}$                                                                                                                         |                                                                           |                                                                                                                                                                          | Opera                          | ation:                                                             |                                                                                    | if Carry bit is '1',<br>(PC) + 2 + 2n $\rightarrow$ PC                                                   |                                                        |  |

| Operation:                                                      | (W) .AND.                                                                                                                                                                         | (f) $\rightarrow$ dest                                                    |                                                                                                                                                                          | Statu                          | s Affected:                                                        | None                                                                               |                                                                                                          |                                                        |  |

| Status Affected:                                                | N, Z                                                                                                                                                                              |                                                                           |                                                                                                                                                                          | Enco                           | dina:                                                              | 1110                                                                               | 0010 nnr                                                                                                 | nn nnnn                                                |  |

| Encoding:                                                       | 0001                                                                                                                                                                              | 01da ff                                                                   | ff ffff                                                                                                                                                                  |                                | ription:                                                           | If the Carry                                                                       | bit is '1', then                                                                                         | the program                                            |  |

| Description:                                                    | register 'f'.<br>in W. If 'd' is<br>in register '<br>If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank.<br>If 'a' is '0' a<br>set is enab<br>in Indexed<br>mode wher<br>Section 22 | s '1', the result<br>f'<br>he Access Ba<br>he BSR is use<br>nd the extend | result is stored<br>is stored back<br>is stored back<br>ink is selected.<br>id to select the<br>ed instruction<br>ction operates<br>Addressing<br>Fh). See<br>iented and | Word<br>Cycle<br>Q Cy<br>If Ju | s:<br>/cle Activity:<br>mp:                                        | added to thuincremente<br>instruction,<br>PC + 2 + 2r<br>two-cycle ir<br>1<br>1(2) | nplement numl<br>e PC. Since the<br>d to fetch the r<br>the new addre<br>n. This instruct<br>istruction. | e PC will have<br>hext<br>iss will be<br>ion is then a |  |

|                                                                 |                                                                                                                                                                                   | set Mode" for                                                             |                                                                                                                                                                          | 1                              | Q1                                                                 | Q2                                                                                 | Q3                                                                                                       | Q4                                                     |  |

| Words:                                                          | 1                                                                                                                                                                                 |                                                                           |                                                                                                                                                                          |                                | Decode                                                             | Read literal<br>'n'                                                                | Process<br>Data                                                                                          | Write to<br>PC                                         |  |

| Cycles:                                                         | 1                                                                                                                                                                                 |                                                                           |                                                                                                                                                                          |                                | No                                                                 | No                                                                                 | No                                                                                                       | No                                                     |  |

| Q Cycle Activity:                                               |                                                                                                                                                                                   |                                                                           |                                                                                                                                                                          |                                | operation                                                          | operation                                                                          | operation                                                                                                | operation                                              |  |

| Q1                                                              | Q2                                                                                                                                                                                | Q3                                                                        | Q4                                                                                                                                                                       | lf No                          | Jump:                                                              |                                                                                    |                                                                                                          |                                                        |  |

| Decode                                                          | Read                                                                                                                                                                              | Process                                                                   | Write to                                                                                                                                                                 | ſ                              | Q1                                                                 | Q2                                                                                 | Q3                                                                                                       | Q4                                                     |  |

|                                                                 | register 'f'                                                                                                                                                                      | Data                                                                      | destination                                                                                                                                                              |                                | Decode                                                             | Read literal<br>'n'                                                                | Process<br>Data                                                                                          | No<br>operation                                        |  |

| Example:<br>Before Instruc<br>W<br>REG<br>After Instructio<br>W | = 17h<br>= C2h                                                                                                                                                                    | REG, 0, 0                                                                 |                                                                                                                                                                          |                                | iple:<br>Before Instruc<br>PC<br>After Instructi<br>If Carry<br>PC | = ad<br>on<br>= 1;                                                                 | BC 5<br>dress (HERE)<br>dress (HERE                                                                      |                                                        |  |

| w<br>REG                                                        | = 02h<br>= C2h                                                                                                                                                                    |                                                                           |                                                                                                                                                                          |                                | If Carry<br>PC                                                     | = 0;                                                                               | dress (HERE                                                                                              |                                                        |  |

| CPFSGT                            | Compare                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | f with W, Sk        | ip if f > W |  |  |  |  |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------|--|--|--|--|

| Syntax:                           | CPFSGT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | f {,a}              |             |  |  |  |  |

| Operands:                         | $0 \le f \le 255$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                     |             |  |  |  |  |

|                                   | a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     |             |  |  |  |  |

| Operation:                        | (f) – (W),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                     |             |  |  |  |  |

|                                   | skip if $(f) > (f)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . ,                 |             |  |  |  |  |

|                                   | (unsigned c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | comparison)         |             |  |  |  |  |

| Status Affected:                  | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                     |             |  |  |  |  |

| Encoding:                         | 0110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 010a fff            | f ffff      |  |  |  |  |

| Description:                      | Compares the contents of data memory<br>location 'f' to the contents of data memory<br>location 'f' to the contents of the W by<br>performing an unsigned subtraction.<br>If the contents of 'f' are greater than the<br>contents of WREG, then the fetched<br>instruction is discarded and a NOP is<br>executed instead, making this a<br>two-cycle instruction.<br>If 'a' is '0', the Access Bank is selected<br>If 'a' is '0', the ASR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operate<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 22.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                     |             |  |  |  |  |

| Wordo:                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | set mode tor        | uctans.     |  |  |  |  |

| Words:                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                     |             |  |  |  |  |

| Cycles:                           | 1(2)<br>Note: 3 cv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | cles if skip and    | 1 followed  |  |  |  |  |

|                                   | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-word instru       |             |  |  |  |  |

| Q Cycle Activity:                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                     |             |  |  |  |  |

| Q1                                | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Q3                  | Q4          |  |  |  |  |

| Decode                            | Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Process             | No          |  |  |  |  |

|                                   | register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Data                | operation   |  |  |  |  |

| lf skip:                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                     |             |  |  |  |  |

| Q1                                | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Q3                  | Q4          |  |  |  |  |

| No                                | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | No                  | No          |  |  |  |  |

| operation<br>If skip and followed | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | operation           | operation   |  |  |  |  |

| Q1                                | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Q3                  | Q4          |  |  |  |  |

| No                                | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | No                  | No          |  |  |  |  |

| operation                         | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | operation           | operation   |  |  |  |  |

| No                                | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | No                  | No          |  |  |  |  |

| operation                         | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | operation           | operation   |  |  |  |  |

| Example:                          | HERE<br>NGREATER<br>GREATER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CPFSGT RE<br>:<br>: | G, 0        |  |  |  |  |