Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 4x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f1330t-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Register | Applicable<br>Devices |      | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |

|----------|-----------------------|------|------------------------------------|------------------------------------------------------------------|---------------------------------|

| SEVTCMPH | 1230                  | 1330 | 0000                               | 0000                                                             | uuuu                            |

| PWMCON0  | 1230                  | 1330 | -100 -000 <b>(6)</b>               | -100 -000 <b>(6)</b>                                             | -uuu -uuu <b>(6)</b>            |

|          |                       |      | -000 -000 <b>(6)</b>               | -000 -000 <b>(6)</b>                                             | -uuu -uuu <b>(6)</b>            |

| PWMCON1  | 1230                  | 1330 | 0000 0-00                          | 0000 0-00                                                        | uuuu u-uu                       |

| DTCON    | 1230                  | 1330 | 0000 0000                          | 0000 0000                                                        | սսսս սսսս                       |

| OVDCOND  | 1230                  | 1330 | 11 1111                            | 11 1111                                                          | uu uuuu                         |

| OVDCONS  | 1230                  | 1330 | 00 0000                            | 00 0000                                                          | uu uuuu                         |

| PORTB    | 1230                  | 1330 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |

| PORTA    | 1230                  | 1330 | xx0x xxxx <sup>(5)</sup>           | uu0u uuuu <sup>(5)</sup>                                         | uuuu uuuu <sup>(5)</sup>        |

## TABLE 5-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

**2:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 5-3 for Reset value for specific condition.

**5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read as '0'.

6: Reset condition of PWMEN bits depends on the PWMPIN Configuration bit of CONFIG3L.

### 6.1.1 PROGRAM COUNTER

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21 bits wide and is contained in three separate 8-bit registers. The low byte, known as the PCL register, is both readable and writable. The high byte, or PCH register, contains the PC<15:8> bits; it is not directly readable or writable. Updates to the PCH register are performed through the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCH register. Updates to the PCU register are performed through the PCLATH register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCU register are performed through the PCLATU register.

The contents of PCLATH and PCLATU are transferred to the program counter by any operation that writes to the PCL. Similarly, the upper two bytes of the program counter are transferred to PCLATH and PCLATU by an operation that reads the PCL. This is useful for computed offsets to the PC (see **Section 6.1.4.1 "Computed GOTO"**).

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the Least Significant bit of PCL is fixed to a value of '0'. The PC increments by 2 to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

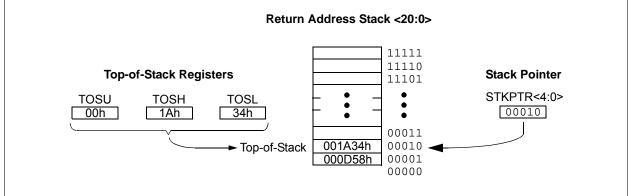

### 6.1.2 RETURN ADDRESS STACK

The return address stack allows any combination of up to 31 program calls and interrupts to occur. The PC is pushed onto the stack when a CALL or RCALL instruction is executed or an interrupt is Acknowledged. The PC value is pulled off the stack on a RETURN, RETLW or a RETFIE instruction. PCLATU and PCLATH are not affected by any of the RETURN or CALL instructions.

The stack operates as a 31-word by 21-bit RAM and a 5-bit Stack Pointer, STKPTR. The stack space is not part of either program or data space. The Stack Pointer is readable and writable and the address on the top of the stack is readable and writable through the Top-of-Stack Special Function Registers. Data can also be pushed to, or popped from the stack, using these registers.

A CALL type instruction causes a push onto the stack; the Stack Pointer is first incremented and the location pointed to by the Stack Pointer is written with the contents of the PC (already pointing to the instruction following the CALL). A RETURN type instruction causes a pop from the stack; the contents of the location pointed to by the STKPTR are transferred to the PC and then the Stack Pointer is decremented.

The Stack Pointer is initialized to '00000' after all Resets. There is no RAM associated with the location corresponding to a Stack Pointer value of '00000'; this is only a Reset value. Status bits indicate if the stack is full, has overflowed or has underflowed.

### 6.1.2.1 Top-of-Stack Access

Only the top of the return address stack (TOS) is readable and writable. A set of three registers, TOSU:TOSH:TOSL, hold the contents of the stack location pointed to by the STKPTR register (Figure 6-2). This allows users to implement a software stack if necessary. After a CALL, RCALL or interrupt, the software can read the pushed value by reading the TOSU:TOSH:TOSL registers. These values can be placed on a user-defined software stack. At return time, the software can return these values to TOSU:TOSH:TOSL and do a return.

The user must disable the global interrupt enable bits while accessing the stack to prevent inadvertent stack corruption.

# 7.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable during normal operation over the entire VDD range.

A read from program memory is executed on one byte at a time. A write to program memory is executed on blocks of 8 bytes at a time. Program memory is erased in blocks of 64 bytes at a time. A bulk erase operation may not be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

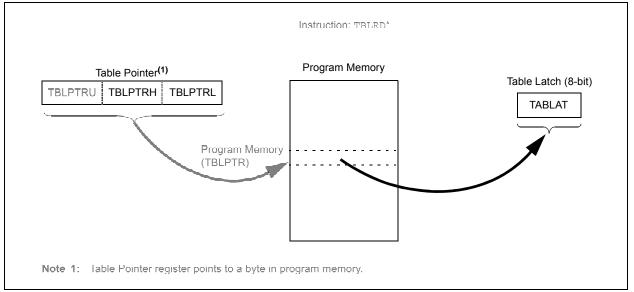

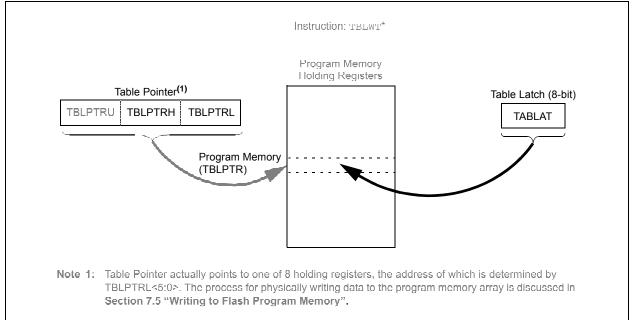

### 7.1 Table Reads and Table Writes

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

Table read operations retrieve data from program memory and place it into the data RAM space. Figure 7-1 shows the operation of a table read with program memory and data RAM.

Table write operations store data from the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in **Section 7.5** "**Writing to Flash Program Memory**". Figure 7-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word-aligned. Therefore, a table block can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word-aligned.

FIGURE 7-1: TABLE READ OPERATION

## FIGURE 7-2: TABLE WRITE OPERATION

## 7.2 Control Registers

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. These include the:

- EECON1 register

- EECON2 register

- TABLAT register

- TBLPTR registers

### 7.2.1 EECON1 AND EECON2 REGISTERS

The EECON1 register (Register 7-1) is the control register for memory accesses. The EECON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

The EEPGD control bit determines if the access will be a program or data EEPROM memory access. When clear, any subsequent operations will operate on the data EEPROM memory. When set, any subsequent operations will operate on the program memory.

The CFGS control bit determines if the access will be to the Configuration/Calibration registers or to program memory/data EEPROM memory. When set, subsequent operations will operate on Configuration registers regardless of EEPGD (see **Section 20.0 "Special Features of the CPU"**). When clear, memory selection access is determined by EEPGD. The FREE bit, when set, will allow a program memory erase operation. When FREE is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WR bit is set and cleared when the internal programming timer expires and the write operation is complete.

| Note: | During normal operation, the WRERR         |

|-------|--------------------------------------------|

|       | may read as '1'. This can indicate that a  |

|       | write operation was prematurely termi-     |

|       | nated by a Reset, or a write operation was |

|       | attempted improperly.                      |

The WR control bit initiates write operations. The bit cannot be cleared, only set, in software; it is cleared in hardware at the completion of the write operation.

**Note:** The EEIF interrupt flag bit (PIR2<4>) is set when the write is complete. It must be cleared in software.

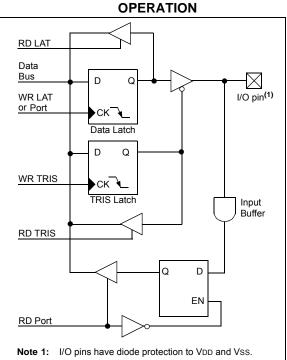

# 10.0 I/O PORTS

Depending on the device selected and features enabled, there are up to five ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three registers for its operation. These registers are:

- TRIS register (Data Direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (Output Latch register)

The Output Latch (LAT register) is useful for readmodify-write operations on the value that the I/O pins are driving.

A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 10-1.

## 10.1 PORTA, TRISA and LATA Registers

PORTA is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it, will write to the port latch.

The Output Latch (LATA) register is also memory mapped. Read-modify-write operations on the LATA register read and write the latched output value for PORTA.

Pins RA6 and RA7 are multiplexed with the main oscillator pins; they are enabled as oscillator or I/O pins by the selection of the main oscillator in the Configuration register (see **Section 20.1 "Configuration Bits"** for details). When they are not used as port pins, RA6 and RA7 and their associated TRIS and LAT bits are read as '0'.

The RA0 pin is multiplexed with one of the analog inputs, one of the external interrupt inputs, one of the interrupt-on-change inputs and one of the analog comparator inputs to become RA0/AN0/INT0/KBI0/CMP0 pin.

The RA1 pin is multiplexed with one of the analog inputs, one of the external interrupt inputs and one of the interrupt-on-change inputs to become RA1/AN1/ INT1/KBI1 pin.

Pins RA2 and RA3 are multiplexed with the Enhanced USART transmission and reception input (see **Section 20.1 "Configuration Bits"** for details).

The RA4 pin is multiplexed with the Timer0 module clock input, one of the analog inputs and the analog VREF+ input to become the RA4/T0CKI/AN2/VREF+ pin.

The Fault detect input for PWM FLTA is multiplexed with pins RA5 and RA7. Its placement is decided by clearing or setting the FLTAMX bit of Configuration Register 3H.

Note: On a Power-on Reset, RA0, RA1, RA4 and RA5 are configured as analog inputs and read as '0'. RA2 and RA3 are configured as digital inputs.

The TRISA register controls the direction of the PORTA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

### EXAMPLE 10-1: INITIALIZING PORTA

| CLRF  | PORTA  | ; Initialize PORTA by<br>; clearing output |

|-------|--------|--------------------------------------------|

|       |        |                                            |

|       |        | ; data latches                             |

| CLRF  | LATA   | ; Alternate method                         |

|       |        | ; to clear output                          |

|       |        | ; data latches                             |

| MOVLW | 07h    | ; Configure A/D                            |

| MOVWF | ADCON1 | ; for digital inputs                       |

| MOVWF | 07h    | ; Configure comparators                    |

| MOVWF | CMCON  | ; for digital input                        |

| MOVLW | OCFh   | ; Value used to                            |

|       |        | ; initialize data                          |

|       |        | ; direction                                |

| MOVWF | TRISA  | ; Set RA<7:6,3:0> as inputs                |

|       |        | ; RA<5:4> as outputs                       |

|       |        |                                            |

### 11.5 RCON Register

Γ.

The RCON register contains flag bits which are used to determine the cause of the last Reset or wake-up from Idle or Sleep modes. RCON also contains the IPEN bit which enables interrupt priorities.

The operation of the SBOREN bit and the Reset flag bits is discussed in more detail in **Section 5.1 "RCON Register"**.

### REGISTER 11-13: RCON: RESET CONTROL REGISTER

| R/W-0 | R/W-1 <sup>(1)</sup> | U-0 | R/W-1 | R-1 | R-1 | R/W-0 <sup>(2)</sup> | R/W-0 |

|-------|----------------------|-----|-------|-----|-----|----------------------|-------|

| IPEN  | SBOREN               | _   | RI    | TO  | PD  | POR                  | BOR   |

| bit 7 |                      |     |       |     |     |                      | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | <b>IPEN:</b> Interrupt Priority Enable bit<br>1 = Enable priority levels on interrupts<br>0 = Disable priority levels on interrupts (PIC16CXXX Compatibility mode) |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | <b>SBOREN:</b> BOR Software Enable bit <sup>(1)</sup>                                                                                                              |

|       | For details of bit operation, see Register 5-1.                                                                                                                    |

| bit 5 | Unimplemented: Read as '0'                                                                                                                                         |

| bit 4 | RI: RESET Instruction Flag bit                                                                                                                                     |

|       | For details of bit operation, see Register 5-1.                                                                                                                    |

| bit 3 | TO: Watchdog Time-out Flag bit                                                                                                                                     |

|       | For details of bit operation, see Register 5-1.                                                                                                                    |

| bit 2 | PD: Power-Down Detection Flag bit                                                                                                                                  |

|       | For details of bit operation, see Register 5-1.                                                                                                                    |

| bit 1 | <b>POR:</b> Power-on Reset Status bit <sup>(2)</sup>                                                                                                               |

|       | For details of bit operation, see Register 5-1.                                                                                                                    |

| bit 0 | BOR: Brown-out Reset Status bit                                                                                                                                    |

|       | For details of bit operation, see Register 5-1.                                                                                                                    |

|       |                                                                                                                                                                    |

- Note 1: If SBOREN is enabled, its Reset state is '1'; otherwise, it is '0'. See Register 5-1 for additional information.

- 2: The actual Reset value of POR is determined by the type of device Reset. See Register 5-1 for additional information.

|              |                       | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |                       |            |                             |  |  |

|--------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|

| BAUD<br>RATE | Fosc = 40.000 MHz     |                               |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |  |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |

| 0.3          | _                     | _                             | _                           | _                     |            | _                           | _                     | _          | _                           | _                     | _          | _                           |  |  |

| 1.2          | —                     | —                             | —                           | 1.221                 | 1.73       | 255                         | 1.202                 | 0.16       | 129                         | 1.201                 | -0.16      | 103                         |  |  |

| 2.4          | 2.441                 | 1.73                          | 255                         | 2.404                 | 0.16       | 129                         | 2.404                 | 0.16       | 64                          | 2.403                 | -0.16      | 51                          |  |  |

| 9.6          | 9.615                 | 0.16                          | 64                          | 9.766                 | 1.73       | 31                          | 9.766                 | 1.73       | 15                          | 9.615                 | -0.16      | 12                          |  |  |

| 19.2         | 19.531                | 1.73                          | 31                          | 19.531                | 1.73       | 15                          | 19.531                | 1.73       | 7                           | _                     | _          | _                           |  |  |

| 57.6         | 56.818                | -1.36                         | 10                          | 62.500                | 8.51       | 4                           | 52.083                | -9.58      | 2                           | —                     | _          | _                           |  |  |

| 115.2        | 125.000               | 8.51                          | 4                           | 104.167               | -9.58      | 2                           | 78.125                | -32.18     | 1                           | —                     | _          | _                           |  |  |

|              |                       | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                       |            |                             |                       |                  |                             |  |  |  |  |  |  |

|--------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------------|-----------------------------|--|--|--|--|--|--|

| BAUD<br>RATE | Fos                   | c = 4.000                     | MHz                         | Fos                   | c = 2.000  | MHz                         | Fos                   | Fosc = 1.000 MHz |                             |  |  |  |  |  |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) |  |  |  |  |  |  |

| 0.3          | 0.300                 | 0.16                          | 207                         | 0.300                 | -0.16      | 103                         | 0.300                 | -0.16            | 51                          |  |  |  |  |  |  |

| 1.2          | 1.202                 | 0.16                          | 51                          | 1.201                 | -0.16      | 25                          | 1.201                 | -0.16            | 12                          |  |  |  |  |  |  |

| 2.4          | 2.404                 | 0.16                          | 25                          | 2.403                 | -0.16      | 12                          | —                     | _                | _                           |  |  |  |  |  |  |

| 9.6          | 8.929                 | -6.99                         | 6                           | _                     | _          | _                           | —                     | _                | _                           |  |  |  |  |  |  |

| 19.2         | 20.833                | 8.51                          | 2                           | —                     | _          | _                           | —                     | _                | _                           |  |  |  |  |  |  |

| 57.6         | 62.500                | 8.51                          | 0                           | —                     | _          | _                           | —                     | _                | _                           |  |  |  |  |  |  |

| 115.2        | 62.500                | -45.75                        | 0                           | _                     |            | _                           | _                     | —                |                             |  |  |  |  |  |  |

|                     |                       | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |                       |            |                             |  |  |  |

|---------------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|

| BAUD<br>RATE<br>(K) | Fosc = 40.000 MHz     |                               |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |  |  |  |

|                     | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |

| 0.3                 |                       |                               |                             | _                     | _          |                             | _                     |            |                             | _                     | _          | _                           |  |  |  |

| 1.2                 | —                     | _                             | _                           | —                     | _          | _                           | —                     | _          | _                           | —                     | _          | —                           |  |  |  |

| 2.4                 | —                     | _                             | _                           | —                     | _          | _                           | 2.441                 | 1.73       | 255                         | 2.403                 | -0.16      | 207                         |  |  |  |

| 9.6                 | 9.766                 | 1.73                          | 255                         | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16       | 64                          | 9.615                 | -0.16      | 51                          |  |  |  |

| 19.2                | 19.231                | 0.16                          | 129                         | 19.231                | 0.16       | 64                          | 19.531                | 1.73       | 31                          | 19.230                | -0.16      | 25                          |  |  |  |

| 57.6                | 58.140                | 0.94                          | 42                          | 56.818                | -1.36      | 21                          | 56.818                | -1.36      | 10                          | 55.555                | 3.55       | 8                           |  |  |  |

| 115.2               | 113.636               | -1.36                         | 21                          | 113.636               | -1.36      | 10                          | 125.000               | 8.51       | 4                           | —                     | _          | _                           |  |  |  |

|       |                       | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |  |  |  |  |  |

|-------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|--|--|

| BAUD  | Foso                  | c = 4.000                     | MHz                         | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |  |  |  |  |  |

| (K)   | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |  |  |

| 0.3   | _                     |                               | _                           |                       | _          | _                           | 0.300                 | -0.16      | 207                         |  |  |  |  |  |

| 1.2   | 1.202                 | 0.16                          | 207                         | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16      | 51                          |  |  |  |  |  |

| 2.4   | 2.404                 | 0.16                          | 103                         | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16      | 25                          |  |  |  |  |  |

| 9.6   | 9.615                 | 0.16                          | 25                          | 9.615                 | -0.16      | 12                          | _                     | _          | —                           |  |  |  |  |  |

| 19.2  | 19.231                | 0.16                          | 12                          | _                     | _          | _                           | _                     | _          | —                           |  |  |  |  |  |

| 57.6  | 62.500                | 8.51                          | 3                           | —                     | _          | —                           | —                     | _          | —                           |  |  |  |  |  |

| 115.2 | 125.000               | 8.51                          | 1                           | —                     | _          | —                           | —                     | _          | —                           |  |  |  |  |  |

© 2009 Microchip Technology Inc.

## 16.1 Triggering A/D Conversions

The A/D conversion can be triggered by setting the GO/ DONE bit. This bit can either be set manually by the programmer or by setting the SEVTEN bit of ADCON0. When the SEVTEN bit is set, the Special Event Trigger from the Power Control PWM module triggers the A/D conversion. For more information, see **Section 14.14 "PWM Special Event Trigger"**.

## 16.2 A/D Acquisition Requirements

For the A/D Converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 16-3. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 2.5 k $\Omega$ . After the analog input channel is

selected (changed), the channel must be sampled for at least the minimum acquisition time before starting a conversion.

| Note: | When    | the    | conversion      | is  | started,   | the |

|-------|---------|--------|-----------------|-----|------------|-----|

|       | holding | g capa | acitor is disco | nne | ected from | the |

|       | input p | in.    |                 |     |            |     |

To calculate the minimum acquisition time, Equation 16-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

Example 16-3 shows the calculation of the minimum required acquisition time, TACQ. This calculation is based on the following application system assumptions:

| CHOLD            | =      | 25 pF                              |

|------------------|--------|------------------------------------|

| Rs               | =      | 2.5 kΩ                             |

| Conversion Error | $\leq$ | 1/2 LSb                            |

| Vdd              | =      | $5V \rightarrow Rss = 2 \ k\Omega$ |

| Temperature      | =      | 85°C (system max.)                 |

## EQUATION 16-1: ACQUISITION TIME

TACQ = Amplifier Settling Time + Holding Capacitor Charging Time + Temperature Coefficient = TAMP + TC + TCOFF

### EQUATION 16-2: A/D MINIMUM CHARGING TIME

| VHOLD | = | $(\text{VREF} - (\text{VREF}/2048)) \bullet (1 - e^{(-\text{TC/CHOLD}(\text{Ric} + \text{Rss} + \text{Rs}))})$ |

|-------|---|----------------------------------------------------------------------------------------------------------------|

| or    |   |                                                                                                                |

| TC    | = | -(CHOLD)(RIC + RSS + RS) ln(1/2048)                                                                            |

### EQUATION 16-3: CALCULATING THE MINIMUM REQUIRED ACQUISITION TIME

| TACQ    | =      | TAMP + TC + TCOFF                                                                                                              |

|---------|--------|--------------------------------------------------------------------------------------------------------------------------------|

| TAMP    | =      | 0.2 μs                                                                                                                         |

| TCOFF   | =      | (Temp – 25°C)(0.02 μs/°C)<br>(85°C – 25°C)(0.02 μs/°C)<br>1.2 μs                                                               |

| Tempera | ture c | oefficient is only required for temperatures $> 25^{\circ}$ C. Below $25^{\circ}$ C, TCOFF = 0 ms.                             |

| Тс      | =      | -(Chold)(Ric + Rss + Rs) $\ln(1/2047)$<br>-(25 pF) (1 k $\Omega$ + 2 k $\Omega$ + 2.5 k $\Omega$ ) $\ln(0.0004883)$<br>1.05 µs |

| TACQ    | =      | 0.2 μs + 1 μs + 1.2 μs<br>2.4 μs                                                                                               |

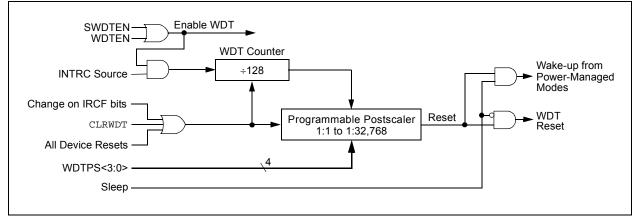

## 20.2 Watchdog Timer (WDT)

For PIC18F1230/1330 devices, the WDT is driven by the INTRC source. When the WDT is enabled, the clock source is also enabled. The nominal WDT period is 4 ms and has the same stability as the INTRC oscillator.

The 4 ms period of the WDT is multiplied by a 16-bit postscaler. Any output of the WDT postscaler is selected by a multiplexer, controlled by bits in Configuration Register 2H. Available periods range from 4 ms to 131.072 seconds (2.18 minutes). The WDT and postscaler are cleared when any of the following events occur: a SLEEP or CLRWDT instruction is executed, the IRCF bits (OSCCON<6:4>) are changed or a clock failure has occurred.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and postscaler counts when executed.

- 2: Changing the setting of the IRCF bits (OSCCON<6:4>) clears the WDT and postscaler counts.

- **3:** When a CLRWDT instruction is executed, the postscaler count will be cleared.

#### 20.2.1 CONTROL REGISTER

Register 20-15 shows the WDTCON register. This is a readable and writable register which contains a control bit that allows software to override the WDT enable Configuration bit, but only if the Configuration bit has disabled the WDT.

### FIGURE 20-1: WDT BLOCK DIAGRAM

# 20.5 Program Verification and Code Protection

The overall structure of the code protection on the PIC18 Flash devices differs significantly from other  $\text{PIC}^{\textcircled{R}}$  devices.

The user program memory is divided into three blocks. One of these is a Boot Block of variable size (maximum 2 Kbytes). The remainder of the memory is divided into two blocks on binary boundaries. Each of the three blocks has three code protection bits associated with them. They are:

- Code-Protect bit (CPx)

- Write-Protect bit (WRTx)

- External Block Table Read bit (EBTRx)

Figure 20-5 shows the program memory organization for 4 and 8-Kbyte devices and the specific code protection bit associated with each block. The actual locations of the bits are summarized in Table 20-3.

### FIGURE 20-5: CODE-PROTECTED PROGRAM MEMORY FOR PIC18F1230/1330

| 4 Kbytes<br>(PIC18F1230)   | IZE/DEVICE<br>8 Kbytes<br>(PIC18F1330) | Address<br>Range   | Block Code Protection<br>Controlled By: |

|----------------------------|----------------------------------------|--------------------|-----------------------------------------|

| Boot Block                 |                                        | 000000h<br>0003FFh | CPB, WRTB, EBTRB                        |

| Block 0                    | Boot Block                             | 000400h<br>0007FFh | CP0, WRT0, EBTR0                        |

| Block 1                    | Block 0                                | 000800h<br>000FFFh | CP1, WRT1, EBTR1                        |

| Unimplemented<br>Read '0's | Block 1                                | 001000h<br>001FFFh | CP2, WRT2, EBTR2                        |

| Unimplemented<br>Read '0's | Unimplemented<br>Read '0's             | 002000h            | (Unimplemented Memory Space)            |

|                            |                                        | 1FFFFFh            |                                         |

### TABLE 20-3: SUMMARY OF CODE PROTECTION REGISTERS

| File    | Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|-------|-------|-------|-------|-------|-------|-------|-------|

| 300008h | CONFIG5L |       | _     | —     | _     |       |       | CP1   | CP0   |

| 300009h | CONFIG5H | CPD   | CPB   | _     | _     | _     | _     | _     | _     |

| 30000Ah | CONFIG6L | —     | —     | —     | _     | _     | _     | WRT1  | WRT0  |

| 30000Bh | CONFIG6H | WRTD  | WRTB  | WRTC  | _     | _     | _     | —     | —     |

| 30000Ch | CONFIG7L | —     | —     | —     | _     | _     | _     | EBTR1 | EBTR0 |

| 30000Dh | CONFIG7H | —     | EBTRB | —     | _     | _     | _     | _     | —     |

Legend: Shaded cells are unimplemented.

# 22.0 INSTRUCTION SET SUMMARY

PIC18F1230/1330 devices incorporate the standard set of 75 PIC18 core instructions, as well as an extended set of 8 new instructions for the optimization of code that is recursive or that utilizes a software stack. The extended set is discussed later in this section.

## 22.1 Standard Instruction Set

The standard PIC18 instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from these PIC MCU instruction sets. Most instructions are a single program memory word (16 bits), but there are four instructions that require two program memory locations.

Each single-word instruction is a 16-bit word divided into an opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into four basic categories:

- · Byte-oriented operations

- **Bit-oriented** operations

- · Literal operations

- · Control operations

The PIC18 instruction set summary in Table 22-2 lists **byte-oriented**, **bit-oriented**, **literal** and **control** operations. Table 22-1 shows the opcode field descriptions.

Most byte-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The destination of the result (specified by 'd')

- 3. The accessed memory (specified by 'a')

The file register designator 'f' specifies which file register is to be used by the instruction. The destination designator 'd' specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the WREG register. If 'd' is one, the result is placed in the file register specified in the instruction.

All bit-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The bit in the file register (specified by 'b')

- 3. The accessed memory (specified by 'a')

The bit field designator 'b' selects the number of the bit affected by the operation, while the file register designator 'f' represents the number of the file in which the bit is located. The **literal** instructions may use some of the following operands:

- A literal value to be loaded into a file register (specified by 'k')

- The desired FSR register to load the literal value into (specified by 'f')

- No operand required (specified by '—')

The **control** instructions may use some of the following operands:

- A program memory address (specified by 'n')

- The mode of the CALL or RETURN instructions (specified by 's')

- The mode of the table read and table write instructions (specified by 'm')

- No operand required (specified by '—')

All instructions are a single word, except for four double-word instructions. These instructions were made double-word to contain the required information in 32 bits. In the second word, the 4 MSbs are '1's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

All single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles, with the additional instruction cycle(s) executed as a NOP.

The double-word instructions execute in two instruction cycles.

One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Two-word branch instructions (if true) would take 3  $\mu$ s.

Figure 22-1 shows the general formats that the instructions can have. All examples use the convention 'nnh' to represent a hexadecimal number.

The Instruction Set Summary, shown in Table 22-2, lists the standard instructions recognized by the Microchip MPASM<sup>™</sup> Assembler.

Section 22.1.1 "Standard Instruction Set" provides a description of each instruction.

# PIC18F1230/1330

### TABLE 22-2: PIC18FXXXX INSTRUCTION SET

| Mnemo     | nic,                            | Description                              | Quality    | 16-  | Bit Instr | uction W | ord  | Status           | Neter      |

|-----------|---------------------------------|------------------------------------------|------------|------|-----------|----------|------|------------------|------------|

| Operands  |                                 | Description                              | Cycles     | MSb  |           |          | LSb  | Affected         | Notes      |

| BYTE-ORIE | BYTE-ORIENTED OPERATIONS        |                                          |            |      |           |          |      |                  |            |

| ADDWF     | f, d, a                         | Add WREG and f                           | 1          | 0010 | 01da0     | ffff     | ffff | C, DC, Z, OV, N  | 1, 2       |

| ADDWFC    | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010 | 00da      | ffff     | ffff | C, DC, Z, OV, N  | 1, 2       |

| ANDWF     | f, d, a                         | AND WREG with f                          | 1          | 0001 | 01da      | ffff     | ffff | Z, N             | 1,2        |

| CLRF      | f, a                            | Clear f                                  | 1          | 0110 | 101a      | ffff     | ffff | Z                | 2          |

| COMF      | f, d, a                         | Complement f                             | 1          | 0001 | 11da      | ffff     | ffff | Z, N             | 1, 2       |

| CPFSEQ    | f, a                            | Compare f with WREG, Skip =              | 1 (2 or 3) | 0110 | 001a      | ffff     | ffff | None             | 4          |

| CPFSGT    | f, a                            | Compare f with WREG, Skip >              | 1 (2 or 3) | 0110 | 010a      | ffff     | ffff | None             | 4          |

| CPFSLT    | f, a                            | Compare f with WREG, Skip <              | 1 (2 or 3) | 0110 | 000a      | ffff     | ffff | None             | 1, 2       |

| DECF      | f, d, a                         | Decrement f                              | 1          | 0000 | 01da      | ffff     | ffff | C, DC, Z, OV, N  | 1, 2, 3, 4 |

| DECFSZ    | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010 | 11da      | ffff     | ffff | None             | 1, 2, 3, 4 |

| DCFSNZ    | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100 | 11da      | ffff     | ffff | None             | 1, 2       |

| INCF      | f, d, a                         | Increment f                              | 1          | 0010 | 10da      | ffff     | ffff | C, DC, Z, OV, N  | 1, 2, 3, 4 |

| INCFSZ    | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011 | 11da      | ffff     | ffff | None             | 4          |

| INFSNZ    | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100 | 10da      | ffff     | ffff | None             | 1, 2       |

| IORWF     | f, d, a                         | Inclusive OR WREG with f                 | 1          | 0001 | 00da      | ffff     | ffff | Z, N             | 1, 2       |

| MOVF      | f, d, a                         | Move f                                   | 1          | 0101 | 00da      | ffff     | ffff | Z, N             | 1          |

| MOVFF     | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2          | 1100 | ffff      | ffff     | ffff | None             |            |

|           |                                 | f <sub>d</sub> (destination) 2nd word    |            | 1111 | ffff      | ffff     | ffff |                  |            |

| MOVWF     | f, a                            | Move WREG to f                           | 1          | 0110 | 111a      | ffff     | ffff | None             |            |

| MULWF     | f, a                            | Multiply WREG with f                     | 1          | 0000 | 001a      | ffff     | ffff | None             | 1, 2       |

| NEGF      | f, a                            | Negate f                                 | 1          | 0110 | 110a      | ffff     | ffff | C, DC, Z, OV, N  |            |

| RLCF      | f, d, a                         | Rotate Left f through Carry              | 1          | 0011 | 01da      | ffff     | ffff | C, Z, N          | 1, 2       |

| RLNCF     | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100 | 01da      | ffff     | ffff | Z, N             |            |

| RRCF      | f, d, a                         | Rotate Right f through Carry             | 1          | 0011 | 00da      | ffff     | ffff | C, Z, N          |            |

| RRNCF     | f, d, a                         | Rotate Right f (No Carry)                | 1          | 0100 | 00da      | ffff     | ffff | Z, N             |            |

| SETF      | f, a                            | Set f                                    | 1          | 0110 | 100a      | ffff     | ffff | None             | 1, 2       |

| SUBFWB    | f, d, a                         | Subtract f from WREG with<br>Borrow      | 1          | 0101 | 01da      | ffff     | ffff | C, DC, Z, OV, N  |            |

| SUBWF     | f, d, a                         | Subtract WREG from f                     | 1          | 0101 | 11da      | ffff     | ffff | C, DC, Z, OV, N  | 1, 2       |

| SUBWFB    | f, d, a                         | Subtract WREG from f with                | 1          | 0101 | 10da      | ffff     | ffff | C, DC, Z, OV, N  |            |

|           | , -,                            | Borrow                                   |            |      |           |          | _    | , _, , _ , _ , _ |            |

| SWAPF     | f, d, a                         | Swap Nibbles in f                        | 1          | 0011 | 10da      | ffff     | ffff | None             | 4          |

| TSTFSZ    | f, a                            | Test f, Skip if 0                        | 1 (2 or 3) | 0110 | 011a      | ffff     | ffff | None             | 1, 2       |

| XORWF     | f, d, a                         | Exclusive OR WREG with f                 | 1          | 0001 | 10da      | ffff     | ffff | Z, N             | l í        |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

3: If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

# PIC18F1230/1330

| RRNCF                                                                                                                            | Rotate Right f (No Carry)                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |                              |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------|--|--|--|--|--|

| Syntax:                                                                                                                          | RRNCF                                                                                                                                                                                             | f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |                              |  |  |  |  |  |

| Operands:                                                                                                                        | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |                              |  |  |  |  |  |

| Operation:                                                                                                                       | . ,                                                                                                                                                                                               | (f <n>) → dest<n 1="" –="">,<br/>(f&lt;0&gt;) → dest&lt;7&gt;</n></n>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |                              |  |  |  |  |  |

| Status Affected:                                                                                                                 | N, Z                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |                              |  |  |  |  |  |

| Encoding:                                                                                                                        | 0100                                                                                                                                                                                              | 00da                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ffff | ffff                         |  |  |  |  |  |

| Description:                                                                                                                     | one bit to t<br>is placed in<br>placed bac<br>If 'a' is '0',<br>selected, c<br>is '1', then<br>per the BS<br>If 'a' is '0' a<br>set is enab<br>in Indexed<br>mode whe<br>Section 2:<br>Bit-Orient | The contents of register 'f' are rotated<br>one bit to the right. If 'd' is '0', the result<br>is placed in W. If 'd' is '1', the result is<br>placed back in register 'f'.<br>If 'a' is '0', the Access Bank will be<br>selected, overriding the BSR value. If 'a'<br>is '1', then the bank will be selected as<br>per the BSR value.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 22.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |      |                              |  |  |  |  |  |

|                                                                                                                                  |                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |                              |  |  |  |  |  |

| M/anda.                                                                                                                          | _                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |                              |  |  |  |  |  |

| Words:                                                                                                                           | 1                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |                              |  |  |  |  |  |

| Cycles:                                                                                                                          | 1<br>1                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |                              |  |  |  |  |  |

| Cycles:<br>Q Cycle Activity:                                                                                                     | 1                                                                                                                                                                                                 | 03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |                              |  |  |  |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1                                                                                               | 1<br>Q2                                                                                                                                                                                           | Q3<br>Proces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | as 1 | Q4<br>Write to               |  |  |  |  |  |

| Cycles:<br>Q Cycle Activity:                                                                                                     | 1                                                                                                                                                                                                 | Q3<br>Proces<br>Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | Q4<br>Write to<br>estination |  |  |  |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1                                                                                               | 1<br>Q2<br>Read<br>register 'f'<br>RRNCF<br>tion<br>= 1101                                                                                                                                        | Proces<br>Data<br>REG, 1,<br>0111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | de   | Write to                     |  |  |  |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example 1:<br>Before Instruct<br>REG<br>After Instruction<br>REG                 | 1<br>Q2<br>Read<br>register 'f'<br>RRNCF<br>tion<br>= 1101<br>on                                                                                                                                  | Proces<br>Data<br>REG, 1,<br>0111<br>1011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0    | Write to                     |  |  |  |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example 1:<br>Before Instruct<br>REG<br>After Instruction<br>REG                 | 1<br>Q2<br>Read<br>register 'f'<br>RRNCF<br>tion<br>= 1101<br>on<br>= 1110<br>RRNCF                                                                                                               | Proces<br>Data<br>REG, 1,<br>0111<br>1011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0    | Write to                     |  |  |  |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example 1:<br>Before Instructor<br>REG<br>After Instruction<br>REG<br>Example 2: | 1<br>Q2<br>Read<br>register 'f'<br>RRNCF<br>tion<br>= 1101<br>m<br>= 1110<br>RRNCF<br>tion<br>= ?<br>= 1101                                                                                       | Proces<br>Data<br>REG, 1,<br>0111<br>1011<br>REG, 0,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0    | Write to                     |  |  |  |  |  |

| SETF     |             | Set f                                                                                                                                                                                     |                                                                                                                  |                                                                                                          |                                                                                                      |  |  |  |  |  |

|----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:  |             |                                                                                                                                                                                           |                                                                                                                  |                                                                                                          |                                                                                                      |  |  |  |  |  |

| Operand  | ls:         | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                  |                                                                                                                  |                                                                                                          |                                                                                                      |  |  |  |  |  |

| Operatio | on:         | $FFh\tof$                                                                                                                                                                                 |                                                                                                                  |                                                                                                          |                                                                                                      |  |  |  |  |  |

| Status A | ffected:    | None                                                                                                                                                                                      |                                                                                                                  |                                                                                                          |                                                                                                      |  |  |  |  |  |

| Encodin  | g:          | 0110                                                                                                                                                                                      | 100a                                                                                                             | ffff                                                                                                     | ffff                                                                                                 |  |  |  |  |  |

| Descript | ion:        | The conten<br>are set to F<br>If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank.<br>If 'a' is '0' a<br>set is enab<br>in Indexed<br>mode wher<br>Section 22<br>Bit-Oriente<br>Literal Offe | Fh.<br>the Access<br>the BSR i<br>und the ex<br>led, this i<br>Literal Of<br>never f ≤<br>2.2.3 "By<br>ed Instru | ss Bank i<br>s used to<br>ktended i<br>nstructio<br>ffset Add<br>95 (5Fh)<br><b>te-Orien</b><br>ctions i | s selected.<br>o select the<br>instruction<br>n operates<br>ressing<br>. See<br>ted and<br>n Indexed |  |  |  |  |  |