Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                     |

| Peripherals                | DMA, I <sup>2</sup> S, LCD, LVD, POR, PWM, WDT                        |

| Number of I/O              | 54                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 16K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                          |

| Data Converters            | A/D 20x16b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LFBGA                                                              |

| Supplier Device Package    | 64-MAPBGA (5x5)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkl33z128vmp4 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Operating Characteristics**

- Voltage range: 1.71 to 3.6 V

- Flash write voltage range: 1.71 to 3.6 V

- Temperature range: –40 to 105 °C

### Packages

- 64 LQFP 10mm x 10mm, 0.5mm pitch, 1.6mm thickness

- 64 MAPBGA 5mm x 5mm, 0.5mm pitch, 1.23mm thickness

#### Security and Integrity

- 80-bit unique identification number per chip

- Advanced flash security

- I/O

- Up to 54 general-purpose input/output pins (GPIO) and 6 high-drive pad

#### Low Power

- Down to 54uA/MHz in very low power run mode

- Down to 1.96uA in VLLS3 mode (RAM + RTC retained)

- · Six flexible static modes

| Ordering Information |                           |               |              |              |         |                    |                                |                            |

|----------------------|---------------------------|---------------|--------------|--------------|---------|--------------------|--------------------------------|----------------------------|

| Pro                  | duct                      | Mer           | nory         | Package      |         | IO and ADC channel |                                |                            |

| Part number          | Marking (Line1/<br>Line2) | Flash<br>(KB) | SRAM<br>(KB) | Pin<br>count | Package | GPIOs              | GPIOs<br>(INT/HD) <sup>1</sup> | ADC<br>channels<br>(SE/DP) |

| MKL33Z128VLH4        | MKL33Z128V//LH4           | 128           | 16           | 64           | LQFP    | 54                 | 31/6                           | 20/4                       |

| MKL33Z256VLH4        | MKL33Z256V//LH4           | 256           | 32           | 64           | LQFP    | 54                 | 31/6                           | 20/4                       |

| MKL33Z128VMP4        | M33P7V                    | 128           | 16           | 64           | MAPBGA  | 54                 | 31/6                           | 20/4                       |

| MKL33Z256VMP4        | M33P8V                    | 256           | 32           | 64           | MAPBGA  | 54                 | 31/6                           | 20/4                       |

1. INT: interrupt pin numbers; HD: high drive pin numbers

### **Related Resources**

| Туре                | Description                                                                                                                      | Resource                                                                 |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Selector<br>Guide   | The Freescale Solution Advisor is a web-based tool that features interactive application wizards and a dynamic product selector. | Solution Advisor                                                         |

| Product Brief       | The Product Brief contains concise overview/summary information to enable quick evaluation of a device for design suitability.   | KLX3PB <sup>1</sup>                                                      |

| Reference<br>Manual | The Reference Manual contains a comprehensive description of the structure and function (operation) of a device.                 | KL33P64M48SF6RM <sup>1</sup>                                             |

| Data Sheet          | The Data Sheet includes electrical characteristics and signal connections.                                                       | This document.                                                           |

| Chip Errata         | The chip mask set Errata provides additional or corrective information for a particular device mask set.                         | KINETIS_L_1N71K <sup>1</sup>                                             |

| Package<br>drawing  | Package dimensions are provided in package drawings.                                                                             | 64-LQFP: 98ASS23234W <sup>1</sup> 64<br>MAPBGA: 98ASA00420D <sup>1</sup> |

1. To find the associated resource, go to http://www.freescale.com and perform a search using this term.

| Symbol           | Description                                                                                         | Min. | Max.  | Unit | Notes |

|------------------|-----------------------------------------------------------------------------------------------------|------|-------|------|-------|

|                  | • $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}, \text{ I}_{\text{OL}} = 18 \text{ mA}$ | —    | 0.5   | V    |       |

|                  | • 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V, I <sub>OL</sub> = 6 mA                                |      |       |      |       |

| I <sub>OLT</sub> | Output low current total for all ports                                                              | —    | 100   | mA   |       |

| I <sub>IN</sub>  | Input leakage current (per pin) for full temperature range                                          | _    | 1     | μA   | 2     |

| I <sub>IN</sub>  | Input leakage current (per pin) at 25 °C                                                            | —    | 0.025 | μA   | 2     |

| I <sub>IN</sub>  | Input leakage current (total all pins) for full temperature range                                   | _    | 64    | μA   | 2     |

| I <sub>OZ</sub>  | Hi-Z (off-state) leakage current (per pin)                                                          | —    | 1     | μA   |       |

| R <sub>PU</sub>  | Internal pullup resistors                                                                           | 20   | 50    | kΩ   | 3     |

### Table 7. Voltage and current operating behaviors (continued)

1. PTB0, PTB1, PTC3, PTC4, PTD6, and PTD7 I/O have both high drive and normal drive capability selected by the associated PTx\_PCRn[DSE] control bit. All other GPIOs are normal drive only.

2. Measured at  $V_{DD} = 3.6 V$

3. Measured at V<sub>DD</sub> supply voltage = V<sub>DD</sub> min and Vinput = V<sub>SS</sub>

# 2.2.4 Power mode transition operating behaviors

All specifications except  $t_{POR}$  and VLLSx $\rightarrow$ RUN recovery times in the following table assume this clock configuration:

- CPU and system clocks = 48 MHz

- Bus and flash clock = 24 MHz

- HIRC clock mode

| Symbol           | Description                                                                                                                                                       | Min. | Тур. | Max. | Unit | Notes |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| t <sub>POR</sub> | After a POR event, amount of time from the point $V_{DD}$ reaches 1.8 V to execution of the first instruction across the operating temperature range of the chip. | _    | _    | 300  | μs   | 1     |

|                  | • VLLS0 → RUN                                                                                                                                                     | _    | 152  | 166  | μs   |       |

|                  | • VLLS1 → RUN                                                                                                                                                     | _    | 152  | 166  | μs   |       |

|                  | • VLLS3 → RUN                                                                                                                                                     | _    | 93   | 104  | μs   |       |

|                  | • LLS → RUN                                                                                                                                                       | _    | 7.5  | 8    | μs   |       |

Table continues on the next page ...

8

| Symbol               | Description                                                                                                                                                                                | Min. | Тур.   | Max.          | Unit  | Notes |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|---------------|-------|-------|

| I <sub>DD_VLPR</sub> | Very-low-power run mode current—2 MHz LIRC<br>mode, While(1) loop in SRAM all peripheral clock<br>enable, 2 MHz core / 0.5 MHz flash, V <sub>DD</sub> = 3.0 V<br>• at 25 °C                |      | 208    | 289           | μA    |       |

| I <sub>DD_WAIT</sub> | Wait mode current—core disabled, 48 MHz<br>system/24 MHz bus, flash disabled (flash doze<br>enabled), all peripheral clocks disabled,<br>MCG_Lite under HIRC mode, V <sub>DD</sub> = 3.0 V | _    | 1.81   | 1.89          | mA    |       |

| I <sub>DD_WAIT</sub> | Wait mode current—core disabled, 24 MHz<br>system/12 MHz bus, flash disabled (flash doze<br>enabled), all peripheral clocks disabled,<br>MCG_Lite under HIRC mode, V <sub>DD</sub> = 3.0 V | _    | 1.22   | 1.39          | mA    |       |

| I <sub>DD_VLPW</sub> | Very-low-power wait mode current, core<br>disabled, 4 MHz system/ 1 MHz bus and flash,<br>all peripheral clocks disabled, V <sub>DD</sub> = 3.0 V                                          | _    | 172    | 182           | μA    |       |

| I <sub>DD_VLPW</sub> | Very-low-power wait mode current, core disabled, 2 MHz system/ 0.5 MHz bus and flash, all peripheral clocks disabled, $V_{DD} = 3.0 V$                                                     | _    | 69     | 76            | μA    |       |

| I <sub>DD_VLPW</sub> | Very-low-power wait mode current, core<br>disabled, 125 kHz system/ 31.25 kHz bus and<br>flash, all peripheral clocks disabled, V <sub>DD</sub> = 3.0 V                                    | —    | 36     | 40            | μΑ    |       |

| DD_PSTOP2            | Partial Stop 2, core and system clock disabled, 12 MHz bus and flash, $V_{DD} = 3.0 V$                                                                                                     |      |        |               |       |       |

|                      |                                                                                                                                                                                            |      | 1.81   | 2.06          | mA    |       |

| DD_PSTOP2            | Partial Stop 2, core and system clock disabled, flash doze enabled, 12 MHz bus, $V_{DD} = 3.0 \text{ V}$                                                                                   |      |        |               |       |       |

|                      |                                                                                                                                                                                            |      | 1.00   | 1.25          | mA    |       |

| I <sub>DD_STOP</sub> | Stop mode current at 3.0 V<br>• at 25 °C and below                                                                                                                                         | _    | 161.93 | 171.82        |       |       |

|                      | • at 50 °C                                                                                                                                                                                 | _    | 181.45 | 191.96        |       |       |

|                      | • at 85 °C                                                                                                                                                                                 |      | 236.29 | 271.17        | μA    |       |

|                      | • at 105 °C                                                                                                                                                                                |      | 390.33 | 465.58        |       |       |

| I <sub>DD_VLPS</sub> | Very-low-power stop mode current at 3.0 V<br>• at 25 °C and below                                                                                                                          |      | 3.31   | 5.14          |       |       |

|                      | • at 50 °C                                                                                                                                                                                 | _    | 10.43  | 17.68         |       |       |

|                      | • at 85 °C                                                                                                                                                                                 | _    | 34.14  | 61.06         | μA    |       |

|                      | • at 105 °C                                                                                                                                                                                |      | 104.38 | 164.44        | Pr. 1 |       |

| I <sub>DD_VLPS</sub> | Very-low-power stop mode current at 1.8 V<br>• at 25 °C and below                                                                                                                          |      | 3.21   | 5.22          |       |       |

|                      | • at 50 °C                                                                                                                                                                                 | _    | 10.26  | 5.22<br>17.62 |       |       |

| 1                    |                                                                                                                                                                                            |      |        |               |       |       |

### Table 9. Power consumption operating behaviors (continued)

| Symbol                | Description                                              | Min. | Тур.   | Max.   | Unit | Notes |

|-----------------------|----------------------------------------------------------|------|--------|--------|------|-------|

|                       | • at 85 °C                                               |      | 102.92 | 162.20 |      |       |

|                       | • at 105 °C                                              |      |        |        |      |       |

| I <sub>DD_LLS</sub>   | Low-leakage stop mode current, all peripheral            |      |        |        |      |       |

|                       | disable, at 3.0 V<br>• at 25 °C and below                |      | 2.06   | 3.33   | μA   |       |

|                       | • at 50 °C                                               | _    | 4.72   | 6.85   |      |       |

|                       | • at 70 °C                                               |      | 8.13   | 13.30  |      |       |

|                       | • at 85 °C                                               |      | 13.34  | 24.70  |      |       |

|                       |                                                          | _    | 41.08  | 52.43  |      |       |

|                       | • at 105 °C                                              |      |        |        |      |       |

| $I_{DD_{LLS}}$        | Low-leakage stop mode current with RTC                   |      |        |        |      |       |

|                       | current, at 3.0 V<br>• at 25 °C and below                |      | 2.46   | 3.73   | μA   |       |

|                       | • at 50 °C                                               |      | 5.12   | 7.25   |      |       |

|                       | • at 70 °C                                               | _    | 8.53   | 11.78  |      |       |

|                       | • at 85 °C                                               | —    | 13.74  | 18.91  |      |       |

|                       | • at 105 °C                                              | _    | 41.48  | 52.83  |      |       |

|                       |                                                          |      |        |        |      |       |

| I <sub>DD_LLS</sub>   | Low-leakage stop mode current with RTC current, at 1.8 V |      |        | 0.70   | μA   | 3     |

|                       | <ul> <li>at 25 °C and below</li> </ul>                   |      | 2.35   | 2.70   |      |       |

|                       | • at 50 °C                                               | —    | 4.91   | 6.75   |      |       |

|                       | • at 70 °C                                               |      | 8.32   | 11.78  |      |       |

|                       | • at 85 °C                                               | —    | 13.44  | 18.21  |      |       |

|                       | • at 105 °C                                              |      | 40.47  | 51.85  |      |       |

| I <sub>DD_VLLS3</sub> | Very-low-leakage stop mode 3 current, all                |      |        |        |      |       |

| 20_1100               | peripheral disable, at 3.0 V                             |      | 1.45   | 1.85   | μA   |       |

|                       | • at 25 °C and below                                     |      | 3.37   | 4.39   |      |       |

|                       | • at 50 °C                                               |      | 5.76   | 8.48   |      |       |

|                       | • at 70 °C                                               |      | 9.72   | 14.30  |      |       |

|                       | • at 85 °C                                               |      | 30.41  | 37.50  |      |       |

|                       | • at 105 °C                                              |      | 00.11  | 07.00  |      |       |

| I <sub>DD_VLLS3</sub> | Very-low-leakage stop mode 3 current with RTC            |      |        |        |      | 3     |

|                       | current, at 3.0 V<br>• at 25 °C and below                | _    | 2.05   | 2.45   | μA   |       |

|                       | • at 50 °C                                               |      | 3.97   | 4.99   |      |       |

|                       | • at 70 °C                                               | _    | 6.36   | 9.08   |      |       |

|                       | • at 85 °C                                               | _    | 10.32  | 14.73  |      |       |

|                       | • at 105 °C                                              | _    | 31.01  | 38.10  |      |       |

|                       |                                                          |      |        |        |      |       |

Table 9. Power consumption operating behaviors (continued)

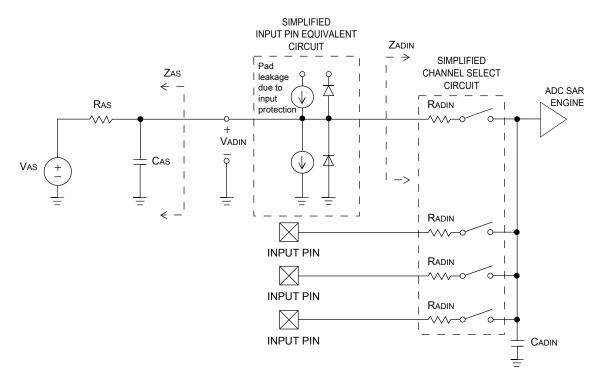

#### Peripheral operating requirements and behaviors

Figure 7. ADC input impedance equivalency diagram

## 3.6.1.2 16-bit ADC electrical characteristics

|                      |                              |                                          |             | DDA,              |                     | JA/              |                      |

|----------------------|------------------------------|------------------------------------------|-------------|-------------------|---------------------|------------------|----------------------|

| Symbol               | Description                  | Conditions <sup>1</sup>                  | Min.        | Typ. <sup>2</sup> | Max.                | Unit             | Notes                |

| I <sub>DDA_ADC</sub> | Supply current               |                                          | 0.215       | _                 | 1.7                 | mA               | 3                    |

|                      | ADC                          | • ADLPC = 1, ADHSC = 0                   | 1.2         | 2.4               | 3.9                 | MHz              | t <sub>ADACK</sub> = |

|                      | asynchronous<br>clock source | <ul> <li>ADLPC = 1, ADHSC = 1</li> </ul> | 2.4         | 4.0               | 6.1                 | MHz              | 1/f <sub>ADACk</sub> |

| f <sub>ADACK</sub>   |                              | <ul> <li>ADLPC = 0, ADHSC = 0</li> </ul> | 3.0         | 5.2               | 7.3                 | MHz              |                      |

|                      |                              | • ADLPC = 0, ADHSC = 1                   | 4.4         | 6.2               | 9.5                 | MHz              |                      |

|                      | Sample Time                  | See Reference Manual chapter for         | sample time | es                | 1                   | I                | I                    |

| TUE                  | Total                        | 12-bit modes                             |             | ±4                | ±6.8                | LSB <sup>4</sup> | 5                    |

|                      | unadjusted error             | <ul> <li>&lt;12-bit modes</li> </ul>     | _           | ±1.4              | ±2.1                |                  |                      |

| DNL                  | Differential non-            | 12-bit modes                             | _           | ±0.7              | -1.1 to             | LSB <sup>4</sup> | 5                    |

|                      | linearity                    | • <12-bit modes                          | _           | ±0.2              | +1.9<br>-0.3 to 0.5 |                  |                      |

| INL                  | Integral non-<br>linearity   | 12-bit modes                             | _           | ±1.0              | -2.7 to<br>+1.9     | LSB <sup>4</sup> | 5                    |

|                      |                              | <ul> <li>&lt;12-bit modes</li> </ul>     | _           | ±0.5              |                     |                  |                      |

| Table 27. | 16-bit ADC | characteristics | (V <sub>REFH</sub> = | $V_{DDA}$ , | V <sub>REFL</sub> = | V <sub>SSA</sub> ) |

|-----------|------------|-----------------|----------------------|-------------|---------------------|--------------------|

|-----------|------------|-----------------|----------------------|-------------|---------------------|--------------------|

Peripheral operating requirements and behaviors

| Symbol         | Description | Min. | Max. | Unit | Notes |

|----------------|-------------|------|------|------|-------|

| T <sub>A</sub> | Temperature | 0    | 50   | °C   | —     |

### Table 30. VREF limited-range operating requirements

### Table 31. VREF limited-range operating behaviors

| Symbol           | Description                                | Min.  | Max.  | Unit | Notes |

|------------------|--------------------------------------------|-------|-------|------|-------|

| V <sub>out</sub> | Voltage reference output with factory trim | 1.173 | 1.225 | V    | _     |

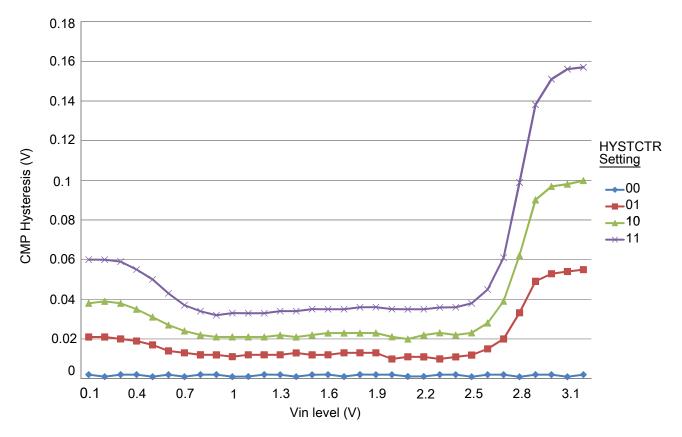

# 3.6.3 CMP and 6-bit DAC electrical specifications

Table 32. Comparator and 6-bit DAC electrical specifications

| Symbol             | Description                                         | Min.                  | Тур. | Max.            | Unit             |

|--------------------|-----------------------------------------------------|-----------------------|------|-----------------|------------------|

| V <sub>DD</sub>    | Supply voltage                                      | 1.71                  |      | 3.6             | V                |

| IDDHS              | Supply current, High-speed mode (EN=1, PMODE=1)     | —                     |      | 200             | μA               |

| I <sub>DDLS</sub>  | Supply current, low-speed mode (EN=1, PMODE=0)      | —                     | _    | 20              | μA               |

| V <sub>AIN</sub>   | Analog input voltage                                | V <sub>SS</sub> – 0.3 |      | V <sub>DD</sub> | V                |

| V <sub>AIO</sub>   | Analog input offset voltage                         | —                     |      | 20              | mV               |

| V <sub>H</sub>     | Analog comparator hysteresis <sup>1</sup>           |                       |      |                 |                  |

|                    | • CR0[HYSTCTR] = 00                                 | _                     | 5    | _               | mV               |

|                    | • CR0[HYSTCTR] = 01                                 | _                     | 10   | _               | mV               |

|                    | • CR0[HYSTCTR] = 10                                 | _                     | 20   | _               | mV               |

|                    | • CR0[HYSTCTR] = 11                                 | _                     | 30   | _               | mV               |

| V <sub>CMPOh</sub> | Output high                                         | V <sub>DD</sub> – 0.5 |      |                 | V                |

| V <sub>CMPOI</sub> | Output low                                          | —                     | _    | 0.5             | V                |

| t <sub>DHS</sub>   | Propagation delay, high-speed mode (EN=1, PMODE=1)  | 20                    | 50   | 200             | ns               |

| t <sub>DLS</sub>   | Propagation delay, low-speed mode (EN=1, PMODE=0)   | 80                    | 250  | 600             | ns               |

|                    | Analog comparator initialization delay <sup>2</sup> | —                     | _    | 40              | μs               |

| I <sub>DAC6b</sub> | 6-bit DAC current adder (enabled)                   | _                     | 7    | _               | μA               |

| INL                | 6-bit DAC integral non-linearity                    | -0.5                  |      | 0.5             | LSB <sup>3</sup> |

| DNL                | 6-bit DAC differential non-linearity                | -0.3                  |      | 0.3             | LSB              |

1. Typical hysteresis is measured with input voltage range limited to 0.6 to  $V_{DD}$ -0.6 V.

Comparator initialization delay is defined as the time between software writes to change control inputs (Writes to CMP\_DACCR[DACEN], CMP\_DACCR[VRSEL], CMP\_DACCR[VOSEL], CMP\_MUXCR[PSEL], and CMP\_MUXCR[MSEL]) and the comparator output settling to a stable level.

3. 1 LSB = V<sub>reference</sub>/64

Peripheral operating requirements and behaviors

Figure 11. Typical hysteresis vs. Vin level (VDD = 3.3 V, PMODE = 1)

# 3.6.4 12-bit DAC electrical characteristics

### 3.6.4.1 12-bit DAC operating requirements Table 33. 12-bit DAC operating requirements

| Symbol            | Desciption              | Min. | Max. | Unit | Notes |

|-------------------|-------------------------|------|------|------|-------|

| V <sub>DDA</sub>  | Supply voltage          |      | 3.6  | V    |       |

| V <sub>DACR</sub> | Reference voltage       | 1.13 | 3.6  | V    | 1     |

| CL                | Output load capacitance | —    | 100  | pF   | 2     |

| ١L                | Output load current     | _    | 1    | mA   |       |

1. The DAC reference can be selected to be  $V_{\text{DDA}}$  or  $V_{\text{REFH}}$

2. A small load capacitance (47 pF) can improve the bandwidth performance of the DAC.

| Num. | Symbol          | Description                   | Min. | Max.                     | Unit | Note |

|------|-----------------|-------------------------------|------|--------------------------|------|------|

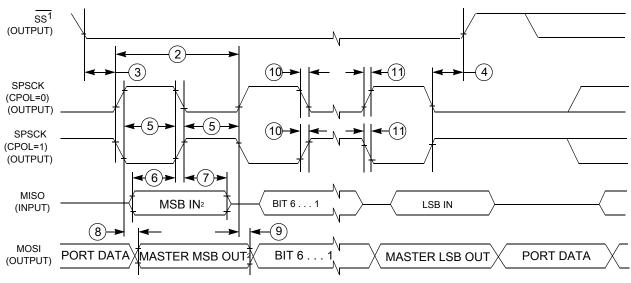

| 8    | t <sub>v</sub>  | Data valid (after SPSCK edge) | —    | 52                       | ns   | —    |

| 9    | t <sub>HO</sub> | Data hold time (outputs)      | 0    | —                        | ns   | —    |

| 10   | t <sub>RI</sub> | Rise time input               | —    | t <sub>periph</sub> - 25 | ns   | —    |

|      | t <sub>FI</sub> | Fall time input               |      |                          |      |      |

| 11   | t <sub>RO</sub> | Rise time output              | —    | 36                       | ns   | —    |

|      | t <sub>FO</sub> | Fall time output              |      |                          |      |      |

Table 36. SPI master mode timing on slew rate enabled pads (continued)

- 1. For SPI0  $f_{periph}$  is the bus clock ( $f_{BUS}$ ). For SPI1  $f_{periph}$  is the system clock ( $f_{SYS}$ ).

- 2.  $t_{periph} = 1/f_{periph}$

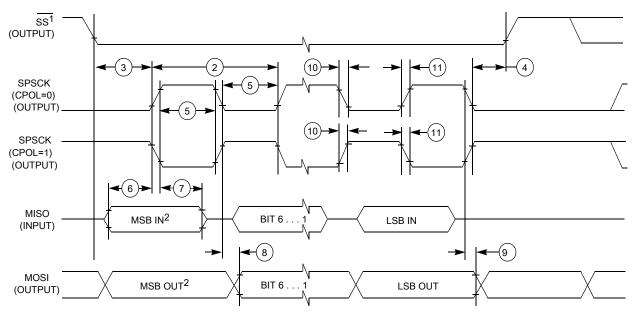

1. If configured as an output.

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

### Figure 14. SPI master mode timing (CPHA = 0)

#### Peripheral operating requirements and behaviors

1.If configured as output

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

### Figure 15. SPI master mode timing (CPHA = 1)

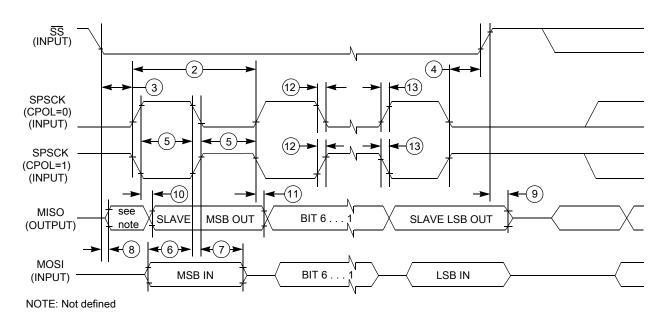

| Table 37. | SPI slave mode timing on slew rate disabled pad | s |

|-----------|-------------------------------------------------|---|

|-----------|-------------------------------------------------|---|

| Num. | Symbol              | Description                    | Min.                     | Max.                     | Unit                | Note |

|------|---------------------|--------------------------------|--------------------------|--------------------------|---------------------|------|

| 1    | f <sub>op</sub>     | Frequency of operation         | 0                        | f <sub>periph</sub> /4   | Hz                  | 1    |

| 2    | t <sub>SPSCK</sub>  | SPSCK period                   | 4 x t <sub>periph</sub>  | _                        | ns                  | 2    |

| 3    | t <sub>Lead</sub>   | Enable lead time               | 1                        | _                        | t <sub>periph</sub> | —    |

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1                        |                          | t <sub>periph</sub> | _    |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30 | _                        | ns                  | —    |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 2.5                      | _                        | ns                  | —    |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 3.5                      |                          | ns                  | _    |

| 8    | t <sub>a</sub>      | Slave access time              | —                        | t <sub>periph</sub>      | ns                  | 3    |

| 9    | t <sub>dis</sub>    | Slave MISO disable time        | —                        | t <sub>periph</sub>      | ns                  | 4    |

| 10   | t <sub>v</sub>      | Data valid (after SPSCK edge)  | —                        | 31                       | ns                  | —    |

| 11   | t <sub>HO</sub>     | Data hold time (outputs)       | 0                        | _                        | ns                  | —    |

| 12   | t <sub>RI</sub>     | Rise time input                | _                        | t <sub>periph</sub> - 25 | ns                  | _    |

|      | t <sub>FI</sub>     | Fall time input                | 1                        |                          |                     |      |

| 13   | t <sub>RO</sub>     | Rise time output               | —                        | 25                       | ns                  | _    |

|      | t <sub>FO</sub>     | Fall time output               |                          |                          |                     |      |

1. For SPI0  $f_{periph}$  is the bus clock (f\_{BUS}). For SPI1  $f_{periph}$  is the system clock (f\_{SYS}).

- 2.  $t_{periph} = 1/f_{periph}$

- 3. Time to data active from high-impedance state

- 4. Hold time to high-impedance state

#### Peripheral operating requirements and behaviors

Figure 17. SPI slave mode timing (CPHA = 1)

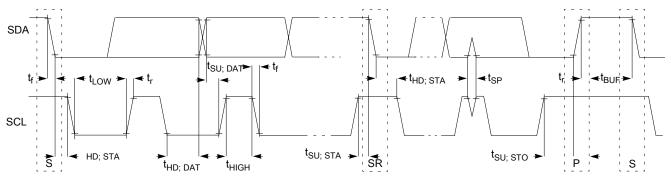

# 3.8.2 I<sup>2</sup>C

### 3.8.2.1 Inter-Integrated Circuit Interface (I2C) timing Table 39. I2C timing

| Characteristic                                                                                     | Characteristic Symbol Standard Mode |                  | Fast              | Unit                               |                  |     |

|----------------------------------------------------------------------------------------------------|-------------------------------------|------------------|-------------------|------------------------------------|------------------|-----|

|                                                                                                    |                                     | Minimum          | Maximum           | Minimum                            | Maximum          |     |

| SCL Clock Frequency                                                                                | f <sub>SCL</sub>                    | 0                | 100               | 0                                  | 400 <sup>1</sup> | kHz |

| Hold time (repeated) START condition.<br>After this period, the first clock pulse is<br>generated. | t <sub>HD</sub> ; STA               | 4                | —                 | 0.6                                | —                | μs  |

| LOW period of the SCL clock                                                                        | t <sub>LOW</sub>                    | 4.7              | —                 | 1.25                               | —                | μs  |

| HIGH period of the SCL clock                                                                       | t <sub>HIGH</sub>                   | 4                | —                 | 0.6                                | —                | μs  |

| Set-up time for a repeated START condition                                                         | t <sub>SU</sub> ; STA               | 4.7              | _                 | 0.6                                | —                | μs  |

| Data hold time for I <sup>2</sup> C bus devices                                                    | t <sub>HD</sub> ; DAT               | 0 <sup>2</sup>   | 3.45 <sup>3</sup> | 04                                 | 0.9 <sup>2</sup> | μs  |

| Data set-up time                                                                                   | t <sub>SU</sub> ; DAT               | 250 <sup>5</sup> | —                 | 100 <sup>3</sup> , <sup>6</sup>    | —                | ns  |

| Rise time of SDA and SCL signals                                                                   | t <sub>r</sub>                      | _                | 1000              | 20 +0.1C <sub>b</sub> <sup>7</sup> | 300              | ns  |

| Fall time of SDA and SCL signals                                                                   | t <sub>f</sub>                      |                  | 300               | 20 +0.1C <sub>b</sub> <sup>6</sup> | 300              | ns  |

| Set-up time for STOP condition                                                                     | t <sub>SU</sub> ; STO               | 4                | _                 | 0.6                                | _                | μs  |

| Bus free time between STOP and<br>START condition                                                  | t <sub>BUF</sub>                    | 4.7              | —                 | 1.3                                | —                | μs  |

| Pulse width of spikes that must be<br>suppressed by the input filter                               | t <sub>SP</sub>                     | N/A              | N/A               | 0                                  | 50               | ns  |

- 1. The maximum SCL Clock Frequency in Fast mode with maximum bus loading can be achieved only when using the high drive pins across the full voltage range and when using the normal drive pins and VDD ≥ 2.7 V.

- The master mode I<sup>2</sup>C deasserts ACK of an address byte simultaneously with the falling edge of SCL. If no slaves

acknowledge this address byte, then a negative hold time can result, depending on the edge rates of the SDA and

SCL lines.

- 3. The maximum tHD; DAT must be met only if the device does not stretch the LOW period (tLOW) of the SCL signal.

- 4. Input signal Slew = 10 ns and Output Load = 50 pF

- 5. Set-up time in slave-transmitter mode is 1 IPBus clock period, if the TX FIFO is empty.

- 6. A Fast mode I<sup>2</sup>C bus device can be used in a Standard mode I2C bus system, but the requirement t<sub>SU; DAT</sub> ≥ 250 ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, then it must output the next data bit to the SDA line t<sub>rmax</sub> + t<sub>SU; DAT</sub> = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification) before the SCL line is released.

- 7.  $C_b$  = total capacitance of the one bus line in pF.

To achieve 1MHz I2C clock rates, consider the following recommendations:

- To counter the effects of clock stretching, the I2C baud Rate select bits can be configured for faster than desired baud rate.

- Use high drive pad and DSE bit should be set in PORTx\_PCRn register.

- Minimize loading on the I2C SDA and SCL pins to ensure fastest rise times for the SCL line to avoid clock stretching.

- Use smaller pull up resistors on SDA and SCL to reduce the RC time constant.

| Characteristic                                                                               | Symbol                | Minimum                            | Maximum        | Unit |

|----------------------------------------------------------------------------------------------|-----------------------|------------------------------------|----------------|------|

| SCL Clock Frequency                                                                          | f <sub>SCL</sub>      | 0                                  | 1 <sup>1</sup> | MHz  |

| Hold time (repeated) START condition. After this period, the first clock pulse is generated. | t <sub>HD</sub> ; STA | 0.26                               |                | μs   |

| LOW period of the SCL clock                                                                  | t <sub>LOW</sub>      | 0.5                                | —              | μs   |

| HIGH period of the SCL clock                                                                 | t <sub>HIGH</sub>     | 0.26                               | —              | μs   |

| Set-up time for a repeated START condition                                                   | t <sub>SU</sub> ; STA | 0.26                               |                | μs   |

| Data hold time for I <sub>2</sub> C bus devices                                              | t <sub>HD</sub> ; DAT | 0                                  | —              | μs   |

| Data set-up time                                                                             | t <sub>SU</sub> ; DAT | 50                                 |                | ns   |

| Rise time of SDA and SCL signals                                                             | t <sub>r</sub>        | 20 +0.1C <sub>b</sub>              | 120            | ns   |

| Fall time of SDA and SCL signals                                                             | t <sub>f</sub>        | 20 +0.1C <sub>b</sub> <sup>2</sup> | 120            | ns   |

| Set-up time for STOP condition                                                               | t <sub>SU</sub> ; STO | 0.26                               | —              | μs   |

| Bus free time between STOP and START condition                                               | t <sub>BUF</sub>      | 0.5                                |                | μs   |

| Pulse width of spikes that must be suppressed by the input filter                            | t <sub>SP</sub>       | 0                                  | 50             | ns   |

Table 40. 1<sup>2</sup>C 1Mbit/s timing

1. The maximum SCL clock frequency of 1 Mbit/s can support maximum bus loading when using the high drive pins across the full voltage range.

2.  $C_b$  = total capacitance of the one bus line in pF.

Peripheral operating requirements and behaviors

Figure 18. Timing definition for devices on the I<sup>2</sup>C bus

# 3.8.3 UART

See General switching specifications.

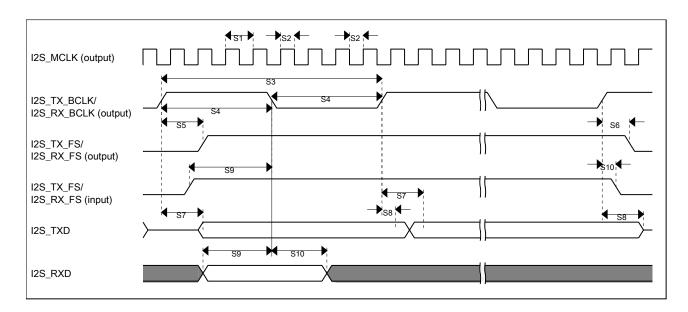

# 3.8.4 I2S/SAI switching specifications

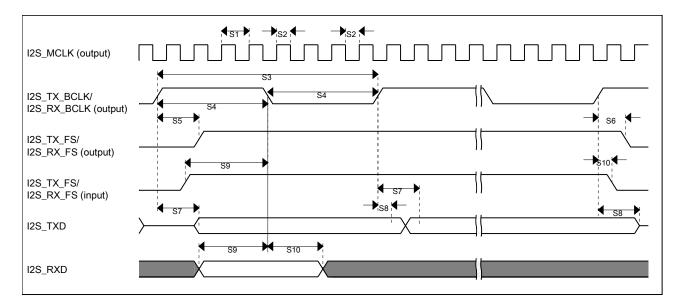

This section provides the AC timing for the I2S/SAI module in master mode (clocks are driven) and slave mode (clocks are input). All timing is given for noninverted serial clock polarity (TCR2[BCP] is 0, RCR2[BCP] is 0) and a noninverted frame sync (TCR4[FSP] is 0, RCR4[FSP] is 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the bit clock signal (BCLK) and/or the frame sync (FS) signal shown in the following figures.

# 3.8.4.1 Normal Run, Wait and Stop mode performance over the full operating voltage range

This section provides the operating performance over the full operating voltage for the device in Normal Run, Wait and Stop modes.

| Num. | Characteristic                                                  | Min. | Max. | Unit        |

|------|-----------------------------------------------------------------|------|------|-------------|

|      | Operating voltage                                               | 1.71 | 3.6  | V           |

| S1   | I2S_MCLK cycle time                                             | 40   | _    | ns          |

| S2   | I2S_MCLK (as an input) pulse width high/low                     | 45%  | 55%  | MCLK period |

| S3   | I2S_TX_BCLK/I2S_RX_BCLK cycle time (output)                     | 80   |      | ns          |

| S4   | I2S_TX_BCLK/I2S_RX_BCLK pulse width high/low                    | 45%  | 55%  | BCLK period |

| S5   | I2S_TX_BCLK/I2S_RX_BCLK to I2S_TX_FS/<br>I2S_RX_FS output valid | -    | 15.5 | ns          |

Table 41. I2S/SAI master mode timing

| Num. | Characteristic                                                    | Min. | Max. | Unit |

|------|-------------------------------------------------------------------|------|------|------|

| S6   | I2S_TX_BCLK/I2S_RX_BCLK to I2S_TX_FS/<br>I2S_RX_FS output invalid | 0    | —    | ns   |

| S7   | I2S_TX_BCLK to I2S_TXD valid                                      | —    | 19   | ns   |

| S8   | I2S_TX_BCLK to I2S_TXD invalid                                    | 0    | —    | ns   |

| S9   | I2S_RXD/I2S_RX_FS input setup before<br>I2S_RX_BCLK               | 26   | —    | ns   |

| S10  | I2S_RXD/I2S_RX_FS input hold after I2S_RX_BCLK                    | 0    | —    | ns   |

|  | Table 41. | I2S/SAI | master | mode | timing | (continued) |

|--|-----------|---------|--------|------|--------|-------------|

|--|-----------|---------|--------|------|--------|-------------|

# Figure 19. I2S/SAI timing — master modes

| Num. | Characteristic                                                    | Min. | Max. | Unit        |

|------|-------------------------------------------------------------------|------|------|-------------|

|      | Operating voltage                                                 | 1.71 | 3.6  | V           |

| S11  | I2S_TX_BCLK/I2S_RX_BCLK cycle time (input)                        | 80   | _    | ns          |

| S12  | I2S_TX_BCLK/I2S_RX_BCLK pulse width high/low (input)              | 45%  | 55%  | MCLK period |

| S13  | I2S_TX_FS/I2S_RX_FS input setup before<br>I2S_TX_BCLK/I2S_RX_BCLK | 10   | -    | ns          |

| S14  | I2S_TX_FS/I2S_RX_FS input hold after<br>I2S_TX_BCLK/I2S_RX_BCLK   | 2    | -    | ns          |

| S15  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output valid                     | —    | 33   | ns          |

| S16  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output invalid                   | 0    | -    | ns          |

| S17  | I2S_RXD setup before I2S_RX_BCLK                                  | 10   | _    | ns          |

## Table 42. I2S/SAI slave mode timing

# Table 43. I2S/SAI master mode timing in VLPR, VLPW, and VLPS modes (full voltage range) (continued)

| Num. | Characteristic                                      | Min. | Max. | Unit |

|------|-----------------------------------------------------|------|------|------|

| S8   | I2S_TX_BCLK to I2S_TXD invalid                      | 0    | —    | ns   |

| S9   | I2S_RXD/I2S_RX_FS input setup before<br>I2S_RX_BCLK |      |      | ns   |

| S10  | I2S_RXD/I2S_RX_FS input hold after I2S_RX_BCLK      | 0    | _    | ns   |

### Figure 21. I2S/SAI timing — master modes

# Table 44. I2S/SAI slave mode timing in VLPR, VLPW, and VLPS modes (full voltage range)

| Num. | Characteristic                                                    | Min. | Max. | Unit        |

|------|-------------------------------------------------------------------|------|------|-------------|

|      | Operating voltage                                                 | 1.71 | 3.6  | V           |

| S11  | I2S_TX_BCLK/I2S_RX_BCLK cycle time (input)                        | 250  | _    | ns          |

| S12  | I2S_TX_BCLK/I2S_RX_BCLK pulse width high/low (input)              | 45%  | 55%  | MCLK period |

| S13  | I2S_TX_FS/I2S_RX_FS input setup before<br>I2S_TX_BCLK/I2S_RX_BCLK | 30   | -    | ns          |

| S14  | I2S_TX_FS/I2S_RX_FS input hold after<br>I2S_TX_BCLK/I2S_RX_BCLK   | 2    | -    | ns          |

| S15  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output valid                     | —    | 87   | ns          |

| S16  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output invalid                   | 0    | -    | ns          |

| S17  | I2S_RXD setup before I2S_RX_BCLK                                  | 30   | —    | ns          |

| S18  | I2S_RXD hold after I2S_RX_BCLK                                    | 2    | —    | ns          |

| S19  | I2S_TX_FS input assertion to I2S_TXD output valid <sup>1</sup>    | —    | 72   | ns          |

| Symbol             | Description                                                                           | Min. | Тур. | Max.                   | Unit                | Notes |

|--------------------|---------------------------------------------------------------------------------------|------|------|------------------------|---------------------|-------|

|                    | • RVTRIM=1110                                                                         | —    | 1.01 | —                      |                     |       |

|                    | • RVTRIM=0001                                                                         | _    | 1.02 | _                      |                     |       |

|                    | • RVTRIM=1001                                                                         | _    | 1.03 | _                      |                     |       |

|                    | • RVTRIM=0101                                                                         | _    | 1.05 | _                      |                     |       |

|                    | • RVTRIM=1101                                                                         | _    | 1.06 | _                      |                     |       |

|                    | • RVTRIM=0011                                                                         | _    | 1.07 | _                      |                     |       |

|                    | • RVTRIM=1011                                                                         | _    | 1.08 | _                      |                     |       |

|                    | • RVTRIM=0111                                                                         | _    | 1.09 | _                      |                     |       |

|                    | • RVTRIM=1111                                                                         |      |      |                        |                     |       |

| Δ <sub>RTRIM</sub> | V <sub>IREG</sub> TRIM resolution                                                     | _    | _    | 3.0                    | % V <sub>IREG</sub> |       |

| I <sub>VIREG</sub> | V <sub>IREG</sub> current adder — RVEN = 1                                            | _    | 1    | —                      | μA                  |       |

| I <sub>RBIAS</sub> | RBIAS current adder                                                                   |      |      |                        |                     |       |

|                    | <ul> <li>LADJ = 10 or 11 — High load (LCD glass<br/>capacitance ≤ 8000 pF)</li> </ul> | _    | 10   | _                      | μA                  |       |

|                    | <ul> <li>LADJ = 00 or 01 — Low load (LCD glass<br/>capacitance ≤ 2000 pF)</li> </ul>  | _    | 1    | _                      | μA                  |       |

| R <sub>RBIAS</sub> | RBIAS resistor values                                                                 |      |      |                        |                     |       |

|                    | <ul> <li>LADJ = 10 or 11 — High load (LCD glass<br/>capacitance ≤ 8000 pF)</li> </ul> | _    | 0.28 | _                      | MΩ                  |       |

|                    | <ul> <li>LADJ = 00 or 01 — Low load (LCD glass<br/>capacitance ≤ 2000 pF)</li> </ul>  | _    | 2.98 | _                      | ΜΩ                  |       |

| VLL1               | VLL1 voltage                                                                          | _    | _    | V <sub>IREG</sub>      | V                   | 4     |

| VLL2               | VLL2 voltage                                                                          | —    | —    | 2 x V <sub>IREG</sub>  | V                   | 4     |

| VLL3               | VLL3 voltage                                                                          | —    | —    | 3 x V <sub>IREG</sub>  | V                   | 4     |

| VLL1               | VLL1 voltage                                                                          | —    | _    | V <sub>DDA</sub> / 3   | V                   | 5     |

| VLL2               | VLL2 voltage                                                                          | —    |      | V <sub>DDA</sub> / 1.5 | V                   | 5     |

| VLL3               | VLL3 voltage                                                                          | —    | —    | V <sub>DDA</sub>       | V                   | 5     |

| Table 45. L | CD electricals | (continued) |

|-------------|----------------|-------------|

|-------------|----------------|-------------|

1. The actual value used could vary with tolerance.

- For highest glass capacitance values, LCD\_GCR[LADJ] should be configured as specified in the LCD Controller chapter within the device's reference manual.

- 3. V<sub>IREG</sub> maximum should never be externally driven to any level other than V<sub>DD</sub> 0.15 V

- VLL1, VLL2 and VLL3 are a function of V<sub>IREG</sub> only when the regulator is enabled (GCR[RVEN]=1) and the charge pump is enabled (GCR[CPSEL]=1).

- 5. VLL1, VLL2 and VLL3 are a function of  $V_{DDA}$  only under either of the following conditions:

- The charge pump is enabled (GCR[CPSEL]=1), the regulator is disabled (GCR[RVEN]=0), and VLL3 = V<sub>DDA</sub> through the internal power switch (GCR[VSUPPLY]=0).

- The resistor bias string is enabled (GCR[CPSEL]=0), the regulator is disabled (GCR[RVEN]=0), and VLL3 is connected to V<sub>DDA</sub> externally (GCR[VSUPPLY]=1).

| 64<br>LQFP | 64<br>MAP<br>BGA | Pin Name          | Default               | ALT0                  | ALT1              | ALT2      | ALT3       | ALT4     | ALT5      | ALT6     | ALT7    |

|------------|------------------|-------------------|-----------------------|-----------------------|-------------------|-----------|------------|----------|-----------|----------|---------|

| 58         | A4               | PTD1              | LCD_P41/<br>ADC0_SE5b | LCD_P41/<br>ADC0_SE5b | PTD1              | SPI0_SCK  |            | TPM0_CH1 |           | FXIO0_D1 | LCD_P41 |

| 59         | C2               | PTD2              | LCD_P42               | LCD_P42               | PTD2              | SPI0_MOSI | UART2_RX   | TPM0_CH2 | SPI0_MISO | FXIO0_D2 | LCD_P42 |

| 60         | B3               | PTD3              | LCD_P43               | LCD_P43               | PTD3              | SPI0_MISO | UART2_TX   | TPM0_CH3 | SPI0_MOSI | FXIO0_D3 | LCD_P43 |

| 61         | A3               | PTD4/<br>LLWU_P14 | LCD_P44               | LCD_P44               | PTD4/<br>LLWU_P14 | SPI1_SS   | UART2_RX   | TPM0_CH4 |           | FXI00_D4 | LCD_P44 |

| 62         | C1               | PTD5              | LCD_P45/<br>ADC0_SE6b | LCD_P45/<br>ADC0_SE6b | PTD5              | SPI1_SCK  | UART2_TX   | TPM0_CH5 |           | FXIO0_D5 | LCD_P45 |

| 63         | B2               | PTD6/<br>LLWU_P15 | LCD_P46/<br>ADC0_SE7b | LCD_P46/<br>ADC0_SE7b | PTD6/<br>LLWU_P15 | SPI1_MOSI | LPUART0_RX |          | SPI1_MISO | FXIO0_D6 | LCD_P46 |

| 64         | A2               | PTD7              | LCD_P47               | LCD_P47               | PTD7              | SPI1_MISO | LPUART0_TX |          | SPI1_MOSI | FXIO0_D7 | LCD_P47 |

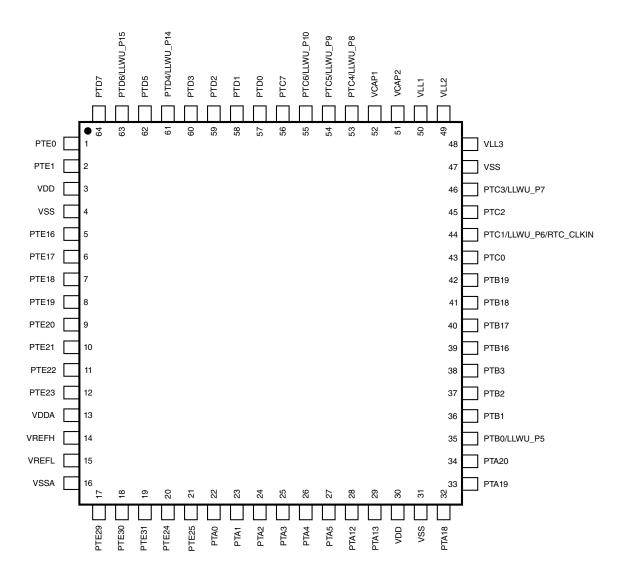

# 5.2 KL33 Family Pinouts

Figure below shows the 64 LQFP pinouts:

Figure below shows the 64 MAPBGA pinouts:

# 8 Terminology and guidelines

# 8.1 Definitions

Key terms are defined in the following table:

| Term                  | Definition                                                                                                                                                                                                                          |  |  |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Rating                | A minimum or maximum value of a technical characteristic that, if exceeded, may cause permanent chip failure:                                                                                                                       |  |  |  |  |  |

|                       | <ul> <li>Operating ratings apply during operation of the chip.</li> <li>Handling ratings apply when the chip is not powered.</li> </ul>                                                                                             |  |  |  |  |  |

|                       | <b>NOTE:</b> The likelihood of permanent chip failure increases rapidly as soon as a characteristic begins to exceed one of its operating ratings.                                                                                  |  |  |  |  |  |

| Operating requirement | A specified value or range of values for a technical characteristic that you must guarantee durin operation to avoid incorrect operation and possibly decreasing the useful life of the chip                                        |  |  |  |  |  |

| Operating behavior    | A specified value or range of values for a technical characteristic that are guaranteed during operation if you meet the operating requirements and any other specified conditions                                                  |  |  |  |  |  |

| Typical value         | A specified value for a technical characteristic that:                                                                                                                                                                              |  |  |  |  |  |

|                       | <ul> <li>Lies within the range of values specified by the operating behavior</li> <li>Is representative of that characteristic during operation when you meet the typical-value conditions or other specified conditions</li> </ul> |  |  |  |  |  |

|                       | <b>NOTE:</b> Typical values are provided as design guidelines and are neither tested nor guaranteed.                                                                                                                                |  |  |  |  |  |

Terminology and guidelines

#### Examples 8.2

### Operating rating:

| Symbol          | Description                  | Min.    | Max. | Unit |  |  |

|-----------------|------------------------------|---------|------|------|--|--|

| V <sub>DD</sub> | 1.0 V core supply<br>voltage | -0.3 AM | 1.2  | V    |  |  |

|                 | ·                            |         |      |      |  |  |

## Operating requirement:

| Operating requi | rement:                      | . 4  | •    |      |

|-----------------|------------------------------|------|------|------|

| Symbol          | Description                  | Min. | Max. | Unit |

| V <sub>DD</sub> | 1.0 V core supply<br>voltage | 0.9  | 1.1  | V    |

|                 |                              |      |      |      |

### Operating behavior that includes a typical value:

| Symbol | Description                                    | Min.  | Тур. | Max. | Unit |

|--------|------------------------------------------------|-------|------|------|------|

| Iwp    | Digital I/O weak<br>pullup/pulldown<br>current | 10 AM | 70   | 130  | μA   |

#### **Typical-value conditions** 8.3

Typical values assume you meet the following conditions (or other conditions as specified):

| Symbol          | Description          | Value | Unit |

|-----------------|----------------------|-------|------|

| T <sub>A</sub>  | Ambient temperature  | 25    | C°   |

| V <sub>DD</sub> | 3.3 V supply voltage | 3.3   | V    |

### How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. Freescale reserves the right to make changes without further notice to any products herein.

Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Freescale, the Freescale logo, Energy Efficient Solutions logo, and Kinetis are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. All other product or service names are the property of their respective owners. ARM and Cortex are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved.

©2014-2015 Freescale Semiconductor, Inc.

Document Number KL33P64M48SF6 Revision 5, 08/2015