Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | XC800                                                                           |

| Core Size                  | 8-Bit                                                                           |

| Speed                      | 24MHz                                                                           |

| Connectivity               | SSI, UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 34                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1.75K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 140°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 48-LQFP                                                                         |

| Supplier Device Package    | PG-TQFP-48                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saa-xc886-8ffa-5v-ac |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2 General Device Information

**Chapter 2** contains the block diagram, pin configurations, definitions and functions of the SAA-XC886.

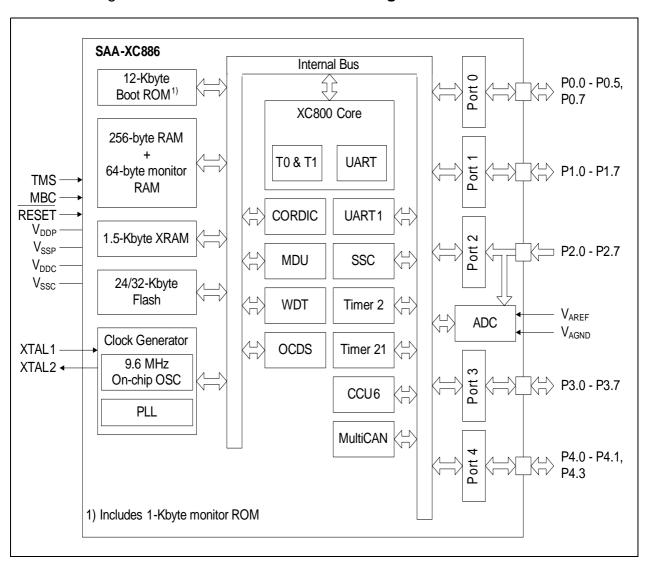

# 2.1 Block Diagram

The block diagram of the SAA-XC886 is shown in Figure 2.

Figure 2 SAA-XC886 Block Diagram

Table 2Pin Definitions and Functions (cont'd)

| Symbol | Pin Number | Туре | Reset<br>State | Function                                       |                                                                                                                                            |

|--------|------------|------|----------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| P1     |            | I/O  |                | I/O port. It ca<br>for the JTAG                | B-bit bidirectional general purpose an be used as alternate functions i, CCU6, UART, Timer 0, Timer 1, per 21, MultiCAN and SSC.           |

| P1.0   | 26         |      | PU             | RXD_0<br>T2EX<br>RXDC0_0                       | UART Receive Data Input<br>Timer 2 External Trigger Input<br>MultiCAN Node 0 Receiver Input                                                |

| P1.1   | 27         |      | PU             | EXINT3<br>T0_1<br>TDO_1<br>TXD_0<br>TXDC0_0    | External Interrupt Input 3 Timer 0 Input JTAG Serial Data Output UART Transmit Data Output/Clock Output MultiCAN Node 0 Transmitter Output |

| P1.2   | 28         |      | PU             | SCK_0                                          | SSC Clock Input/Output                                                                                                                     |

| P1.3   | 29         |      | PU             | MTSR_0 TXDC1_3                                 | SSC Master Transmit Output/Slave Receive Input MultiCAN Node 1 Transmitter Output                                                          |

| P1.4   | 30         |      | PU             | MRST_0 EXINT0_1 RXDC1_3                        | SSC Master Receive Input/<br>Slave Transmit Output<br>External Interrupt Input 0<br>MultiCAN Node 1 Receiver Input                         |

| P1.5   | 31         |      | PU             | CCPOS0_1<br>EXINT5<br>T1_1<br>EXF2_0<br>RXDO_0 | CCU6 Hall Input 0 External Interrupt Input 5 Timer 1 Input Timer 2 External Flag Output UART Transmit Data Output                          |

Table 2

Pin Definitions and Functions (cont'd)

| Symbol | Pin Number | Туре | Reset<br>State | Function                               |                                                                                              |

|--------|------------|------|----------------|----------------------------------------|----------------------------------------------------------------------------------------------|

| P1.6   | 8          |      | PU             | CCPOS1_1<br>T12HR_0                    | CCU6 Hall Input 1<br>CCU6 Timer 12 Hardware Run<br>Input                                     |

|        |            |      |                | EXINT6_0<br>RXDC0_2<br>T21_1           | External Interrupt Input 6 MultiCAN Node 0 Receiver Input Timer 21 Input                     |

| P1.7   | 9          |      | PU             | CCPOS2_1<br>T13HR_0<br>T2_1<br>TXDC0_2 | CCU6 Hall Input 2 CCU6 Timer 13 Hardware Run Input Timer 2 Input MultiCAN Node 0 Transmitter |

|        |            |      |                |                                        | Output  .6 can be used as a software chip  : for the SSC.                                    |

Table 2

Pin Definitions and Functions (cont'd)

| Symbol | Pin Number | Туре | Reset<br>State | Function           |                                                                |

|--------|------------|------|----------------|--------------------|----------------------------------------------------------------|

| P3.7   | 34         |      |                | EXINT4<br>COUT63_0 | External Interrupt Input 4 Output of Capture/Compare channel 3 |

Data Sheet 13 V1.1, 2010-08

# 3 Functional Description

Chapter 3 provides an overview of the SAA-XC886 functional description.

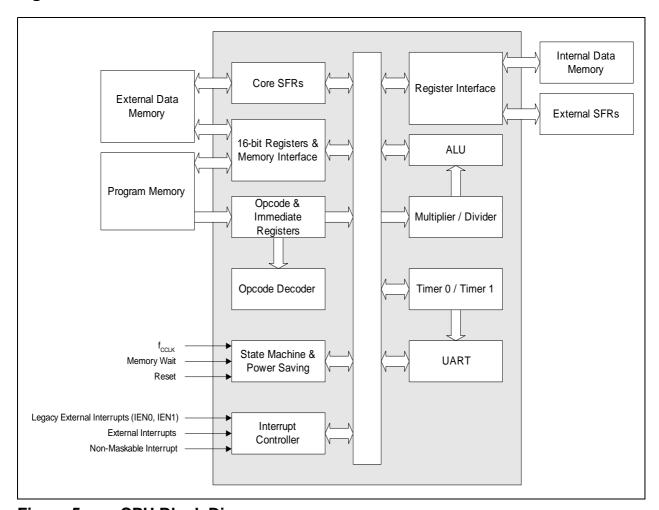

#### 3.1 Processor Architecture

The SAA-XC886 is based on a high-performance 8-bit Central Processing Unit (CPU) that is compatible with the standard 8051 processor. While the standard 8051 processor is designed around a 12-clock machine cycle, the SAA-XC886 CPU uses a 2-clock machine cycle. This allows fast access to ROM or RAM memories without wait state. Access to the Flash memory, however, requires an additional wait state (one machine cycle). The instruction set consists of 45% one-byte, 41% two-byte and 14% three-byte instructions.

The SAA-XC886 CPU provides a range of debugging features, including basic stop/start, single-step execution, breakpoint support and read/write access to the data memory, program memory and Special Function Registers (SFRs).

Figure 5 shows the CPU functional blocks.

Figure 5 CPU Block Diagram

Table 7

SCU Register Overview (cont'd)

| Addr            | Register Name                                                        | Bit       | 7             | 6 | 5           | 4               | 3          | 2           | 1             | 0             |

|-----------------|----------------------------------------------------------------------|-----------|---------------|---|-------------|-----------------|------------|-------------|---------------|---------------|

| BE <sub>H</sub> | COCON Reset: 00 <sub>H</sub><br>Clock Output Control Register        | Bit Field | 0 TLEN COUT S |   |             |                 |            | COI         | REL           |               |

|                 |                                                                      | Туре      |               | r | rw          | rw              |            | r           | W             |               |

| E9 <sub>H</sub> | MISC_CON Reset: 00 <sub>H</sub> Miscellaneous Control Register       | Bit Field |               |   |             | 0               |            |             |               | DFLAS<br>HEN  |

|                 |                                                                      | Type      |               |   |             | r               |            |             |               | rwh           |

| RMAP =          | = 0, PAGE 3                                                          |           |               |   |             |                 |            |             |               |               |

| вз <sub>Н</sub> | XADDRH Reset: F0H                                                    | Bit Field |               |   |             | ADI             | DRH        |             |               |               |

|                 | On-chip XRAM Address Higher Order                                    | Туре      |               |   |             | r               | W          |             |               |               |

| B4 <sub>H</sub> | IRCON3 Reset: 00 <sub>H</sub> Interrupt Request Register 3           | Bit Field |               | 0 | CANS<br>RC5 | CCU6<br>SR1     | (          | 0           | CANS<br>RC4   | CCU6<br>SR0   |

|                 |                                                                      | Туре      |               | r | rwh         | rwh             |            | r           | rwh           | rwh           |

| в5 <sub>Н</sub> | IRCON4 Reset: 00 <sub>H</sub> Interrupt Request Register 4           | Bit Field |               | 0 | CANS<br>RC7 | CCU6<br>SR3     | (          | 0           | CANS<br>RC6   | CCU6<br>SR2   |

|                 |                                                                      | Туре      |               | r | rwh         | rwh             |            | r           | rwh           | rwh           |

| В7 <sub>Н</sub> | MODPISEL1 Reset: 00 <sub>H</sub><br>Peripheral Input Select Register | Bit Field | EXINT<br>6IS  |   | 0           | UR <sup>2</sup> | RIS        | T21EX<br>IS | JTAGT<br>DIS1 | JTAGT<br>CKS1 |

|                 | 1                                                                    | Туре      | rw            |   | r           | r               | W          | rw          | rw            | rw            |

| ва <sub>Н</sub> | MODPISEL2 Reset: 00 <sub>H</sub>                                     | Bit Field |               | ( | 0           |                 | T21IS      | T2IS        | T1IS          | TOIS          |

|                 | Peripheral Input Select Register 2                                   | Туре      |               |   | r           |                 | rw         | rw          | rw            | rw            |

| ввн             | PMCON2 Reset: 00 <sub>H</sub><br>Power Mode Control Register 2       | Bit Field |               |   | (           | 0               |            |             | UART<br>1_DIS | T21_D<br>IS   |

|                 |                                                                      | Туре      |               |   |             | r               |            |             | rw            | rw            |

| BD <sub>H</sub> | MODSUSP Reset: 01 <sub>H</sub> Module Suspend Control                | Bit Field |               | 0 |             | T21SU<br>SP     | T2SUS<br>P | T13SU<br>SP | T12SU<br>SP   | WDTS<br>USP   |

|                 | Register                                                             | Туре      |               | r |             | rw              | rw         | rw          | rw            | rw            |

# 3.2.4.5 WDT Registers

The WDT SFRs can be accessed in the mapped memory area (RMAP = 1).

Table 8 WDT Register Overview

| Addr            | Register Name                                        | Bit       | 7 | 6 | 5          | 4         | 3    | 2         | 1         | 0         |

|-----------------|------------------------------------------------------|-----------|---|---|------------|-----------|------|-----------|-----------|-----------|

| RMAP =          | : 1                                                  |           |   |   |            |           |      |           |           |           |

| ввН             | WDTCON Reset: 00 <sub>H</sub> Watchdog Timer Control | Bit Field | ( | ) | WINB<br>EN | WDTP<br>R | 0    | WDTE<br>N | WDTR<br>S | WDTI<br>N |

|                 | Register                                             | Туре      |   | r | rw         | rh        | r    | rw        | rwh       | rw        |

| всн             | WDTREL Reset: 00 <sub>H</sub>                        | Bit Field |   |   |            | WDT       | REL  |           |           |           |

|                 | Watchdog Timer Reload<br>Register                    | Туре      |   |   |            | r         | w    |           |           |           |

| вD <sub>Н</sub> | WDTWINB Reset: 00 <sub>H</sub>                       | Bit Field |   |   |            | WDT       | WINB |           |           |           |

|                 | Watchdog Window-Boundary Count Register              | Туре      |   |   |            | r         | w    | •         | •         |           |

Table 10

ADC Register Overview (cont'd)

| Addr            | Register Name                                             | Bit       | 7          | 6          | 5      | 4              | 3      | 2  | 1       | 0    |  |  |  |

|-----------------|-----------------------------------------------------------|-----------|------------|------------|--------|----------------|--------|----|---------|------|--|--|--|

| CDH             | ADC_LCBR Reset: B7H                                       | Bit Field |            | BOL        | JND1   |                | BOUND0 |    |         |      |  |  |  |

|                 | Limit Check Boundary Register                             | Туре      |            | r          | w      |                |        | rw |         |      |  |  |  |

| CEH             | ADC_INPCR0 Reset: 00H                                     | Bit Field |            |            |        | S <sup>-</sup> | тс     |    |         |      |  |  |  |

|                 | Input Class 0 Register                                    | Туре      |            |            |        | r              | W      |    |         |      |  |  |  |

| CF <sub>H</sub> | ADC_ETRCR Reset: 00 <sub>H</sub> External Trigger Control | Bit Field | SYNE<br>N1 | SYNE<br>N0 |        | ETRSEL1        | l      |    | ETRSELO | )    |  |  |  |

|                 | Register                                                  | Туре      | rw         | rw         |        | rw             |        |    | rw      |      |  |  |  |

| RMAP =          | = 0, PAGE 1                                               |           |            |            |        |                |        |    |         |      |  |  |  |

| CAH             | ADC_CHCTR0 Reset: 00H                                     | Bit Field | 0          |            | LCC    |                | (      | )  | RESI    | RSEL |  |  |  |

|                 | Channel Control Register 0                                | Type      | r          |            | rw     |                | I      | r  | r       | w    |  |  |  |

| СВН             | ADC_CHCTR1 Reset: 00H                                     | Bit Field | 0          |            | LCC    |                | (      | )  | RESI    | RSEL |  |  |  |

|                 | Channel Control Register 1                                | Туре      | r          |            | rw     |                |        | r  | r       | W    |  |  |  |

| CCH             | ADC_CHCTR2 Reset: 00 <sub>H</sub>                         | Bit Field | 0          |            | LCC    |                | (      | )  | RESI    | RSEL |  |  |  |

|                 | Channel Control Register 2                                | Туре      | r          |            | rw     |                |        | r  | r       | W    |  |  |  |

| CDH             | ADC_CHCTR3 Reset: 00H                                     | Bit Field | 0          |            | LCC    |                | (      | )  | RESI    | RSEL |  |  |  |

|                 | Channel Control Register 3                                | Туре      | r          |            | rw     |                | 1      | r  | r       | W    |  |  |  |

| CEH             | ADC_CHCTR4 Reset: 00H                                     | Bit Field | 0          |            | LCC    |                | (      | )  | RESI    | RSEL |  |  |  |

|                 | Channel Control Register 4                                | Туре      | r          |            | rw     |                | 1      | r  | r       | W    |  |  |  |

| CF <sub>H</sub> | ADC_CHCTR5 Reset: 00H                                     | Bit Field | 0          |            | LCC    |                | (      | )  | RESI    | RSEL |  |  |  |

|                 | Channel Control Register 5                                | Туре      | r          |            | rw     |                | 1      | r  | r       | W    |  |  |  |

| D2 <sub>H</sub> | ADC_CHCTR6 Reset: 00H                                     | Bit Field | 0          |            | LCC    |                | (      | )  | RESI    | RSEL |  |  |  |

|                 | Channel Control Register 6                                | Туре      | r          |            | rw     |                | 1      | r  | r       | W    |  |  |  |

| D3 <sub>H</sub> | ADC_CHCTR7 Reset: 00H                                     | Bit Field | 0          |            | LCC    |                | (      | )  | RESI    | RSEL |  |  |  |

|                 | Channel Control Register 7                                | Туре      | r          |            | rw     |                |        | r  | r       | W    |  |  |  |

| RMAP =          | = 0, PAGE 2                                               |           |            |            |        |                |        |    |         |      |  |  |  |

| CAH             | ADC_RESROL Reset: 00H                                     | Bit Field | RES        | SULT       | 0      | VF             | DRC    |    | CHNR    |      |  |  |  |

|                 | Result Register 0 Low                                     | Туре      | r          | h          | r      | rh             | rh     |    | rh      |      |  |  |  |

| СВН             | ADC_RESR0H Reset: 00H                                     | Bit Field |            |            | •      | RES            | SULT   |    |         |      |  |  |  |

|                 | Result Register 0 High                                    | Туре      |            |            |        | r              | h      |    |         |      |  |  |  |

| CCH             | ADC_RESR1L Reset: 00H                                     | Bit Field | RES        | SULT       | 0      | VF             | DRC    |    | CHNR    |      |  |  |  |

|                 | Result Register 1 Low                                     | Туре      | r          | h          | r      | rh             | rh     |    | rh      |      |  |  |  |

| CDH             | ADC_RESR1H Reset: 00H                                     | Bit Field |            |            |        | RES            | SULT   |    |         |      |  |  |  |

| -               | Result Register 1 High                                    | Туре      |            |            |        | rh             |        |    |         |      |  |  |  |

| CEH             | ADC_RESR2L Reset: 00H                                     | Bit Field | RES        | SULT       | 0      | VF DRC         |        |    | CHNR    |      |  |  |  |

|                 | Result Register 2 Low                                     | Туре      | r          | h          |        |                |        |    | rh      |      |  |  |  |

| CF <sub>H</sub> | ADC_RESR2H Reset: 00H                                     | Bit Field |            |            | RESULT |                |        |    |         |      |  |  |  |

|                 | Result Register 2 High                                    | Туре      |            |            |        | r              | h      |    |         |      |  |  |  |

| D2 <sub>H</sub> | ADC_RESR3L Reset: 00H                                     | Bit Field | RES        | SULT       | 0      | VF             | DRC    |    | CHNR    |      |  |  |  |

|                 | Result Register 3 Low                                     | Туре      | r          | h          | r      | rh             | rh     |    | rh      |      |  |  |  |

Table 10

ADC Register Overview (cont'd)

| Addr            | Register Name                                                        | Bit       | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |

|-----------------|----------------------------------------------------------------------|-----------|------------|------------|------------|------------|------------|------------|------------|------------|

| D3 <sub>H</sub> | ADC_RESR3H Reset: 00H                                                | Bit Field |            | ·          | ·          | RES        | ULT        | l          | l .        | l          |

|                 | Result Register 3 High                                               | Туре      |            |            |            | r          | h          |            |            |            |

| RMAP =          | = 0, PAGE 3                                                          |           | I          |            |            |            |            |            |            |            |

| CAH             | ADC_RESRA0L Reset: 00H                                               | Bit Field |            | RESULT     |            | VF         | DRC        |            | CHNR       |            |

|                 | Result Register 0, View A Low                                        | Туре      |            | rh         |            | rh         | rh         |            | rh         |            |

| СВН             | ADC_RESRA0H Reset: 00H                                               | Bit Field |            |            |            | RES        | ULT        | l.         |            |            |

|                 | Result Register 0, View A High                                       | Туре      |            |            |            | r          | h          |            |            |            |

| ccH             | ADC_RESRA1L Reset: 00H                                               | Bit Field |            | RESULT     |            | VF         | DRC        |            | CHNR       |            |

|                 | Result Register 1, View A Low                                        | Туре      |            | rh         |            | rh         | rh         |            | rh         |            |

| CDH             | ADC_RESRA1H Reset: 00H                                               | Bit Field |            |            |            | RES        | ULT        |            |            |            |

|                 | Result Register 1, View A High                                       | Туре      |            |            |            | r          | h          |            |            |            |

| CEH             | ADC_RESRA2L Reset: 00H                                               | Bit Field |            | RESULT     |            | VF         | DRC        |            | CHNR       |            |

|                 | Result Register 2, View A Low                                        | Туре      |            | rh         |            | rh         | rh         |            | rh         |            |

| CF <sub>H</sub> | ADC_RESRA2H Reset: 00H                                               | Bit Field |            |            |            | RES        | ULT        |            |            |            |

|                 | Result Register 2, View A High                                       | Туре      |            |            |            | r          | h          |            |            |            |

| D2 <sub>H</sub> | ADC_RESRA3L Reset: 00H                                               | Bit Field |            | RESULT     |            | VF         | DRC        |            | CHNR       |            |

|                 | Result Register 3, View A Low                                        | Туре      |            | rh         |            | rh         | rh         |            | rh         |            |

| D3 <sub>H</sub> | ADC_RESRA3H Reset: 00H                                               | Bit Field |            |            |            | RES        | ULT        |            |            |            |

|                 | Result Register 3, View A High                                       | Туре      |            |            |            | r          | h          |            |            |            |

| RMAP =          | = 0, PAGE 4                                                          |           |            |            |            |            |            |            |            |            |

| CAH             | ADC_RCR0 Reset: 00 <sub>H</sub> Result Control Register 0            | Bit Field | VFCT<br>R  | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |

|                 |                                                                      | Туре      | rw         | rw         | r          | rw         |            | r          |            | rw         |

| СВН             | ADC_RCR1 Reset: 00 <sub>H</sub> Result Control Register 1            | Bit Field | VFCT<br>R  | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |

|                 |                                                                      | Туре      | rw         | rw         | r          | rw         |            | r          |            | rw         |

| CCH             | ADC_RCR2 Reset: 00 <sub>H</sub> Result Control Register 2            | Bit Field | VFCT<br>R  | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |

|                 |                                                                      | Туре      | rw         | rw         | r          | rw         |            | r          |            | rw         |

| CDH             | ADC_RCR3 Reset: 00 <sub>H</sub> Result Control Register 3            | Bit Field | VFCT<br>R  | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |

|                 |                                                                      | Type      | rw         | rw         | r          | rw         |            | r          |            | rw         |

| CEH             | ADC_VFCR Reset: 00H                                                  | Bit Field |            | (          | 0          |            | VFC3       | VFC2       | VFC1       | VFC0       |

|                 | Valid Flag Clear Register                                            | Туре      |            |            | r          |            | W          | W          | W          | W          |

| RMAP =          | = 0, PAGE 5                                                          |           |            |            |            |            |            |            |            |            |

| CA <sub>H</sub> | ADC_CHINFR Reset: 00 <sub>H</sub><br>Channel Interrupt Flag Register | Bit Field | CHINF<br>7 | CHINF<br>6 | CHINF<br>5 | CHINF<br>4 | CHINF<br>3 | CHINF<br>2 | CHINF<br>1 | CHINF<br>0 |

|                 |                                                                      | Туре      | rh         |

| СВН             | ADC_CHINCR Reset: 00 <sub>H</sub> Channel Interrupt Clear Register   | Bit Field | CHINC<br>7 | CHINC<br>6 | CHINC<br>5 | CHINC<br>4 | CHINC<br>3 | CHINC<br>2 | CHINC<br>1 | CHINC<br>0 |

|                 | -                                                                    |           |            |            |            |            |            |            |            |            |

Table 12 T21 Register Overview (cont'd)

| Addr            | Register Name                  | Bit       | 7 | 6 | 5 | 4  | 3   | 2 | 1 | 0 |

|-----------------|--------------------------------|-----------|---|---|---|----|-----|---|---|---|

| C5 <sub>H</sub> | T21_T2H Reset: 00 <sub>H</sub> | Bit Field |   |   |   | T⊦ | IL2 |   |   |   |

|                 | Timer 2 Register High          | Туре      |   |   |   | rv | vh  |   |   |   |

# 3.2.4.10 CCU6 Registers

The CCU6 SFRs can be accessed in the standard memory area (RMAP = 0).

Table 13 CCU6 Register Overview

| Addr            | Register Name                                                             | Bit       | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |  |

|-----------------|---------------------------------------------------------------------------|-----------|------------|------------|------------|------------|------------|------------|------------|------------|--|

| RMAP =          | = 0                                                                       | I         | I          |            | I          | I          | I          | I          | I          | I          |  |

| A3 <sub>H</sub> | CCU6_PAGE Reset: 00H                                                      | Bit Field | C          | )P         | ST         | NR         | 0          |            | PAGE       |            |  |

|                 | Page Register                                                             | Туре      | \          | N          | ١          | V          | r          |            | rw         |            |  |

| RMAP =          | = 0, PAGE 0                                                               |           |            |            |            |            |            |            |            |            |  |

| 9A <sub>H</sub> | CCU6_CC63SRL Reset: 00H                                                   | Bit Field |            |            |            | CC6        | 3SL        |            |            |            |  |

|                 | Capture/Compare Shadow Register for Channel CC63 Low                      | Туре      |            |            |            | r          | W          |            |            |            |  |

| 9B <sub>H</sub> | CCU6_CC63SRH Reset: 00 <sub>H</sub>                                       | Bit Field |            |            |            | CC6        | 3SH        |            |            |            |  |

|                 | Capture/Compare Shadow Register for Channel CC63 High                     | Туре      |            |            |            | r          | W          |            |            |            |  |

| 9C <sub>H</sub> | CCU6_TCTR4L Reset: 00 <sub>H</sub> Timer Control Register 4 Low           | Bit Field | T12<br>STD | T12<br>STR | (          | )          | DT<br>RES  | T12<br>RES | T12R<br>S  | T12R<br>R  |  |

|                 |                                                                           | Туре      | W          | W          |            | r          | W          | W          | W          | W          |  |

| 9D <sub>H</sub> | CCU6_TCTR4H Reset: 00 <sub>H</sub> Timer Control Register 4 High          | Bit Field | T13<br>STD | T13<br>STR |            | 0          |            | T13<br>RES | T13R<br>S  | T13R<br>R  |  |

|                 |                                                                           | Туре      | w          | w          |            | r          |            | W          | w          | W          |  |

| 9E <sub>H</sub> | CCU6_MCMOUTSL Reset: 00 <sub>H</sub> Multi-Channel Mode Output Shadow     | Bit Field | STRM<br>CM | 0          |            |            | MCI        | MPS        |            |            |  |

|                 | Register Low                                                              | Туре      | W          | r          |            |            | r          | w          |            |            |  |

| 9F <sub>H</sub> | CCU6_MCMOUTSH Reset: 00 <sub>H</sub> Multi-Channel Mode Output Shadow     | Bit Field | STRH<br>P  | 0          |            | CURHS      |            |            | EXPHS      |            |  |

|                 | Register High                                                             | Туре      | W          | r          |            | rw         |            |            | rw         |            |  |

| <sup>A4</sup> H | CCU6_ISRL Reset: 00 <sub>H</sub> Capture/Compare Interrupt Status         | Bit Field | RT12<br>PM | RT12<br>OM | RCC6<br>2F | RCC6<br>2R | RCC6<br>1F | RCC6<br>1R | RCC6<br>0F | RCC6<br>0R |  |

|                 | Reset Register Low                                                        | Туре      | W          | W          | W          | W          | W          | W          | W          | w          |  |

| A5 <sub>H</sub> | CCU6_ISRH Reset: 00 <sub>H</sub> Capture/Compare Interrupt Status         | Bit Field | RSTR       | RIDLE      | RWH<br>E   | RCHE       | 0          | RTRP<br>F  | RT13<br>PM | RT13<br>CM |  |

|                 | Reset Register High                                                       | Type      | w          | w          | W          | W          | r          | W          | W          | W          |  |

| A6 <sub>H</sub> | CCU6_CMPMODIFL Reset: 00 <sub>H</sub> Compare State Modification Register | Bit Field | 0          | MCC6<br>3S |            | 0          |            | MCC6<br>2S | MCC6<br>1S | MCC6<br>0S |  |

|                 | Low                                                                       | Туре      | r          | W          |            | r          |            | W          | w          | w          |  |

| A7 <sub>H</sub> | CCU6_CMPMODIFH Reset: 00 <sub>H</sub> Compare State Modification Register | Bit Field | 0          | MCC6<br>3R |            | 0          |            | MCC6<br>2R | MCC6<br>1R | MCC6<br>0R |  |

|                 | High                                                                      | Туре      | r          | w          |            | r          |            | w          | w          | w          |  |

# Table 13 CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                      | Bit                | 7                               | 6    | 5    | 4    | 3          | 2    | 1      | 0    |

|-----------------|--------------------------------------------------------------------|--------------------|---------------------------------|------|------|------|------------|------|--------|------|

| FA <sub>H</sub> | CCU6_CC60SRL Reset: 00 <sub>H</sub>                                | Bit Field          | CC60SL                          |      |      |      |            |      |        |      |

|                 | Capture/Compare Shadow Register for Channel CC60 Low               | Туре               |                                 |      |      | rv   | /h         |      |        |      |

| FB <sub>H</sub> | CCU6_CC60SRH Reset: 00H                                            | Bit Field          |                                 |      |      | CC6  | 0SH        |      |        |      |

|                 | Capture/Compare Shadow Register for Channel CC60 High              | Туре               |                                 |      |      | rv   | /h         |      |        |      |

| FC <sub>H</sub> | CCU6_CC61SRL Reset: 00H                                            | Bit Field          |                                 |      |      | CC6  | 1SL        |      |        |      |

|                 | Capture/Compare Shadow Register for Channel CC61 Low               | Туре               |                                 |      |      | rv   | /h         |      |        |      |

| FD <sub>H</sub> | CCU6_CC61SRH Reset: 00H                                            | Bit Field          |                                 |      |      | CC6  | 1SH        |      |        |      |

|                 | Capture/Compare Shadow Register for Channel CC61 High              | Туре               |                                 |      |      | rv   | /h         |      |        |      |

| FE <sub>H</sub> | CCU6_CC62SRL Reset: 00H                                            | Bit Field          |                                 |      |      | CC6  | 2SL        |      |        |      |

|                 | Capture/Compare Shadow Register for Channel CC62 Low               | Туре               |                                 |      |      | rv   | /h         |      |        |      |

| FF <sub>H</sub> | CCU6_CC62SRH Reset: 00H                                            | Bit Field          |                                 |      |      | CC6  | 2SH        |      |        |      |

|                 | Capture/Compare Shadow Register for Channel CC62 High              | Туре               |                                 |      |      | rv   | /h         |      |        |      |

| RMAP =          | = 0, PAGE 1                                                        |                    |                                 |      |      |      |            |      |        |      |

| <sup>9A</sup> H | CCU6_CC63RL Reset: 00 <sub>H</sub> Capture/Compare Register for    | Bit Field          |                                 |      |      | CC6  | 3VL        |      |        |      |

|                 | Channel CC63 Low                                                   | Туре               |                                 |      |      | r    | h          |      |        |      |

| 9B <sub>H</sub> | CCU6_CC63RH Reset: 00H                                             | Bit Field          |                                 |      |      | CC6  | 3VH        |      |        |      |

|                 | Capture/Compare Register for Channel CC63 High                     | Туре               |                                 |      |      | r    | h          |      |        |      |

| 9CH             | CCU6_T12PRL Reset: 00H                                             | Bit Field          |                                 |      |      | T12  | PVL        |      |        |      |

|                 | Timer T12 Period Register Low                                      | Туре               |                                 |      |      | rv   | /h         |      |        |      |

| 9D <sub>H</sub> | CCU6_T12PRH Reset: 00 <sub>H</sub>                                 | Bit Field          |                                 |      |      | T12  | PVH        |      |        |      |

|                 | Timer T12 Period Register High                                     | Туре               |                                 |      |      | rv   | /h         |      |        |      |

| 9E <sub>H</sub> | CCU6_T13PRL Reset: 00 <sub>H</sub> Timer T13 Period Register Low   | Bit Field          |                                 |      |      | T13  | PVL        |      |        |      |

|                 | Timer 113 Feriod Register Low                                      | Туре               |                                 |      |      | rv   | /h         |      |        |      |

| 9F <sub>H</sub> | CCU6_T13PRH Reset: 00 <sub>H</sub> Timer T13 Period Register High  | Bit Field          |                                 |      |      | T13  | PVH        |      |        |      |

|                 |                                                                    | Туре               |                                 |      |      | rv   | /h         |      |        |      |

| <sup>A4</sup> H | CCU6_T12DTCL Reset: 00 <sub>H</sub> Dead-Time Control Register for | Bit Field          |                                 |      |      | רם   | ГМ         |      |        |      |

|                 | Timer T12 Low                                                      | Туре               |                                 |      |      | n    | N          |      |        |      |

| A5 <sub>H</sub> | CCU6_T12DTCH Reset: 00 <sub>H</sub> Dead-Time Control Register for | Bit Field          | 0                               | DTR2 | DTR1 | DTR0 | 0          | DTE2 | DTE1   | DTE0 |

|                 | Timer T12 High                                                     | Туре               | r                               | rh   | rh   | rh   | r          | rw   | rw     | rw   |

| A6 <sub>H</sub> | CCU6_TCTR0L Reset: 00 <sub>H</sub> Timer Control Register 0 Low    | Bit Field          | СТМ                             | CDIR | STE1 | T12R | T12<br>PRE |      | T12CLK |      |

|                 |                                                                    | Туре               | rw                              | rh   | rh   | rh   | rw         |      | rw     |      |

| <sup>A7</sup> H | CCU6_TCTR0H Reset: 00 <sub>H</sub> Timer Control Register 0 High   | Bit Field          | ield 0 STE1 T13R T13 T13CLK PRE |      |      |      |            |      |        |      |

|                 |                                                                    | Type r rh rh rw rw |                                 |      |      |      |            |      |        |      |

| FA <sub>H</sub> | CCU6_CC60RL Reset: 00H                                             | Bit Field          |                                 |      |      |      |            |      |        |      |

|                 | Capture/Compare Register for Channel CC60 Low                      | Туре               |                                 |      |      | r    | h          |      |        |      |

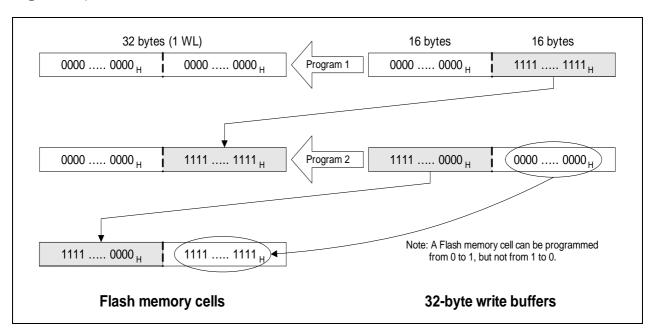

## 3.3.3 Flash Programming Width

For the P-Flash banks, a programmed wordline (WL) must be erased before it can be reprogrammed as the Flash cells can only withstand one gate disturb. This means that the entire sector containing the WL must be erased since it is impossible to erase a single WL.

For the D-Flash bank, the same WL can be programmed twice before erasing is required as the Flash cells are able to withstand two gate disturbs. This means if the number of data bytes that needs to be written is smaller than the 32-byte minimum programming width, the user can opt to program this number of data bytes (x; where x can be any integer from 1 to 31) first and program the remaining bytes (32 - x) later. Hence, it is possible to program the same WL, for example, with 16 bytes of data two times (see **Figure 11**)

Figure 11 D-Flash Programming

Note: When programming a D-Flash WL the second time, the previously programmed Flash memory cells (whether 0s or 1s) should be reprogrammed with 0s to retain its original contents and to prevent "over-programming".

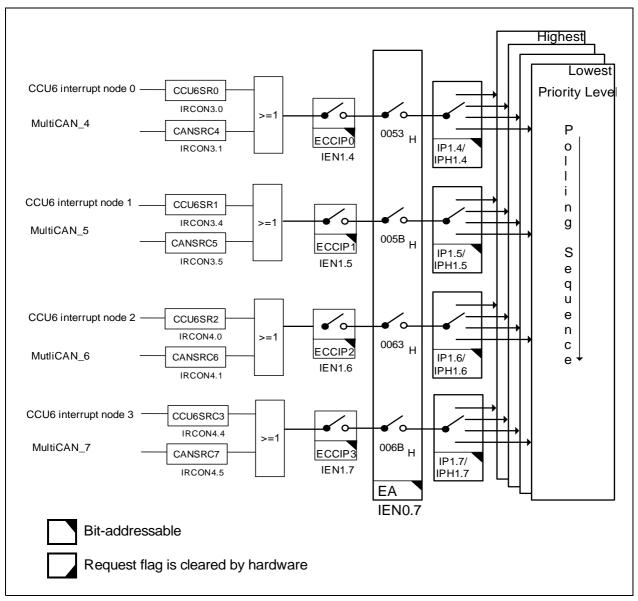

Figure 17 Interrupt Request Sources (Part 5)

Table 19 Interrupt Vector Addresses (cont'd)

| Interrupt<br>Source | Vector<br>Address | Assignment for SAA-<br>XC886                       | Enable Bit | SFR  |

|---------------------|-------------------|----------------------------------------------------|------------|------|

| XINTR6              | 0033 <sub>H</sub> | MultiCAN Nodes 1 and 2                             | EADC       | IEN1 |

|                     |                   | ADC[1:0]                                           |            |      |

| XINTR7              | 003B <sub>H</sub> | SSC                                                | ESSC       |      |

| XINTR8              | 0043 <sub>H</sub> | External Interrupt 2                               | EX2        |      |

|                     |                   | T21                                                |            |      |

|                     |                   | CORDIC                                             |            |      |

|                     |                   | UART1                                              |            |      |

|                     |                   | UART1 Fractional Divider (Normal Divider Overflow) |            |      |

|                     |                   | MDU[1:0]                                           | 1          |      |

| XINTR9              | 004B <sub>H</sub> | External Interrupt 3                               | EXM        |      |

|                     |                   | External Interrupt 4                               |            |      |

|                     |                   | External Interrupt 5                               |            |      |

|                     |                   | External Interrupt 6                               |            |      |

|                     |                   | MultiCAN Node 3                                    |            |      |

| XINTR10             | 0053 <sub>H</sub> | CCU6 INP0                                          | ECCIP0     |      |

|                     |                   | MultiCAN Node 4                                    |            |      |

| XINTR11             | 005B <sub>H</sub> | CCU6 INP1                                          | ECCIP1     |      |

|                     |                   | MultiCAN Node 5                                    |            |      |

| XINTR12             | 0063 <sub>H</sub> | CCU6 INP2                                          | ECCIP2     |      |

|                     |                   | MultiCAN Node 6                                    |            |      |

| XINTR13             | 006B <sub>H</sub> | CCU6 INP3                                          | ECCIP3     |      |

|                     |                   | MultiCAN Node 7                                    |            |      |

## 3.4.3 Interrupt Priority

An interrupt that is currently being serviced can only be interrupted by a higher-priority interrupt, but not by another interrupt of the same or lower priority. Hence, an interrupt of the highest priority cannot be interrupted by any other interrupt request.

If two or more requests of different priority levels are received simultaneously, the request of the highest priority is serviced first. If requests of the same priority are received simultaneously, then an internal polling sequence determines which request is serviced first. Thus, within each priority level, there is a second priority structure determined by the polling sequence shown in **Table 20**.

Table 20 Priority Structure within Interrupt Level

| , , , , , , , , , , , , , , , , , , ,                                                       |           |  |  |  |  |  |

|---------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|

| Source                                                                                      | Level     |  |  |  |  |  |

| Non-Maskable Interrupt (NMI)                                                                | (highest) |  |  |  |  |  |

| External Interrupt 0                                                                        | 1         |  |  |  |  |  |

| Timer 0 Interrupt                                                                           | 2         |  |  |  |  |  |

| External Interrupt 1                                                                        | 3         |  |  |  |  |  |

| Timer 1 Interrupt                                                                           | 4         |  |  |  |  |  |

| UART Interrupt                                                                              | 5         |  |  |  |  |  |

| Timer 2,UART Normal Divider Overflow,<br>MultiCAN, LIN Interrupt                            | 6         |  |  |  |  |  |

| ADC, MultiCAN Interrupt                                                                     | 7         |  |  |  |  |  |

| SSC Interrupt                                                                               | 8         |  |  |  |  |  |

| External Interrupt 2, Timer 21, UART1, UART1 Normal Divider Overflow, MDU, CORDIC Interrupt | 9         |  |  |  |  |  |

| External Interrupt [6:3], MultiCAN Interrupt                                                | 10        |  |  |  |  |  |

| CCU6 Interrupt Node Pointer 0, MultiCAN interrupt                                           | 11        |  |  |  |  |  |

| CCU6 Interrupt Node Pointer 1, MultiCAN Interrupt                                           | 12        |  |  |  |  |  |

| CCU6 Interrupt Node Pointer 2, MultiCAN Interrupt                                           | 13        |  |  |  |  |  |

| CCU6 Interrupt Node Pointer 3, MultiCAN Interrupt                                           | 14        |  |  |  |  |  |

| ·                                                                                           |           |  |  |  |  |  |

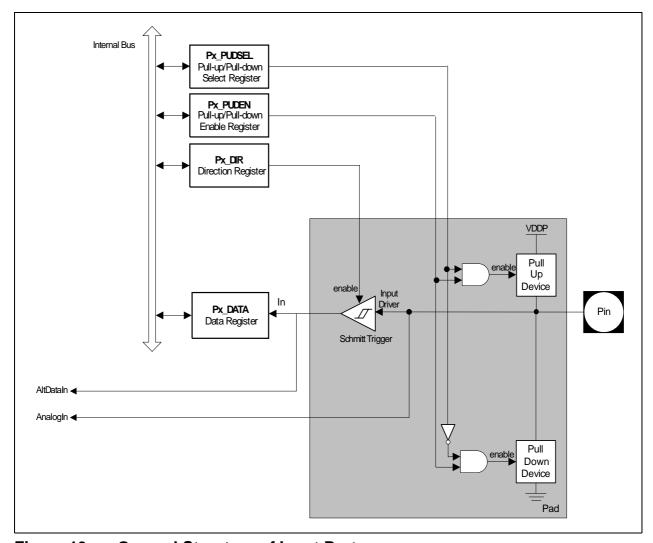

Figure 19 shows the structure of an input-only port pin.

Figure 19 General Structure of Input Port

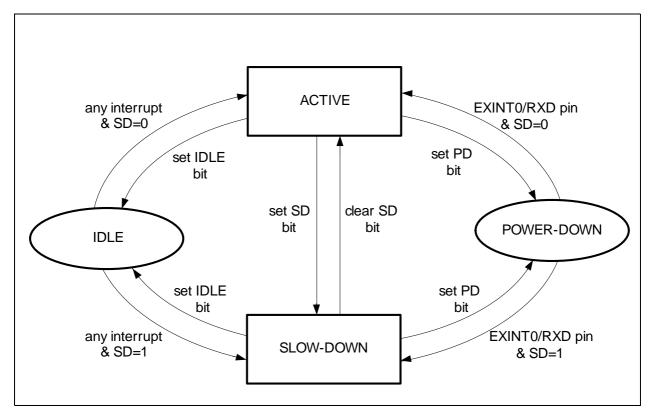

## 3.9 Power Saving Modes

The power saving modes of the SAA-XC886 provide flexible power consumption through a combination of techniques, including:

- Stopping the CPU clock

- Stopping the clocks of individual system components

- Reducing clock speed of some peripheral components

- Power-down of the entire system with fast restart capability

After a reset, the active mode (normal operating mode) is selected by default (see **Figure 26**) and the system runs in the main system clock frequency. From active mode, different power saving modes can be selected by software. They are:

- Idle mode

- Slow-down mode

- Power-down mode

Figure 26 Transition between Power Saving Modes

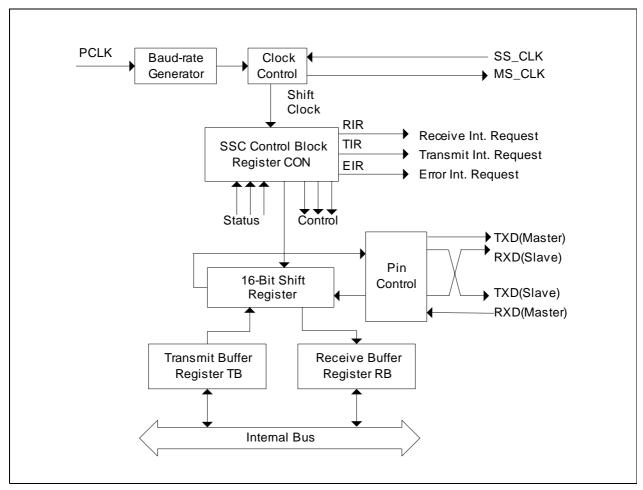

Figure 31 SSC Block Diagram

#### 3.18 Timer 2 and Timer 21

Timer 2 and Timer 21 are 16-bit general purpose timers (THL2) that are fully compatible and have two modes of operation, a 16-bit auto-reload mode and a 16-bit one channel capture mode, see **Table 32**. As a timer, the timers count with an input clock of PCLK/12 (if prescaler is disabled). As a counter, they count 1-to-0 transitions on pin T2. In the counter mode, the maximum resolution for the count is PCLK/24 (if prescaler is disabled).

| Table 32        | Timer 2 Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Mode            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Auto-reload     | <ul> <li>Up/Down Count Disabled</li> <li>Count up only</li> <li>Start counting from 16-bit reload value, overflow at FFFF<sub>H</sub></li> <li>Reload event configurable for trigger by overflow condition only, or by negative/positive edge at input pin T2EX as well</li> <li>Programmble reload value in register RC2</li> <li>Interrupt is generated with reload event</li> </ul>                                                                                                                                                                                                                                        |  |  |  |  |

|                 | <ul> <li>Up/Down Count Enabled</li> <li>Count up or down, direction determined by level at input pin T2EX</li> <li>No interrupt is generated</li> <li>Count up         <ul> <li>Start counting from 16-bit reload value, overflow at FFFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Programmble reload value in register RC2</li> </ul> </li> <li>Count down         <ul> <li>Start counting from FFFF<sub>H</sub>, underflow at value defined in register RC2</li> <li>Reload event triggered by underflow condition</li> <li>Reload value fixed at FFFF<sub>H</sub></li> </ul> </li> </ul> |  |  |  |  |

| Channel capture | <ul> <li>Count up only</li> <li>Start counting from 0000<sub>H</sub>, overflow at FFFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Reload value fixed at 0000<sub>H</sub></li> <li>Capture event triggered by falling/rising edge at pin T2EX</li> <li>Captured timer value stored in register RC2</li> <li>Interrupt is generated with reload or capture event</li> </ul>                                                                                                                                                                                                                     |  |  |  |  |

However, it is important to note that the conversion error could increase due to loss of charges on the capacitors, if  $f_{\rm ADC}$  becomes too low during slow-down mode.

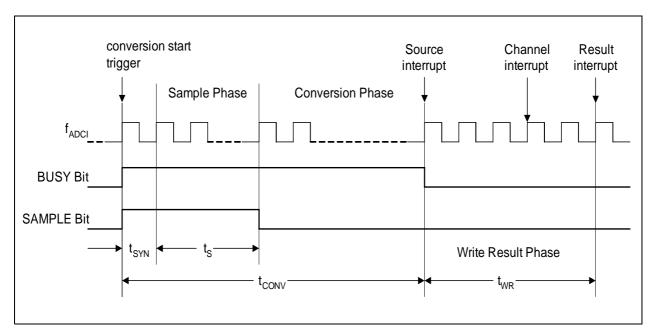

# 3.21.2 ADC Conversion Sequence

The analog-to-digital conversion procedure consists of the following phases:

- Synchronization phase (t<sub>SYN</sub>)

- Sample phase  $(t_S)$

- Conversion phase

- Write result phase  $(t_{WR})$

Figure 35 ADC Conversion Timing

Data Sheet 98 V1.1, 2010-08

#### **Electrical Parameters**

## 4.1.2 Absolute Maximum Rating

Maximum ratings are the extreme limits to which the SAA-XC886 can be subjected to without permanent damage.

**Table 36** Absolute Maximum Rating Parameters

| Parameter                                                                                                             | Symbol            | Limit Values |                                  | Unit | Notes                            |

|-----------------------------------------------------------------------------------------------------------------------|-------------------|--------------|----------------------------------|------|----------------------------------|

|                                                                                                                       |                   | min.         | max.                             |      |                                  |

| Ambient temperature                                                                                                   | $T_{A}$           | -40          | 140                              | °C   | under bias                       |

| Storage temperature                                                                                                   | $T_{ST}$          | -65          | 150                              | °C   | 1)                               |

| Junction temperature                                                                                                  | $T_{J}$           | -40          | 150                              | °C   | under bias <sup>1)</sup>         |

| $\begin{tabular}{lll} \hline & Voltage on power supply pin with \\ & respect to $V_{\rm SS}$ \\ \hline \end{tabular}$ | $V_{DDP}$         | -0.5         | 6                                | V    | 1)                               |

| Voltage on any pin with respect to $V_{\rm SS}$                                                                       | $V_{IN}$          | -0.5         | V <sub>DDP</sub> + 0.5 or max. 6 | V    | whichever is lower <sup>1)</sup> |

| Input current on any pin during overload condition                                                                    | $I_{IN}$          | -10          | 10                               | mA   | 1)                               |

| Absolute sum of all input currents during overload condition                                                          | $\Sigma  I_{IN} $ | _            | 50                               | mA   | 1)                               |

<sup>1)</sup> Not subjected to production test, verified by design/characterization.

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions  $(V_{\rm IN} > V_{\rm DDP})$  or  $V_{\rm IN} < V_{\rm SS}$  the voltage on  $V_{\rm DDP}$  pin with respect to ground  $(V_{\rm SS})$  must not exceed the values defined by the absolute maximum ratings.