Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | XC800                                                                           |

| Core Size                  | 8-Bit                                                                           |

| Speed                      | 24MHz                                                                           |

| Connectivity               | CANbus, LINbus, SSI, UART/USART                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 34                                                                              |

| Program Memory Size        | 24KB (24K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | - ·                                                                             |

| RAM Size                   | 1.75K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 140°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 48-LQFP                                                                         |

| Supplier Device Package    | PG-TQFP-48                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saa-xc886clm-6ffa-ac |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **General Device Information**

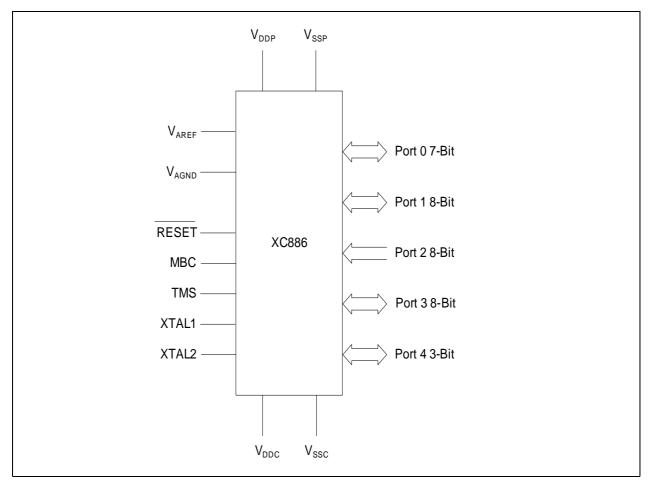

## 2.2 Logic Symbol

The logic symbols of the SAA-XC886 are shown in Figure 3.

Figure 3 SAA-XC886 Logic Symbol

#### **General Device Information**

| Symbol | Pin Number | Туре | Reset<br>State | Function                                                  |                                                                                                                                                                             |

|--------|------------|------|----------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P2     |            | I    |                | port. It can b<br>the digital inp                         | B-bit general purpose input-only<br>e used as alternate functions for<br>puts of the JTAG and CCU6. It is<br>the analog inputs for the ADC.                                 |

| P2.0   | 14         |      | Hi-Z           | CCPOS0_0<br>EXINT1_0<br>T12HR_2<br>TCK_1<br>CC61_3<br>AN0 | CCU6 Hall Input 0<br>External Interrupt Input 1<br>CCU6 Timer 12 Hardware Run<br>Input<br>JTAG Clock Input<br>Input of Capture/Compare<br>channel 1<br>Analog Input 0       |

| P2.1   | 15         |      | Hi-Z           | CCPOS1_0<br>EXINT2_0<br>T13HR_2<br>TDI_1<br>CC62_3<br>AN1 | CCU6 Hall Input 1<br>External Interrupt Input 2<br>CCU6 Timer 13 Hardware Run<br>Input<br>JTAG Serial Data Input<br>Input of Capture/Compare<br>channel 2<br>Analog Input 1 |

| P2.2   | 16         |      | Hi-Z           | CCPOS2_0<br>CTRAP_1<br>CC60_3<br>AN2                      | CCU6 Hall Input 2<br>CCU6 Trap Input<br>Input of Capture/Compare<br>channel 0<br>Analog Input 2                                                                             |

| P2.3   | 19         |      | Hi-Z           | AN3                                                       | Analog Input 3                                                                                                                                                              |

| P2.4   | 20         |      | Hi-Z           | AN4                                                       | Analog Input 4                                                                                                                                                              |

| P2.5   | 21         |      | Hi-Z           | AN5                                                       | Analog Input 5                                                                                                                                                              |

| P2.6   | 22         |      | Hi-Z           | AN6                                                       | Analog Input 6                                                                                                                                                              |

| P2.7   | 25         |      | Hi-Z           | AN7                                                       | Analog Input 7                                                                                                                                                              |

## Table 2Pin Definitions and Functions (cont'd)

infineon

#### 3.2.4 SAA-XC886 Register Overview

The SFRs of the SAA-XC886 are organized into groups according to their functional units. The contents (bits) of the SFRs are summarized in **Chapter 3.2.4.14**.

Note: The addresses of the bitaddressable SFRs appear in bold typeface.

#### 3.2.4.1 CPU Registers

The CPU SFRs can be accessed in both the standard and mapped memory areas (RMAP = 0 or 1).

| Addr            | Register Name                                      | Bit       | 7         | 6                    | 5    | 4    | 3         | 2    | 1    | 0    |  |  |  |

|-----------------|----------------------------------------------------|-----------|-----------|----------------------|------|------|-----------|------|------|------|--|--|--|

| RMAP =          | = 0 or 1                                           |           |           |                      |      |      |           |      |      | I    |  |  |  |

| 81 <sub>H</sub> | SP Reset: 07 <sub>H</sub>                          | Bit Field |           |                      |      | S    | P         |      |      |      |  |  |  |

|                 | Stack Pointer Register                             | Туре      | rw        |                      |      |      |           |      |      |      |  |  |  |

| 82 <sub>H</sub> | DPL Reset: 00 <sub>H</sub>                         | Bit Field | DPL7      | DPL6                 | DPL5 | DPL4 | DPL3      | DPL2 | DPL1 | DPL0 |  |  |  |

|                 | Data Pointer Register Low                          | Туре      | rw        | rw                   | rw   | rw   | rw        | rw   | rw   | rw   |  |  |  |

| 83 <sub>H</sub> | DPH Reset: 00 <sub>H</sub>                         | Bit Field | DPH7      | DPH6                 | DPH5 | DPH4 | DPH3      | DPH2 | DPH1 | DPH0 |  |  |  |

|                 | Data Pointer Register High                         | Туре      | rw        | rw                   | rw   | rw   | rw        | rw   | rw   | rw   |  |  |  |

| 87 <sub>H</sub> | PCON Reset: 00 <sub>H</sub>                        | Bit Field | SMOD      | SMOD 0 GF1 GF0 0 IDL |      |      |           |      |      |      |  |  |  |

|                 | Power Control Register                             | Туре      | rw        |                      | r    |      | rw        | rw   | r    | rw   |  |  |  |

| 88 <sub>H</sub> | TCON Reset: 00 <sub>H</sub>                        | Bit Field | TF1       | TR1                  | TF0  | TR0  | IE1       | IT1  | IE0  | IT0  |  |  |  |

|                 | Timer Control Register                             | Туре      | rwh       | rw                   | rwh  | rw   | rwh       | rw   | rwh  | rw   |  |  |  |

| 89 <sub>H</sub> | TMOD Reset: 00 <sub>H</sub><br>Timer Mode Register | Bit Field | GATE<br>1 | T1S                  | T1   | IM   | GATE<br>0 | TOS  | Т    | ТОМ  |  |  |  |

|                 |                                                    | Туре      | rw        | rw                   | rv   | W    | rw        | rw   | r    | w    |  |  |  |

| 8A <sub>H</sub> | TL0 Reset: 00 <sub>H</sub>                         | Bit Field |           |                      |      | V    | AL        |      |      |      |  |  |  |

|                 | Timer 0 Register Low                               | Туре      |           |                      |      | rv   | vh        |      |      |      |  |  |  |

| 8B <sub>H</sub> | TL1 Reset: 00 <sub>H</sub>                         | Bit Field |           |                      |      | V    | AL        |      |      |      |  |  |  |

|                 | Timer 1 Register Low                               | Туре      |           |                      |      | rv   | vh        |      |      |      |  |  |  |

| 8C <sub>H</sub> | THO Reset: 00 <sub>H</sub>                         | Bit Field |           |                      |      | V    | ۹L        |      |      |      |  |  |  |

|                 | Timer 0 Register High                              | Туре      |           |                      |      | rv   | vh        |      |      |      |  |  |  |

| 8D <sub>H</sub> | TH1 Reset: 00 <sub>H</sub>                         | Bit Field |           |                      |      | V    | ۹L        |      |      |      |  |  |  |

|                 | Timer 1 Register High                              | Туре      |           |                      |      | rv   | vh        |      |      |      |  |  |  |

| 98 <sub>H</sub> | SCON Reset: 00 <sub>H</sub>                        | Bit Field | SM0       | SM1                  | SM2  | REN  | TB8       | RB8  | TI   | RI   |  |  |  |

|                 | Serial Channel Control Register                    | Туре      | rw        | rw                   | rw   | rw   | rw        | rwh  | rwh  | rwh  |  |  |  |

| 99 <sub>H</sub> | SBUF Reset: 00 <sub>H</sub>                        | Bit Field |           |                      |      | V    | ۹L        |      |      |      |  |  |  |

|                 | Serial Data Buffer Register                        | Туре      |           |                      |      | rv   | vh        |      |      |      |  |  |  |

#### Table 4 CPU Register Overview

## Table 8 WDT Register Overview (cont'd)

| Addr            | Register Name                | Bit       | 7 6 5 4 3 2 1 |  |  |   |   |  |  | 0       |  |  |  |  |  |

|-----------------|------------------------------|-----------|---------------|--|--|---|---|--|--|---------|--|--|--|--|--|

| ве <sub>Н</sub> | WDTL Reset: 00 <sub>H</sub>  | Bit Field | WDT           |  |  |   |   |  |  |         |  |  |  |  |  |

|                 | Watchdog Timer Register Low  | Туре      | rh            |  |  |   |   |  |  |         |  |  |  |  |  |

| bf <sub>H</sub> | WDTH Reset: 00 <sub>H</sub>  | Bit Field | WDT           |  |  |   |   |  |  | eld WDT |  |  |  |  |  |

|                 | Watchdog Timer Register High | Туре      |               |  |  | r | h |  |  |         |  |  |  |  |  |

#### 3.2.4.6 Port Registers

The Port SFRs can be accessed in the standard memory area (RMAP = 0).

#### Table 9 Port Register Overview

| Addr            | Register Name                    | Bit       | 7  | 6  | 5  | 4  | 3  | 2  | 1    | 0  |

|-----------------|----------------------------------|-----------|----|----|----|----|----|----|------|----|

| RMAP =          | = 0                              |           |    |    |    |    |    |    |      |    |

| B2 <sub>H</sub> | PORT_PAGE Reset: 00 <sub>H</sub> | Bit Field | C  | P  | ST | NR | 0  |    | PAGE |    |

|                 | Page Register                    | Туре      | ١  | N  | ١  | N  | r  |    | rw   |    |

| RMAP =          | = 0, PAGE 0                      |           |    |    | •  |    | •  | •  |      |    |

| 80 <sub>H</sub> | P0_DATA Reset: 00 <sub>H</sub>   | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1   | P0 |

|                 | P0 Data Register                 | Туре      | rw   | rw |

| 86 <sub>H</sub> | P0_DIR Reset: 00 <sub>H</sub>    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1   | P0 |

|                 | P0 Direction Register            | Туре      | rw   | rw |

| 90 <sub>H</sub> | P1_DATA Reset: 00 <sub>H</sub>   | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1   | P0 |

|                 | P1 Data Register                 | Туре      | rw   | rw |

| 91 <sub>H</sub> | P1_DIR Reset: 00 <sub>H</sub>    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1   | P0 |

|                 | P1 Direction Register            | Туре      | rw   | rw |

| 92 <sub>H</sub> | P5_DATA Reset: 00 <sub>H</sub>   | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1   | P0 |

|                 | P5 Data Register                 | Туре      | rw   | rw |

| <sup>93</sup> H | P5_DIR Reset: 00 <sub>H</sub>    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1   | P0 |

|                 | P5 Direction Register            | Туре      | rw   | rw |

| A0 <sub>H</sub> | P2_DATA Reset: 00 <sub>H</sub>   | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1   | P0 |

|                 | P2 Data Register                 | Туре      | rw   | rw |

| A1 <sub>H</sub> | P2_DIR Reset: 00 <sub>H</sub>    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1   | P0 |

|                 | P2 Direction Register            | Туре      | rw   | rw |

| во <sub>Н</sub> | P3_DATA Reset: 00 <sub>H</sub>   | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1   | P0 |

|                 | P3 Data Register                 | Туре      | rw   | rw |

| B1 <sub>H</sub> | P3_DIR Reset: 00 <sub>H</sub>    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1   | P0 |

|                 | P3 Direction Register            | Туре      | rw   | rw |

| C8 <sub>H</sub> | P4_DATA Reset: 00 <sub>H</sub>   | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1   | P0 |

|                 | P4 Data Register                 | Туре      | rw   | rw |

| C9 <sub>H</sub> | P4_DIR Reset: 00 <sub>H</sub>    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1   | P0 |

|                 | P4 Direction Register            | Туре      | rw   | rw |

0 P0 rw P0 rw P0 rw P0 rw P0 rw

P0 rw P0 rw P0 rw P0 rw P0

rw

#### **Functional Description**

| Table           | Fable 9         Port Register Overview (cont'd) |           |    |    |    |    |    |    |    |   |  |

|-----------------|-------------------------------------------------|-----------|----|----|----|----|----|----|----|---|--|

| Addr            | Register Name                                   | Bit       | 7  | 6  | 5  | 4  | 3  | 2  | 1  | Γ |  |

| 93 <sub>H</sub> | P5_ALTSEL1 Reset: 00 <sub>H</sub>               | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 |   |  |

|                 | P5 Alternate Select 1 Register                  | Туре      | rw | ľ |  |

| во <sub>Н</sub> | P3_ALTSEL0 Reset: 00 <sub>H</sub>               | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 |   |  |

|                 | P3 Alternate Select 0 Register                  | Туре      | rw | ľ |  |

| B1 <sub>H</sub> | P3_ALTSEL1 Reset: 00 <sub>H</sub>               | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 |   |  |

|                 | P3 Alternate Select 1 Register                  | Туре      | rw | ľ |  |

| C8 <sub>H</sub> | P4_ALTSEL0 Reset: 00 <sub>H</sub>               | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 |   |  |

|                 | P4 Alternate Select 0 Register                  | Туре      | rw | Ī |  |

| C9 <sub>H</sub> | P4_ALTSEL1 Reset: 00 <sub>H</sub>               | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 |   |  |

|                 | P4 Alternate Select 1 Register                  | Туре      | rw | ľ |  |

| RMAP =          | = 0, PAGE 3                                     |           |    |    |    |    |    |    |    | - |  |

| 80 <sub>H</sub> | P0_OD Reset: 00 <sub>H</sub>                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 |   |  |

|                 | P0 Open Drain Control Register                  | Туре      | rw | ľ |  |

| 90 <sub>H</sub> | P1_OD Reset: 00 <sub>H</sub>                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 |   |  |

|                 | P1 Open Drain Control Register                  | Туре      | rw | Ī |  |

| 92 <sub>H</sub> | P5_OD Reset: 00 <sub>H</sub>                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | ſ |  |

|                 | P5 Open Drain Control Register                  | Туре      | rw | ľ |  |

| во <sub>Н</sub> | P3_OD Reset: 00 <sub>H</sub>                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 |   |  |

|                 | P3 Open Drain Control Register                  | Туре      | rw | ľ |  |

| C8 <sub>H</sub> | P4_OD Reset: 00 <sub>H</sub>                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | Γ |  |

|                 | P4 Open Drain Control Register                  | Туре      | rw | Γ |  |

#### Port Pagister Overview (cont'd) Table O

#### 3.2.4.7 **ADC Registers**

The ADC SFRs can be accessed in the standard memory area (RMAP = 0).

| Table 10 | ADC Register Overview |

|----------|-----------------------|

|----------|-----------------------|

| Addr            | Register Name                                                        | Bit       | 7         | 6         | 5        | 4    | 3    | 2     | 1          | 0     |  |

|-----------------|----------------------------------------------------------------------|-----------|-----------|-----------|----------|------|------|-------|------------|-------|--|

| RMAP =          | = 0                                                                  |           |           |           |          |      |      |       |            |       |  |

| D1 <sub>H</sub> | ADC_PAGE Reset: 00 <sub>H</sub>                                      | Bit Field | 0         | P         | STNR     |      | 0    | PAGE  |            |       |  |

|                 | Page Register                                                        | Туре      | V         | v         | ١        | N    | r    |       | rw         |       |  |

| RMAP =          | = 0, PAGE 0                                                          |           |           |           |          |      |      |       |            |       |  |

| CA <sub>H</sub> | ADC_GLOBCTR Reset: 30 <sub>H</sub>                                   | Bit Field | ANON      | DW        | C.       | ГС   | 0    |       |            |       |  |

|                 | Global Control Register                                              | Туре      | rw        | rw        | r        | W    |      |       | r          |       |  |

| св <sub>Н</sub> | ADC_GLOBSTR Reset: 00 <sub>H</sub><br>Global Status Register         | Bit Field | (         | )         |          | CHNR |      | 0     | SAMP<br>LE | BUSY  |  |

|                 |                                                                      | Туре      | I         | r         |          | rh   |      |       | rh         | rh    |  |

| cc <sup>H</sup> | ADC_PRAR Reset: 00 <sub>H</sub><br>Priority and Arbitration Register | Bit Field | ASEN<br>1 | ASEN<br>0 | 0 ARBM C |      | CSM1 | PRIO1 | CSM0       | PRIO0 |  |

|                 |                                                                      | Туре      | rw        | rw        | r        | rw   | rw   | rw    | rw         | rw    |  |

#### Table 13 CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                         | Bit       | 7   | 6    | 5         | 4    | 3          | 2    | 1      | 0    |  |  |

|-----------------|-----------------------------------------------------------------------|-----------|-----|------|-----------|------|------------|------|--------|------|--|--|

| FA <sub>H</sub> | CCU6_CC60SRL Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | OSL        |      |        |      |  |  |

|                 | Capture/Compare Shadow Register<br>for Channel CC60 Low               | Туре      |     |      |           | rv   | /h         |      |        |      |  |  |

| FB <sub>H</sub> | CCU6_CC60SRH Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | 0SH        |      |        |      |  |  |

|                 | Capture/Compare Shadow Register<br>for Channel CC60 High              | Туре      |     |      |           | rv   | /h         |      |        |      |  |  |

| FC <sub>H</sub> | CCU6_CC61SRL Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | 1SL        |      |        |      |  |  |

|                 | Capture/Compare Shadow Register<br>for Channel CC61 Low               | Туре      |     |      |           | rv   | /h         |      |        |      |  |  |

| FD <sub>H</sub> | CCU6_CC61SRH Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | 1SH        |      |        |      |  |  |

|                 | Capture/Compare Shadow Register<br>for Channel CC61 High              | Туре      |     |      |           | rv   | /h         |      |        |      |  |  |

| FE <sub>H</sub> | CCU6_CC62SRL Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | 2SL        |      |        |      |  |  |

|                 | Capture/Compare Shadow Register<br>for Channel CC62 Low               | Туре      |     |      |           | rv   | /h         |      |        |      |  |  |

| FF <sub>H</sub> | CCU6_CC62SRH Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | 2SH        |      |        |      |  |  |

|                 | Capture/Compare Shadow Register<br>for Channel CC62 High              | Туре      |     |      |           | rv   | /h         |      |        |      |  |  |

| RMAP =          | 0, PAGE 1                                                             |           |     |      |           |      |            |      |        |      |  |  |

| 9A <sub>H</sub> | CCU6_CC63RL Reset: 00 <sub>H</sub>                                    | Bit Field |     |      |           | CC6  | 3VL        |      |        |      |  |  |

|                 | Capture/Compare Register for<br>Channel CC63 Low                      | Туре      |     |      |           | r    | h          |      |        |      |  |  |

| 9B <sub>H</sub> | CCU6_CC63RH Reset: 00 <sub>H</sub>                                    | Bit Field |     |      |           | CC6  | 3VH        |      |        |      |  |  |

|                 | Capture/Compare Register for<br>Channel CC63 High                     | Туре      |     |      |           | r    | h          |      |        |      |  |  |

| 9CH             | CCU6_T12PRL Reset: 00 <sub>H</sub>                                    | Bit Field |     |      |           | T12  | PVL        |      |        |      |  |  |

|                 | Timer T12 Period Register Low                                         | Туре      |     |      |           | rv   | <b>/</b> h |      |        |      |  |  |

| 9D <sub>H</sub> | CCU6_T12PRH Reset: 00 <sub>H</sub>                                    | Bit Field |     |      |           | T12  | PVH        |      |        |      |  |  |

|                 | Timer T12 Period Register High                                        | Туре      |     |      |           | rv   | /h         |      |        |      |  |  |

| 9E <sub>H</sub> | CCU6_T13PRL Reset: 00 <sub>H</sub><br>Timer T13 Period Register Low   | Bit Field |     |      |           | T13  | PVL        |      |        |      |  |  |

|                 |                                                                       | Туре      |     |      |           | rv   | /h         |      |        |      |  |  |

| 9F <sub>H</sub> | CCU6_T13PRH Reset: 00 <sub>H</sub><br>Timer T13 Period Register High  | Bit Field |     |      |           | T13  | PVH        |      |        |      |  |  |

|                 |                                                                       | Туре      |     |      |           | rv   |            |      |        |      |  |  |

| <sup>A4</sup> H | CCU6_T12DTCL Reset: 00 <sub>H</sub><br>Dead-Time Control Register for | Bit Field |     |      |           | DI   | ſM         |      |        |      |  |  |

|                 | Timer T12 Low                                                         | Туре      |     |      |           | n    | N          |      |        |      |  |  |

| А5 <sub>Н</sub> | CCU6_T12DTCH Reset: 00 <sub>H</sub><br>Dead-Time Control Register for | Bit Field | 0   | DTR2 | DTR1      | DTR0 | 0          | DTE2 | DTE1   | DTE0 |  |  |

|                 | Timer T12 High                                                        | Туре      | r   | rh   | rh        | rh   | r          | rw   | rw     | rw   |  |  |

| A6 <sub>H</sub> | CCU6_TCTR0L Reset: 00 <sub>H</sub><br>Timer Control Register 0 Low    | Bit Field | СТМ | CDIR | STE1<br>2 | T12R | T12<br>PRE |      | T12CLK |      |  |  |

|                 |                                                                       | Туре      | rw  | rh   | rh        | rh   | rw         |      | rw     |      |  |  |

| А7 <sub>Н</sub> | CCU6_TCTR0H Reset: 00 <sub>H</sub><br>Timer Control Register 0 High   | Bit Field | (   | 0    | STE1<br>3 | T13R | T13<br>PRE |      | T13CLK |      |  |  |

|                 |                                                                       | Туре      |     | r    | rh        | rh   | rw         |      | rw     |      |  |  |

| FA <sub>H</sub> | CCU6_CC60RL Reset: 00 <sub>H</sub>                                    | Bit Field |     |      |           | CC6  | 0VL        |      |        |      |  |  |

|                 | Capture/Compare Register for<br>Channel CC60 Low                      | Туре      |     |      |           | r    | h          |      |        |      |  |  |

#### Table 13 CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                                        | Bit               | 7          | 6           | 5          | 4             | 3          | 2          | 1          | 0          |  |  |

|-----------------|--------------------------------------------------------------------------------------|-------------------|------------|-------------|------------|---------------|------------|------------|------------|------------|--|--|

| FB <sub>H</sub> | CCU6_TCTR2H Reset: 00 <sub>H</sub>                                                   | Bit Field         |            | (           | 0          | <u> </u>      | T13F       | RSEL       | T12F       | RSEL       |  |  |

|                 | Timer Control Register 2 High                                                        | Туре              |            |             | r          |               | r          | w          | r          | w          |  |  |

| FC <sub>H</sub> | CCU6_MODCTRL Reset: 00 <sub>H</sub><br>Modulation Control Register Low               | Bit Field         | MCM<br>EN  | 0           |            |               | T12M       | T12MODEN   |            |            |  |  |

|                 |                                                                                      | Туре              | rw         | r           |            |               | r          | w          |            |            |  |  |

| FD <sub>H</sub> | CCU6_MODCTRH Reset: 00 <sub>H</sub><br>Modulation Control Register High              | Bit Field         | ECT1<br>3O | 0           |            |               | T13M       | T13MODEN   |            |            |  |  |

|                 |                                                                                      | Туре              | rw         | r           |            |               | r          | w          |            |            |  |  |

| FE <sub>H</sub> | CCU6_TRPCTRL Reset: 00 <sub>H</sub><br>Trap Control Register Low                     | Bit Field         |            |             | 0          |               |            | TRPM<br>2  | TRPM<br>1  | TRPM<br>0  |  |  |

|                 |                                                                                      | Туре              |            |             | r          |               |            | rw         | rw         | rw         |  |  |

| FF <sub>H</sub> | CCU6_TRPCTRH Reset: 00 <sub>H</sub><br>Trap Control Register High                    | Bit Field         | TRPP<br>EN | TRPE<br>N13 |            |               | TRI        | TRPEN      |            |            |  |  |

|                 |                                                                                      | Туре              | rw         | rw          |            |               | r          | rw         |            |            |  |  |

| RMAP =          | = 0, PAGE 3                                                                          | 1                 |            |             |            |               |            |            |            |            |  |  |

| 9A <sub>H</sub> | CCU6_MCMOUTL Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Register            | Bit Field         | 0          | R           |            |               | MC         | MCMP       |            |            |  |  |

|                 | Low                                                                                  | Туре              | r          | rh          |            |               | r          | rh         |            |            |  |  |

| 9B <sub>H</sub> | CCU6_MCMOUTH Reset: 00 <sub>H</sub>                                                  | Bit Field         | (          | C           |            | CURH          |            | EXPH       |            |            |  |  |

|                 | Multi-Channel Mode Output Register<br>High                                           | Туре              |            | r           |            | rh            |            | rh         |            |            |  |  |

| 9CH             | CCU6_ISL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status                  | Bit Field         | T12<br>PM  | T12<br>OM   | ICC62<br>F | ICC62<br>R    | ICC61<br>F | ICC61<br>R | ICC60<br>F | ICC60<br>R |  |  |

|                 | Register Low                                                                         | Туре              | rh         | rh          | rh         | rh            | rh         | rh         | rh         | rh         |  |  |

| 9D <sub>H</sub> | CCU6_ISH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status<br>Register High | Bit Field         | STR        | IDLE        | WHE        | CHE           | TRPS       | TRPF       | T13<br>PM  | T13<br>CM  |  |  |

|                 |                                                                                      | Туре              | rh         | rh          | rh         | rh            | rh         | rh         | rh         | rh         |  |  |

| 9EH             | CCU6_PISEL0L Reset: 00 <sub>H</sub><br>Port Input Select Register 0 Low              | Bit Field         | IST        | RP          | ISC        | C62           | ISC        | C61        | ISC        | C60        |  |  |

|                 |                                                                                      | Туре              | r          | w           | r          | N             | r          | w          | r          | w          |  |  |

| 9F <sub>H</sub> | CCU6_PISEL0H Reset: 00 <sub>H</sub><br>Port Input Select Register 0 High             | Bit Field         | IST1       | 2HR         | ISP        | OS2           | ISP        | OS1        | ISP        | OS0        |  |  |

|                 |                                                                                      | Туре              | r          | W           | r          | N             | r          | W          | r          | W          |  |  |

| <sup>A4</sup> H | CCU6_PISEL2 Reset: 00 <sub>H</sub><br>Port Input Select Register 2                   | Bit Field         |            |             | (          | )             |            |            | IST1       | 3HR        |  |  |

|                 |                                                                                      | Туре              |            |             |            | r             |            |            | r          | W          |  |  |

| FA <sub>H</sub> | CCU6_T12L Reset: 00 <sub>H</sub><br>Timer T12 Counter Register Low                   | Bit Field         |            |             |            | T12           | CVL        |            |            |            |  |  |

|                 |                                                                                      | Туре              |            |             |            |               | rwh        |            |            |            |  |  |

| FB <sub>H</sub> | CCU6_T12HReset: 00HTimer T12 Counter Register High                                   | Bit Field<br>Type |            |             |            | T12CVH<br>rwh |            |            |            |            |  |  |

| FC              | CCU6_T13L Reset: 00H                                                                 | Bit Field         |            |             |            |               | CVL        |            |            |            |  |  |

| FC <sub>H</sub> | Timer T13 Counter Register Low                                                       | Туре              |            |             |            |               | vh         |            |            |            |  |  |

| FD <sub>H</sub> | CCU6_T13H Reset: 00 <sub>H</sub>                                                     | Bit Field         |            |             |            |               | CVH        |            |            |            |  |  |

| г <b>- н</b>    | Timer T13 Counter Register High                                                      | 2                 |            |             |            | 1.0           |            |            |            |            |  |  |

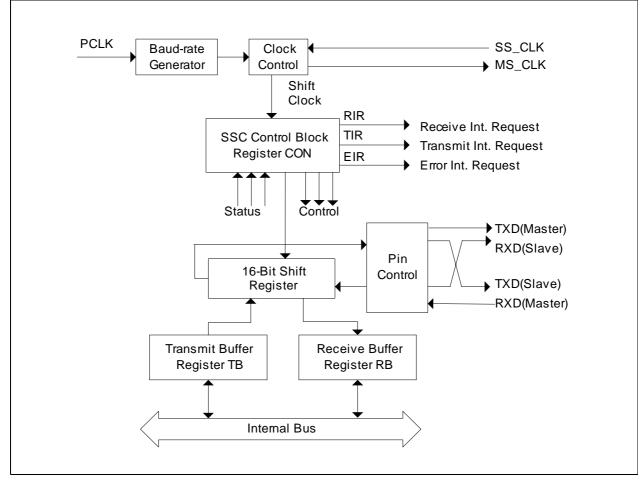

## 3.2.4.12 SSC Registers

The SSC SFRs can be accessed in the standard memory area (RMAP = 0).

| Addr            | Register Name                             | Bit       | 7        | 6  | 5  | 4    | 3    | 2   | 1   | 0   |  |

|-----------------|-------------------------------------------|-----------|----------|----|----|------|------|-----|-----|-----|--|

| RMAP =          | = 0                                       |           |          |    |    |      |      |     |     |     |  |

| A9 <sub>H</sub> | SSC_PISEL Reset: 00 <sub>H</sub>          | Bit Field |          |    | 0  |      |      | CIS | SIS | MIS |  |

|                 | Port Input Select Register                | Туре      |          |    | r  |      |      | rw  | rw  | rw  |  |

| AA <sub>H</sub> | SSC_CONL Reset: 00 <sub>H</sub>           | Bit Field | LB       | PO | PH | HB   |      | BM  |     |     |  |

|                 | Control Register Low<br>Programming Mode  | Туре      | rw       | rw | rw | rw   |      | r   | W   |     |  |

| AA <sub>H</sub> | SSC_CONL Reset: 00 <sub>H</sub>           | Bit Field |          |    | 0  |      |      | В   | С   |     |  |

|                 | Control Register Low<br>Operating Mode    | Туре      |          |    | r  |      |      | r   | h   |     |  |

| ab <sub>h</sub> | SSC_CONH Reset: 00 <sub>H</sub>           | Bit Field | EN       | MS | 0  | AREN | BEN  | PEN | REN | TEN |  |

|                 | Control Register High<br>Programming Mode | Туре      | rw       | rw | r  | rw   | rw   | rw  | rw  | rw  |  |

| ав <sub>Н</sub> | SSC_CONH Reset: 00 <sub>H</sub>           | Bit Field | EN       | MS | 0  | BSY  | BE   | PE  | RE  | TE  |  |

|                 | Control Register High<br>Operating Mode   | Туре      | rw       | rw | r  | rh   | rwh  | rwh | rwh | rwh |  |

| ac <sub>h</sub> | SSC_TBL Reset: 00 <sub>H</sub>            | Bit Field |          |    |    | TB_V | ALUE |     |     |     |  |

|                 | Transmitter Buffer Register Low           | Туре      |          |    |    | rv   | W    |     |     |     |  |

| ad <sub>H</sub> | SSC_RBL Reset: 00 <sub>H</sub>            | Bit Field |          |    |    | RB_V | ALUE |     |     |     |  |

|                 | Receiver Buffer Register Low              | Туре      |          |    |    | r    | h    |     |     |     |  |

| ае <sub>Н</sub> | SSC_BRL Reset: 00 <sub>H</sub>            | Bit Field | BR_VALUE |    |    |      |      |     |     |     |  |

|                 | Baud Rate Timer Reload<br>Register Low    | Туре      | rw       |    |    |      |      |     |     |     |  |

| AF <sub>H</sub> | SSC_BRH Reset: 00 <sub>H</sub>            | Bit Field |          |    |    | BR_V | ALUE |     |     |     |  |

|                 | Baud Rate Timer Reload<br>Register High   | Туре      |          |    |    | r    | N    |     |     |     |  |

#### Table 15 SSC Register Overview

#### 3.2.4.13 MultiCAN Registers

The MultiCAN SFRs can be accessed in the standard memory area (RMAP = 0).

| Addr            | Register Name                        | Bit       | 7   | 6   | 5   | 4   | 3    | 2    | 1    | 0    |

|-----------------|--------------------------------------|-----------|-----|-----|-----|-----|------|------|------|------|

| RMAP =          | RMAP = 0                             |           |     |     |     |     |      |      |      |      |

| D8 <sub>H</sub> | ADCON Reset: 00 <sub>H</sub>         | Bit Field | V3  | V2  | V1  | V0  | AUAD |      | BSY  | RWEN |

|                 | CAN Address/Data Control<br>Register | Туре      | rw  | rw  | rw  | rw  | rw   |      | rh   | rw   |

| D9 <sub>H</sub> | ADL Reset: 00 <sub>H</sub>           | Bit Field | CA9 | CA8 | CA7 | CA6 | CA5  | CA4  | CA3  | CA2  |

|                 | CAN Address Register Low             | Туре      | rwh | rwh | rwh | rwh | rwh  | rwh  | rwh  | rwh  |

| da <sub>H</sub> | ADH Reset: 00 <sub>H</sub>           | Bit Field | 0   |     |     |     | CA13 | CA12 | CA11 | CA10 |

|                 | CAN Address Register High            | Туре      | r   |     |     |     | rwh  | rwh  | rwh  | rwh  |

#### SAA-XC886CLM

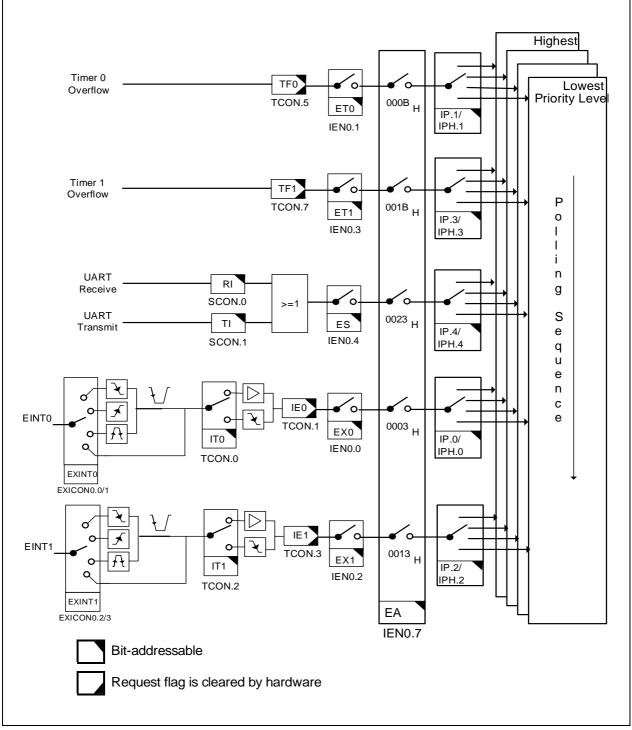

Figure 13 Interrupt Request Sources (Part 1)

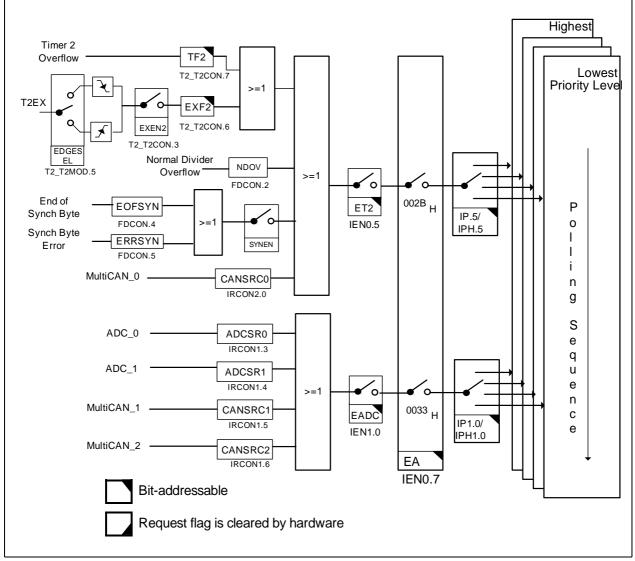

Figure 14 Interrupt Request Sources (Part 2)

infineon

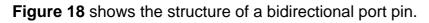

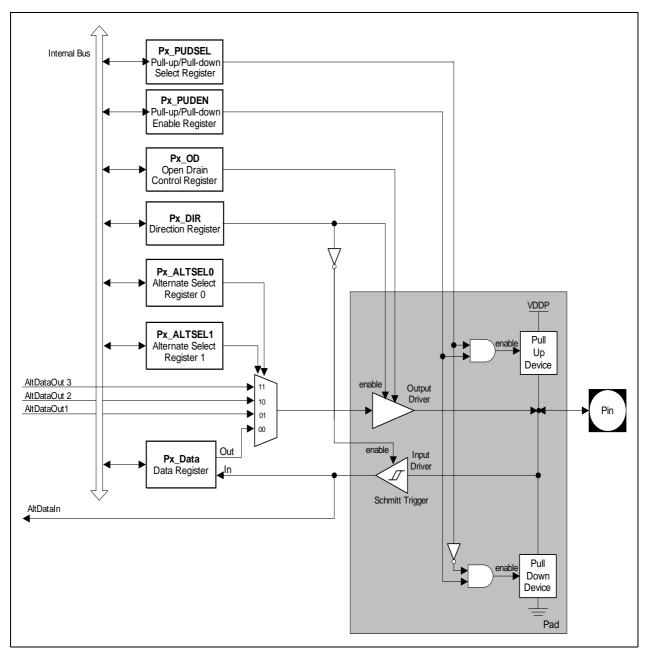

Figure 18 General Structure of Bidirectional Port

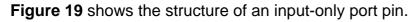

Figure 19 General Structure of Input Port

Table 24 shows the VCO range for the SAA-XC886.

| Table 24VCO Range |

|-------------------|

|-------------------|

| $f_{\sf VCOmin}$ | $f_{\sf VCOmax}$ | $f_{\sf VCOFREEmin}$ | $f_{\sf VCOFREEmax}$ | Unit |

|------------------|------------------|----------------------|----------------------|------|

| 150              | 200              | 20                   | 80                   | MHz  |

| 100              | 150              | 10                   | 80                   | MHz  |

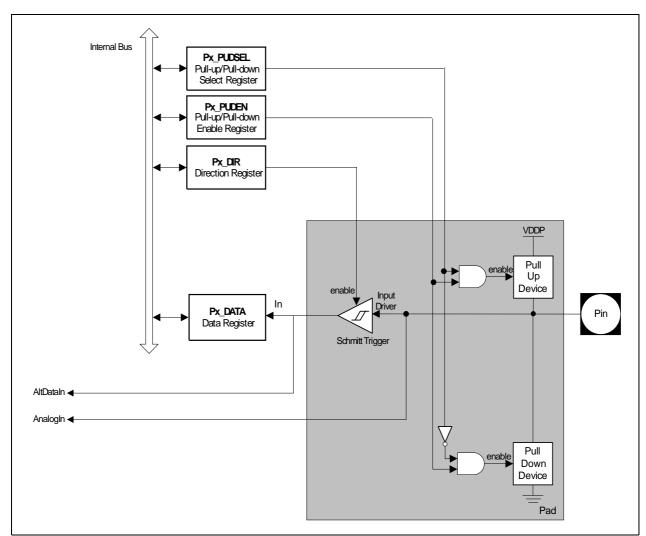

#### 3.8.1 Recommended External Oscillator Circuits

The oscillator circuit, a Pierce oscillator, is designed to work with both, an external crystal oscillator or an external stable clock source. It basically consists of an inverting amplifier and a feedback element with XTAL1 as input, and XTAL2 as output.

When using a crystal, a proper external oscillator circuitry must be connected to both pins, XTAL1 and XTAL2. The crystal frequency can be within the range of 4 MHz to 12 MHz. Additionally, it is necessary to have two load capacitances  $C_{X1}$  and  $C_{X2}$ , and depending on the crystal type, a series resistor  $R_{X2}$ , to limit the current. A test resistor  $R_Q$  may be temporarily inserted to measure the oscillation allowance (negative resistance) of the oscillator circuitry.  $R_Q$  values are typically specified by the crystal vendor. The  $C_{X1}$  and  $C_{X2}$  values shown in **Figure 24** can be used as starting points for the negative resistance evaluation and for non-productive systems. The exact values and related operating range are dependent on the crystal frequency and have to be determined and optimized together with the final target system is strongly recommended to verify the input amplitude at XTAL1 and to determine the actual oscillation allowance (margin negative resistance) for the oscillator-crystal system.

When using an external clock signal, the signal must be connected to XTAL1. XTAL2 is left open (unconnected).

The oscillator can also be used in combination with a ceramic resonator. The final circuitry must also be verified by the resonator vendor. **Figure 24** shows the recommended external oscillator circuitries for both operating modes, external crystal mode and external input clock mode.

#### Figure 24 External Oscillator Circuitry

Note: For crystal operation, it is strongly recommended to measure the negative resistance in the final target system (layout) to determine the optimum parameters for the oscillator operation. Please refer to the minimum and maximum values of the negative resistance specified by the crystal supplier.

- Interrupt enabling and corresponding flag

#### 3.13 UART and UART1

The SAA-XC886 provides two Universal Asynchronous Receiver/Transmitter (UART and UART1) modules for full-duplex asynchronous reception/transmission. Both are also receive-buffered, i.e., they can commence reception of a second byte before a previously received byte has been read from the receive register. However, if the first byte still has not been read by the time reception of the second byte is complete, one of the bytes will be lost.

#### Features

- Full-duplex asynchronous modes

- 8-bit or 9-bit data frames, LSB first

- Fixed or variable baud rate

- Receive buffered

- Multiprocessor communication

- Interrupt generation on the completion of a data transmission or reception

The UART modules can operate in the four modes shown in **Table 28**.

| Baud Rate                                  |

|--------------------------------------------|

| f <sub>PCLK</sub> /2                       |

| Variable                                   |

| $f_{PCLK}/32 \text{ or } f_{PCLK}/64^{1)}$ |

| Variable                                   |

|                                            |

#### Table 28UART Modes

1) For UART1 module, the baud rate is fixed at  $f_{PCLK}/64$ .

There are several ways to generate the baud rate clock for the serial port, depending on the mode in which it is operating. In mode 0, the baud rate for the transfer is fixed at  $f_{\rm PCLK}/2$ . In mode 2, the baud rate is generated internally based on the UART input clock and can be configured to either  $f_{\rm PCLK}/32$  or  $f_{\rm PCLK}/64$ . For UART1 module, only  $f_{\rm PCLK}/64$  is available. The variable baud rate is set by the underflow rate on the dedicated baud-rate generator. For UART module, the variable baud rate alternatively can be set by the overflow rate on Timer 1.

#### 3.13.1 Baud-Rate Generator

Both UART modules have their own dedicated baud-rate generator, which is based on a programmable 8-bit reload value, and includes divider stages (i.e., prescaler and

#### 3.15.1 LIN Header Transmission

LIN header transmission is only applicable in master mode. In the LIN communication, a master task decides when and which frame is to be transferred on the bus. It also identifies a slave task to provide the data transported by each frame. The information needed for the handshaking between the master and slave tasks is provided by the master task through the header portion of the frame.

The header consists of a break and synch pattern followed by an identifier. Among these three fields, only the break pattern cannot be transmitted as a normal 8-bit UART data. The break must contain a dominant value of 13 bits or more to ensure proper synchronization of slave nodes.

In the LIN communication, a slave task is required to be synchronized at the beginning of the protected identifier field of frame. For this purpose, every frame starts with a sequence consisting of a break field followed by a synch byte field. This sequence is unique and provides enough information for any slave task to detect the beginning of a new frame and be synchronized at the start of the identifier field.

Upon entering LIN communication, a connection is established and the transfer speed (baud rate) of the serial communication partner (host) is automatically synchronized in the following steps:

- STEP 1: Initialize interface for reception and timer for baud rate measurement

- STEP 2: Wait for an incoming LIN frame from host

- STEP 3: Synchronize the baud rate to the host

- STEP 4: Enter for Master Request Frame or for Slave Response Frame

- Note: Re-synchronization and setup of baud rate are always done for **every** Master Request Header or Slave Response Header LIN frame.

#### SAA-XC886CLM

Figure 31 SSC Block Diagram

# infineon

## **Functional Description**

## 3.22 On-Chip Debug Support

The On-Chip Debug Support (OCDS) provides the basic functionality required for the software development and debugging of XC800-based systems.

The OCDS design is based on these principles:

- Use the built-in debug functionality of the XC800 Core

- Add a minimum of hardware overhead

- Provide support for most of the operations by a Monitor Program

- Use standard interfaces to communicate with the Host (a Debugger)

#### Features

- Set breakpoints on instruction address and on address range within the Program Memory

- Set breakpoints on internal RAM address range

- Support unlimited software breakpoints in Flash/RAM code region

- Process external breaks via JTAG and upon activating a dedicated pin

- Step through the program code

The OCDS functional blocks are shown in **Figure 36**. The Monitor Mode Control (MMC) block at the center of OCDS system brings together control signals and supports the overall functionality. The MMC communicates with the XC800 Core, primarily via the Debug Interface, and also receives reset and clock signals.

After processing memory address and control signals from the core, the MMC provides proper access to the dedicated extra-memories: a Monitor ROM (holding the code) and a Monitor RAM (for work-data and Monitor-stack).

The OCDS system is accessed through the JTAG<sup>1)</sup>, which is an interface dedicated exclusively for testing and debugging activities and is not normally used in an application. The dedicated MBC pin is used for external configuration and debugging control.

Note: All the debug functionality described here can normally be used only after SAA-XC886 has been started in OCDS mode.

<sup>1)</sup> The pins of the JTAG port can be assigned to either the primary port (Port 0) or either of the secondary ports (Ports 1 and 2/Port 5).

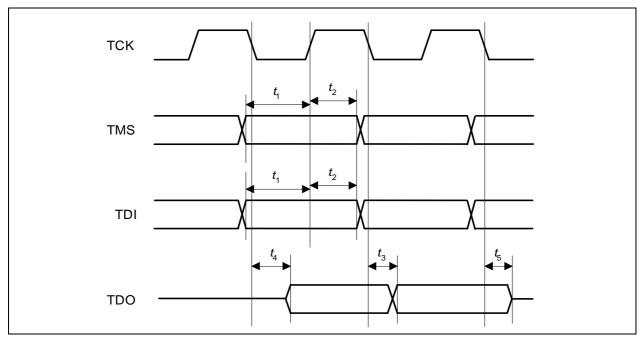

User must set the JTAG pins (TCK and TDI) as input during connection with the OCDS system.

#### **Electrical Parameters**

| Table 48 | JTAG Timing (Operating Conditions apply; CL = 50 pF) (cont'd) |

|----------|---------------------------------------------------------------|

|----------|---------------------------------------------------------------|

| Parameter                                   | Symbol                |    | Limits  |    | Unit | Test       |  |

|---------------------------------------------|-----------------------|----|---------|----|------|------------|--|

|                                             |                       |    | min max |    |      | Conditions |  |

| TDO high impedance to valid output from TCK | <i>t</i> <sub>4</sub> | CC | -       | 35 | ns   | 1)         |  |

| TDO valid output to high impedance from TCK | <i>t</i> <sub>5</sub> | CC | -       | 27 | ns   | 1)         |  |

1) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

Figure 46 JTAG Timing

www.infineon.com

Published by Infineon Technologies AG