Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | XC800                                                                             |

| Core Size                  | 8-Bit                                                                             |

| Speed                      | 24MHz                                                                             |

| Connectivity               | LINbus, SSI, UART/USART                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 34                                                                                |

| Program Memory Size        | 24KB (24K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 1.75K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 140°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 48-LQFP                                                                           |

| Supplier Device Package    | PG-TQFP-48                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saa-xc886lm-6ffa-5v-ac |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **General Device Information**

| Symbol | Pin Number | Туре | Reset<br>State | Function |                                                    |

|--------|------------|------|----------------|----------|----------------------------------------------------|

| P0.4   | 1          |      | Hi-Z           | MTSR_1   | SSC Master Transmit Output/<br>Slave Receive Input |

|        |            |      |                | CC62_1   | Input/Output of<br>Capture/Compare channel 2       |

|        |            |      |                | TXD1_0   | UART1 Transmit Data<br>Output/Clock Output         |

| P0.5   | 2          |      | Hi-Z           | MRST_1   | SSC Master Receive Input/Slave<br>Transmit Output  |

|        |            |      |                | EXINT0_0 | External Interrupt Input 0                         |

|        |            |      |                | T2EX1_1  | Timer 21 External Trigger Input                    |

|        |            |      |                | RXD1_0   | UART1 Receive Data Input                           |

|        |            |      |                | COUT62_1 | Output of Capture/Compare<br>channel 2             |

| P0.7   | 47         |      | PU             | CLKOUT_1 | Clock Output                                       |

## Table 2Pin Definitions and Functions (cont'd)

#### **General Device Information**

| Symbol | Pin Number | Туре | Reset<br>State | Function                                                                                                                                                                                               |                                                                                                                                                                             |  |  |  |  |  |

|--------|------------|------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| P2     |            | I    |                | <b>Port 2</b><br>Port 2 is an 8-bit general purpose input-only port. It can be used as alternate functions for the digital inputs of the JTAG and CCU6. It also used as the analog inputs for the ADC. |                                                                                                                                                                             |  |  |  |  |  |

| P2.0   | 14         |      | Hi-Z           | CCPOS0_0<br>EXINT1_0<br>T12HR_2<br>TCK_1<br>CC61_3<br>AN0                                                                                                                                              | CCU6 Hall Input 0<br>External Interrupt Input 1<br>CCU6 Timer 12 Hardware Run<br>Input<br>JTAG Clock Input<br>Input of Capture/Compare<br>channel 1<br>Analog Input 0       |  |  |  |  |  |

| P2.1   | 15         |      | Hi-Z           | CCPOS1_0<br>EXINT2_0<br>T13HR_2<br>TDI_1<br>CC62_3<br>AN1                                                                                                                                              | CCU6 Hall Input 1<br>External Interrupt Input 2<br>CCU6 Timer 13 Hardware Run<br>Input<br>JTAG Serial Data Input<br>Input of Capture/Compare<br>channel 2<br>Analog Input 1 |  |  |  |  |  |

| P2.2   | 16         |      | Hi-Z           | CCPOS2_0<br>CTRAP_1<br>CC60_3<br>AN2                                                                                                                                                                   | CCU6 Hall Input 2<br>CCU6 Trap Input<br>Input of Capture/Compare<br>channel 0<br>Analog Input 2                                                                             |  |  |  |  |  |

| P2.3   | 19         |      | Hi-Z           | AN3                                                                                                                                                                                                    | Analog Input 3                                                                                                                                                              |  |  |  |  |  |

| P2.4   | 20         |      | Hi-Z           | AN4                                                                                                                                                                                                    | Analog Input 4                                                                                                                                                              |  |  |  |  |  |

| P2.5   | 21         |      | Hi-Z           | AN5                                                                                                                                                                                                    | Analog Input 5                                                                                                                                                              |  |  |  |  |  |

| P2.6   | 22         |      | Hi-Z           | AN6                                                                                                                                                                                                    | Analog Input 6                                                                                                                                                              |  |  |  |  |  |

| P2.7   | 25         |      | Hi-Z           | AN7                                                                                                                                                                                                    | Analog Input 7                                                                                                                                                              |  |  |  |  |  |

# Table 2Pin Definitions and Functions (cont'd)

infineon

### **General Device Information**

| Symbol | Pin Number | Туре | Reset<br>State | Function                                 |                                                                                                                                                           |

|--------|------------|------|----------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Р3     |            | I/O  |                | I/O port. It ca                          | B-bit bidirectional general purpose<br>an be used as alternate functions<br>ART1, Timer 21 and MultiCAN.                                                  |

| P3.0   | 35         |      | Hi-Z           | CCPOS1_2<br>CC60_0<br>RXDO1_1            | CCU6 Hall Input 1<br>Input/Output of<br>Capture/Compare channel 0<br>UART1 Transmit Data Output                                                           |

| P3.1   | 36         |      | Hi-Z           | CCPOS0_2<br>CC61_2<br>COUT60_0<br>TXD1_1 | CCU6 Hall Input 0<br>Input/Output of<br>Capture/Compare channel 1<br>Output of Capture/Compare<br>channel 0<br>UART1 Transmit Data<br>Output/Clock Output |

| P3.2   | 37         |      | Hi-Z           | CCPOS2_2<br>RXDC1_1<br>RXD1_1<br>CC61_0  | CCU6 Hall Input 2<br>MultiCAN Node 1 Receiver Input<br>UART1 Receive Data Input<br>Input/Output of<br>Capture/Compare channel 1                           |

| P3.3   | 38         |      | Hi-Z           | COUT61_0<br>TXDC1_1                      | Output of Capture/Compare<br>channel 1<br>MultiCAN Node 1 Transmitter<br>Output                                                                           |

| P3.4   | 39         |      | Hi-Z           | CC62_0<br>RXDC0_1<br>T2EX1_0             | Input/Output of<br>Capture/Compare channel 2<br>MultiCAN Node 0 Receiver Input<br>Timer 21 External Trigger Input                                         |

| P3.5   | 40         |      | Hi-Z           | COUT62_0<br>EXF21_0<br>TXDC0_1           | Output of Capture/Compare<br>channel 2<br>Timer 21 External Flag Output<br>MultiCAN Node 0 Transmitter<br>Output                                          |

| P3.6   | 33         |      | PD             | CTRAP_0                                  | CCU6 Trap Input                                                                                                                                           |

## Table 2Pin Definitions and Functions (cont'd)

### **General Device Information**

| Symbol | Pin Number | Туре | Reset<br>State | Function            |                                                                                                                                              |  |  |  |  |

|--------|------------|------|----------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| P4     |            | I/O  |                | I/O port. It ca     | Port 4 is an 8-bit bidirectional general purpose<br>O port. It can be used as alternate functions<br>or CCU6, Timer 0, Timer 1, Timer 21 and |  |  |  |  |

| P4.0   | 45         |      | Hi-Z           | RXDC0_3<br>CC60_1   | MultiCAN Node 0 Receiver Input<br>Output of Capture/Compare<br>channel 0                                                                     |  |  |  |  |

| P4.1   | 46         |      | Hi-Z           | TXDC0_3<br>COUT60_1 | MultiCAN Node 0 Transmitter<br>Output<br>Output of Capture/Compare<br>channel 0                                                              |  |  |  |  |

| P4.3   | 32         |      | Hi-Z           | EXF21_1<br>COUT63_2 | Timer 21 External Flag Output<br>Output of Capture/Compare<br>channel 3                                                                      |  |  |  |  |

## Table 2Pin Definitions and Functions (cont'd)

#### **General Device Information**

| Symbol            | Pin Number | Туре | Reset<br>State | Function                                                                                              |

|-------------------|------------|------|----------------|-------------------------------------------------------------------------------------------------------|

| $V_{DDP}$         | 7, 17, 43  | _    | _              | <b>I/O Port Supply (5.0 V)</b><br>Also used by EVR and analog modules. All<br>pins must be connected. |

| $V_{\rm SSP}$     | 18, 42     | -    | _              | I/O Port Ground<br>All pins must be connected.                                                        |

| $V_{DDC}$         | 6          | -    | _              | Core Supply Monitor (2.5 V)                                                                           |

| V <sub>SSC</sub>  | 5          | _    | _              | Core Supply Ground                                                                                    |

| $V_{AREF}$        | 24         | _    | _              | ADC Reference Voltage                                                                                 |

| $V_{AGND}$        | 23         | _    | _              | ADC Reference Ground                                                                                  |

| XTAL1             | 4          | I    | Hi-Z           | External Oscillator Input<br>(backup for on-chip OSC, normally NC)                                    |

| XTAL2             | 3          | 0    | Hi-Z           | External Oscillator Output<br>(backup for on-chip OSC, normally NC)                                   |

| TMS               | 10         | I    | PD             | Test Mode Select                                                                                      |

| RESET             | 41         | I    | PU             | Reset Input                                                                                           |

| MBC <sup>1)</sup> | 44         | I    | PU             | Monitor & BootStrap Loader Control                                                                    |

## Table 2Pin Definitions and Functions (cont'd)

1) An external pull-up device in the range of 4.7 k $\Omega$  to 100 k $\Omega$ . is required to enter user mode. Alternatively MBC can be tied to high if alternate functions (for debugging) of the pin are not utilized.

### **Functional Description**

| Addr            | Register Name              | Bit                                   | 7                | 6    | 5 | 4  | 3   | 2 | 1 | 0 |  |  |  |

|-----------------|----------------------------|---------------------------------------|------------------|------|---|----|-----|---|---|---|--|--|--|

| B3 <sub>H</sub> | MD1 Reset: 00 <sub>H</sub> | Bit Field                             |                  | DATA |   |    |     |   |   |   |  |  |  |

|                 | MDU Operand Register 1     | Туре                                  | rw               |      |   |    |     |   |   |   |  |  |  |

| вз <sub>Н</sub> | MR1 Reset: 00 <sub>H</sub> | Bit Field                             |                  |      |   | DA | TA  |   |   |   |  |  |  |

|                 | MDU Result Register 1      | Туре                                  | rh               |      |   |    |     |   |   |   |  |  |  |

| B4 <sub>H</sub> | MD2 Reset: 00 <sub>H</sub> | Bit Field                             | DATA             |      |   |    |     |   |   |   |  |  |  |

|                 | MDU Operand Register 2     | Туре                                  | rw               |      |   |    |     |   |   |   |  |  |  |

| B4 <sub>H</sub> | MR2 Reset: 00 <sub>H</sub> | Bit Field                             | DATA             |      |   |    |     |   |   |   |  |  |  |

|                 | MDU Result Register 2      | Туре                                  |                  | rh   |   |    |     |   |   |   |  |  |  |

| в5 <sub>Н</sub> | MD3 Reset: 00 <sub>H</sub> | Bit Field                             | DATA             |      |   |    |     |   |   |   |  |  |  |

|                 | MDU Operand Register 3     | Туре                                  | rw               |      |   |    |     |   |   |   |  |  |  |

| в5 <sub>Н</sub> | MR3 Reset: 00 <sub>H</sub> | Bit Field                             | DATA             |      |   |    |     |   |   |   |  |  |  |

|                 | MDU Result Register 3      | Туре                                  | rw<br>DATA<br>rh |      |   |    |     |   |   |   |  |  |  |

| B6 <sub>H</sub> | MD4 Reset: 00 <sub>H</sub> | Bit Field                             |                  |      |   | DA | ATA |   |   |   |  |  |  |

|                 | MDU Operand Register 4     | Туре                                  |                  |      |   | r  | w   |   |   |   |  |  |  |

| B6 <sub>H</sub> | MR4 Reset: 00 <sub>H</sub> | Bit Field                             |                  |      |   | DA | ΛTA |   |   |   |  |  |  |

|                 | MDU Result Register 4      | Туре                                  |                  |      |   | r  | 'n  |   |   |   |  |  |  |

| в7 <sub>Н</sub> | MD5 Reset: 00 <sub>H</sub> | Bit Field                             | DATA             |      |   |    |     |   |   |   |  |  |  |

|                 | MDU Operand Register 5     | Туре                                  |                  |      |   | r  | w   |   |   |   |  |  |  |

| в7 <sub>Н</sub> | MR5 Reset: 00 <sub>H</sub> | Reset: 00 <sub>H</sub> Bit Field DATA |                  |      |   |    |     |   |   |   |  |  |  |

|                 | MDU Result Register 5      | Туре                                  |                  |      |   | r  | 'n  |   |   |   |  |  |  |

#### **MDU Register Overview** (cont'd) Table 5

İnfineon

#### **CORDIC Registers** 3.2.4.3

The CORDIC SFRs can be accessed in the mapped memory area (RMAP = 1).

#### **CORDIC Register Overview** Table 6

| Addr            | Register Name                    | Bit       | 7     | 6 | 5 | 4  | 3   | 2 | 1 | 0 |  |  |

|-----------------|----------------------------------|-----------|-------|---|---|----|-----|---|---|---|--|--|

| RMAP =          | = 1                              |           |       |   |   | •  |     |   |   |   |  |  |

| 9A <sub>H</sub> | CD_CORDXL Reset: 00 <sub>H</sub> | Bit Field | DATAL |   |   |    |     |   |   |   |  |  |

|                 | CORDIC X Data Low Byte           | Туре      | rw    |   |   |    |     |   |   |   |  |  |

| 9BH             | CD_CORDXH Reset: 00 <sub>H</sub> | Bit Field |       |   |   | DA | TAH |   |   |   |  |  |

|                 | CORDIC X Data High Byte          | Туре      | rw    |   |   |    |     |   |   |   |  |  |

| 9C <sub>H</sub> | CD_CORDYL Reset: 00 <sub>H</sub> | Bit Field |       |   |   | DA | TAL |   |   |   |  |  |

|                 | CORDIC Y Data Low Byte           | Туре      | rw    |   |   |    |     |   |   |   |  |  |

| 9D <sub>H</sub> | CD_CORDYH Reset: 00 <sub>H</sub> | Bit Field |       |   |   | DA | ТАН |   |   |   |  |  |

|                 | CORDIC Y Data High Byte          | Туре      | rw    |   |   |    |     |   |   |   |  |  |

| 9E <sub>H</sub> | CD_CORDZL Reset: 00 <sub>H</sub> | Bit Field | DATAL |   |   |    |     |   |   |   |  |  |

|                 | CORDIC Z Data Low Byte           | Туре      | rw    |   |   |    |     |   |   |   |  |  |

#### Table 6CORDIC Register Overview (cont'd)

| Addr            | Register Name                                             | Bit       | 7         | 6           | 5           | 4           | 3          | 2   | 1         | 0   |

|-----------------|-----------------------------------------------------------|-----------|-----------|-------------|-------------|-------------|------------|-----|-----------|-----|

| 9F <sub>H</sub> | CD_CORDZH Reset: 00 <sub>H</sub>                          | Bit Field |           |             |             | DA          | ГАН        |     |           |     |

|                 | CORDIC Z Data High Byte                                   | Туре      | rw        |             |             |             |            |     |           |     |

| ۵0 <sub>H</sub> | CD_STATC Reset: 00 <sub>H</sub><br>CORDIC Status and Data | Bit Field | KEEP<br>Z | KEEP<br>Y   | KEEP<br>X   | DMAP        | INT_E<br>N | EOC | ERRO<br>R | BSY |

|                 | Control Register                                          | Туре      | rw        | rw          | rw          | rw          | rw         | rwh | rh        | rh  |

| <sup>А1</sup> Н | CD_CON Reset: 00 <sub>H</sub><br>CORDIC Control Register  | Bit Field | MPS       |             | X_USI<br>GN | ST_M<br>ODE | ROTV<br>EC | MC  | DE        | ST  |

|                 |                                                           | Туре      | r         | rw rw rw rw |             |             |            |     | rwh       |     |

# 3.2.4.4 System Control Registers

The system control SFRs can be accessed in the mapped memory area (RMAP = 0).

### Table 7 SCU Register Overview

| Addr            | Register Name                                                       | Bit       | 7  | 6           | 5            | 4            | 3            | 2            | 1            | 0           |

|-----------------|---------------------------------------------------------------------|-----------|----|-------------|--------------|--------------|--------------|--------------|--------------|-------------|

| RMAP =          | = 0 or 1                                                            |           |    |             |              |              |              |              |              | 1           |

| 8F <sub>H</sub> | SYSCON0 Reset: 04 <sub>H</sub><br>System Control Register 0         | Bit Field |    | 0           |              | IMOD<br>E    | 0            | 1            | 0            | RMAP        |

|                 |                                                                     | Туре      |    | r           |              | rw           | r            | r            | r            | rw          |

| RMAP =          | = 0                                                                 |           |    |             |              |              |              |              |              |             |

| bf <sub>H</sub> | SCU_PAGE Reset: 00 <sub>H</sub>                                     | Bit Field | C  | )P          | ST           | NR           | 0            |              | PAGE         |             |

|                 | Page Register                                                       | Туре      | ,  | w           | ١            | N            | r            |              | rw           |             |

| RMAP =          | = 0, PAGE 0                                                         |           |    |             |              |              |              |              |              |             |

| вз <sub>Н</sub> | MODPISEL Reset: 00 <sub>H</sub><br>Peripheral Input Select Register | Bit Field | 0  | URRIS<br>H  | JTAGT<br>DIS | JTAGT<br>CKS | EXINT<br>2IS | EXINT<br>1IS | EXINT<br>0IS | URRIS       |

|                 |                                                                     | Туре      | r  | rw          | rw           | rw           | rw           | rw           | rw           | rw          |

| B4 <sub>H</sub> | IRCON0 Reset: 00 <sub>H</sub><br>Interrupt Request Register 0       | Bit Field | 0  | EXINT<br>6  | EXINT<br>5   | EXINT<br>4   | EXINT<br>3   | EXINT<br>2   | EXINT<br>1   | EXINT<br>0  |

|                 |                                                                     | Туре      | r  | rwh         | rwh          | rwh          | rwh          | rwh          | rwh          | rwh         |

| в5 <sub>Н</sub> | IRCON1 Reset: 00 <sub>H</sub><br>Interrupt Request Register 1       | Bit Field | 0  | CANS<br>RC2 | CANS<br>RC1  | ADCS<br>R1   | ADCS<br>R0   | RIR          | TIR          | EIR         |

|                 |                                                                     | Туре      | r  | rwh         | rwh          | rwh          | rwh          | rwh          | rwh          | rwh         |

| в6 <sub>Н</sub> | IRCON2 Reset: 00 <sub>H</sub><br>Interrupt Request Register 2       | Bit Field |    | 0           |              | CANS<br>RC3  |              | 0            |              | CANS<br>RC0 |

|                 |                                                                     | Туре      |    | r           |              | rwh          |              | r            |              | rwh         |

| в7 <sub>Н</sub> | EXICON0 Reset: F0 <sub>H</sub>                                      | Bit Field | EX | INT3        | EXI          | NT2          | EXI          | NT1          | EXI          | NT0         |

|                 | External Interrupt Control<br>Register 0                            | Туре      | r  | W           | r            | w            | r            | w            | r            | w           |

| ва <sub>Н</sub> | EXICON1 Reset: 3F <sub>H</sub>                                      | Bit Field |    | 0           | EXI          | NT6          | EXI          | NT5          | EXI          | NT4         |

|                 | External Interrupt Control<br>Register 1                            | Туре      |    | r           | r            | w            | r            | w            | r            | W           |

| вв <sub>Н</sub> | NMICON Reset: 00 <sub>H</sub><br>NMI Control Register               | Bit Field | 0  | NMI<br>ECC  | NMI<br>VDDP  | NMI<br>VDD   | NMI<br>OCDS  | NMI<br>FLASH | NMI<br>PLL   | NMI<br>WDT  |

|                 |                                                                     | Туре      | r  | rw          | rw           | rw           | rw           | rw           | rw           | rw          |

## Table 13 CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                                        | Bit       | 7               | 6               | 5           | 4           | 3           | 2           | 1           | 0           |  |

|-----------------|--------------------------------------------------------------------------------------|-----------|-----------------|-----------------|-------------|-------------|-------------|-------------|-------------|-------------|--|

| FB <sub>H</sub> | CCU6_CC60RH Reset: 00 <sub>H</sub>                                                   | Bit Field |                 |                 |             | CC6         | 60VH        |             |             |             |  |

|                 | Capture/Compare Register for<br>Channel CC60 High                                    | Туре      |                 |                 |             | r           | 'n          |             |             |             |  |

| FC <sub>H</sub> | CCU6_CC61RL Reset: 00 <sub>H</sub>                                                   | Bit Field |                 |                 |             | CC6         | 61VL        |             |             |             |  |

|                 | Capture/Compare Register for<br>Channel CC61 Low                                     | Туре      |                 |                 |             | r           | 'n          |             |             |             |  |

| FD <sub>H</sub> | CCU6_CC61RH Reset: 00 <sub>H</sub>                                                   | Bit Field |                 |                 |             | CC6         | 61VH        |             |             |             |  |

|                 | Capture/Compare Register for<br>Channel CC61 High                                    | Туре      |                 |                 |             | r           | 'n          |             |             |             |  |

| Fe <sub>H</sub> | CCU6_CC62RL Reset: 00 <sub>H</sub>                                                   | Bit Field |                 |                 |             | CCe         | 62VL        |             |             |             |  |

|                 | Capture/Compare Register for<br>Channel CC62 Low                                     | Туре      |                 |                 |             | r           | 'n          |             |             |             |  |

| FF <sub>H</sub> | CCU6_CC62RH Reset: 00 <sub>H</sub>                                                   | Bit Field |                 |                 |             | CC6         | S2VH        |             |             |             |  |

|                 | Capture/Compare Register for<br>Channel CC62 High                                    | Туре      |                 |                 |             | r           | 'n          |             |             |             |  |

| RMAP =          | = 0, PAGE 2                                                                          |           |                 |                 |             |             |             |             |             |             |  |

| 9A <sub>H</sub> | CCU6_T12MSELL Reset: 00 <sub>H</sub><br>T12 Capture/Compare Mode Select              | Bit Field |                 | MSI             | EL61        |             |             | MSEL60      |             |             |  |

|                 | Register Low                                                                         | Туре      |                 | r               | W           |             |             | r           | w           |             |  |

| 9B <sub>H</sub> | CCU6_T12MSELH Reset: 00 <sub>H</sub>                                                 | Bit Field | DBYP            |                 | HSYNC       |             |             | MSEL62      |             |             |  |

|                 | T12 Capture/Compare Mode Select<br>Register High                                     | Туре      | rw              |                 | rw          |             |             | r           |             |             |  |

| 9CH             | CCU6_IENL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Enable<br>Register Low | Bit Field | ENT1<br>2<br>PM | ENT1<br>2<br>OM | ENCC<br>62F | ENCC<br>62R | ENCC<br>61F | ENCC<br>61R | ENCC<br>60F | ENCC<br>60R |  |

|                 |                                                                                      | Туре      | rw              | rw              | rw          | rw          | rw          | rw          | rw          | rw          |  |

| 9D <sub>H</sub> | CCU6_IENH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Enable                 | Bit Field | EN<br>STR       | EN<br>IDLE      | EN<br>WHE   | EN<br>CHE   | 0           | EN<br>TRPF  | ENT1<br>3PM | ENT1<br>3CM |  |

|                 | Register High                                                                        | Туре      | rw              | rw              | rw          | rw          | r           | rw          | rw          | rw          |  |

| 9E <sub>H</sub> | CCU6_INPL Reset: 40 <sub>H</sub><br>Capture/Compare Interrupt Node                   | Bit Field | INP             | CHE             | INPO        | CC62        | INPO        | CC61        | INPO        | CC60        |  |

|                 | Pointer Register Low                                                                 | Туре      | r               | W               | r           | W           | r           | W           | r           | W           |  |

| 9F <sub>H</sub> | CCU6_INPH Reset: 39 <sub>H</sub><br>Capture/Compare Interrupt Node                   | Bit Field | (               | C               | INP         | T13         | INF         | T12         | INP         | ERR         |  |

|                 | Pointer Register High                                                                | Туре      |                 | r               | r           | w           | r           | w           | r           | w           |  |

| A4 <sub>H</sub> | CCU6_ISSL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status                 | Bit Field | ST12<br>PM      | ST12<br>OM      | SCC6<br>2F  | SCC6<br>2R  | SCC6<br>1F  | SCC6<br>1R  | SCC6<br>0F  | SCC6<br>0R  |  |

|                 | Set Register Low                                                                     | Туре      | w               | w               | w           | w           | w           | w           | w           | w           |  |

| <sup>А5</sup> Н | CCU6_ISSH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status                 | Bit Field | SSTR            | SIDLE           | SWHE        | SCHE        | SWH<br>C    | STRP<br>F   | ST13<br>PM  | ST13<br>CM  |  |

|                 | Set Register High                                                                    | Туре      | w               | w               | w           | w           | w           | w           | w           | w           |  |

| A6 <sub>H</sub> | CCU6_PSLR Reset: 00 <sub>H</sub><br>Passive State Level Register                     | Bit Field | PSL63           | 0               |             |             | P           | SL          |             |             |  |

|                 |                                                                                      | Туре      | rwh             | r               |             |             | r           | vh          |             |             |  |

| <sup>А7</sup> Н | CCU6_MCMCTR Reset: 00 <sub>H</sub><br>Multi-Channel Mode Control Register            | Bit Field |                 | 0               |             | SYN         | 0           |             | SWSEL       |             |  |

|                 |                                                                                      | Type      |                 | r<br>Tao        | 1           | w           | r           |             | rw          | T40         |  |

| FA <sub>H</sub> | CCU6_TCTR2LReset: 00HTimer Control Register 2 Low                                    | Bit Field | 0               | 113             | STED        |             | T13TEC      |             | T13<br>SSC  | T12<br>SSC  |  |

|                 |                                                                                      | Туре      | r               | r               | W           |             | rw          |             | rw          | rw          |  |

# 3.2.4.12 SSC Registers

The SSC SFRs can be accessed in the standard memory area (RMAP = 0).

| Addr            | Register Name                             | Bit       | 7  | 6  | 5  | 4        | 3    | 2   | 1   | 0   |  |

|-----------------|-------------------------------------------|-----------|----|----|----|----------|------|-----|-----|-----|--|

| RMAP =          | = 0                                       |           |    |    |    |          |      |     |     |     |  |

| A9 <sub>H</sub> | SSC_PISEL Reset: 00 <sub>H</sub>          | Bit Field |    |    | 0  |          |      | CIS | SIS | MIS |  |

|                 | Port Input Select Register                | Туре      |    |    | r  |          |      | rw  | rw  | rw  |  |

| AA <sub>H</sub> | SSC_CONL Reset: 00 <sub>H</sub>           | Bit Field | LB | PO | PH | HB       |      | В   | М   |     |  |

|                 | Control Register Low<br>Programming Mode  | Туре      | rw | rw | rw | rw       | rw   |     |     |     |  |

| AA <sub>H</sub> | SSC_CONL Reset: 00 <sub>H</sub>           | Bit Field |    |    | 0  |          |      | BC  |     |     |  |

|                 | Control Register Low<br>Operating Mode    | Туре      |    |    | r  |          |      | r   | h   |     |  |

| ab <sub>h</sub> | SSC_CONH Reset: 00 <sub>H</sub>           | Bit Field | EN | MS | 0  | AREN     | BEN  | PEN | REN | TEN |  |

|                 | Control Register High<br>Programming Mode | Туре      | rw | rw | r  | rw       | rw   | rw  | rw  | rw  |  |

| ав <sub>Н</sub> | SSC_CONH Reset: 00 <sub>H</sub>           | Bit Field | EN | MS | 0  | BSY      | BE   | PE  | RE  | TE  |  |

|                 | Control Register High<br>Operating Mode   | Туре      | rw | rw | r  | rh       | rwh  | rwh | rwh | rwh |  |

| ac <sub>h</sub> | SSC_TBL Reset: 00 <sub>H</sub>            | Bit Field |    |    |    | TB_V     | ALUE |     |     |     |  |

|                 | Transmitter Buffer Register Low           | Туре      |    |    |    | rv       | W    |     |     |     |  |

| ad <sub>H</sub> | SSC_RBL Reset: 00 <sub>H</sub>            | Bit Field |    |    |    | RB_V     | ALUE |     |     |     |  |

|                 | Receiver Buffer Register Low              | Туре      |    |    |    | r        | h    |     |     |     |  |

| ае <sub>Н</sub> | SSC_BRL Reset: 00 <sub>H</sub>            | Bit Field |    |    |    | BR_VALUE |      |     |     |     |  |

|                 | Baud Rate Timer Reload<br>Register Low    | Туре      |    |    | rw |          |      |     |     |     |  |

| AF <sub>H</sub> | SSC_BRH Reset: 00 <sub>H</sub>            | Bit Field |    |    |    | BR_V     | ALUE |     |     |     |  |

|                 | Baud Rate Timer Reload<br>Register High   | Туре      |    |    |    | r        | N    |     |     |     |  |

### Table 15 SSC Register Overview

## 3.2.4.13 MultiCAN Registers

The MultiCAN SFRs can be accessed in the standard memory area (RMAP = 0).

| Addr                                                                                 | Register Name              | Bit       | 7   | 6   | 5   | 4   | 3    | 2    | 1    | 0    |

|--------------------------------------------------------------------------------------|----------------------------|-----------|-----|-----|-----|-----|------|------|------|------|

| RMAP =                                                                               | = 0                        |           |     |     |     |     |      |      |      |      |

| D8 <sub>H</sub> ADCON Reset: 00 <sub>H</sub><br>CAN Address/Data Control<br>Register |                            | Bit Field | V3  | V2  | V1  | V0  | AUAD |      | BSY  | RWEN |

|                                                                                      |                            | Туре      | rw  | rw  | rw  | rw  | rw   |      | rh   | rw   |

| D9 <sub>H</sub>                                                                      | ADL Reset: 00 <sub>H</sub> | Bit Field | CA9 | CA8 | CA7 | CA6 | CA5  | CA4  | CA3  | CA2  |

|                                                                                      | CAN Address Register Low   | Туре      | rwh | rwh | rwh | rwh | rwh  | rwh  | rwh  | rwh  |

| da <sub>H</sub>                                                                      | ADH Reset: 00 <sub>H</sub> | Bit Field | 0   |     |     |     | CA13 | CA12 | CA11 | CA10 |

|                                                                                      | CAN Address Register High  | Туре      | r   |     |     |     | rwh  | rwh  | rwh  | rwh  |

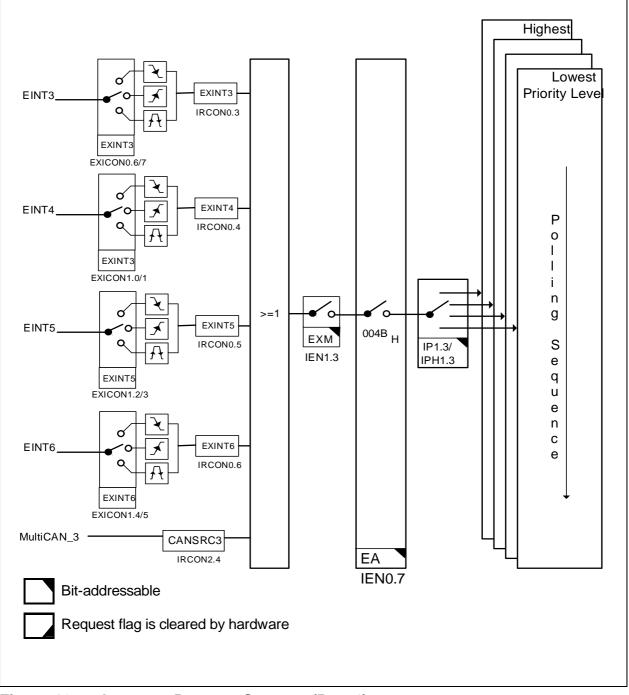

Figure 16 Interrupt Request Sources (Part 4)

Figure 17 Interrupt Request Sources (Part 5)

| Interrupt<br>Source | Vector<br>Address | Assignment for SAA-<br>XC886                          | Enable Bit | SFR  |  |

|---------------------|-------------------|-------------------------------------------------------|------------|------|--|

| XINTR6              | 0033 <sub>H</sub> | MultiCAN Nodes 1 and 2                                | EADC       | IEN1 |  |

|                     |                   | ADC[1:0]                                              |            |      |  |

| XINTR7              | 003B <sub>H</sub> | SSC                                                   | ESSC       |      |  |

| XINTR8              | 0043 <sub>H</sub> | External Interrupt 2                                  | EX2        |      |  |

|                     |                   | T21                                                   |            |      |  |

|                     |                   | CORDIC                                                |            |      |  |

|                     |                   | UART1                                                 |            |      |  |

|                     |                   | UART1 Fractional Divider<br>(Normal Divider Overflow) |            |      |  |

|                     |                   | MDU[1:0]                                              |            |      |  |

| XINTR9              | 004B <sub>H</sub> | External Interrupt 3                                  | EXM        |      |  |

|                     |                   | External Interrupt 4                                  |            |      |  |

|                     |                   | External Interrupt 5                                  |            |      |  |

|                     |                   | External Interrupt 6                                  |            |      |  |

|                     |                   | MultiCAN Node 3                                       |            |      |  |

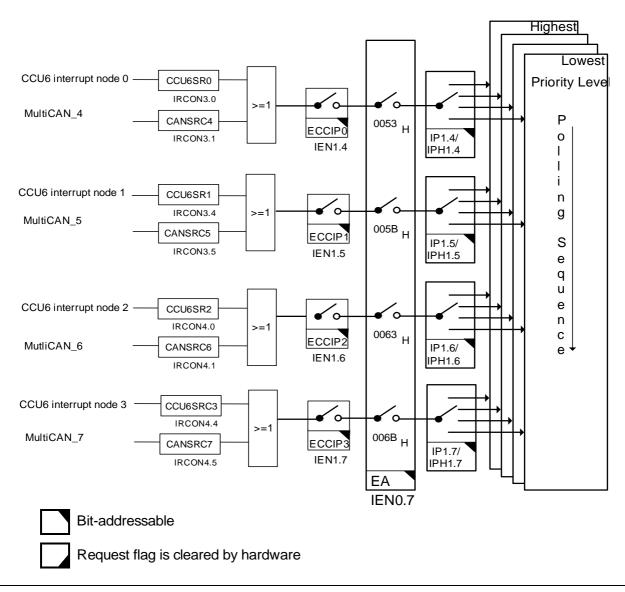

| XINTR10             | 0053 <sub>H</sub> | CCU6 INP0                                             | ECCIP0     |      |  |

|                     |                   | MultiCAN Node 4                                       |            |      |  |

| XINTR11             | 005B <sub>H</sub> | CCU6 INP1                                             | ECCIP1     |      |  |

|                     |                   | MultiCAN Node 5                                       |            |      |  |

| XINTR12             | 0063 <sub>H</sub> | CCU6 INP2                                             | ECCIP2     |      |  |

|                     |                   | MultiCAN Node 6                                       |            |      |  |

| XINTR13             | 006B <sub>H</sub> | CCU6 INP3                                             | ECCIP3     |      |  |

|                     |                   | MultiCAN Node 7                                       |            |      |  |

infineon

#### **Functional Description**

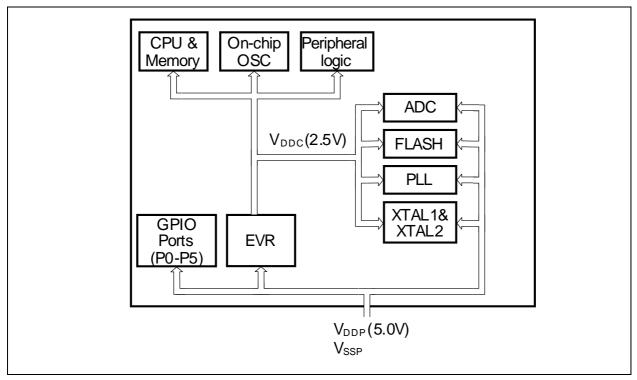

## 3.6 Power Supply System with Embedded Voltage Regulator

The SAA-XC886 microcontroller requires two different levels of power supply:

- 5.0 V for the Embedded Voltage Regulator (EVR) and Ports

- 2.5 V for the core, memory, on-chip oscillator, and peripherals

**Figure 20** shows the SAA-XC886 power supply system. A power supply of 5.0 V must be provided from the external power supply pin. The 2.5 V power supply for the logic is generated by the EVR. The EVR helps to reduce the power consumption of the whole chip and the complexity of the application board design.

The EVR consists of a main voltage regulator and a low power voltage regulator. In active mode, both voltage regulators are enabled. In power-down mode, the main voltage regulator is switched off, while the low power voltage regulator continues to function and provide power supply to the system with low power consumption.

Figure 20 SAA-XC886 Power Supply System

#### **EVR Features**

- Input voltage ( $V_{\text{DDP}}$ ): 5.0 V

- Output voltage ( $V_{DDC}$ ): 2.5 V ± 7.5%

- Low power voltage regulator provided in power-down mode

- $V_{\text{DDC}}$  and  $V_{\text{DDP}}$  prewarning detection

- V<sub>DDC</sub> brownout detection

Table 32

#### **Functional Description**

## 3.18 Timer 2 and Timer 21

**Timer 2 Modes**

Timer 2 and Timer 21 are 16-bit general purpose timers (THL2) that are fully compatible and have two modes of operation, a 16-bit auto-reload mode and a 16-bit one channel capture mode, see **Table 32**. As a timer, the timers count with an input clock of PCLK/12 (if prescaler is disabled). As a counter, they count 1-to-0 transitions on pin T2. In the counter mode, the maximum resolution for the count is PCLK/24 (if prescaler is disabled).

| I able 52          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Auto-reload        | <ul> <li>Up/Down Count Disabled</li> <li>Count up only</li> <li>Start counting from 16-bit reload value, overflow at FFFF<sub>H</sub></li> <li>Reload event configurable for trigger by overflow condition only, or by negative/positive edge at input pin T2EX as well</li> <li>Programmble reload value in register RC2</li> <li>Interrupt is generated with reload event</li> </ul>                                                                                                                                                                                                                                         |

|                    | <ul> <li>Up/Down Count Enabled</li> <li>Count up or down, direction determined by level at input pin T2EX</li> <li>No interrupt is generated</li> <li>Count up <ul> <li>Start counting from 16-bit reload value, overflow at FFFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Programmble reload value in register RC2</li> </ul> </li> <li>Count down <ul> <li>Start counting from FFFF<sub>H</sub>, underflow at value defined in register RC2</li> <li>Reload event triggered by underflow condition <ul> <li>Reload event triggered by underflow condition</li> </ul> </li> </ul></li></ul> |

| Channel<br>capture | <ul> <li>Count up only</li> <li>Start counting from 0000<sub>H</sub>, overflow at FFFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Reload value fixed at 0000<sub>H</sub></li> <li>Capture event triggered by falling/rising edge at pin T2EX</li> <li>Captured timer value stored in register RC2</li> <li>Interrupt is generated with reload or capture event</li> </ul>                                                                                                                                                                                                                      |

## 3.19 Capture/Compare Unit 6

The Capture/Compare Unit 6 (CCU6) provides two independent timers (T12, T13), which can be used for Pulse Width Modulation (PWM) generation, especially for AC-motor control. The CCU6 also supports special control modes for block commutation and multi-phase machines.

The timer T12 can function in capture and/or compare mode for its three channels. The timer T13 can work in compare mode only.

The multi-channel control unit generates output patterns, which can be modulated by T12 and/or T13. The modulation sources can be selected and combined for the signal modulation.

#### **Timer T12 Features**

- Three capture/compare channels, each channel can be used either as a capture or as a compare channel

- Supports generation of a three-phase PWM (six outputs, individual signals for highside and lowside switches)

- 16-bit resolution, maximum count frequency = peripheral clock frequency

- Dead-time control for each channel to avoid short-circuits in the power stage

- Concurrent update of the required T12/13 registers

- Generation of center-aligned and edge-aligned PWM

- Supports single-shot mode

- Supports many interrupt request sources

- Hysteresis-like control mode

#### **Timer T13 Features**

- One independent compare channel with one output

- 16-bit resolution, maximum count frequency = peripheral clock frequency

- Can be synchronized to T12

- Interrupt generation at period-match and compare-match

- Supports single-shot mode

#### Additional Features

- Implements block commutation for Brushless DC-drives

- Position detection via Hall-sensor pattern

- Automatic rotational speed measurement for block commutation

- Integrated error handling

- Fast emergency stop without CPU load via external signal (CTRAP)

- · Control modes for multi-channel AC-drives

- Output levels can be selected and adapted to the power stage

The block diagram of the CCU6 module is shown in **Figure 32**.

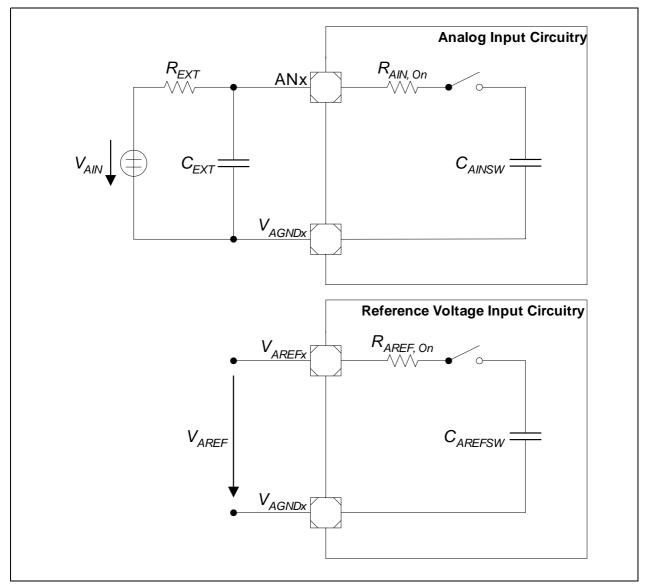

## 4.2.3 ADC Characteristics

The values in the table below are given for an analog power supply between 4.5 V to 5.5 V. All ground pins ( $V_{SS}$ ) must be externally connected to one single star point in the system. The voltage difference between the ground pins must not exceed 200mV.

| Parameter                            | Symbol              |    | Lir                       | nit Val         | ues                        | Unit | Test Conditions/<br>Remarks                                 |  |

|--------------------------------------|---------------------|----|---------------------------|-----------------|----------------------------|------|-------------------------------------------------------------|--|

|                                      |                     |    | min.                      | typ.            | max.                       |      |                                                             |  |

| Analog reference voltage             | $V_{AREF}$          | SR | V <sub>AGND</sub><br>+ 1  | $V_{DDP}$       | V <sub>DDP</sub><br>+ 0.05 | V    | 1)                                                          |  |

| Analog reference ground              | $V_{AGND}$          | SR | V <sub>SS</sub> -<br>0.05 | V <sub>SS</sub> | V <sub>AREF</sub><br>- 1   | V    | 1)                                                          |  |

| Analog input<br>voltage range        | $V_{AIN}$           | SR | $V_{AGND}$                | _               | $V_{AREF}$                 | V    |                                                             |  |

| ADC clocks                           | $f_{\rm ADC}$       |    | _                         | 24              | 25.8                       | MHz  | module clock <sup>1)</sup>                                  |  |

|                                      | f <sub>adci</sub>   |    | -                         | _               | 10                         | MHz  | internal analog clock <sup>1)</sup><br>See <b>Figure 34</b> |  |

| Sample time                          | t <sub>S</sub>      | СС | (2 + IN)<br>$t_{ADCI}$    | PCR0.           | STC) ×                     | μS   | 1)                                                          |  |

| Conversion time                      | t <sub>C</sub>      | CC | See Se                    | ection          | 4.2.3.1                    | μS   | 1)                                                          |  |

| Total unadjusted                     | TUE                 | CC | -                         | _               | 1                          | LSB  | 8-bit conversion <sup>2)</sup>                              |  |

| error                                |                     |    | _                         | _               | 2                          | LSB  | 10-bit conversion <sup>2)</sup>                             |  |

| Differential<br>Nonlinearity         | /EA <sub>DNL</sub>  | CC | -                         | 1               | -                          | LSB  | 10-bit conversion <sup>1)</sup>                             |  |

| Integral<br>Nonlinearity             | /EA <sub>INL</sub>  | CC | -                         | 1               | -                          | LSB  | 10-bit conversion <sup>1)</sup>                             |  |

| Offset                               | /EA <sub>OFF</sub>  | CC | _                         | 1               | -                          | LSB  | 10-bit conversion <sup>1)</sup>                             |  |

| Gain                                 | /EA <sub>GAIN</sub> | CC | -                         | 1               | -                          | LSB  | 10-bit conversion <sup>1)</sup>                             |  |

| Overload current coupling factor for | K <sub>OVA</sub>    | CC | -                         | _               | 1.0 x<br>10 <sup>-4</sup>  | -    | $I_{\rm OV} > 0^{1/3}$                                      |  |

| analog inputs                        |                     |    | -                         | _               | 1.5 x<br>10 <sup>-3</sup>  | -    | $I_{\rm OV} < 0^{1)3)}$                                     |  |

| Overload current coupling factor for | K <sub>OVD</sub>    | CC | -                         | _               | 5.0 x<br>10 <sup>-3</sup>  | -    | $I_{\rm OV} > 0^{1/3}$                                      |  |

| digital I/O pins                     |                     |    | _                         | _               | 1.0 x<br>10 <sup>-2</sup>  | -    | $I_{\rm OV} < 0^{1)3)}$                                     |  |

Table 40ADC Characteristics (Operating Conditions apply;  $V_{DDP} = 5V$  Range)

Figure 38 ADC Input Circuits

## 4.3 AC Parameters

The electrical characteristics of the AC Parameters are detailed in this section.

## 4.3.1 Testing Waveforms

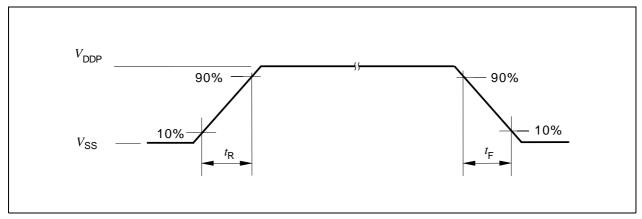

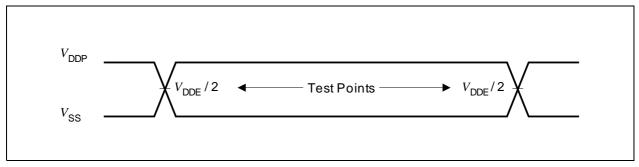

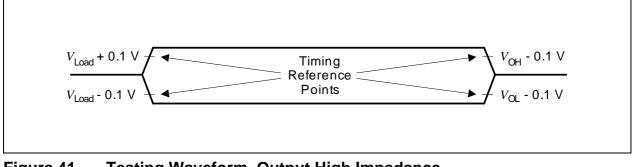

The testing waveforms for rise/fall time, output delay and output high impedance are shown in **Figure 39**, **Figure 40** and **Figure 41**.

Figure 39 Rise/Fall Time Parameters

Figure 40 Testing Waveform, Output Delay

Figure 41 Testing Waveform, Output High Impedance

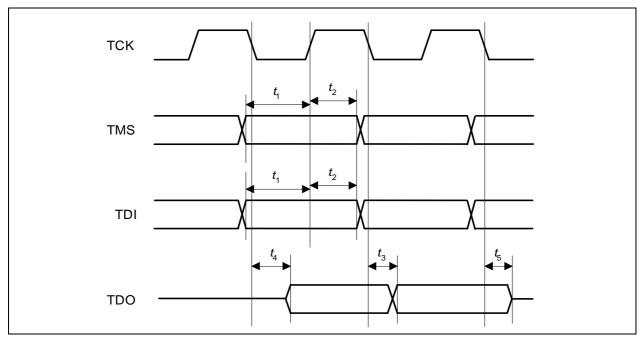

| Table 48 | JTAG Timing (Operating Conditions apply; CL = 50 pF) (cont'd) |

|----------|---------------------------------------------------------------|

|----------|---------------------------------------------------------------|

| Parameter                                   | Symbol                |    | Lir | nits    | Unit | Test<br>Conditions |  |

|---------------------------------------------|-----------------------|----|-----|---------|------|--------------------|--|

|                                             |                       |    | min | min max |      |                    |  |

| TDO high impedance to valid output from TCK | <i>t</i> <sub>4</sub> | CC | -   | 35      | ns   | 1)                 |  |

| TDO valid output to high impedance from TCK | <i>t</i> <sub>5</sub> | CC | -   | 27      | ns   | 1)                 |  |

1) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

Figure 46 JTAG Timing

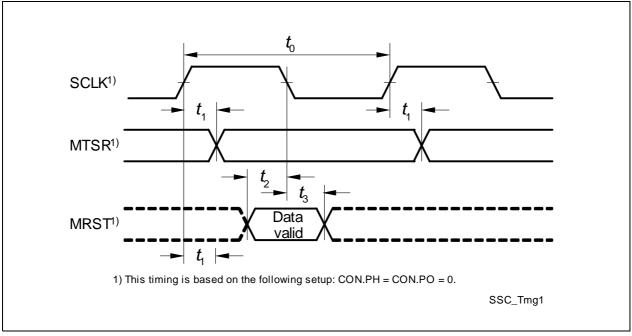

## 4.3.7 SSC Master Mode Timing

Table 49 provides the characteristics of the SSC timing in the SAA-XC886.

| Table 49 | SSC Master Mode Timing (Operating Conditions apply; CL = 50 pF) |

|----------|-----------------------------------------------------------------|

|----------|-----------------------------------------------------------------|

| Parameter            | Symbol                |    | Limi               | t Values | Unit | Test       |  |

|----------------------|-----------------------|----|--------------------|----------|------|------------|--|

|                      |                       |    | min.               | max.     |      | Conditions |  |

| SCLK clock period    | t <sub>0</sub>        | CC | 2*T <sub>SSC</sub> | _        | ns   | 1)2)       |  |

| MTSR delay from SCLK | t <sub>1</sub>        | CC | 0                  | 8        | ns   | 2)         |  |

| MRST setup to SCLK   | <i>t</i> <sub>2</sub> | SR | 24                 | -        | ns   | 2)         |  |

| MRST hold from SCLK  | <i>t</i> <sub>3</sub> | SR | 0                  | -        | ns   | 2)         |  |

1)  $T_{SSCmin} = T_{CPU} = 1/f_{CPU}$ . When  $f_{CPU} = 24$  MHz,  $t_0 = 83.3$  ns.  $T_{CPU}$  is the CPU clock period.

2) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

Figure 47 SSC Master Mode Timing