#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | PowerPC e300                                                            |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                          |

| Speed                           | 667MHz                                                                  |

| Co-Processors/DSP               | Communications; QUICC Engine, Security; SEC                             |

| RAM Controllers                 | DDR, DDR2                                                               |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | -                                                                       |

| Ethernet                        | 10/100/1000Mbps (1)                                                     |

| SATA                            | -                                                                       |

| USB                             | USB 1.x (1)                                                             |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                        |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                        |

| Security Features               | Cryptography, Random Number Generator                                   |

| Package / Case                  | 740-LBGA                                                                |

| Supplier Device Package         | 740-TBGA (37.5x37.5)                                                    |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8360evvalfg |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

wide range of protocols including ATM, Ethernet, HDLC, and POS. The QUICC Engine module's enhanced interworking eases the transition and reduces investment costs from ATM to IP based systems. The other major features include a dual DDR SDRAM memory controller for the MPC8360E, which allows equipment providers to partition system parameters and data in an extremely efficient way, such as using one 32-bit DDR memory controller for control plane processing and the other for data plane processing. The MPC8358E has a single DDR SDRAM memory controller. The MPC8360E/58E also offers a 32-bit PCI controller, a flexible local bus, and a dedicated security engine.

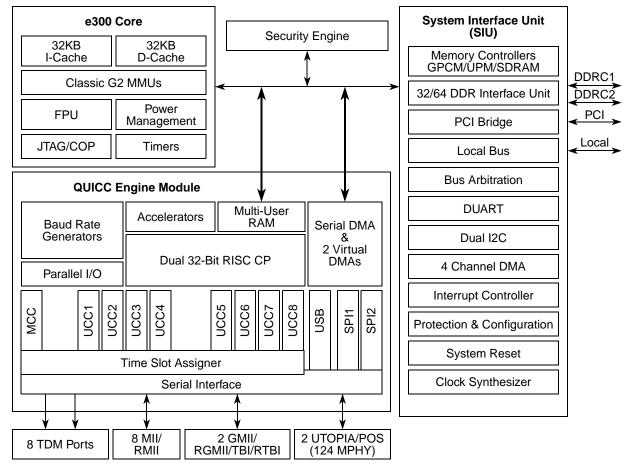

This figure shows the MPC8360Eblock diagram.

Figure 1. MPC8360E Block Diagram

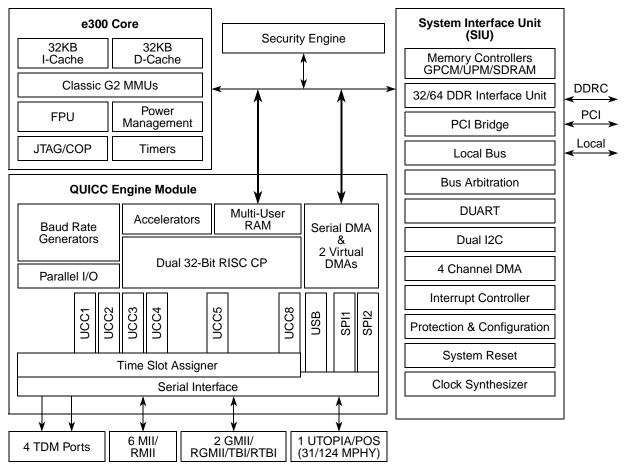

This figure shows the MPC8358E block diagram.

Figure 2. MPC8358E Block Diagram

Major features of the MPC8360E/58E are as follows:

- e300 PowerPC processor core (enhanced version of the MPC603e core)

- Operates at up to 667 MHz (for the MPC8360E) and 400 MHz (for the MPC8358E)

- High-performance, superscalar processor core

- Floating-point, integer, load/store, system register, and branch processing units

- 32-Kbyte instruction cache, 32-Kbyte data cache

- Lockable portion of L1 cache

- Dynamic power management

- Software-compatible with the Freescale processor families implementing the Power Architecture<sup>™</sup> technology

- QUICC Engine unit

- Two 32-bit RISC controllers for flexible support of the communications peripherals, each operating up to 500 MHz (for the MPC8360E) and 400 MHz (for the MPC8358E)

- Serial DMA channel for receive and transmit on all serial channels

- QUICC Engine module peripheral request interface (for SEC, PCI, IEEE Std. 1588<sup>TM</sup>)

- Eight universal communication controllers (UCCs) on the MPC8360E and six UCCs on the MPC8358E supporting the following protocols and interfaces (not all of them simultaneously):

- IEEE 1588 protocol supported

- 10/100 Mbps Ethernet/IEEE Std. 802.3<sup>TM</sup> CDMA/CS interface through a media-independent interface (MII, RMII, RGMII)<sup>1</sup>

- 1000 Mbps Ethernet/IEEE 802.3 CDMA/CS interface through a media-independent interface (GMII, RGMII, TBI, RTBI) on UCC1 and UCC2

- 9.6-Kbyte jumbo frames

- ATM full-duplex SAR, up to 622 Mbps (OC-12/STM-4), AAL0, AAL1, and AAL5 in accordance ITU-T I.363.5

- ATM AAL2 CPS, SSSAR, and SSTED up to 155 Mbps (OC-3/STM-1) Mbps full duplex (with 4 CPS packets per cell) in accordance ITU-T I.366.1 and I.363.2

- ATM traffic shaping for CBR, VBR, UBR, and GFR traffic types compatible with ATM forum TM4.1 for up to 64-Kbyte simultaneous ATM channels

- ATM AAL1 structured and unstructured circuit emulation service (CES 2.0) in accordance with ITU-T I.163.1 and ATM Forum af-vtoa-00-0078.000

- IMA (Inverse Multiplexing over ATM) for up to 31 IMA links over 8 IMA groups in accordance with the ATM forum AF-PHY-0086.000 (Version 1.0) and AF-PHY-0086.001 (Version 1.1)

- ATM Transmission Convergence layer support in accordance with ITU-T I.432

- ATM OAM handling features compatible with ITU-T I.610

- PPP, Multi-Link (ML-PPP), Multi-Class (MC-PPP) and PPP mux in accordance with the following RFCs: 1661, 1662, 1990, 2686, and 3153

- IP support for IPv4 packets including TOS, TTL, and header checksum processing

- Ethernet over first mile IEEE 802.3ah

- Shim header

- Ethernet-to-Ethernet/AAL5/AAL2 inter-working

- L2 Ethernet switching using MAC address or IEEE Std. 802.1P/Q<sup>™</sup> VLAN tags

- ATM (AAL2/AAL5) to Ethernet (IP) interworking in accordance with RFC2684 including bridging of ATM ports to Ethernet ports

- Extensive support for ATM statistics and Ethernet RMON/MIB statistics

- AAL2 protocol rate up to 4 CPS at OC-3/STM-1 rate

- Packet over Sonet (POS) up to 622-Mbps full-duplex 124 MultiPHY

- POS hardware; microcode must be loaded as an IRAM package

- Transparent up to 70-Mbps full-duplex

- HDLC up to 70-Mbps full-duplex

- HDLC BUS up to 10 Mbps

- Asynchronous HDLC

- UART

- BISYNC up to 2 Mbps

- User-programmable Virtual FIFO size

- QUICC multichannel controller (QMC) for 64 TDM channels

- One multichannel communication controller (MCC) only on the MPC8360E supporting the following:

- 256 HDLC or transparent channels

- 128 SS7 channels

- Almost any combination of subgroups can be multiplexed to single or multiple TDM interfaces

- Two UTOPIA/POS interfaces on the MPC8360E supporting 124 MultiPHY each (optional 2\*128 MultiPHY with extended address) and one UTOPIA/POS interface on the MPC8358E supporting 31/124 MultiPHY

- Two serial peripheral interfaces (SPI); SPI2 is dedicated to Ethernet PHY management

1.SMII or SGMII media-independent interface is not currently supported.

**Overall DC Electrical Characteristics**

# 2.1 **Overall DC Electrical Characteristics**

This section covers the ratings, conditions, and other characteristics.

# 2.1.1 Absolute Maximum Ratings

This table provides the absolute maximum ratings.

#### Table 1. Absolute Maximum Ratings<sup>1</sup>

|                                                                         | Characteristic                                                                                              | Symbol                             | Max Value                        | Unit | Notes |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------------|------|-------|

| Core and PLL supply                                                     | voltage for                                                                                                 | V <sub>DD</sub> & AV <sub>DD</sub> | -0.3 to 1.32                     | V    | —     |

|                                                                         | t Number with<br>label of AD=266MHz and AG=400MHz &<br>ency label of E=300MHz & G=400MHz                    |                                    |                                  |      |       |

|                                                                         | t Number with<br>label of AG=400MHz and AJ=533MHz &<br>ency label of G=400MHz                               |                                    |                                  |      |       |

| Core and PLL supply voltage for                                         |                                                                                                             | V <sub>DD</sub> & AV <sub>DD</sub> | -0.3 to 1.37                     | V    | —     |

| MPC8360 device Part<br>Processor Frequency<br>Frequency label of H=     | label of AL=667MHz and QUICC Engine                                                                         |                                    |                                  |      |       |

| DDR and DDR2 DRA                                                        | M I/O voltage<br>DDR<br>DDR2                                                                                | GV <sub>DD</sub>                   | -0.3 to 2.75<br>-0.3 to 1.89     | V    | —     |

| Three-speed Ethernet                                                    | I/O, MII management voltage                                                                                 | LV <sub>DD</sub>                   | -0.3 to 3.63                     | V    | —     |

| PCI, local bus, DUAR <sup>-</sup><br>I <sup>2</sup> C, SPI, and JTAG I/ | Γ, system control and power management,<br>) voltage                                                        | OV <sub>DD</sub>                   | -0.3 to 3.63                     | V    | —     |

| Input voltage                                                           | DDR DRAM signals                                                                                            | MV <sub>IN</sub>                   | -0.3 to (GV <sub>DD</sub> + 0.3) | V    | 2, 5  |

|                                                                         | DDR DRAM reference                                                                                          | MV <sub>REF</sub>                  | -0.3 to (GV <sub>DD</sub> + 0.3) | V    | 2, 5  |

|                                                                         | Three-speed Ethernet signals                                                                                | LV <sub>IN</sub>                   | -0.3 to (LV <sub>DD</sub> + 0.3) | V    | 4, 5  |

|                                                                         | Local bus, DUART, CLKIN, system<br>control and power management, I <sup>2</sup> C, SPI,<br>and JTAG signals | OV <sub>IN</sub>                   | -0.3 to (OV <sub>DD</sub> + 0.3) | V    | 3, 5  |

|                                                                         | PCI                                                                                                         | OV <sub>IN</sub>                   | -0.3 to (OV <sub>DD</sub> + 0.3) | V    | 6     |

| Characteristic                                                                                          | Symbol           | Recommended<br>Value   | Unit | Notes |

|---------------------------------------------------------------------------------------------------------|------------------|------------------------|------|-------|

| PCI, local bus, DUART, system control and power management, I <sup>2</sup> C, SPI, and JTAG I/O voltage | OV <sub>DD</sub> | 3.3 V ± 330 mV         | V    | Ι     |

| Junction temperature                                                                                    | TJ               | 0 to 105<br>-40 to 105 | °C   | 2     |

#### Table 2. Recommended Operating Conditions (continued)

Notes:

- 1. GV<sub>DD</sub>, LV<sub>DD</sub>, OV<sub>DD</sub>, AV<sub>DD</sub>, and V<sub>DD</sub> must track each other and must vary in the same direction—either in the positive or negative direction.

- The operating conditions for junction temperature, T<sub>J</sub>, on the 600/333/400 MHz and 500/333/500 MHz on rev. 2.0 silicon is 0° to 70 °C. Refer to Errata General9 in *Chip Errata for the MPC8360E, Rev. 1*.

- 3. For more information on Part Numbering, refer to Table 80.

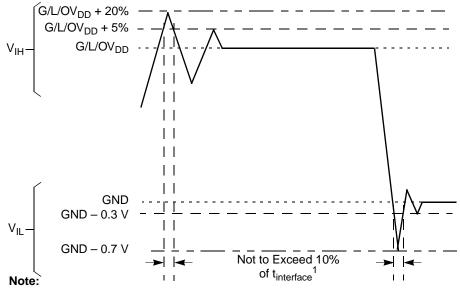

This figure shows the undershoot and overshoot voltages at the interfaces of the device.

1. Note that  $t_{\mbox{interface}}$  refers to the clock period associated with the bus clock interface.

Figure 3. Overshoot/Undershoot Voltage for  $GV_{DD}/OV_{DD}/LV_{DD}$

Power Sequencing

# 2.2.1 Power-Up Sequencing

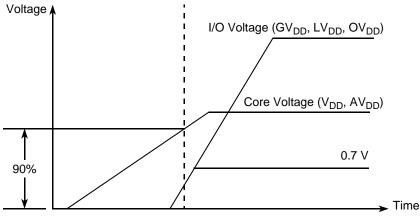

MPC8360E/58E does not require the core supply voltage ( $V_{DD}$  and  $AV_{DD}$ ) and I/O supply voltages ( $GV_{DD}$ ,  $LV_{DD}$ , and  $OV_{DD}$ ) to be applied in any particular order. During the power ramp up, before the power supplies are stable and if the I/O voltages are supplied before the core voltage, there may be a period of time that all input and output pins are actively be driven and cause contention and excessive current from 3A to 5A. In order to avoid actively driving the I/O pins and to eliminate excessive current draw, apply the core voltage ( $V_{DD}$ ) before the I/O voltage ( $GV_{DD}$ ,  $LV_{DD}$ , and  $OV_{DD}$ ) and assert PORESET before the power supplies fully ramp up. In the case where the core voltage is applied first, the core voltage supply must rise to 90% of its nominal value before the I/O supplies reach 0.7 V, see this figure.

Figure 5. Power Sequencing Example

I/O voltage supplies (GV<sub>DD</sub>, LV<sub>DD</sub>, and OV<sub>DD</sub>) do not have any ordering requirements with respect to one another.

## 2.2.2 Power-Down Sequencing

The MPC8360E/58E does not require the core supply voltage and I/O supply voltages to be powered down in any particular order.

# **3 Power Characteristics**

The estimated typical power dissipation values are shown in these tables.

| Table 4. MPC8360E TBG/ | Core Power Dissipation <sup>1</sup> |

|------------------------|-------------------------------------|

|------------------------|-------------------------------------|

| Core<br>Frequency (MHz) | CSB<br>Frequency (MHz) | QUICC Engine<br>Frequency (MHz) | Typical | Maximum | Unit | Notes      |

|-------------------------|------------------------|---------------------------------|---------|---------|------|------------|

| 266                     | 266                    | 500                             | 5.0     | 5.6     | W    | 2, 3, 5    |

| 400                     | 266                    | 400                             | 4.5     | 5.0     | W    | 2, 3, 4    |

| 533                     | 266                    | 400                             | 4.8     | 5.3     | W    | 2, 3, 4    |

| 667                     | 333                    | 400                             | 5.8     | 6.3     | W    | 3, 6, 7, 8 |

| 500                     | 333                    | 500                             | 5.9     | 6.4     | W    | 3, 6, 7, 8 |

**DC Electrical Characteristics**

# 4.1 DC Electrical Characteristics

This table provides the clock input (CLKIN/PCI\_SYNC\_IN) DC timing specifications for the device.

| Parameter                 | Condition                                                                                   | Symbol          | Min  | Max                    | Unit |

|---------------------------|---------------------------------------------------------------------------------------------|-----------------|------|------------------------|------|

| Input high voltage        | —                                                                                           | V <sub>IH</sub> | 2.7  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage         | —                                                                                           | V <sub>IL</sub> | -0.3 | 0.4                    | V    |

| CLKIN input current       | 0 V ≤V <sub>IN</sub> ≤OV <sub>DD</sub>                                                      | I <sub>IN</sub> | —    | ±10                    | μA   |

| PCI_SYNC_IN input current | 0 V ≤V <sub>IN</sub> ≤0.5V or<br>OV <sub>DD</sub> – 0.5V ≤V <sub>IN</sub> ≤OV <sub>DD</sub> | I <sub>IN</sub> | _    | ±10                    | μA   |

| PCI_SYNC_IN input current | 0.5 V ≤V <sub>IN</sub> ≤OV <sub>DD</sub> – 0.5 V                                            | I <sub>IN</sub> | —    | ±100                   | μA   |

## 4.2 AC Electrical Characteristics

The primary clock source for the device can be one of two inputs, CLKIN or PCI\_CLK, depending on whether the device is configured in PCI host or PCI agent mode. This table provides the clock input (CLKIN/PCI\_CLK) AC timing specifications for the device.

| Table 8. | <b>CLKIN</b> | AC | Timing | Specifications |

|----------|--------------|----|--------|----------------|

|----------|--------------|----|--------|----------------|

| Parameter/Condition              | Symbol                               | Min | Typical | Max   | Unit | Notes |

|----------------------------------|--------------------------------------|-----|---------|-------|------|-------|

| CLKIN/PCI_CLK frequency          | f <sub>CLKIN</sub>                   | —   | _       | 66.67 | MHz  | 1     |

| CLKIN/PCI_CLK cycle time         | t <sub>CLKIN</sub>                   | 15  | —       | _     | ns   | —     |

| CLKIN/PCI_CLK rise and fall time | t <sub>KH</sub> , t <sub>KL</sub>    | 0.6 | 1.0     | 2.3   | ns   | 2     |

| CLKIN/PCI_CLK duty cycle         | t <sub>KHK</sub> /t <sub>CLKIN</sub> | 40  | —       | 60    | %    | 3     |

| CLKIN/PCI_CLK jitter             | _                                    | —   | —       | ±150  | ps   | 4, 5  |

#### Notes:

- 1. **Caution:** The system, core, USB, security, and 10/100/1000 Ethernet must not exceed their respective maximum or minimum operating frequencies.

- 2. Rise and fall times for CLKIN/PCI\_CLK are measured at 0.4 V and 2.7 V.

- 3. Timing is guaranteed by design and characterization.

- 4. This represents the total input jitter-short term and long term-and is guaranteed by design.

- 5. The CLKIN/PCI\_CLK driver's closed loop jitter bandwidth should be <500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track CLKIN drivers with the specified jitter.

# 4.3 Gigabit Reference Clock Input Timing

This table provides the Gigabit reference clocks (GTX\_CLK125) AC timing specifications.

#### Table 9. GTX\_CLK125 AC Timing Specifications

At recommended operating conditions with LV<sub>DD</sub> = 2.5  $\pm$  0.125 mV/ 3.3 V  $\pm$  165 mV

| Parameter/Condition   | Symbol            | Min | Typical | Max | Unit | Notes |

|-----------------------|-------------------|-----|---------|-----|------|-------|

| GTX_CLK125 frequency  | t <sub>G125</sub> | -   | 125     | _   | MHz  | —     |

| GTX_CLK125 cycle time | t <sub>G125</sub> |     | 8       |     | ns   | —     |

#### DDR and DDR2 SDRAM AC Electrical Characteristics

| Parameter/Condition                                     | Symbol            | Min                      | Мах                      | Unit | Notes |

|---------------------------------------------------------|-------------------|--------------------------|--------------------------|------|-------|

| Input high voltage                                      | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.18 | GV <sub>DD</sub> + 0.3   | V    |       |

| Input low voltage                                       | V <sub>IL</sub>   | -0.3                     | MV <sub>REF</sub> – 0.18 | V    | _     |

| Output leakage current                                  | I <sub>OZ</sub>   | —                        | ±10                      | μA   | 4     |

| Output high current (V <sub>OUT</sub> = 1.95 V)         | I <sub>ОН</sub>   | -15.2                    |                          | mA   | —     |

| Output low current (V <sub>OUT</sub> = 0.35 V)          | I <sub>OL</sub>   | 15.2                     | _                        | mA   | _     |

| MV <sub>REF</sub> input leakage current                 | I <sub>VREF</sub> | —                        | ±10                      | μA   | —     |

| Input current (0 V ≰⁄ <sub>IN</sub> ≤OV <sub>DD</sub> ) | I <sub>IN</sub>   | —                        | ±10                      | μA   | _     |

#### Table 16. DDR SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 2.5 V (continued)

#### Notes:

1.  $GV_{DD}$  is expected to be within 50 mV of the DRAM  $GV_{DD}$  at all times.

- 2.  $MV_{REF}$  is expected to be equal to  $0.5 \times GV_{DD}$ , and to track  $GV_{DD}$  DC variations as measured at the receiver. Peak-to-peak noise on  $MV_{REF}$  may not exceed ±2% of the DC value.

- 3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail should track variations in the DC level of MV<sub>REF</sub>.

- 4. Output leakage is measured with all outputs disabled, 0 V  $\leq$ V<sub>OUT</sub>  $\leq$ GV<sub>DD</sub>.

This table provides the DDR capacitance when  $GV_{DD}(typ) = 2.5$  V.

#### Table 17. DDR SDRAM Capacitance for GV<sub>DD</sub>(typ) = 2.5 V

| Parameter/Condition                     | Symbol           | Min | Мах | Unit | Notes |

|-----------------------------------------|------------------|-----|-----|------|-------|

| Input/output capacitance: DQ, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1     |

| Delta input/output capacitance: DQ, DQS | C <sub>DIO</sub> | —   | 0.5 | pF   | 1     |

Note:

1. This parameter is sampled.  $GV_{DD}$  = 2.5 V ± 0.125 V, f = 1 MHz, T<sub>A</sub> = 25°C, V<sub>OUT</sub> =  $GV_{DD}/2$ , V<sub>OUT</sub> (peak-to-peak) = 0.2 V.

# 6.2 DDR and DDR2 SDRAM AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR and DDR2 SDRAM interface.

## 6.2.1 DDR and DDR2 SDRAM Input AC Timing Specifications

This table provides the input AC timing specifications for the DDR2 SDRAM interface when  $GV_{DD}(typ) = 1.8 V$ .

#### Table 18. DDR2 SDRAM Input AC Timing Specifications for GV<sub>DD</sub>(typ) = 1.8 V

At recommended operating conditions with  $GV_{DD}$  of 1.8 V ± 5%.

| Parameter             | Symbol          | Min                      | Мах                      | Unit | Notes |

|-----------------------|-----------------|--------------------------|--------------------------|------|-------|

| AC input low voltage  | V <sub>IL</sub> | _                        | MV <sub>REF</sub> – 0.25 | V    | —     |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.25 |                          | V    | —     |

#### GMII, MII, RMII, TBI, RGMII, and RTBI AC Timing Specifications

Physical Layer Device Specification Version 1.2a (9/22/2000). The electrical characteristics for the MDIO and MDC are specified in Section 8.3, "Ethernet Management Interface Electrical Characteristics."

## 8.1.1 10/100/1000 Ethernet DC Electrical Characteristics

The electrical characteristics specified here apply to media independent interface (MII), reduced gigabit media independent interface (RGMII), reduced ten-bit interface (RTBI), reduced media independent interface (RMII) signals, management data input/output (MDIO) and management data clock (MDC).

The MII and RMII interfaces are defined for 3.3 V, while the RGMII and RTBI interfaces can be operated at 2.5 V. The RGMII and RTBI interfaces follow the *Reduced Gigabit Media-Independent Interface (RGMII) Specification Version 1.3*. The RMII interface follows the *RMII Consortium RMII Specification Version 1.2*.

Table 25. RGMII/RTBI, GMII, TBI, MII, and RMII DC Electrical Characteristics (when operating at 3.3 V)

| Parameter            | Symbol           | Conditions                |                        | Min  | Max                    | Unit | Notes |

|----------------------|------------------|---------------------------|------------------------|------|------------------------|------|-------|

| Supply voltage 3.3 V | LV <sub>DD</sub> | _                         |                        | 2.97 | 3.63                   | V    | 1     |

| Output high voltage  | V <sub>OH</sub>  | I <sub>OH</sub> = -4.0 mA | LV <sub>DD</sub> = Min | 2.40 | LV <sub>DD</sub> + 0.3 | V    | _     |

| Output low voltage   | V <sub>OL</sub>  | I <sub>OL</sub> = 4.0 mA  | LV <sub>DD</sub> = Min | GND  | 0.50                   | V    | _     |

| Input high voltage   | V <sub>IH</sub>  | _                         | —                      | 2.0  | LV <sub>DD</sub> + 0.3 | V    | _     |

| Input low voltage    | V <sub>IL</sub>  | _                         | —                      | -0.3 | 0.90                   | V    | _     |

| Input current        | I <sub>IN</sub>  | 0 V ≤V <sub>II</sub>      | N ≤LV <sub>DD</sub>    | —    | ±10                    | μA   | -     |

#### Note:

1. GMII/MII pins that are not needed for RGMII, RMII, or RTBI operation are powered by the OV<sub>DD</sub> supply.

| Table 26. RGMII/RTBI DC Electrical Characteristics | (when operating at 2.5 V) |

|----------------------------------------------------|---------------------------|

|----------------------------------------------------|---------------------------|

| Parameters           | Symbol           | Conditions                |                     | Min       | Max                    | Unit |

|----------------------|------------------|---------------------------|---------------------|-----------|------------------------|------|

| Supply voltage 2.5 V | LV <sub>DD</sub> | —                         |                     | 2.37      | 2.63                   | V    |

| Output high voltage  | V <sub>OH</sub>  | I <sub>OH</sub> = -1.0 mA | $LV_{DD} = Min$     | 2.00      | LV <sub>DD</sub> + 0.3 | V    |

| Output low voltage   | V <sub>OL</sub>  | I <sub>OL</sub> = 1.0 mA  | $LV_{DD} = Min$     | GND – 0.3 | 0.40                   | V    |

| Input high voltage   | V <sub>IH</sub>  | —                         | $LV_{DD} = Min$     | 1.7       | LV <sub>DD</sub> + 0.3 | V    |

| Input low voltage    | V <sub>IL</sub>  | —                         | $LV_{DD} = Min$     | -0.3      | 0.70                   | V    |

| Input current        | I <sub>IN</sub>  | 0 V ≤V <sub>II</sub>      | N ≤LV <sub>DD</sub> | —         | ±10                    | μA   |

# 8.2 GMII, MII, RMII, TBI, RGMII, and RTBI AC Timing Specifications

The AC timing specifications for GMII, MII, TBI, RGMII, and RTBI are presented in this section.

## 8.2.1 GMII Timing Specifications

This sections describe the GMII transmit and receive AC timing specifications.

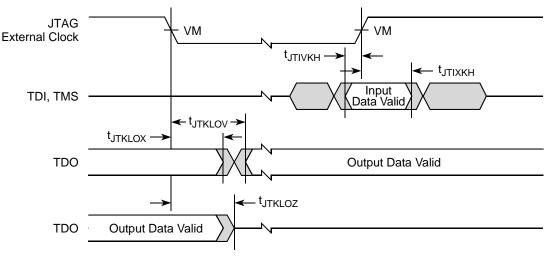

This figure provides the test access port timing diagram.

VM = Midpoint Voltage (OV<sub>DD</sub>/2)

Figure 33. Test Access Port Timing Diagram

# 11 I<sup>2</sup>C

This section describes the DC and AC electrical characteristics for the  $I^2C$  interface of the MPC8360E/58E.

# 11.1 I<sup>2</sup>C DC Electrical Characteristics

This table provides the DC electrical characteristics for the  $I^2C$  interface of the device.

#### Table 44. I<sup>2</sup>C DC Electrical Characteristics

At recommended operating conditions with  $OV_{DD}$  of 3.3 V ± 10%.

| Parameter                                                                                     | Symbol              | Min                   | Max                    | Unit | Notes |

|-----------------------------------------------------------------------------------------------|---------------------|-----------------------|------------------------|------|-------|

| Input high voltage level                                                                      | V <sub>IH</sub>     | $0.7 	imes OV_{DD}$   | OV <sub>DD</sub> + 0.3 | V    | —     |

| Input low voltage level                                                                       | V <sub>IL</sub>     | -0.3                  | $0.3 	imes OV_{DD}$    | V    | —     |

| Low level output voltage                                                                      | V <sub>OL</sub>     | 0                     | 0.4                    | V    | 1     |

| Output fall time from $V_{IH}(min)$ to $V_{IL}(max)$ with a bus capacitance from 10 to 400 pF | <sup>t</sup> I2KLKV | $20 + 0.1 \times C_B$ | 250                    | ns   | 2     |

| Pulse width of spikes which must be suppressed by the input filter                            | t <sub>i2KHKL</sub> | 0                     | 50                     | ns   | 3     |

| Capacitance for each I/O pin                                                                  | CI                  | —                     | 10                     | pF   | —     |

| Input current (0 V ≤V <sub>IN</sub> ≤OV <sub>DD</sub> )                                       | I <sub>IN</sub>     | —                     | ±10                    | μA   | 4     |

#### Notes:

1. Output voltage (open drain or open collector) condition = 3 mA sink current.

- 2.  $C_B$  = capacitance of one bus line in pF.

- 3. Refer to the MPC8360E Integrated Communications Processor Reference Manual for information on the digital filter used.

- 4. I/O pins obstruct the SDA and SCL lines if OV<sub>DD</sub> is switched off.

**Pinout Listings**

#### Table 66. MPC8360E TBGA Pinout Listing (continued)

| Signal                                         | Package Pin Number                | Pin Type | Power<br>Supply    | Notes |

|------------------------------------------------|-----------------------------------|----------|--------------------|-------|

| LCLK[2]/LCS[7]                                 | G37                               | 0        | OV <sub>DD</sub>   | —     |

| LSYNC_OUT                                      | F34                               | 0        | OV <sub>DD</sub>   | —     |

| LSYNC_IN                                       | G35                               | I        | OV <sub>DD</sub>   | _     |

|                                                | Programmable Interrupt Controller |          |                    | 1     |

| MCP_OUT                                        | E34                               | 0        | OV <sub>DD</sub>   | 2     |

| IRQ0/MCP_IN                                    | C37                               | I        | OV <sub>DD</sub>   | —     |

| IRQ[1]/M1SRCID[4]/M2SRCID[4]/<br>LSRCID[4]     | F35                               | I/O      | OV <sub>DD</sub>   | —     |

| IRQ[2]/M1DVAL/M2DVAL/LDVAL                     | F36                               | I/O      | OV <sub>DD</sub>   | —     |

| IRQ[3]/CORE_SRESET                             | H34                               | I/O      | OV <sub>DD</sub>   | —     |

| IRQ[4:5]                                       | G33, G32                          | I/O      | OV <sub>DD</sub>   | —     |

| IRQ[6]/LCS[6]/CKSTOP_OUT                       | E35                               | I/O      | OV <sub>DD</sub>   | —     |

| IRQ[7]/LCS[7]/CKSTOP_IN                        | H36                               | I/O      | OV <sub>DD</sub>   | —     |

|                                                | DUART                             |          |                    | 1     |

| UART1_SOUT/M1SRCID[0]/<br>M2SRCID[0]/LSRCID[0] | E32                               | 0        | OV <sub>DD</sub>   | —     |

| UART1_SIN/M1SRCID[1]/<br>M2SRCID[1]/LSRCID[1]  | B34                               | I/O      | OV <sub>DD</sub>   | _     |

| UART1_CTS/M1SRCID[2]/<br>M2SRCID[2]/LSRCID[2]  | C34                               | I/O      | OV <sub>DD</sub>   | —     |

| UART1_RTS/M1SRCID[3]/<br>M2SRCID[3]/LSRCID[3]  | A35                               | 0        | OV <sub>DD</sub>   | _     |

|                                                | I <sup>2</sup> C Interface        |          |                    |       |

| IIC1_SDA                                       | D34                               | I/O      | OV <sub>DD</sub>   | 2     |

| IIC1_SCL                                       | B35                               | I/O      | OV <sub>DD</sub>   | 2     |

| IIC2_SDA                                       | E33                               | I/O      | OV <sub>DD</sub>   | 2     |

| IIC2_SCL                                       | C35                               | I/O      | OV <sub>DD</sub>   | 2     |

|                                                | QUICC Engine Block                |          |                    |       |

| CE_PA[0]                                       | F8                                | I/O      | LV <sub>DD0</sub>  | _     |

| CE_PA[1:2]                                     | AH1, AG5                          | I/O      | OV <sub>DD</sub>   |       |

| CE_PA[3:7]                                     | F6, D4, C3, E5, A3                | I/O      | LV <sub>DD</sub> 0 | _     |

| CE_PA[8]                                       | AG3                               | I/O      | OV <sub>DD</sub>   |       |

| CE_PA[9:12]                                    | F7, B3, E6, B4                    | I/O      | LV <sub>DD</sub> 0 | _     |

| CE_PA[13:14]                                   | AG1, AF6                          | I/O      | OV <sub>DD</sub>   | _     |

| CE_PA[15]                                      | B2                                | I/O      | LV <sub>DD</sub> 0 | _     |

| CE_PA[16]                                      | AF4                               | I/O      | OV <sub>DD</sub>   | _     |

| CE_PA[17:21]                                   | B16, A16, E17, A17, B17           | I/O      | LV <sub>DD</sub> 1 | —     |

#### Table 67. MPC8358E TBGA Pinout Listing (continued)

| Signal             | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pin Type                                                        | Power<br>Supply    | Notes |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------|-------|

| PORESET            | L37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                               | OV <sub>DD</sub>   |       |

| HRESET             | L36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I/O                                                             | OV <sub>DD</sub>   | 1     |

| SRESET             | M33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I/O                                                             | OV <sub>DD</sub>   | 2     |

|                    | Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                 |                    |       |

| THERM0             | AP19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I                                                               | GV <sub>DD</sub>   | —     |

| THERM1             | AT31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I                                                               | GV <sub>DD</sub>   | —     |

|                    | Power and Ground Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                 |                    |       |

| AV <sub>DD</sub> 1 | K35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power for<br>LBIU DLL<br>(1.2 V)                                | AV <sub>DD</sub> 1 | _     |

| AV <sub>DD</sub> 2 | K36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power for<br>CE PLL<br>(1.2 V)                                  | AV <sub>DD</sub> 2 | _     |

| AV <sub>DD</sub> 5 | AM29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Power for<br>e300 PLL<br>(1.2 V)                                | AV <sub>DD</sub> 5 | _     |

| AV <sub>DD</sub> 6 | К37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power for<br>system<br>PLL (1.2 V)                              | AV <sub>DD</sub> 6 | _     |

| GND                | <ul> <li>A2, A8, A13, A19, A22, A25, A31, A33, A36, B7,<br/>B12, B24, B27, B30, C4, C6, C9, C15, C26, C32,<br/>D3, D8, D11, D14, D17, D19, D23, D27, E7, E13,<br/>E25, E30, E36, F4, F37, G34, H1, H5, H32, H33, J4,<br/>J32, J37, K1, L3, L5, L33, L34, M1, M34, M35, N37,<br/>P2, P5, P35, P36, R4, T3, U1, U5, U35, V37, W1,<br/>W4, W33, W36, Y34, AA3, AA5, AC3, AC32, AC35,<br/>AD1, AD37, AE4, AE34, AE36, AF33, AG4, AG6,<br/>AG32, AH35, AJ1, AJ4, AJ32, AJ35, AJ37, AK36,<br/>AL3, AL34, AM4, AN6, AN23, AN30, AP8, AP12,<br/>AP14, AP16, AP17, AP20, AP25, AR6, AR8, AR9,<br/>AR19, AR24, AR31, AR35, AR37, AT4, AT10, AT19,<br/>AT20, AT25, AU14, AU22, AU28, AU35</li> </ul> | _                                                               | _                  | -     |

| GV <sub>DD</sub>   | AD4, AE3, AF1, AF5, AF35, AF37, AG2, AG36,<br>AH33, AH34, AK5, AM1, AM35, AM37, AN2, AN10,<br>AN11, AN12, AN14, AN32, AN36, AP5, AP23,<br>AP28, AR1, AR7, AR10, AR12, AR21, AR25, AR27,<br>AR33, AT15, AT22, AT28, AT33, AU2, AU5, AU16,<br>AU31, AU36                                                                                                                                                                                                                                                                                                                                                                                                                                    | Power for<br>DDR<br>DRAM I/O<br>voltage<br>(2.5 or<br>1.8 V)    | GV <sub>DD</sub>   | _     |

| LV <sub>DD</sub> 0 | D5, D6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Power for<br>UCC1<br>Ethernet<br>interface<br>(2.5 V,<br>3.3 V) | LV <sub>DD</sub> 0 | —     |

Pinout Listings

| Signal             | Package Pin Number                                                                                                                                                                                                                                                                                       | Pin Type                                                                    | Power<br>Supply             | Notes |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------|-------|

| LV <sub>DD</sub> 1 | C17, D16                                                                                                                                                                                                                                                                                                 | Power for<br>UCC2<br>Ethernet<br>interface<br>option 1<br>(2.5 V,<br>3.3 V) | LV <sub>DD</sub> 1          | 9     |

| LV <sub>DD</sub> 2 | B18, E21                                                                                                                                                                                                                                                                                                 | Power for<br>UCC2<br>Ethernet<br>interface<br>option 2<br>(2.5 V,<br>3.3 V) | LV <sub>DD</sub> 2          | 9     |

| V <sub>DD</sub>    | C36, D29, D35, E16, F9, F12, F15, F17, F18, F20,<br>F21, F23, F25, F26, F29, F31, F32, F33, G6, J6,<br>K32, M32, N6, P33, R6, R32, U32, V6, Y5, Y32,<br>AB6, AB33, AD6, AF32, AK6, AL6, AM7, AM9,<br>AM10, AM11, AM12, AM13, AM14, AM15, AM18,<br>AM21, AM25, AM28, AM32, AN15, AN21, AN26,<br>AU9, AU17 | Power for<br>core<br>(1.2 V)                                                | V <sub>DD</sub>             | _     |

| OV <sub>DD</sub>   | A10, B9, B15, B32, C1, C12, C22, C29, D24, E3,<br>E10, E27, G4, H35, J1, J35, K2, M4, N3, N34, R2,<br>R37, T36, U2, U33, V4, V34, W3, Y35, Y37, AA1,<br>AA36, AB2, AB34                                                                                                                                  | PCI,<br>10/100<br>Ethernet,<br>and other<br>standard<br>(3.3 V)             | OV <sub>DD</sub>            | _     |

| MVREF1             | AN20                                                                                                                                                                                                                                                                                                     | I                                                                           | DDR<br>reference<br>voltage | _     |

| MVREF2             | AU32                                                                                                                                                                                                                                                                                                     | I                                                                           | DDR<br>reference<br>voltage | —     |

|                    |                                                                                                                                                                                                                                                                                                          |                                                                             |                             |       |

| SPARE1             | B11                                                                                                                                                                                                                                                                                                      | I/O                                                                         | OV <sub>DD</sub>            | 8     |

| SPARE3             | AH32                                                                                                                                                                                                                                                                                                     | —                                                                           | GV <sub>DD</sub>            | 8     |

| SPARE4             | AU18                                                                                                                                                                                                                                                                                                     |                                                                             | GV <sub>DD</sub>            | 7     |

| SPARE5             | AP1                                                                                                                                                                                                                                                                                                      | —                                                                           | GV <sub>DD</sub>            | 8     |

#### Table 67. MPC8358E TBGA Pinout Listing (continued)

System PLL Configuration

| RCWL[SPMF] | System PLL<br>Multiplication Factor |

|------------|-------------------------------------|

| 1100       | × 12                                |

| 1101       | × 13                                |

| 1110       | × 14                                |

| 1111       | × 15                                |

| Table 70. S | System PLL Mu | Itiplication | Factors | (continued) |

|-------------|---------------|--------------|---------|-------------|

|-------------|---------------|--------------|---------|-------------|

The RCWL[SVCOD] denotes the system PLL VCO internal frequency as shown in this table.

| ,           |             |

|-------------|-------------|

| RCWL[SVCOD] | VCO Divider |

| 00          | 4           |

| 01          | 8           |

| 10          | 2           |

| 11          | Reserved    |

#### Table 71. System PLL VCO Divider

#### NOTE

The VCO divider must be set properly so that the system VCO frequency is in the range of 600-1400 MHz.

The system VCO frequency is derived from the following equations:

- $csb_clk = \{PCI_SYNC_IN \times (1 + CFG_CLKIN_DIV)\} \times SPMF$

- System VCO Frequency = *csb\_clk* × VCO divider (if both RCWL[DDRCM] and RCWL[LBCM] are cleared) OR

- System VCO frequency =  $2 \times csb_clk \times$  VCO divider (if either RCWL[DDRCM] or RCWL[LBCM] are set).

As described in Section 21, "Clocking," the LBCM, DDRCM, and SPMF parameters in the reset configuration word low and the CFG\_CLKIN\_DIV configuration input signal select the ratio between the primary clock input (CLKIN or PCI\_CLK) and the internal coherent system bus clock (*csb\_clk*). This table shows the expected frequency values for the CSB frequency for select *csb\_clk* to CLKIN/PCI\_SYNC\_IN ratios.

|                                             |                                                    |       | In | put Clock Fre | quency (MHz | ) <sup>2</sup> |

|---------------------------------------------|----------------------------------------------------|-------|----|---------------|-------------|----------------|

| CFG_CLKIN_DIV<br>at Reset <sup>1</sup> SPMF | <i>csb_clk</i> :<br>Input Clock Ratio <sup>2</sup> | 16.67 | 25 | 33.33         | 66.67       |                |

|                                             |                                                    |       |    | csb_clk Freq  | uency (MHz) |                |

| Low                                         | 0010                                               | 2:1   |    |               |             | 133            |

| Low                                         | 0011                                               | 3:1   |    |               | 100         | 200            |

| Low                                         | 0100                                               | 4:1   |    | 100           | 133         | 266            |

| Low                                         | 0101                                               | 5:1   |    | 125           | 166         | 333            |

#### Table 72. CSB Frequency Options

Core PLL Configuration

# 21.2 Core PLL Configuration

RCWL[COREPLL] selects the ratio between the internal coherent system bus clock (*csb\_clk*) and the e300 core clock (*core\_clk*). This table shows the encodings for RCWL[COREPLL]. COREPLL values not listed in this table should be considered reserved.

| RCWL[COREPLL] |      |   | core_clk:csb_clk                                                  | VCO divider                                                       |  |

|---------------|------|---|-------------------------------------------------------------------|-------------------------------------------------------------------|--|

| 0–1           | 2–5  | 6 | Ratio                                                             |                                                                   |  |

| nn            | 0000 | n | PLL bypassed<br>(PLL off, <i>csb_clk</i><br>clocks core directly) | PLL bypassed<br>(PLL off, <i>csb_clk</i><br>clocks core directly) |  |

| 00            | 0001 | 0 | 1:1                                                               | ÷2                                                                |  |

| 01            | 0001 | 0 | 1:1                                                               | ÷4                                                                |  |

| 10            | 0001 | 0 | 1:1                                                               | ÷8                                                                |  |

| 11            | 0001 | 0 | 1:1                                                               | ÷8                                                                |  |

| 00            | 0001 | 1 | 1.5:1                                                             | ÷2                                                                |  |

| 01            | 0001 | 1 | 1.5:1                                                             | ÷4                                                                |  |

| 10            | 0001 | 1 | 1.5:1                                                             | ÷8                                                                |  |

| 11            | 0001 | 1 | 1.5:1                                                             | ÷8                                                                |  |

| 00            | 0010 | 0 | 2:1                                                               | ÷2                                                                |  |

| 01            | 0010 | 0 | 2:1                                                               | ÷4                                                                |  |

| 10            | 0010 | 0 | 2:1                                                               | ÷8                                                                |  |

| 11            | 0010 | 0 | 2:1                                                               | ÷8                                                                |  |

| 00            | 0010 | 1 | 2.5:1                                                             | ÷2                                                                |  |

| 01            | 0010 | 1 | 2.5:1                                                             | ÷4                                                                |  |

| 10            | 0010 | 1 | 2.5:1                                                             | ÷8                                                                |  |

| 11            | 0010 | 1 | 2.5:1                                                             | ÷8                                                                |  |

| 00            | 0011 | 0 | 3:1                                                               | ÷2                                                                |  |

| 01            | 0011 | 0 | 3:1                                                               | ÷4                                                                |  |

| 10            | 0011 | 0 | 3:1                                                               | ÷8                                                                |  |

| 11            | 0011 | 0 | 3:1                                                               | ÷8                                                                |  |

#### Table 73. e300 Core PLL Configuration

#### NOTE

Core VCO frequency = Core frequency  $\times$  VCO divider. The VCO divider (RCWL[COREPLL[0:1]]) must be set properly so that the core VCO frequency is in the range of 800–1800 MHz. Having a core frequency below the CSB frequency is not a possible option because the core frequency must be equal to or greater than the CSB frequency.

Suggested PLL Configurations

| Conf<br>No. <sup>1</sup> | SPMF                             | CORE<br>PLL | CEPMF | CEPDF | Input<br>Clock Freq<br>(MHz) | CSB Freq<br>(MHz) | Core Freq<br>(MHz) | QUICC<br>Engine<br>Freq (MHz) | 400<br>(MHz) | 533<br>(MHz) | 667<br>(MHz) |

|--------------------------|----------------------------------|-------------|-------|-------|------------------------------|-------------------|--------------------|-------------------------------|--------------|--------------|--------------|

| c5                       | æ                                | æ           | 10000 | 0     | 33                           | —                 | —                  | 533                           | _            | 8            | 8            |

| c6                       | æ                                | æ           | 10001 | 0     | 33                           | —                 | —                  | 566                           | _            | —            | 8            |

|                          | 66 MHz CLKIN/PCI_SYNC_IN Options |             |       |       |                              |                   |                    |                               |              |              |              |

| s1h                      | 0011                             | 0000110     | æ     | æ     | 66                           | 200               | 400                | —                             | ~            | 8            | 8            |

| s2h                      | 0011                             | 0000101     | æ     | æ     | 66                           | 200               | 500                | _                             | _            | 8            | 8            |

| s3h                      | 0011                             | 0000110     | æ     | æ     | 66                           | 200               | 600                | _                             | _            | —            | 8            |

| s4h                      | 0100                             | 0000011     | æ     | æ     | 66                           | 266               | 400                | _                             | 8            | ∞            | 8            |

| s5h                      | 0100                             | 0000100     | æ     | æ     | 66                           | 266               | 533                | _                             | _            | ∞            | 8            |

| s6h                      | 0100                             | 0000101     | æ     | æ     | 66                           | 266               | 667                | _                             | _            | —            | 8            |

| s7h                      | 0101                             | 0000010     | æ     | æ     | 66                           | 333               | 333                | _                             | 8            | ∞            | 8            |

| s8h                      | 0101                             | 0000011     | æ     | æ     | 66                           | 333               | 500                | _                             | _            | ∞            | 8            |

| s9h                      | 0101                             | 0000100     | æ     | æ     | 66                           | 333               | 667                | _                             |              | —            | 8            |

| c1h                      | æ                                | æ           | 00101 | 0     | 66                           | —                 | —                  | 333                           | 8            | 8            | 8            |

| c2h                      | æ                                | æ           | 00110 | 0     | 66                           | —                 | _                  | 400                           | 8            | 8            | 8            |

| c3h                      | æ                                | æ           | 00111 | 0     | 66                           | —                 | _                  | 466                           |              | 8            | 8            |

| c4h                      | æ                                | æ           | 01000 | 0     | 66                           | —                 | _                  | 533                           | _            | 8            | 8            |

| c5h                      | æ                                | æ           | 01001 | 0     | 66                           |                   |                    | 600                           | _            |              | 8            |

Table 76. Suggested PLL Configurations (continued)

Note:

1. The Conf No. consist of prefix, an index and a postfix. The prefix "s" and "c" stands for "syset" and "ce" respectively. The postfix "h" stands for "high input clock." The index is a serial number.

The following steps describe how to use above table. See Example 1.

- 2. Choose the up or down sections in the table according to input clock rate 33 MHz or 66 MHz.

- 3. Select a suitable CSB and core clock rates from Table 76. Copy the SPMF and CORE PLL configuration bits.

- 4. Select a suitable QUICC Engine block clock rate from Table 76. Copy the CEPMF and CEPDF configuration bits.

- 5. Insert the chosen SPMF, COREPLL, CEPMF and CEPDF to the RCWL fields, respectively.

# 22.3.1 Experimental Determination of the Junction Temperature with a Heat Sink

When heat sink is used, the junction temperature is determined from a thermocouple inserted at the interface between the case of the package and the interface material. A clearance slot or hole is normally required in the heat sink. Minimizing the size of the clearance is important to minimize the change in thermal performance caused by removing part of the thermal interface to the heat sink. Because of the experimental difficulties with this technique, many engineers measure the heat sink temperature and then back calculate the case temperature using a separate measurement of the thermal resistance of the interface. From this case temperature, the junction temperature is determined from the junction-to-case thermal resistance.

$$T_J = T_C + (R_{\theta JC} \times P_D)$$

where:

$T_I$  = junction temperature (° C)

$T_C$  = case temperature of the package (° C)

$R_{\theta JC}$  = junction to case thermal resistance (° C/W)

$P_D$  = power dissipation (W)

# 23 System Design Information

This section provides electrical and thermal design recommendations for successful application of the MPC8360E/58E. Additional information can be found in *MPC8360E/MPC8358E PowerQUICC Design Checklist* (AN3097).

# 23.1 System Clocking

The device includes two PLLs, as follows.

- The platform PLL (AV<sub>DD</sub>1) generates the platform clock from the externally supplied CLKIN input. The frequency ratio between the platform and CLKIN is selected using the platform PLL ratio configuration bits as described in Section 21.1, "System PLL Configuration."

- The e300 core PLL (AV<sub>DD</sub>2) generates the core clock as a slave to the platform clock. The frequency ratio between the e300 core clock and the platform clock is selected using the e300 PLL ratio configuration bits as described in Section 21.2, "Core PLL Configuration."

# 23.2 PLL Power Supply Filtering

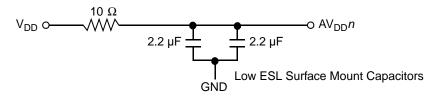

Each of the PLLs listed above is provided with power through independent power supply pins ( $AV_{DD}$ 1,  $AV_{DD}$ 2, respectively). The  $AV_{DD}$  level should always be equivalent to  $V_{DD}$ , and preferably these voltages are derived directly from  $V_{DD}$  through a low frequency filter scheme such as the following.

There are a number of ways to reliably provide power to the PLLs, but the recommended solution is to provide five independent filter circuits as illustrated in Figure 56, one to each of the five  $AV_{DD}$  pins. By providing independent filters to each PLL, the opportunity to cause noise injection from one PLL to the other is reduced.

This circuit is intended to filter noise in the PLLs resonant frequency range from a 500 kHz to 10 MHz range. It should be built with surface mount capacitors with minimum Effective Series Inductance (ESL). Consistent with the recommendations of Dr. Howard Johnson in *High Speed Digital Design: A Handbook of Black Magic* (Prentice Hall, 1993), multiple small capacitors of equal value are recommended over a single large value capacitor.

Each circuit should be placed as close as possible to the specific  $AV_{DD}$  pin being supplied to minimize noise coupled from nearby circuits. It should be possible to route directly from the capacitors to the  $AV_{DD}$  pin, which is on the periphery of package, without the inductance of vias.

This figure shows the PLL power supply filter circuit.

Figure 56. PLL Power Supply Filter Circuit

# 23.3 Decoupling Recommendations

Due to large address and data buses as well as high operating frequencies, the device can generate transient power surges and high frequency noise in its power supply, especially while driving large capacitive loads. This noise must be prevented from reaching other components in the device system, and the device itself requires a clean, tightly regulated source of power. Therefore, it is recommended that the system designer place at least one decoupling capacitor at each  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  pins of the device. These decoupling capacitors should receive their power from separate  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and GND power planes in the PCB, utilizing short traces to minimize inductance. Capacitors may be placed directly under the device using a standard escape pattern. Others may surround the part.

These capacitors should have a value of 0.01 or 0.1  $\mu$ F. Only ceramic SMT (surface mount technology) capacitors should be used to minimize lead inductance, preferably 0402 or 0603 sizes.

Additionally, it is recommended that there be several bulk storage capacitors distributed around the PCB, feeding the  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  planes, to enable quick recharging of the smaller chip capacitors. These bulk capacitors should have a low ESR (equivalent series resistance) rating to ensure the quick response time necessary. They should also be connected to the power and ground planes through two vias to minimize inductance. Suggested bulk capacitors—100–330  $\mu$ F (AVX TPS tantalum or Sanyo OSCON).

# 23.4 Connection Recommendations

To ensure reliable operation, it is highly recommended to connect unused inputs to an appropriate signal level. Unused active low inputs should be tied to  $OV_{DD}$ ,  $GV_{DD}$ , or  $LV_{DD}$  as required. Unused active high inputs should be connected to GND. All NC (no-connect) signals must remain unconnected.

Power and ground connections must be made to all external V<sub>DD</sub>, GV<sub>DD</sub>, LV<sub>DD</sub>, OV<sub>DD</sub>, and GND pins of the device.

# 23.5 Output Buffer DC Impedance

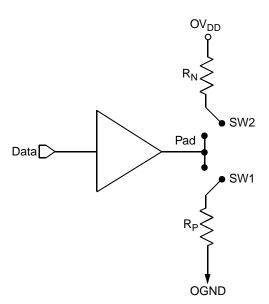

The device drivers are characterized over process, voltage, and temperature. For all buses, the driver is a push-pull single-ended driver type (open drain for  $I^2C$ ).

To measure  $Z_0$  for the single-ended drivers, an external resistor is connected from the chip pad to  $OV_{DD}$  or GND. Then, the value of each resistor is varied until the pad voltage is  $OV_{DD}/2$  (see Figure 57). The output impedance is the average of two components, the resistances of the pull-up and pull-down devices. When data is held high, SW1 is closed (SW2 is open) and  $R_p$  is trimmed until the voltage at the pad equals  $OV_{DD}/2$ .  $R_p$  then becomes the resistance of the pull-up devices.  $R_p$  and  $R_N$  are designed to be close to each other in value. Then,  $Z_0 = (R_P + R_N)/2$ .

**Configuration Pin Muxing**

Figure 57. Driver Impedance Measurement

The value of this resistance and the strength of the driver's current source can be found by making two measurements. First, the output voltage is measured while driving logic 1 without an external differential termination resistor. The measured voltage is  $V_1 = R_{source} \times I_{source}$ . Second, the output voltage is measured while driving logic 1 with an external precision differential termination resistor of value  $R_{term}$ . The measured voltage is  $V_2 = 1/(1/R_1 + 1/R_2)) \times I_{source}$ . Solving for the output impedance gives  $R_{source} = R_{term} \times (V_1/V_2 - 1)$ . The drive current is then  $I_{source} = V_1/R_{source}$ .

This table summarizes the signal impedance targets. The driver impedance are targeted at minimum  $V_{DD}$ , nominal  $OV_{DD}$ , 105° C.

| Impedance      | Local Bus, Ethernet, DUART,<br>Control, Configuration, Power<br>Management | PCI       | DDR DRAM  | Symbol            | Unit |

|----------------|----------------------------------------------------------------------------|-----------|-----------|-------------------|------|

| R <sub>N</sub> | 42 Target                                                                  | 25 Target | 20 Target | Z <sub>0</sub>    | W    |

| R <sub>P</sub> | 42 Target                                                                  | 25 Target | 20 Target | Z <sub>0</sub>    | W    |

| Differential   | NA                                                                         | NA        | NA        | Z <sub>DIFF</sub> | W    |

**Table 79. Impedance Characteristics**

**Note:** Nominal supply voltages. See Table 1,  $T_J = 105^{\circ}$  C.

# 23.6 Configuration Pin Muxing

The device provides the user with power-on configuration options that can be set through the use of external pull-up or pull-down resistors of 4.7 k $\Omega$ on certain output pins (see customer visible configuration pins). These pins are generally used as output only pins in normal operation.

While HRESET is asserted however, these pins are treated as inputs. The value presented on these pins while HRESET is asserted, is latched when HRESET deasserts, at which time the input receiver is disabled and the I/O circuit takes on its normal function. Careful board layout with stubless connections to these pull-up/pull-down resistors coupled with the large value of the pull-up/pull-down resistor should minimize the disruption of signal quality or speed for output pins thus configured.

# 23.7 Pull-Up Resistor Requirements

The device requires high resistance pull-up resistors (10 k $\Omega$  is recommended) on open drain type pins including I<sup>2</sup>C pins, Ethernet Management MDIO pin, and EPIC interrupt pins.

For more information on required pull-up resistors and the connections required for the JTAG interface, see *MPC8360E/MPC8358E PowerQUICC Design Checklist* (AN3097).

# 24 Ordering Information

# 24.1 Part Numbers Fully Addressed by this Document

This table provides the Freescale part numbering nomenclature for the MPC8360E/58E. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. Additionally to the processor frequency, the part numbering scheme also includes an application modifier, which may specify special application conditions. Each part number also contains a revision code that refers to the die mask revision number.

| MPC                                  | nnnn               | е                                       | t                                                                            | рр                                  | aa                                                              | а                          | а                            | Α                       |

|--------------------------------------|--------------------|-----------------------------------------|------------------------------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------|----------------------------|------------------------------|-------------------------|

| Product<br>Code                      | Part<br>Identifier | Encryption<br>Acceleration              | Temperature<br>Range                                                         | Package <sup>2</sup>                | Processor<br>Frequency <sup>3</sup>                             | Platform<br>Frequency      | QUICC<br>Engine<br>Frequency | Die<br>Revision         |