### NXP USA Inc. - <u>MPC8358EZUAGDG Datasheet</u>

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e300                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 400MHz                                                                 |

| Co-Processors/DSP               | Communications; QUICC Engine, Security; SEC                            |

| RAM Controllers                 | DDR, DDR2                                                              |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (1)                                                    |

| SATA                            | -                                                                      |

| USB                             | USB 1.x (1)                                                            |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | Cryptography, Random Number Generator                                  |

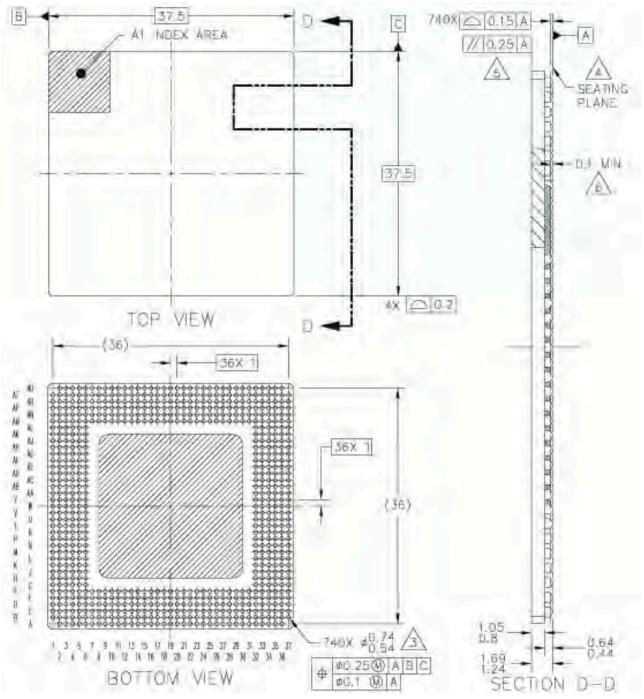

| Package / Case                  | 740-LBGA                                                               |

| Supplier Device Package         | 740-TBGA (37.5x37.5)                                                   |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8358ezuagdg |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- 10/100 Mbps Ethernet/IEEE Std. 802.3<sup>TM</sup> CDMA/CS interface through a media-independent interface (MII, RMII, RGMII)<sup>1</sup>

- 1000 Mbps Ethernet/IEEE 802.3 CDMA/CS interface through a media-independent interface (GMII, RGMII, TBI, RTBI) on UCC1 and UCC2

- 9.6-Kbyte jumbo frames

- ATM full-duplex SAR, up to 622 Mbps (OC-12/STM-4), AAL0, AAL1, and AAL5 in accordance ITU-T I.363.5

- ATM AAL2 CPS, SSSAR, and SSTED up to 155 Mbps (OC-3/STM-1) Mbps full duplex (with 4 CPS packets per cell) in accordance ITU-T I.366.1 and I.363.2

- ATM traffic shaping for CBR, VBR, UBR, and GFR traffic types compatible with ATM forum TM4.1 for up to 64-Kbyte simultaneous ATM channels

- ATM AAL1 structured and unstructured circuit emulation service (CES 2.0) in accordance with ITU-T I.163.1 and ATM Forum af-vtoa-00-0078.000

- IMA (Inverse Multiplexing over ATM) for up to 31 IMA links over 8 IMA groups in accordance with the ATM forum AF-PHY-0086.000 (Version 1.0) and AF-PHY-0086.001 (Version 1.1)

- ATM Transmission Convergence layer support in accordance with ITU-T I.432

- ATM OAM handling features compatible with ITU-T I.610

- PPP, Multi-Link (ML-PPP), Multi-Class (MC-PPP) and PPP mux in accordance with the following RFCs: 1661, 1662, 1990, 2686, and 3153

- IP support for IPv4 packets including TOS, TTL, and header checksum processing

- Ethernet over first mile IEEE 802.3ah

- Shim header

- Ethernet-to-Ethernet/AAL5/AAL2 inter-working

- L2 Ethernet switching using MAC address or IEEE Std. 802.1P/Q<sup>™</sup> VLAN tags

- ATM (AAL2/AAL5) to Ethernet (IP) interworking in accordance with RFC2684 including bridging of ATM ports to Ethernet ports

- Extensive support for ATM statistics and Ethernet RMON/MIB statistics

- AAL2 protocol rate up to 4 CPS at OC-3/STM-1 rate

- Packet over Sonet (POS) up to 622-Mbps full-duplex 124 MultiPHY

- POS hardware; microcode must be loaded as an IRAM package

- Transparent up to 70-Mbps full-duplex

- HDLC up to 70-Mbps full-duplex

- HDLC BUS up to 10 Mbps

- Asynchronous HDLC

- UART

- BISYNC up to 2 Mbps

- User-programmable Virtual FIFO size

- QUICC multichannel controller (QMC) for 64 TDM channels

- One multichannel communication controller (MCC) only on the MPC8360E supporting the following:

- 256 HDLC or transparent channels

- 128 SS7 channels

- Almost any combination of subgroups can be multiplexed to single or multiple TDM interfaces

- Two UTOPIA/POS interfaces on the MPC8360E supporting 124 MultiPHY each (optional 2\*128 MultiPHY with extended address) and one UTOPIA/POS interface on the MPC8358E supporting 31/124 MultiPHY

- Two serial peripheral interfaces (SPI); SPI2 is dedicated to Ethernet PHY management

1.SMII or SGMII media-independent interface is not currently supported.

| Table 4. MPC8360E TBGA Core Power Dissipa | tion <sup>1</sup> (continued) |

|-------------------------------------------|-------------------------------|

|-------------------------------------------|-------------------------------|

| Core<br>Frequency (MHz) | CSB<br>Frequency (MHz) | QUICC Engine<br>Frequency (MHz) | Typical | Maximum | Unit | Notes      |

|-------------------------|------------------------|---------------------------------|---------|---------|------|------------|

| 667                     | 333                    | 500                             | 6.1     | 6.8     | W    | 2, 3, 5, 9 |

#### Notes:

- 1. The values do not include I/O supply power (OV<sub>DD</sub>, LV<sub>DD</sub>, GV<sub>DD</sub>) or AV<sub>DD</sub>. For I/O power values, see Table 6.

- 2. Typical power is based on a voltage of  $V_{DD}$  = 1.2 V or 1.3 V, a junction temperature of  $T_J$  = 105°C, and a Dhrystone benchmark application.

- 3. Thermal solutions need to design to a value higher than typical power on the end application, T<sub>A</sub> target, and I/O power.

- 4. Maximum power is based on a voltage of V<sub>DD</sub> = 1.2 V, WC process, a junction T<sub>J</sub> = 105°C, and an artificial smoke test.

- Maximum power is based on a voltage of V<sub>DD</sub> = 1.3 V for applications that use 667 MHz (CPU)/500 (QE) with WC process, a junction T<sub>1</sub> = 105° C, and an artificial smoke test.

- 6. Typical power is based on a voltage of  $V_{DD}$  = 1.3 V, a junction temperature of  $T_J$  = 70° C, and a Dhrystone benchmark application.

- Maximum power is based on a voltage of V<sub>DD</sub> = 1.3 V for applications that use 667 MHz (CPU) or 500 (QE) with WC process, a junction T<sub>J</sub> = 70° C, and an artificial smoke test.

- 8. This frequency combination is only available for rev. 2.0 silicon.

- 9. This frequency combination is not available for rev. 2.0 silicon.

#### Table 5. MPC8358E TBGA Core Power Dissipation<sup>1</sup>

| Core<br>Frequency (MHz) | CSB<br>Frequency (MHz) | QUICC Engine<br>Frequency (MHz) | Typical | Maximum | Unit | Notes   |

|-------------------------|------------------------|---------------------------------|---------|---------|------|---------|

| 266                     | 266                    | 300                             | 4.1     | 4.5     | W    | 2, 3, 4 |

| 400                     | 266                    | 400                             | 4.5     | 5.0     | W    | 2, 3, 4 |

#### Notes:

- 1. The values do not include I/O supply power (OV<sub>DD</sub>,  $LV_{DD}$ ,  $GV_{DD}$ ) or  $AV_{DD}$ . For I/O power values, see Table 6.

- Typical power is based on a voltage of V<sub>DD</sub> = 1.2 V, a junction temperature of T<sub>J</sub> = 105°C, and a Dhrystone benchmark application.

- 3. Thermal solutions need to design to a value higher than typical power on the end application, T<sub>A</sub> target, and I/O power.

- 4. Maximum power is based on a voltage of V<sub>DD</sub> = 1.2 V, WC process, a junction T<sub>J</sub> = 105°C, and an artificial smoke test.

## 5.2 **RESET AC Electrical Characteristics**

This section describes the AC electrical specifications for the reset initialization timing requirements of the device. This table provides the reset initialization AC timing specifications for the DDR SDRAM component(s).

| Parameter/Condition                                                                                                                                        | Min | Max | Unit                     | Notes |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------------|-------|

| Required assertion time of $\overrightarrow{\text{HRESET}}$ or $\overrightarrow{\text{SRESET}}$ (input) to activate reset flow                             | 32  | -   | t <sub>PCI_SYNC_IN</sub> | 1     |

| Required assertion time of $\overrightarrow{\text{PORESET}}$ with stable clock applied to CLKIN when the device is in PCI host mode                        | 32  | -   | <sup>t</sup> CLKIN       | 2     |

| Required assertion time of PORESET with stable clock applied to PCI_SYNC_IN when the device is in PCI agent mode                                           | 32  | -   | t <sub>PCI_SYNC_IN</sub> | 1     |

| HRESET/SRESET assertion (output)                                                                                                                           | 512 | _   | t <sub>PCI_SYNC_IN</sub> | 1     |

| HRESET negation to SRESET negation (output)                                                                                                                | 16  | —   | t <sub>PCI_SYNC_IN</sub> | 1     |

| Input setup time for POR config signals (CFG_RESET_SOURCE[0:2] and CFG_CLKIN_DIV) with respect to negation of PORESET when the device is in PCI host mode  | 4   | —   | <sup>t</sup> CLKIN       | 2     |

| Input setup time for POR config signals (CFG_RESET_SOURCE[0:2] and CFG_CLKIN_DIV) with respect to negation of PORESET when the device is in PCI agent mode | 4   | -   | <sup>t</sup> PCI_SYNC_IN | 1     |

| Input hold time for POR config signals with respect to negation of $\overline{\text{HRESET}}$                                                              | 0   | —   | ns                       | —     |

| Time for the device to turn off POR config signals with respect to the assertion of HRESET                                                                 |     | 4   | ns                       | 3     |

| Time for the device to turn on POR config signals with respect to the negation of $\overrightarrow{HRESET}$                                                | 1   | -   | t <sub>PCI_SYNC_IN</sub> | 1, 3  |

#### Table 11. RESET Initialization Timing Specifications

#### Notes:

- t<sub>PCI\_SYNC\_IN</sub> is the clock period of the input clock applied to PCI\_SYNC\_IN. When the device is In PCI host mode the primary clock is applied to the CLKIN input, and PCI\_SYNC\_IN period depends on the value of CFG\_CLKIN\_DIV. Refer MPC8360E PowerQUICC II Pro Integrated Communications Processor Reference Manual for more details.

- t<sub>CLKIN</sub> is the clock period of the input clock applied to CLKIN. It is only valid when the device is in PCI host mode. Refer MPC8360E PowerQUICC II Pro Integrated Communications Processor Reference Manual for more details.

- 3. POR config signals consists of CFG\_RESET\_SOURCE[0:2] and CFG\_CLKIN\_DIV.

This table provides the PLL and DLL lock times.

#### Table 12. PLL and DLL Lock Times

| Parameter/Condition | Min  | Max     | Unit           | Notes |

|---------------------|------|---------|----------------|-------|

| PLL lock times      | —    | 100     | μs             |       |

| DLL lock times      | 7680 | 122,880 | csb_clk cycles | 1, 2  |

Notes:

1. DLL lock times are a function of the ratio between the output clock and the coherency system bus clock (csb\_clk). A 2:1 ratio results in the minimum and an 8:1 ratio results in the maximum.

2. The csb\_clk is determined by the CLKIN and system PLL ratio. See Section 21, "Clocking," for more information.

DDR and DDR2 SDRAM AC Electrical Characteristics

## 6.2.2 DDR and DDR2 SDRAM Output AC Timing Specifications

Table 21 and Table 22 provide the output AC timing specifications and measurement conditions for the DDR and DDR2 SDRAM interface.

# Table 21. DDR and DDR2 SDRAM Output AC Timing Specifications for Source Synchronous Mode

At recommended operating conditions with  $\text{GV}_{\text{DD}}$  of (1.8 V or 2.5 V) ± 5%.

| Parameter <sup>8</sup>                                                                         | Symbol <sup>1</sup> | Min                         | Мах                               | Unit | Notes |

|------------------------------------------------------------------------------------------------|---------------------|-----------------------------|-----------------------------------|------|-------|

| MCK[n] cycle time, (MCK[n]/MCK[n] crossing)                                                    | t <sub>MCK</sub>    | 6                           | 10                                | ns   | 2     |

| Skew between any MCK to ADDR/CMD<br>333 MHz<br>266 MHz<br>200 MHz                              |                     | -1.0<br>-1.1<br>-1.2        | 0.2<br>0.3<br>0.4                 | ns   | 3     |

| ADDR/CMD output setup with respect to MCK<br>333 MHz<br>266 MHz<br>200 MHz                     |                     | 2.1<br>2.8<br>3.5           | _                                 | ns   | 4     |

| ADDR/CMD output hold with respect to MCK<br>333 MHz<br>266 MHz—DDR1<br>266 MHz—DDR2<br>200 MHz |                     | 2.0<br>2.7<br>2.8<br>3.5    | _                                 | ns   | 4     |

| MCS(n) output setup with respect to MCK<br>333 MHz<br>266 MHz<br>200 MHz                       |                     | 2.1<br>2.8<br>3.5           | _                                 | ns   | 4     |

| MCS(n) output hold with respect to MCK<br>333 MHz<br>266 MHz<br>200 MHz                        |                     | 2.0<br>2.7<br>3.5           | _                                 | ns   | 4     |

| MCK to MDQS                                                                                    | t <sub>DDKHMH</sub> | -0.8                        | 0.7                               | ns   | 5, 9  |

| MDQ/MECC/MDM output setup with respect to MDQS<br>333 MHz<br>266 MHz<br>200 MHz                | 2211220             | 0.7<br>1.0<br>1.2           | _                                 | ns   | 6     |

| MDQ/MECC/MDM output hold with respect to MDQS<br>333 MHz<br>266 MHz<br>200 MHz                 | DDICEDX             | 0.7<br>1.0<br>1.2           | _                                 | ns   | 6     |

| MDQS preamble start                                                                            | t <sub>DDKHMP</sub> | $-0.5 \times t_{MCK} - 0.6$ | $-0.5\timest_{\text{MCK}}^{}+0.6$ | ns   | 7     |

GMII, MII, RMII, TBI, RGMII, and RTBI AC Timing Specifications

## 8.2.1.2 GMII Receive AC Timing Specifications

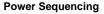

This table provides the GMII receive AC timing specifications.

#### Table 28. GMII Receive AC Timing Specifications

At recommended operating conditions with LV\_{DD}/OV\_{DD} of 3.3 V  $\pm$  10%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit | Notes |

|---------------------------------------------|-------------------------------------|-----|-----|-----|------|-------|

| RX_CLK clock period                         | t <sub>GRX</sub>                    | _   | 8.0 | _   | ns   | —     |

| RX_CLK duty cycle                           | t <sub>GRXH</sub> /t <sub>GRX</sub> | 40  | —   | 60  | %    | —     |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>GRDVKH</sub>                 | 2.0 | —   | _   | ns   | _     |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>GRDXKH</sub>                 | 0.2 | —   | _   | ns   | 2     |

| RX_CLK clock rise time, (20% to 80%)        | t <sub>GRXR</sub>                   | _   | —   | 1.0 | ns   | _     |

| RX_CLK clock fall time, (80% to 20%)        | t <sub>GRXF</sub>                   | _   |     | 1.0 | ns   | _     |

#### Notes:

- 1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>GRDVKH</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>RX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>RX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>GRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GRX</sub> represents the GMII (G) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- In rev. 2.0 silicon, due to errata, t<sub>GRDXKH</sub> minimum is 0.5 which is not compliant with the standard. Refer to Errata QE\_ENET18 in Chip Errata for the MPC8360E, Rev. 1.

This figure shows the GMII receive AC timing diagram.

Figure 11. GMII Receive AC Timing Diagram

## 8.2.5 RGMII and RTBI AC Timing Specifications

This table presents the RGMII and RTBI AC timing specifications.

#### Table 35. RGMII and RTBI AC Timing Specifications

At recommended operating conditions with  $LV_{DD}$  of 2.5 V ± 5%.

| Parameter/Condition                        | Symbol <sup>1</sup>                              | Min      | Тур | Мах      | Unit | Notes |

|--------------------------------------------|--------------------------------------------------|----------|-----|----------|------|-------|

| Data to clock output skew (at transmitter) | t <sub>SKRGTKHDX</sub><br>t <sub>SKRGTKHDV</sub> | -0.5<br> | —   | —<br>0.5 | ns   | 7     |

| Data to clock input skew (at receiver)     | t <sub>SKRGDXKH</sub><br>t <sub>SKRGDVKH</sub>   | 1.0      | —   | <br>2.6  | ns   | 2     |

| Clock cycle duration                       | t <sub>RGT</sub>                                 | 7.2      | 8.0 | 8.8      | ns   | 3     |

| Duty cycle for 1000Base-T                  | t <sub>RGTH</sub> /t <sub>RGT</sub>              | 45       | 50  | 55       | %    | 4, 5  |

| Duty cycle for 10BASE-T and 100BASE-TX     | t <sub>RGTH</sub> /t <sub>RGT</sub>              | 40       | 50  | 60       | %    | 3, 5  |

| Rise time (20–80%)                         | t <sub>RGTR</sub>                                | _        | —   | 0.75     | ns   | —     |

| Fall time (20–80%)                         | t <sub>RGTF</sub>                                | _        | —   | 0.75     | ns   | —     |

| GTX_CLK125 reference clock period          | t <sub>G125</sub>                                | _        | 8.0 | _        | ns   | 6     |

| GTX_CLK125 reference clock duty cycle      | t <sub>G125H</sub> /t <sub>G125</sub>            | 47       | —   | 53       | %    | —     |

Notes:

- Note that, in general, the clock reference symbol representation for this section is based on the symbols RGT to represent RGMII and RTBI timing. For example, the subscript of t<sub>RGT</sub> represents the TBI (T) receive (Rx) clock. Note also that the notation for rise (R) and fall (F) times follows the clock symbol that is being represented. For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (RGT).

- 2. This implies that PC board design requires clocks to be routed such that an additional trace delay of greater than 1.5 ns can be added to the associated clock signal.

- 3. For 10 and 100 Mbps,  $t_{RGT}$  scales to 400 ns ± 40 ns and 40 ns ± 4 ns, respectively.

- 4. Duty cycle may be stretched/shrunk during speed changes or while transitioning to a received packet's clock domains as long as the minimum duty cycle is not violated and stretching occurs for no more than three t<sub>RGT</sub> of the lowest speed transitioned between.

- 5. Duty cycle reference is LV<sub>DD</sub>/2.

- 6. This symbol is used to represent the external GTX\_CLK125 and does not follow the original symbol naming convention.

- 7. In rev. 2.0 silicon, due to errata, t<sub>SKRGTKHDX</sub> minimum is –2.3 ns and t<sub>SKRGTKHDV</sub> maximum is 1 ns for UCC1, 1.2 ns for UCC2 option 1, and 1.8 ns for UCC2 option 2. In rev. 2.1 silicon, due to errata, t<sub>SKRGTKHDX</sub> minimum is –0.65 ns for UCC2 option 1 and –0.9 for UCC2 option 2, and t<sub>SKRGTKHDV</sub> maximum is 0.75 ns for UCC1 and UCC2 option 1 and 0.85 for UCC2 option 2. Refer to Errata QE\_ENET10 in *Chip Errata for the MPC8360E, Rev. 1*. UCC1 does meet t<sub>SKRGTKHDX</sub> minimum for rev. 2.1 silicon.

Local Bus DC Electrical Characteristics

## 8.3.3 IEEE 1588 Timer AC Specifications

This table provides the IEEE 1588 timer AC specifications.

#### Table 38. IEEE 1588 Timer AC Specifications

| Parameter                    | Symbol              | Min | Max | Unit | Notes |

|------------------------------|---------------------|-----|-----|------|-------|

| Timer clock frequency        | t <sub>TMRCK</sub>  | 0   | 70  | MHz  | 1     |

| Input setup to timer clock   | t <sub>TMRCKS</sub> | —   | _   | _    | 2, 3  |

| Input hold from timer clock  | t <sub>TMRCKH</sub> | —   | _   | _    | 2, 3  |

| Output clock to output valid | t <sub>GCLKNV</sub> | 0   | 6   | ns   | —     |

| Timer alarm to output valid  | t <sub>TMRAL</sub>  | —   |     | _    | 2     |

Notes:

1. The timer can operate on rtc\_clock or tmr\_clock. These clocks get muxed and any one of them can be selected. The minimum and maximum requirement for both rtc\_clock and tmr\_clock are the same.

- 2. These are asynchronous signals.

- 3. Inputs need to be stable at least one TMR clock.

## 9 Local Bus

This section describes the DC and AC electrical specifications for the local bus interface of the MPC8360E/58E.

## 9.1 Local Bus DC Electrical Characteristics

This table provides the DC electrical characteristics for the local bus interface.

#### Table 39. Local Bus DC Electrical Characteristics

| Parameter                                            | Symbol          | Min                    | Мах                    | Unit |

|------------------------------------------------------|-----------------|------------------------|------------------------|------|

| High-level input voltage                             | V <sub>IH</sub> | 2                      | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                              | V <sub>IL</sub> | -0.3                   | 0.8                    | V    |

| High-level output voltage, I <sub>OH</sub> = −100 μA | V <sub>OH</sub> | OV <sub>DD</sub> - 0.4 | —                      | V    |

| Low-level output voltage, I <sub>OL</sub> = 100 μA   | V <sub>OL</sub> | —                      | 0.2                    | V    |

| Input current                                        | I <sub>IN</sub> | —                      | ±10                    | μA   |

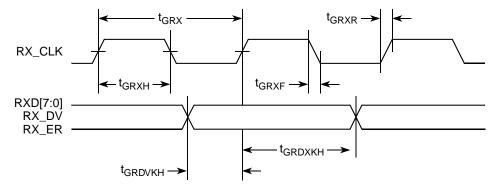

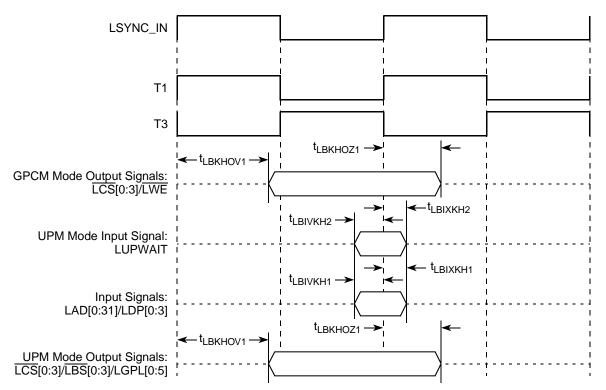

## 9.2 Local Bus AC Electrical Specifications

This table describes the general timing parameters of the local bus interface of the device.

#### Table 40. Local Bus General Timing Parameters—DLL Enabled

| Parameter                                        | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|--------------------------------------------------|----------------------|-----|-----|------|-------|

| Local bus cycle time                             | t <sub>LBK</sub>     | 7.5 | _   | ns   | 2     |

| Input setup to local bus clock (except LUPWAIT)  | t <sub>LBIVKH1</sub> | 1.7 | _   | ns   | 3, 4  |

| LUPWAIT input setup to local bus clock           | t <sub>LBIVKH2</sub> | 1.9 | _   | ns   | 3, 4  |

| Input hold from local bus clock (except LUPWAIT) | t <sub>LBIXKH1</sub> | 1.0 |     | ns   | 3, 4  |

#### Local Bus AC Electrical Specifications

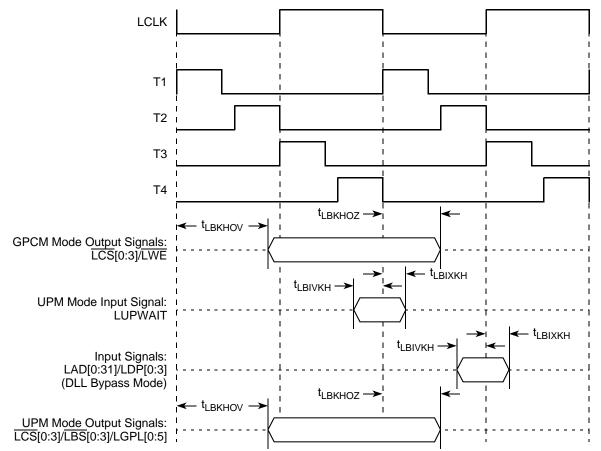

Figure 25. Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 2 (DLL Enabled)

Figure 27. Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 4 (DLL Bypass Mode)

#### **SPI AC Timing Specifications**

| Table 56. | SPI AC | Timing | Specifications <sup>1</sup> |

|-----------|--------|--------|-----------------------------|

|-----------|--------|--------|-----------------------------|

| Characteristic                                         | Symbol <sup>2</sup> | Min | Max | Unit |

|--------------------------------------------------------|---------------------|-----|-----|------|

| SPI inputs—Slave mode (external clock) input hold time | t <sub>NEIXKH</sub> | 2   | —   | ns   |

Notes:

- 1. Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are measured at the pin.

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>NIKHOV</sub> symbolizes the NMSI outputs internal timing (NI) for the time t<sub>SPI</sub> memory clock reference (K) goes from the high state (H) until outputs (O) are valid (V).

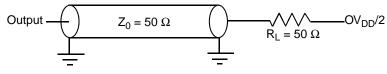

This figure provides the AC test load for the SPI.

Figure 41. SPI AC Test Load

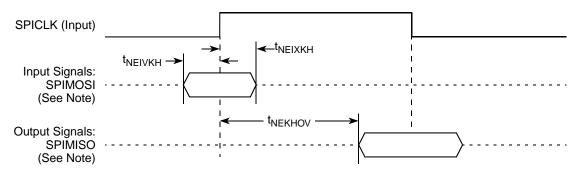

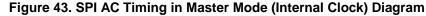

These figures represent the AC timing from Table 56. Note that although the specifications generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge is the active edge.

This figure shows the SPI timing in slave mode (external clock).

Note: The clock edge is selectable on SPI.

#### Figure 42. SPI AC Timing in Slave Mode (External Clock) Diagram

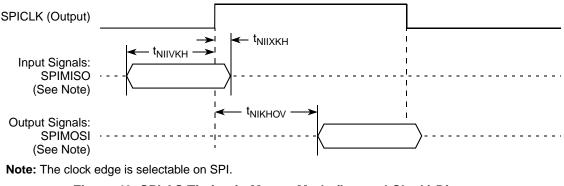

This figure shows the SPI timing in Master mode (internal clock).

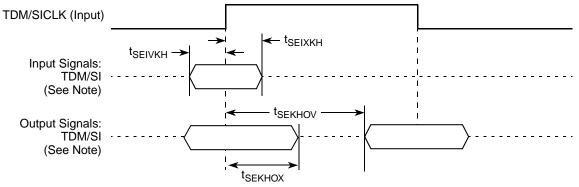

This figure shows the TDM/SI timing with external clock.

Note: The clock edge is selectable on TDM/SI

## 17.3 UTOPIA/POS

This section describes the DC and AC electrical specifications for the UTOPIA/POS of the MPC8360E/58E.

## **17.4 UTOPIA/POS DC Electrical Characteristics**

This table provides the DC electrical characteristics for the device UTOPIA.

Table 59. UTOPIA DC Electrical Characteristics

| Characteristic      | Symbol          | Condition                              | Min  | Мах                    | Unit |

|---------------------|-----------------|----------------------------------------|------|------------------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA              | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA               | _    | 0.5                    | V    |

| Input high voltage  | V <sub>IH</sub> | _                                      | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | _                                      | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | 0 V ≤V <sub>IN</sub> ≤OV <sub>DD</sub> | _    | ±10                    | μA   |

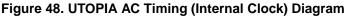

## 17.5 UTOPIA/POS AC Timing Specifications

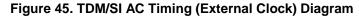

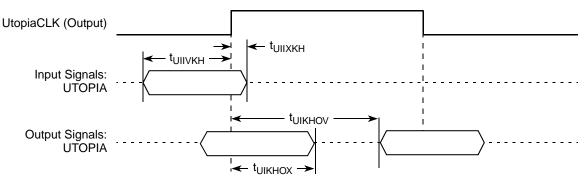

This table provides the UTOPIA input and output AC timing specifications.

Table 60. UTOPIA AC Timing Specifications<sup>1</sup>

| Characteristic                                | Symbol <sup>2</sup> | Min | Мах  | Unit | Notes |

|-----------------------------------------------|---------------------|-----|------|------|-------|

| UTOPIA outputs—Internal clock delay           | t <sub>UIKHOV</sub> | 0   | 11.5 | ns   | —     |

| UTOPIA outputs—External clock delay           | t <sub>UEKHOV</sub> | 1   | 11.6 | ns   | _     |

| UTOPIA outputs—Internal clock high impedance  | t <sub>UIKHOX</sub> | 0   | 8.0  | ns   | —     |

| UTOPIA outputs—External clock high impedance  | t <sub>UEKHOX</sub> | 1   | 10.0 | ns   | —     |

| UTOPIA inputs—Internal clock input setup time | <sup>t</sup> ∪IIVKH | 6   | _    | ns   | —     |

| UTOPIA inputs—External clock input setup time | t <sub>UEIVKH</sub> | 4   | _    | ns   | 3     |

HDLC, BISYNC, Transparent, and Synchronous UART DC Electrical Characteristics

This figure shows the UTOPIA timing with internal clock.

# 18 HDLC, BISYNC, Transparent, and Synchronous UART

This section describes the DC and AC electrical specifications for the high level data link control (HDLC), BISYNC, transparent, and synchronous UART protocols of the MPC8360E/58E.

## 18.1 HDLC, BISYNC, Transparent, and Synchronous UART DC Electrical Characteristics

This table provides the DC electrical characteristics for the device HDLC, BISYNC, transparent, and synchronous UART protocols.

| Table 61. HDLC, BISYNC, Transparent, a | nd Synchronous UART DC Electrical Characteristics |

|----------------------------------------|---------------------------------------------------|

|----------------------------------------|---------------------------------------------------|

| Characteristic      | Symbol          | Condition                              | Min  | Мах                    | Unit |

|---------------------|-----------------|----------------------------------------|------|------------------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -2.0 mA              | 2.4  | _                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA               | —    | 0.5                    | V    |

| Input high voltage  | V <sub>IH</sub> | _                                      | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | _                                      | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | 0 V ≤V <sub>IN</sub> ≤OV <sub>DD</sub> | —    | ±10                    | μA   |

# 18.2 HDLC, BISYNC, Transparent, and Synchronous UART AC Timing Specifications

These tables provide the input and output AC timing specifications for HDLC, BISYNC, transparent, and synchronous UART protocols.

#### Table 62. HDLC, BISYNC, and Transparent AC Timing Specifications<sup>1</sup>

| Characteristic               | Symbol <sup>2</sup> | Min | Max  | Unit |

|------------------------------|---------------------|-----|------|------|

| Outputs—Internal clock delay | t <sub>HIKHOV</sub> | 0   | 11.2 | ns   |

| Outputs—External clock delay | t <sub>HEKHOV</sub> | 1   | 10.8 | ns   |

Mechanical Dimensions of the TBGA Package

## 20.2 Mechanical Dimensions of the TBGA Package

This figure depicts the mechanical dimensions and bottom surface nomenclature of the device, 740-TBGA package.

Figure 53. Mechanical Dimensions and Bottom Surface Nomenclature of the TBGA Package

**Pinout Listings**

#### Table 66. MPC8360E TBGA Pinout Listing (continued)

| Signal             | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pin Type                                                     | Power<br>Supply     | Notes |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------|-------|

|                    | РМС                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                            |                     | 1     |

| QUIESCE            | B36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                            | OV <sub>DD</sub>    | _     |

|                    | System Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                              |                     |       |

| PORESET            | L37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                            | $OV_{DD}$           | _     |

| HRESET             | L36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I/O                                                          | $OV_{DD}$           | 1     |

| SRESET             | M33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I/O                                                          | $OV_{DD}$           | 2     |

|                    | Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                              |                     |       |

| THERM0             | AP19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I                                                            | GV <sub>DD</sub>    | _     |

| THERM1             | AT31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I                                                            | ${\rm GV}_{\rm DD}$ | —     |

|                    | Power and Ground Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                              |                     |       |

| AV <sub>DD</sub> 1 | K35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power for<br>LBIU DLL<br>(1.2 V)                             | AV <sub>DD</sub> 1  | _     |

| AV <sub>DD</sub> 2 | K36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power for<br>CE PLL<br>(1.2 V)                               | AV <sub>DD</sub> 2  | _     |

| AV <sub>DD</sub> 5 | AM29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Power for<br>e300 PLL<br>(1.2 V)                             | AV <sub>DD</sub> 5  | —     |

| AV <sub>DD</sub> 6 | K37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power for<br>system<br>PLL (1.2 V)                           | AV <sub>DD</sub> 6  | —     |

| GND                | <ul> <li>A2, A8, A13, A19, A22, A25, A31, A33, A36, B7,<br/>B12, B24, B27, B30, C4, C6, C9, C15, C26, C32,<br/>D3, D8, D11, D14, D17, D19, D23, D27, E7, E13,<br/>E25, E30, E36, F4, F37, G34, H1, H5, H32, H33, J4,<br/>J32, J37, K1, L3, L5, L33, L34, M1, M34, M35, N37,<br/>P2, P5, P35, P36, R4, T3, U1, U5, U35, V37, W1,<br/>W4, W33, W36, Y34, AA3, AA5, AC3, AC32, AC35,<br/>AD1, AD37, AE4, AE34, AE36, AF33, AG4, AG6,<br/>AG32, AH35, AJ1, AJ4, AJ32, AJ35, AJ37, AK36,<br/>AL3, AL34, AM4, AN6, AN23, AN30, AP8, AP12,<br/>AP14, AP16, AP17, AP20, AP25, AR6, AR8, AR9,<br/>AR19, AR24, AR31, AR35, AR37, AT4, AT10, AT19,<br/>AT20, AT25, AU14, AU22, AU28, AU35</li> </ul> |                                                              |                     | _     |

| GV <sub>DD</sub>   | AD4, AE3, AF1, AF5, AF35, AF37, AG2, AG36,<br>AH33, AH34, AK5, AM1, AM35, AM37, AN2, AN10,<br>AN11, AN12, AN14, AN32, AN36, AP5, AP23,<br>AP28, AR1, AR7, AR10, AR12, AR21, AR25, AR27,<br>AR33, AT15, AT22, AT28, AT33, AU2, AU5, AU16,<br>AU31, AU36                                                                                                                                                                                                                                                                                                                                                                                                                                    | Power for<br>DDR<br>DRAM I/O<br>voltage<br>(2.5 or<br>1.8 V) | GV <sub>DD</sub>    | _     |

#### Table 67. MPC8358E TBGA Pinout Listing (continued)

| Signal                                         | Signal Package Pin Number  |     | Power<br>Supply    | Notes |  |

|------------------------------------------------|----------------------------|-----|--------------------|-------|--|

| IRQ[4:5]                                       | G33, G32                   | I/O | OV <sub>DD</sub>   | —     |  |

| IRQ[6]/LCS[6]/CKSTOP_OUT                       | E35                        | I/O | OV <sub>DD</sub>   | _     |  |

| IRQ[7]/LCS[7]/CKSTOP_IN                        | 7]/LCS[7]/CKSTOP_IN H36    |     |                    |       |  |

|                                                | DUART                      |     |                    |       |  |

| UART1_SOUT/M1SRCID[0]/<br>M2SRCID[0]/LSRCID[0] | E32                        | 0   | OV <sub>DD</sub>   | -     |  |

| UART1_SIN/M1SRCID[1]/<br>M2SRCID[1]/LSRCID[1]  | B34                        | I/O | OV <sub>DD</sub>   | —     |  |

| UART1_CTS/M1SRCID[2]/<br>M2SRCID[2]/LSRCID[2]  | C34                        | I/O | OV <sub>DD</sub>   | —     |  |

| UART1_RTS/M1SRCID[3]/<br>M2SRCID[3]/LSRCID[3]  | A35                        | 0   | OV <sub>DD</sub>   | —     |  |

|                                                | I <sup>2</sup> C Interface |     |                    |       |  |

| IIC1_SDA                                       | D34                        | I/O | OV <sub>DD</sub>   | 2     |  |

| IIC1_SCL                                       | SCL B35                    |     | OV <sub>DD</sub>   | 2     |  |

| IIC2_SDA                                       | E33                        | I/O | OV <sub>DD</sub>   | 2     |  |

| IIC2_SCL                                       | C35                        | I/O | OV <sub>DD</sub>   | 2     |  |

|                                                | QUICC Engine               |     |                    |       |  |

| CE_PA[0]                                       | F8                         | I/O | LV <sub>DD0</sub>  | _     |  |

| CE_PA[1:2]                                     | AH1, AG5                   | I/O | OV <sub>DD</sub>   | _     |  |

| CE_PA[3:7]                                     | F6, D4, C3, E5, A3         | I/O | LV <sub>DD</sub> 0 | —     |  |

| CE_PA[8]                                       | AG3                        | I/O | OV <sub>DD</sub>   | _     |  |

| CE_PA[9:12]                                    | F7, B3, E6, B4             | I/O | LV <sub>DD</sub> 0 |       |  |

| CE_PA[13:14]                                   | AG1, AF6                   | I/O | OV <sub>DD</sub>   | —     |  |

| CE_PA[15]                                      | B2                         | I/O | LV <sub>DD</sub> 0 |       |  |

| CE_PA[16]                                      | AF4                        | I/O | OV <sub>DD</sub>   | _     |  |

| CE_PA[17:21]                                   | B16, A16, E17, A17, B17    | I/O | LV <sub>DD</sub> 1 |       |  |

| CE_PA[22]                                      | AF3                        | I/O | OV <sub>DD</sub>   | _     |  |

| CE_PA[23:26]                                   | C18, D18, E18, A18         | I/O | LV <sub>DD</sub> 1 | —     |  |

| CE_PA[27:28]                                   | AF2, AE6                   | I/O | OV <sub>DD</sub>   | —     |  |

| CE_PA[29]                                      | B19                        | I/O | LV <sub>DD</sub> 1 | _     |  |

| CE_PA[30]                                      | AE5                        | I/O | OV <sub>DD</sub>   | —     |  |

| CE_PA[31]                                      | F16                        | I/O | LV <sub>DD</sub> 1 | —     |  |

**Pinout Listings**

| Signal                        | Package Pin Number                                                                                                | Pin Type         | Power<br>Supply    | Notes    |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------|--------------------|----------|

| CE_PB[0:27]                   | I/O                                                                                                               | OV <sub>DD</sub> | _                  |          |

| CE_PC[0:1]                    | V1, U6                                                                                                            | I/O              | OV <sub>DD</sub>   |          |

| CE_PC[2:3]                    | C16, A15                                                                                                          | I/O              | LV <sub>DD</sub> 1 | _        |

| CE_PC[4:6]                    | U4, U3, T6                                                                                                        | I/O              | OV <sub>DD</sub>   | _        |

| CE_PC[7]                      | C19                                                                                                               | I/O              | LV <sub>DD</sub> 2 | _        |

| CE_PC[8:9]                    | A4, C5                                                                                                            | I/O              | LV <sub>DD</sub> 0 | _        |

| CE_PC[10:30]                  | T5, T4, T2, T1, R5, R3, R1, C11, D12, F13, B10,<br>C10, E12, A9, B8, D10, A14, E15, B14, D15, AH2                 | I/O              | OV <sub>DD</sub>   | -        |

| CE_PD[0:27]                   | E11, D9, C8, F11, A7, E9, C7, A6, F10, B6, D7, E8, B5, A5, C2, E4, F5, B1, D2, G5, D1, E2, H6, F3, E1, F2, G3, H4 | I/O              | OV <sub>DD</sub>   | —        |

| CE_PE[0:31]                   | I/O                                                                                                               | OV <sub>DD</sub> | _                  |          |

| CE_PF[0:3]                    | F14, D13, A12, A11                                                                                                | I/O              | OV <sub>DD</sub>   | _        |

|                               | Clocks                                                                                                            |                  |                    |          |

| PCI_CLK_OUT[0]/CE_PF[26]      | B22                                                                                                               | I/O              | LV <sub>DD</sub> 2 | _        |

| PCI_CLK_OUT[1:2]/CE_PF[27:28] | D22, A23                                                                                                          | I/O              | OV <sub>DD</sub>   | _        |

| CLKIN                         | E37                                                                                                               | I                | OV <sub>DD</sub>   | _        |

| PCI_CLOCK/PCI_SYNC_IN         | M36                                                                                                               | I                | OV <sub>DD</sub>   | _        |

| PCI_SYNC_OUT/CE_PF[29]        | D37                                                                                                               | I/O              | OV <sub>DD</sub>   | 3        |

|                               | JTAG                                                                                                              |                  |                    | 1        |

| ТСК                           | K33                                                                                                               | I                | OV <sub>DD</sub>   | _        |

| TDI                           | K34                                                                                                               | I                | OV <sub>DD</sub>   | 4        |

| TDO                           | H37                                                                                                               | 0                | OV <sub>DD</sub>   | 3        |

| TMS                           | J36                                                                                                               | I                | OV <sub>DD</sub>   | 4        |

| TRST                          | L32                                                                                                               | I                | OV <sub>DD</sub>   | 4        |

|                               | Test                                                                                                              | I                |                    | 1        |

| TEST                          | L35                                                                                                               | I                | OV <sub>DD</sub>   | 7        |

| TEST_SEL                      | AU34                                                                                                              | I                | GV <sub>DD</sub>   | 10       |

|                               | РМС                                                                                                               | 1                | 55                 | <u>I</u> |

| QUIESCE                       | B36                                                                                                               | 0                | OV <sub>DD</sub>   | _        |

|                               | System Control                                                                                                    | 1                | L                  | I        |

#### Table 67. MPC8358E TBGA Pinout Listing (continued)

#### Table 67. MPC8358E TBGA Pinout Listing (continued)

| Signal             | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pin Type                                                        | Power<br>Supply    | Notes |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------|-------|

| PORESET            | L37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                               | OV <sub>DD</sub>   |       |

| HRESET             | L36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I/O                                                             | OV <sub>DD</sub>   | 1     |

| SRESET             | M33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I/O                                                             | OV <sub>DD</sub>   | 2     |

|                    | Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                 |                    |       |

| THERM0             | AP19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I                                                               | GV <sub>DD</sub>   | —     |

| THERM1             | AT31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I                                                               | GV <sub>DD</sub>   | —     |

|                    | Power and Ground Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                 |                    |       |

| AV <sub>DD</sub> 1 | K35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power for<br>LBIU DLL<br>(1.2 V)                                | AV <sub>DD</sub> 1 | _     |

| AV <sub>DD</sub> 2 | K36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power for<br>CE PLL<br>(1.2 V)                                  | AV <sub>DD</sub> 2 | _     |

| AV <sub>DD</sub> 5 | AM29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Power for<br>e300 PLL<br>(1.2 V)                                | AV <sub>DD</sub> 5 | _     |

| AV <sub>DD</sub> 6 | К37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power for<br>system<br>PLL (1.2 V)                              | AV <sub>DD</sub> 6 | _     |

| GND                | <ul> <li>A2, A8, A13, A19, A22, A25, A31, A33, A36, B7,<br/>B12, B24, B27, B30, C4, C6, C9, C15, C26, C32,<br/>D3, D8, D11, D14, D17, D19, D23, D27, E7, E13,<br/>E25, E30, E36, F4, F37, G34, H1, H5, H32, H33, J4,<br/>J32, J37, K1, L3, L5, L33, L34, M1, M34, M35, N37,<br/>P2, P5, P35, P36, R4, T3, U1, U5, U35, V37, W1,<br/>W4, W33, W36, Y34, AA3, AA5, AC3, AC32, AC35,<br/>AD1, AD37, AE4, AE34, AE36, AF33, AG4, AG6,<br/>AG32, AH35, AJ1, AJ4, AJ32, AJ35, AJ37, AK36,<br/>AL3, AL34, AM4, AN6, AN23, AN30, AP8, AP12,<br/>AP14, AP16, AP17, AP20, AP25, AR6, AR8, AR9,<br/>AR19, AR24, AR31, AR35, AR37, AT4, AT10, AT19,<br/>AT20, AT25, AU14, AU22, AU28, AU35</li> </ul> | _                                                               | _                  | -     |

| GV <sub>DD</sub>   | AD4, AE3, AF1, AF5, AF35, AF37, AG2, AG36,<br>AH33, AH34, AK5, AM1, AM35, AM37, AN2, AN10,<br>AN11, AN12, AN14, AN32, AN36, AP5, AP23,<br>AP28, AR1, AR7, AR10, AR12, AR21, AR25, AR27,<br>AR33, AT15, AT22, AT28, AT33, AU2, AU5, AU16,<br>AU31, AU36                                                                                                                                                                                                                                                                                                                                                                                                                                    | Power for<br>DDR<br>DRAM I/O<br>voltage<br>(2.5 or<br>1.8 V)    | GV <sub>DD</sub>   | _     |

| LV <sub>DD</sub> 0 | D5, D6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Power for<br>UCC1<br>Ethernet<br>interface<br>(2.5 V,<br>3.3 V) | LV <sub>DD</sub> 0 | —     |

| Index | SPMF | CORE<br>PLL | CEPMF | CEPDF | Input Clock<br>(MHz) | CSB Freq<br>(MHz) | Core Freq<br>(MHz) | QUICC<br>Engine Freq<br>(MHz) | 400<br>(MHz) | 533<br>(MHz) | 667<br>(MHz) |

|-------|------|-------------|-------|-------|----------------------|-------------------|--------------------|-------------------------------|--------------|--------------|--------------|

| Α     | 1000 | 0000011     | 01001 | 0     | 33                   | 266               | 400                | 300                           | 8            | 8            | 8            |

| В     | 0100 | 0000100     | 00110 | 0     | 66                   | 266               | 533                | 400                           | 8            | 8            | 8            |

Example 1. Sample Table Use

- **Example A.** To configure the device with CSB clock rate of 266 MHz, core rate of 400 MHz, and QUICC Engine clock rate 300 MHz while the input clock rate is 33 MHz. Conf No. 's10' and 'c1' are selected from Table 76. SPMF is 1000, CORPLL is 0000011, CEPMF is 01001, and CEPDF is 0.

- **Example B.** To configure the device with CSBCSB clock rate of 266 MHz, core rate of 533 MHz and QUICC Engine clock rate 400 MHz while the input clock rate is 66 MHz. Conf No. 's5h' and 'c2h' are selected from Table 76. SPMF is 0100, CORPLL is 0000100, CEPMF is 00110, and CEPDF is 0.

## 22 Thermal

This section describes the thermal specifications of the MPC8360E/58E.

## 22.1 Thermal Characteristics

This table provides the package thermal characteristics for the 37.5 mm  $\times$  37.5 mm 740-TBGA package.

Table 77. Package Thermal Characteristics for the TBGA Package

| Characteristic                                                    |                       | Value | Unit  | Notes |

|-------------------------------------------------------------------|-----------------------|-------|-------|-------|

| Junction-to-ambient natural convection on single-layer board (1s) | R <sub>θJA</sub>      | 15    | ° C/W | 1, 2  |

| Junction-to-ambient natural convection on four-layer board (2s2p) | R <sub>θJA</sub>      | 11    | ° C/W | 1, 3  |

| Junction-to-ambient (@1 m/s) on single-layer board (1s)           | R <sub>θJMA</sub>     | 10    | ° C/W | 1, 3  |

| Junction-to-ambient (@ 1 m/s) on four-layer board (2s2p)          | R <sub>θJMA</sub>     | 8     | ° C/W | 1, 3  |

| Junction-to-ambient (@ 2 m/s) on single-layer board (1s)          | R <sub>θJMA</sub>     | 9     | ° C/W | 1, 3  |

| Junction-to-ambient (@ 2 m/s) on four-layer board (2s2p)          | R <sub>θJMA</sub>     | 7     | ° C/W | 1, 3  |

| Junction-to-board thermal                                         | $R_{\theta JB}$       | 4.5   | ° C/W | 4     |

| Junction-to-case thermal                                          | $R_{	extsf{	heta}JC}$ | 1.1   | ° C/W | 5     |

where:

$T_I$  = junction temperature (° C)

$T_I = T_B + (R_{\theta IB} \times P_D)$

$T_B$  = board temperature at the package perimeter (° C)

$R_{\theta JA}$  = junction to board thermal resistance (° C/W) per JESD51-8

$P_D$  = power dissipation in the package (W)

When the heat loss from the package case to the air can be ignored, acceptable predictions of junction temperature can be made. The application board should be similar to the thermal test condition: the component is soldered to a board with internal planes.

#### 22.2.3 Experimental Determination of Junction Temperature

To determine the junction temperature of the device in the application after prototypes are available, the Thermal Characterization Parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using the following equation:

$$T_J = T_T + (\Psi_{JT} \times P_D)$$

where:

$T_J$  = junction temperature (° C)

$T_T$  = thermocouple temperature on top of package (° C)

$\Psi_{IT}$  = junction-to-ambient thermal resistance (° C/W)

$P_D$  = power dissipation in the package (W)

The thermal characterization parameter is measured per JESD51-2 specification using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

### 22.2.4 Heat Sinks and Junction-to-Ambient Thermal Resistance

In some application environments, a heat sink is required to provide the necessary thermal management of the device. When a heat sink is used, the thermal resistance is expressed as the sum of a junction to case thermal resistance and a case to ambient thermal resistance:

$R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$

where:

$R_{\theta JA}$  = junction-to-ambient thermal resistance (° C/W)

$R_{\theta JC}$  = junction-to-case thermal resistance (° C/W)

$R_{\theta CA}$  = case-to-ambient thermal resistance (° C/W)

$R_{\theta JC}$  is device related and cannot be influenced by the user. The user controls the thermal environment to change the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the size of the heat sink, the airflow around the device, the interface material, the mounting arrangement on printed-circuit board, or change the thermal dissipation on the printed-circuit board surrounding the device.

To illustrate the thermal performance of the devices with heat sinks, the thermal performance has been simulated with a few commercially available heat sinks. The heat sink choice is determined by the application environment (temperature, airflow, adjacent component power dissipation) and the physical space available. Because there is not a standard application environment, a standard heat sink is not required.

**Configuration Pin Muxing**

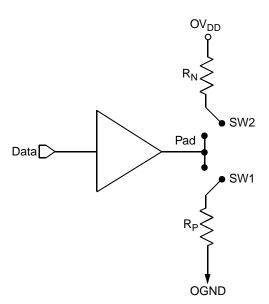

Figure 57. Driver Impedance Measurement

The value of this resistance and the strength of the driver's current source can be found by making two measurements. First, the output voltage is measured while driving logic 1 without an external differential termination resistor. The measured voltage is  $V_1 = R_{source} \times I_{source}$ . Second, the output voltage is measured while driving logic 1 with an external precision differential termination resistor of value  $R_{term}$ . The measured voltage is  $V_2 = 1/(1/R_1 + 1/R_2)) \times I_{source}$ . Solving for the output impedance gives  $R_{source} = R_{term} \times (V_1/V_2 - 1)$ . The drive current is then  $I_{source} = V_1/R_{source}$ .

This table summarizes the signal impedance targets. The driver impedance are targeted at minimum  $V_{DD}$ , nominal  $OV_{DD}$ , 105° C.

| Impedance      | Local Bus, Ethernet, DUART,<br>Control, Configuration, Power<br>Management | PCI       | DDR DRAM  | Symbol            | Unit |

|----------------|----------------------------------------------------------------------------|-----------|-----------|-------------------|------|

| R <sub>N</sub> | 42 Target                                                                  | 25 Target | 20 Target | Z <sub>0</sub>    | W    |

| R <sub>P</sub> | 42 Target                                                                  | 25 Target | 20 Target | Z <sub>0</sub>    | W    |

| Differential   | NA                                                                         | NA        | NA        | Z <sub>DIFF</sub> | W    |

**Table 79. Impedance Characteristics**

**Note:** Nominal supply voltages. See Table 1,  $T_J = 105^{\circ}$  C.

## 23.6 Configuration Pin Muxing

The device provides the user with power-on configuration options that can be set through the use of external pull-up or pull-down resistors of 4.7 k $\Omega$ on certain output pins (see customer visible configuration pins). These pins are generally used as output only pins in normal operation.

While HRESET is asserted however, these pins are treated as inputs. The value presented on these pins while HRESET is asserted, is latched when HRESET deasserts, at which time the input receiver is disabled and the I/O circuit takes on its normal function. Careful board layout with stubless connections to these pull-up/pull-down resistors coupled with the large value of the pull-up/pull-down resistor should minimize the disruption of signal quality or speed for output pins thus configured.