## NXP USA Inc. - <u>MPC8360CZUADDH Datasheet</u>

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e300                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 266MHz                                                                 |

| Co-Processors/DSP               | Communications; QUICC Engine                                           |

| RAM Controllers                 | DDR, DDR2                                                              |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (1)                                                    |

| SATA                            | -                                                                      |

| USB                             | USB 1.x (1)                                                            |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                     |

| Security Features               | -                                                                      |

| Package / Case                  | 740-LBGA                                                               |

| Supplier Device Package         | 740-TBGA (37.5x37.5)                                                   |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8360czuaddh |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

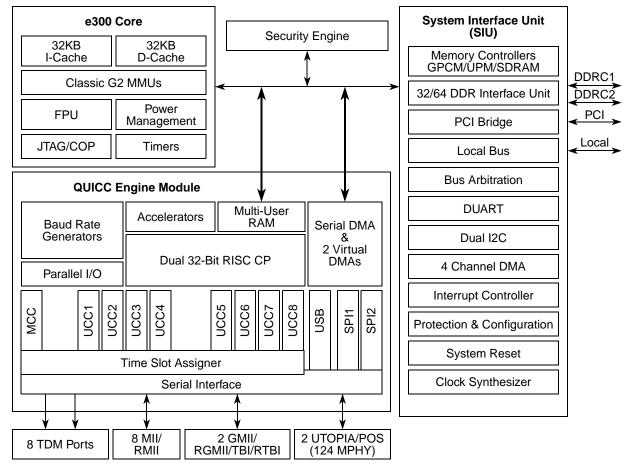

wide range of protocols including ATM, Ethernet, HDLC, and POS. The QUICC Engine module's enhanced interworking eases the transition and reduces investment costs from ATM to IP based systems. The other major features include a dual DDR SDRAM memory controller for the MPC8360E, which allows equipment providers to partition system parameters and data in an extremely efficient way, such as using one 32-bit DDR memory controller for control plane processing and the other for data plane processing. The MPC8358E has a single DDR SDRAM memory controller. The MPC8360E/58E also offers a 32-bit PCI controller, a flexible local bus, and a dedicated security engine.

This figure shows the MPC8360Eblock diagram.

Figure 1. MPC8360E Block Diagram

#### **Power Sequencing**

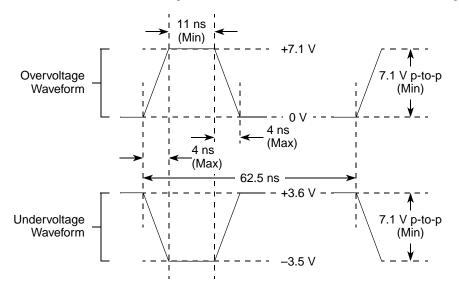

This figure shows the undershoot and overshoot voltage of the PCI interface of the device for the 3.3-V signals, respectively.

Figure 4. Maximum AC Waveforms on PCI interface for 3.3-V Signaling

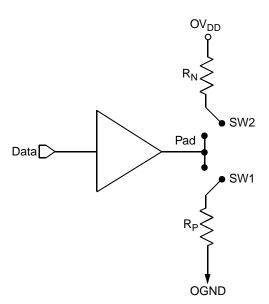

### 2.1.3 Output Driver Characteristics

This table provides information on the characteristics of the output driver strengths. The values are preliminary estimates.

| Driver Type                                        | Output Impedance (Ω)                       | Supply Voltage                                           |

|----------------------------------------------------|--------------------------------------------|----------------------------------------------------------|

| Local bus interface utilities signals              | 42                                         | OV <sub>DD</sub> = 3.3 V                                 |

| PCI signals                                        | 25                                         |                                                          |

| PCI output clocks (including PCI_SYNC_OUT)         | 42                                         |                                                          |

| DDR signal                                         | 20<br>36 (half-strength mode) <sup>1</sup> | GV <sub>DD</sub> = 2.5 V                                 |

| DDR2 signal                                        | 18<br>36 (half-strength mode) <sup>1</sup> | GV <sub>DD</sub> = 1.8 V                                 |

| 10/100/1000 Ethernet signals                       | 42                                         | LV <sub>DD</sub> = 2.5/3.3 V                             |

| DUART, system control, I <sup>2</sup> C, SPI, JTAG | 42                                         | OV <sub>DD</sub> = 3.3 V                                 |

| GPIO signals                                       | 42                                         | OV <sub>DD</sub> = 3.3 V<br>LV <sub>DD</sub> = 2.5/3.3 V |

Note:

1. DDR output impedance values for half strength mode are verified by design and not tested.

## 2.2 Power Sequencing

This section details the power sequencing considerations for the MPC8360E/58E.

| Table 4. MPC8360E TBGA Core Power Dissipa | tion <sup>1</sup> (continued) |

|-------------------------------------------|-------------------------------|

|-------------------------------------------|-------------------------------|

| Core<br>Frequency (MHz) | CSB<br>Frequency (MHz) | QUICC Engine<br>Frequency (MHz) | Typical | Maximum | Unit | Notes      |

|-------------------------|------------------------|---------------------------------|---------|---------|------|------------|

| 667                     | 333                    | 500                             | 6.1     | 6.8     | W    | 2, 3, 5, 9 |

#### Notes:

- 1. The values do not include I/O supply power (OV<sub>DD</sub>, LV<sub>DD</sub>, GV<sub>DD</sub>) or AV<sub>DD</sub>. For I/O power values, see Table 6.

- 2. Typical power is based on a voltage of  $V_{DD}$  = 1.2 V or 1.3 V, a junction temperature of  $T_J$  = 105°C, and a Dhrystone benchmark application.

- 3. Thermal solutions need to design to a value higher than typical power on the end application, T<sub>A</sub> target, and I/O power.

- 4. Maximum power is based on a voltage of V<sub>DD</sub> = 1.2 V, WC process, a junction T<sub>J</sub> = 105°C, and an artificial smoke test.

- Maximum power is based on a voltage of V<sub>DD</sub> = 1.3 V for applications that use 667 MHz (CPU)/500 (QE) with WC process, a junction T<sub>1</sub> = 105° C, and an artificial smoke test.

- 6. Typical power is based on a voltage of  $V_{DD}$  = 1.3 V, a junction temperature of  $T_J$  = 70° C, and a Dhrystone benchmark application.

- Maximum power is based on a voltage of V<sub>DD</sub> = 1.3 V for applications that use 667 MHz (CPU) or 500 (QE) with WC process, a junction T<sub>J</sub> = 70° C, and an artificial smoke test.

- 8. This frequency combination is only available for rev. 2.0 silicon.

- 9. This frequency combination is not available for rev. 2.0 silicon.

#### Table 5. MPC8358E TBGA Core Power Dissipation<sup>1</sup>

| Core<br>Frequency (MHz) | CSB<br>Frequency (MHz) | QUICC Engine<br>Frequency (MHz) | Typical | Maximum | Unit | Notes   |

|-------------------------|------------------------|---------------------------------|---------|---------|------|---------|

| 266                     | 266                    | 300                             | 4.1     | 4.5     | W    | 2, 3, 4 |

| 400                     | 266                    | 400                             | 4.5     | 5.0     | W    | 2, 3, 4 |

#### Notes:

- 1. The values do not include I/O supply power (OV<sub>DD</sub>,  $LV_{DD}$ ,  $GV_{DD}$ ) or  $AV_{DD}$ . For I/O power values, see Table 6.

- Typical power is based on a voltage of V<sub>DD</sub> = 1.2 V, a junction temperature of T<sub>J</sub> = 105°C, and a Dhrystone benchmark application.

- 3. Thermal solutions need to design to a value higher than typical power on the end application, T<sub>A</sub> target, and I/O power.

- 4. Maximum power is based on a voltage of V<sub>DD</sub> = 1.2 V, WC process, a junction T<sub>J</sub> = 105°C, and an artificial smoke test.

**QUICC Engine Block Operating Frequency Limitations**

# 5.3 QUICC Engine Block Operating Frequency Limitations

This section specify the limits of the AC electrical characteristics for the operation of the QUICC Engine block's communication interfaces.

### NOTE

The settings listed below are required for correct hardware interface operation. Each protocol by itself requires a minimal QUICC Engine block operating frequency setting for meeting the performance target. Because the performance is a complex function of all the QUICC Engine block settings, the user should make use of the QUICC Engine block performance utility tool provided by Freescale to validate their system.

This table lists the maximal QUICC Engine block I/O frequencies and the minimal QUICC Engine block core frequency for each interface.

| Interface                     | Interface Operating<br>Frequency (MHz) | Max Interface Bit<br>Rate (Mbps) | Min QUICC Engine<br>Operating<br>Frequency <sup>1</sup> (MHz) | Notes |

|-------------------------------|----------------------------------------|----------------------------------|---------------------------------------------------------------|-------|

| Ethernet Management: MDC/MDIO | 10 (max)                               | 10                               | 20                                                            | —     |

| MII                           | 25 (typ)                               | 100                              | 50                                                            | —     |

| RMII                          | 50 (typ)                               | 100                              | 50                                                            | —     |

| GMII/RGMII/TBI/RTBI           | 125 (typ)                              | 1000                             | 250                                                           |       |

| SPI (master/slave)            | 10 (max)                               | 10                               | 20                                                            | —     |

| UCC through TDM               | 50 (max)                               | 50 (max) 70                      |                                                               | 2     |

| MCC                           | 25 (max) 16.67                         |                                  | 16 × F                                                        | 2, 4  |

| UTOPIA L2                     | 50 (max)                               | 50 (max) 800 2 × F               |                                                               | 2     |

| POS-PHY L2                    | 50 (max)                               | 800                              | 800 2 × F                                                     |       |

| HDLC bus                      | 10 (max)                               | 10                               | 20                                                            | _     |

| HDLC/transparent              | 50 (max)                               | 50 (max) 50 8/3 >                |                                                               | 2, 3  |

| UART/async HDLC               | 3.68 (max internal ref clock)          |                                  |                                                               | —     |

| BISYNC                        | 2 (max)                                | 2 20                             |                                                               | —     |

| USB                           | 48 (ref clock)                         | 12                               | 96                                                            |       |

#### Table 13. QUICC Engine Block Operating Frequency Limitations

Notes:

1. The QUICC Engine module needs to run at a frequency higher than or equal to what is listed in this table.

2. 'F' is the actual interface operating frequency.\

3. The bit rate limit is independent of the data bus width (that is, the same for serial, nibble, or octal interfaces).

4. TDM in high-speed mode for serial data interface.

# 6 DDR and DDR2 SDRAM

This section describes the DC and AC electrical specifications for the DDR and DDR2 SDRAM interface of the MPC8360E/58E.

#### DDR and DDR2 SDRAM AC Electrical Characteristics

| Parameter/Condition                                     | Symbol            | Min                      | Мах                      | Unit | Notes |

|---------------------------------------------------------|-------------------|--------------------------|--------------------------|------|-------|

| Input high voltage                                      | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.18 | GV <sub>DD</sub> + 0.3   | V    |       |

| Input low voltage                                       | V <sub>IL</sub>   | -0.3                     | MV <sub>REF</sub> – 0.18 | V    | _     |

| Output leakage current                                  | I <sub>OZ</sub>   | —                        | ±10                      | μA   | 4     |

| Output high current (V <sub>OUT</sub> = 1.95 V)         | I <sub>ОН</sub>   | -15.2                    |                          | mA   | —     |

| Output low current (V <sub>OUT</sub> = 0.35 V)          | I <sub>OL</sub>   | 15.2                     | _                        | mA   | _     |

| MV <sub>REF</sub> input leakage current                 | I <sub>VREF</sub> | —                        | ±10                      | μA   | —     |

| Input current (0 V ≰⁄ <sub>IN</sub> ≤OV <sub>DD</sub> ) | I <sub>IN</sub>   | —                        | ±10                      | μA   | _     |

#### Table 16. DDR SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 2.5 V (continued)

#### Notes:

1.  $GV_{DD}$  is expected to be within 50 mV of the DRAM  $GV_{DD}$  at all times.

- 2.  $MV_{REF}$  is expected to be equal to  $0.5 \times GV_{DD}$ , and to track  $GV_{DD}$  DC variations as measured at the receiver. Peak-to-peak noise on  $MV_{REF}$  may not exceed ±2% of the DC value.

- 3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail should track variations in the DC level of MV<sub>REF</sub>.

- 4. Output leakage is measured with all outputs disabled, 0 V  $\leq$ V<sub>OUT</sub>  $\leq$ GV<sub>DD</sub>.

This table provides the DDR capacitance when  $GV_{DD}(typ) = 2.5$  V.

#### Table 17. DDR SDRAM Capacitance for GV<sub>DD</sub>(typ) = 2.5 V

| Parameter/Condition                     | Symbol           | Min | Мах | Unit | Notes |

|-----------------------------------------|------------------|-----|-----|------|-------|

| Input/output capacitance: DQ, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1     |

| Delta input/output capacitance: DQ, DQS | C <sub>DIO</sub> | —   | 0.5 | pF   | 1     |

Note:

1. This parameter is sampled.  $GV_{DD}$  = 2.5 V ± 0.125 V, f = 1 MHz, T<sub>A</sub> = 25°C, V<sub>OUT</sub> =  $GV_{DD}/2$ , V<sub>OUT</sub> (peak-to-peak) = 0.2 V.

## 6.2 DDR and DDR2 SDRAM AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR and DDR2 SDRAM interface.

## 6.2.1 DDR and DDR2 SDRAM Input AC Timing Specifications

This table provides the input AC timing specifications for the DDR2 SDRAM interface when  $GV_{DD}(typ) = 1.8 V$ .

#### Table 18. DDR2 SDRAM Input AC Timing Specifications for GV<sub>DD</sub>(typ) = 1.8 V

At recommended operating conditions with  $GV_{DD}$  of 1.8 V ± 5%.

| Parameter             | Symbol          | Min                      | Мах                      | Unit | Notes |

|-----------------------|-----------------|--------------------------|--------------------------|------|-------|

| AC input low voltage  | V <sub>IL</sub> | _                        | MV <sub>REF</sub> – 0.25 | V    | —     |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.25 |                          | V    | —     |

#### **DDR and DDR2 SDRAM AC Electrical Characteristics**

This table provides the input AC timing specifications for the DDR SDRAM interface when  $GV_{DD}(typ) = 2.5 \text{ V}$ .

#### Table 19. DDR SDRAM Input AC Timing Specifications

At recommended operating conditions with  $GV_{DD}$  of 2.5 V ± 5%.

| Parameter             | Symbol          | Min                      | Мах                      | Unit | Notes |

|-----------------------|-----------------|--------------------------|--------------------------|------|-------|

| AC input low voltage  | V <sub>IL</sub> | _                        | MV <sub>REF</sub> – 0.31 | V    | —     |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.31 | _                        | V    | —     |

#### Table 20. DDR and DDR2 SDRAM Input AC Timing Specifications Mode

At recommended operating conditions with  $GV_{DD}$  of (1.8 or 2.5 V) ± 5%.

| Parameter                                                          | Symbol | Min                    | Мах                 | Unit | Notes |

|--------------------------------------------------------------------|--------|------------------------|---------------------|------|-------|

| MDQS—MDQ/MECC input skew per byte<br>333 MHz<br>266 MHz<br>200 MHz |        | -750<br>-1125<br>-1250 | 750<br>1125<br>1250 | ps   | 1, 2  |

#### Notes:

1. AC timing values are based on the DDR data rate, which is twice the DDR memory bus frequency.

Maximum possible skew between a data strobe (MDQS[n]) and any corresponding bit of data (MDQ[8n + {0...7}] if 0 ≤n ≤7) or ECC (MECC[{0...7}] if n = 8).

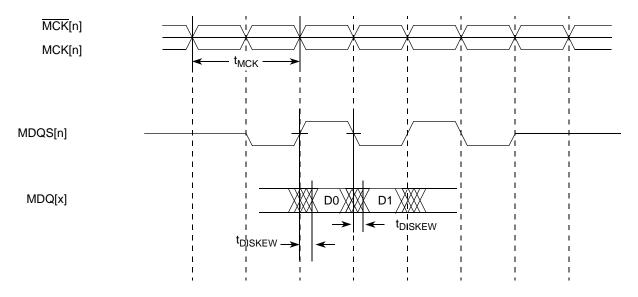

This figure shows the input timing diagram for the DDR controller.

Figure 6. DDR Input Timing Diagram

#### GMII, MII, RMII, TBI, RGMII, and RTBI AC Timing Specifications

Physical Layer Device Specification Version 1.2a (9/22/2000). The electrical characteristics for the MDIO and MDC are specified in Section 8.3, "Ethernet Management Interface Electrical Characteristics."

## 8.1.1 10/100/1000 Ethernet DC Electrical Characteristics

The electrical characteristics specified here apply to media independent interface (MII), reduced gigabit media independent interface (RGMII), reduced ten-bit interface (RTBI), reduced media independent interface (RMII) signals, management data input/output (MDIO) and management data clock (MDC).

The MII and RMII interfaces are defined for 3.3 V, while the RGMII and RTBI interfaces can be operated at 2.5 V. The RGMII and RTBI interfaces follow the *Reduced Gigabit Media-Independent Interface (RGMII) Specification Version 1.3*. The RMII interface follows the *RMII Consortium RMII Specification Version 1.2*.

Table 25. RGMII/RTBI, GMII, TBI, MII, and RMII DC Electrical Characteristics (when operating at 3.3 V)

| Parameter            | Symbol           | Conditions                             |                        | Min  | Max                    | Unit | Notes |

|----------------------|------------------|----------------------------------------|------------------------|------|------------------------|------|-------|

| Supply voltage 3.3 V | LV <sub>DD</sub> | —                                      |                        | 2.97 | 3.63                   | V    | 1     |

| Output high voltage  | V <sub>OH</sub>  | I <sub>OH</sub> = -4.0 mA              | LV <sub>DD</sub> = Min | 2.40 | LV <sub>DD</sub> + 0.3 | V    | _     |

| Output low voltage   | V <sub>OL</sub>  | I <sub>OL</sub> = 4.0 mA               | LV <sub>DD</sub> = Min | GND  | 0.50                   | V    | _     |

| Input high voltage   | V <sub>IH</sub>  | _                                      | —                      | 2.0  | LV <sub>DD</sub> + 0.3 | V    | _     |

| Input low voltage    | V <sub>IL</sub>  | _                                      | —                      | -0.3 | 0.90                   | V    | _     |

| Input current        | I <sub>IN</sub>  | 0 V ≤V <sub>IN</sub> ≤LV <sub>DD</sub> |                        | —    | ±10                    | μA   | _     |

#### Note:

1. GMII/MII pins that are not needed for RGMII, RMII, or RTBI operation are powered by the OV<sub>DD</sub> supply.

| Table 26. RGMII/RTBI DC Electrical Characteristics | (when operating at 2.5 V) |

|----------------------------------------------------|---------------------------|

|----------------------------------------------------|---------------------------|

| Parameters           | Symbol           | Conditions                                 |                 | Min       | Max                    | Unit |

|----------------------|------------------|--------------------------------------------|-----------------|-----------|------------------------|------|

| Supply voltage 2.5 V | LV <sub>DD</sub> | —                                          |                 | 2.37      | 2.63                   | V    |

| Output high voltage  | V <sub>OH</sub>  | $I_{OH} = -1.0 \text{ mA}$ $LV_{DD} = Min$ |                 | 2.00      | LV <sub>DD</sub> + 0.3 | V    |

| Output low voltage   | V <sub>OL</sub>  | I <sub>OL</sub> = 1.0 mA                   | $LV_{DD} = Min$ | GND – 0.3 | 0.40                   | V    |

| Input high voltage   | V <sub>IH</sub>  | —                                          | $LV_{DD} = Min$ | 1.7       | LV <sub>DD</sub> + 0.3 | V    |

| Input low voltage    | V <sub>IL</sub>  | —                                          | $LV_{DD} = Min$ | -0.3      | 0.70                   | V    |

| Input current        | I <sub>IN</sub>  | 0 V ≤V <sub>IN</sub> ≤LV <sub>DD</sub>     |                 | —         | ±10                    | μA   |

## 8.2 GMII, MII, RMII, TBI, RGMII, and RTBI AC Timing Specifications

The AC timing specifications for GMII, MII, TBI, RGMII, and RTBI are presented in this section.

## 8.2.1 GMII Timing Specifications

This sections describe the GMII transmit and receive AC timing specifications.

GMII, MII, RMII, TBI, RGMII, and RTBI AC Timing Specifications

## 8.2.1.2 GMII Receive AC Timing Specifications

This table provides the GMII receive AC timing specifications.

#### **Table 28. GMII Receive AC Timing Specifications**

At recommended operating conditions with LV\_{DD}/OV\_{DD} of 3.3 V  $\pm$  10%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit | Notes |

|---------------------------------------------|-------------------------------------|-----|-----|-----|------|-------|

| RX_CLK clock period                         | t <sub>GRX</sub>                    | _   | 8.0 | _   | ns   | —     |

| RX_CLK duty cycle                           | t <sub>GRXH</sub> /t <sub>GRX</sub> | 40  | —   | 60  | %    | _     |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>GRDVKH</sub>                 | 2.0 | —   | _   | ns   | _     |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>GRDXKH</sub>                 | 0.2 | —   | _   | ns   | 2     |

| RX_CLK clock rise time, (20% to 80%)        | t <sub>GRXR</sub>                   | _   | —   | 1.0 | ns   | _     |

| RX_CLK clock fall time, (80% to 20%)        | t <sub>GRXF</sub>                   | _   |     | 1.0 | ns   | _     |

#### Notes:

- 1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>GRDVKH</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>RX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>RX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>GRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GRX</sub> represents the GMII (G) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- In rev. 2.0 silicon, due to errata, t<sub>GRDXKH</sub> minimum is 0.5 which is not compliant with the standard. Refer to Errata QE\_ENET18 in Chip Errata for the MPC8360E, Rev. 1.

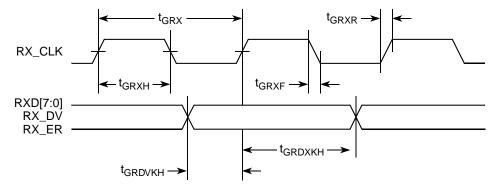

This figure shows the GMII receive AC timing diagram.

Figure 11. GMII Receive AC Timing Diagram

## 8.2.2 MII AC Timing Specifications

This section describes the MII transmit and receive AC timing specifications.

### 8.2.2.1 MII Transmit AC Timing Specifications

This table provides the MII transmit AC timing specifications.

#### Table 29. MII Transmit AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/OV_{DD}$  of 3.3 V ± 10%.

| Parameter/Condition                             | Symbol <sup>1</sup>                        | Min | Тур | Max     | Unit |

|-------------------------------------------------|--------------------------------------------|-----|-----|---------|------|

| TX_CLK clock period 10 Mbps                     | t <sub>MTX</sub>                           | _   | 400 | —       | ns   |

| TX_CLK clock period 100 Mbps                    | t <sub>MTX</sub>                           | _   | 40  | _       | ns   |

| TX_CLK duty cycle                               | t <sub>MTXH</sub> /t <sub>MTX</sub>        | 35  | _   | 65      | %    |

| TX_CLK to MII data TXD[3:0], TX_ER, TX_EN delay | t <sub>MTKHDX</sub><br>t <sub>MTKHDV</sub> | 1   | 5   | —<br>15 | ns   |

| TX_CLK data clock rise time, (20% to 80%)       | t <sub>MTXR</sub>                          | 1.0 | _   | 4.0     | ns   |

| TX_CLK data clock fall time, (80% to 20%)       | t <sub>MTXF</sub>                          | 1.0 | _   | 4.0     | ns   |

#### Note:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub></sub>

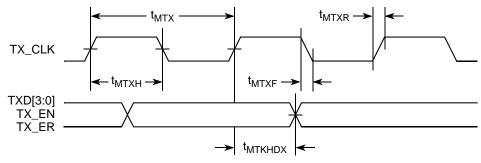

This figure shows the MII transmit AC timing diagram.

Figure 12. MII Transmit AC Timing Diagram

GMII, MII, RMII, TBI, RGMII, and RTBI AC Timing Specifications

## 8.2.2.2 MII Receive AC Timing Specifications

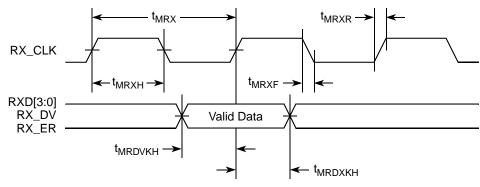

This table provides the MII receive AC timing specifications.

#### Table 30. MII Receive AC Timing Specifications

At recommended operating conditions with LV\_{DD}/OV\_{DD} of 3.3 V  $\pm$  10%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min  | Тур | Max | Unit |

|---------------------------------------------|-------------------------------------|------|-----|-----|------|

| RX_CLK clock period 10 Mbps                 | t <sub>MRX</sub>                    | _    | 400 | —   | ns   |

| RX_CLK clock period 100 Mbps                | t <sub>MRX</sub>                    | _    | 40  | —   | ns   |

| RX_CLK duty cycle                           | t <sub>MRXH</sub> /t <sub>MRX</sub> | 35   | —   | 65  | %    |

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>MRDVKH</sub>                 | 10.0 | —   | —   | ns   |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>MRDXKH</sub>                 | 10.0 | —   | —   | ns   |

| RX_CLK clock rise time, (20% to 80%)        | t <sub>MRXR</sub>                   | 1.0  | —   | 4.0 | ns   |

| RX_CLK clock fall time, (80% to 20%)        | t <sub>MRXF</sub>                   | 1.0  | —   | 4.0 | ns   |

#### Note:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub>

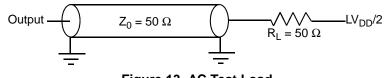

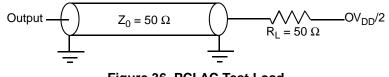

This figure provides the AC test load.

This figure shows the MII receive AC timing diagram.

Figure 14. MII Receive AC Timing Diagram

## 8.2.5 RGMII and RTBI AC Timing Specifications

This table presents the RGMII and RTBI AC timing specifications.

#### Table 35. RGMII and RTBI AC Timing Specifications

At recommended operating conditions with  $LV_{DD}$  of 2.5 V ± 5%.

| Parameter/Condition                        | Symbol <sup>1</sup>                              | Min      | Тур | Мах      | Unit | Notes |

|--------------------------------------------|--------------------------------------------------|----------|-----|----------|------|-------|

| Data to clock output skew (at transmitter) | t <sub>SKRGTKHDX</sub><br>t <sub>SKRGTKHDV</sub> | -0.5<br> | —   | —<br>0.5 | ns   | 7     |

| Data to clock input skew (at receiver)     | t <sub>SKRGDXKH</sub><br>t <sub>SKRGDVKH</sub>   | 1.0      | —   | <br>2.6  | ns   | 2     |

| Clock cycle duration                       | t <sub>RGT</sub>                                 | 7.2      | 8.0 | 8.8      | ns   | 3     |

| Duty cycle for 1000Base-T                  | t <sub>RGTH</sub> /t <sub>RGT</sub>              | 45       | 50  | 55       | %    | 4, 5  |

| Duty cycle for 10BASE-T and 100BASE-TX     | t <sub>RGTH</sub> /t <sub>RGT</sub>              | 40       | 50  | 60       | %    | 3, 5  |

| Rise time (20–80%)                         | t <sub>RGTR</sub>                                | _        | —   | 0.75     | ns   | —     |

| Fall time (20–80%)                         | t <sub>RGTF</sub>                                | _        | —   | 0.75     | ns   | —     |

| GTX_CLK125 reference clock period          | t <sub>G125</sub>                                | _        | 8.0 | _        | ns   | 6     |

| GTX_CLK125 reference clock duty cycle      | t <sub>G125H</sub> /t <sub>G125</sub>            | 47       | —   | 53       | %    | —     |

Notes:

- Note that, in general, the clock reference symbol representation for this section is based on the symbols RGT to represent RGMII and RTBI timing. For example, the subscript of t<sub>RGT</sub> represents the TBI (T) receive (Rx) clock. Note also that the notation for rise (R) and fall (F) times follows the clock symbol that is being represented. For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (RGT).

- 2. This implies that PC board design requires clocks to be routed such that an additional trace delay of greater than 1.5 ns can be added to the associated clock signal.

- 3. For 10 and 100 Mbps,  $t_{RGT}$  scales to 400 ns ± 40 ns and 40 ns ± 4 ns, respectively.

- 4. Duty cycle may be stretched/shrunk during speed changes or while transitioning to a received packet's clock domains as long as the minimum duty cycle is not violated and stretching occurs for no more than three t<sub>RGT</sub> of the lowest speed transitioned between.

- 5. Duty cycle reference is LV<sub>DD</sub>/2.

- 6. This symbol is used to represent the external GTX\_CLK125 and does not follow the original symbol naming convention.

- 7. In rev. 2.0 silicon, due to errata, t<sub>SKRGTKHDX</sub> minimum is –2.3 ns and t<sub>SKRGTKHDV</sub> maximum is 1 ns for UCC1, 1.2 ns for UCC2 option 1, and 1.8 ns for UCC2 option 2. In rev. 2.1 silicon, due to errata, t<sub>SKRGTKHDX</sub> minimum is –0.65 ns for UCC2 option 1 and –0.9 for UCC2 option 2, and t<sub>SKRGTKHDV</sub> maximum is 0.75 ns for UCC1 and UCC2 option 1 and 0.85 for UCC2 option 2. Refer to Errata QE\_ENET10 in *Chip Errata for the MPC8360E, Rev. 1*. UCC1 does meet t<sub>SKRGTKHDX</sub> minimum for rev. 2.1 silicon.

**PCI AC Electrical Specifications**

#### Table 47. PCI AC Timing Specifications at 66 MHz (continued)

| Parameter                      | Symbol <sup>1</sup> | Min | Мах | Unit | Notes   |

|--------------------------------|---------------------|-----|-----|------|---------|

| Clock to output high impedance | t <sub>PCKHOZ</sub> | —   | 14  | ns   | 2, 3    |

| Input setup to clock           | t <sub>PCIVKH</sub> | 3.0 | _   | ns   | 2, 4    |

| Input hold from clock          | t <sub>PCIXKH</sub> | 0.3 | _   | ns   | 2, 4, 6 |

Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>PCIVKH</sub> symbolizes PCI timing (PC) with respect to the time the input signals (I) reach the valid state (V) relative to the PCI\_SYNC\_IN clock, t<sub>SYS</sub>, reference (K) going to the high (H) state or setup time. Also, t<sub>PCRHFV</sub> symbolizes PCI timing (PC) with respect to the time hard reset (R) went high (H) relative to the frame signal (F) going to the valid (V) state.

</sub>

- 2. See the timing measurement conditions in the PCI 2.2 Local Bus Specifications.

- 3. For purposes of active/float timing measurements, the Hi-Z or off-state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 4. Input timings are measured at the pin.

- 5. In rev. 2.0 silicon, due to errata, t<sub>PCIHOV</sub> maximum is 6.6 ns. Refer to Errata PCI21 in Chip Errata for the MPC8360E, Rev. 1.

- 6. In rev. 2.0 silicon, due to errata, t<sub>PCIXKH</sub> minimum is 1 ns. Refer to Errata PCI17 in Chip Errata for the MPC8360E, Rev. 1.

#### Table 48. PCI AC Timing Specifications at 33 MHz

| Parameter                      | Symbol <sup>1</sup> | Min | Мах | Unit | Notes   |

|--------------------------------|---------------------|-----|-----|------|---------|

| Clock to output valid          | t <sub>PCKHOV</sub> | —   | 11  | ns   | 2       |

| Output hold from clock         | t <sub>PCKHOX</sub> | 2   | _   | ns   | 2       |

| Clock to output high impedance | t <sub>PCKHOZ</sub> | —   | 14  | ns   | 2, 3    |

| Input setup to clock           | t <sub>PCIVKH</sub> | 7.0 | _   | ns   | 2, 2    |

| Input hold from clock          | t <sub>PCIXKH</sub> | 0.3 | —   | ns   | 2, 4, 5 |

#### Notes:

- The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>PCIVKH</sub> symbolizes PCI timing (PC) with respect to the time the input signals (I) reach the valid state (V) relative to the PCI\_SYNC\_IN clock, t<sub>SYS</sub>, reference (K) going to the high (H) state or setup time. Also, t<sub>PCRHFV</sub> symbolizes PCI timing (PC) with respect to the time hard reset (R) went high (H) relative to the frame signal (F) going to the valid (V) state.

- 2. See the timing measurement conditions in the PCI 2.2 Local Bus Specifications.

- 3. For purposes of active/float timing measurements, the Hi-Z or off-state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 4. Input timings are measured at the pin.

- 5. In rev. 2.0 silicon, due to errata, t<sub>PCIXKH</sub> minimum is 1 ns. Refer to Errata PCI17 in Chip Errata for the MPC8360E, Rev. 1.

This figure provides the AC test load for PCI.

Figure 36. PCI AC Test Load

**Pinout Listings**

| Signal                             | Package Pin Number                                                                                                           | Pin Type | Power<br>Supply    | Notes |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------|--------------------|-------|

| MEMC1_MCKE[0:1]                    | AL32, AU33                                                                                                                   | 0        | GV <sub>DD</sub>   | 3     |

| MEMC1_MCK[0:1]                     | AK37, AT37                                                                                                                   | 0        | GV <sub>DD</sub>   | —     |

| MEMC1_MCK[2:3]/<br>MEMC2_MCK[0:1]  | AN1, AR2                                                                                                                     | 0        | GV <sub>DD</sub>   | _     |

| MEMC1_MCK[4:5]/<br>MEMC2_MCKE[0:1] | AN25, AK1                                                                                                                    | 0        | GV <sub>DD</sub>   | _     |

| MEMC1_MCK[0:1]                     | AL37, AT36                                                                                                                   | 0        | GV <sub>DD</sub>   | —     |

| MEMC1_MCK[2:3]/<br>MEMC2_MCK[0:1]  | AP2, AT2                                                                                                                     | 0        | GV <sub>DD</sub>   |       |

| MEMC1_MCK[4]/<br>MEMC2_MDM[8]      | AN24                                                                                                                         | 0        | GV <sub>DD</sub>   | —     |

| MEMC1_MCK[5]/<br>MEMC2_MDQS[8]     | AL1                                                                                                                          | 0        | GV <sub>DD</sub>   | —     |

| MDIC[0:1]                          | AH6, AP30                                                                                                                    | I/O      | GV <sub>DD</sub>   | 10    |

| S                                  | Secondary DDR SDRAM Memory Controller Interface                                                                              |          | •                  | 1     |

| MEMC2_MECC[0:7]                    | AN16, AP18, AM16, AM17, AN17, AP13, AP15, AN13                                                                               | I/O      | GV <sub>DD</sub>   | -     |

| MEMC2_MBA[0:2]                     | AU12, AU15, AU13                                                                                                             | 0        | GV <sub>DD</sub>   | _     |

| MEMC2_MA[0:14]                     | AT12, AP11, AT13, AT14, AR13, AR15, AR16,<br>AT16, AT18, AT17, AP10, AR20, AR17, AR14,<br>AR11                               | 0        | GV <sub>DD</sub>   | -     |

| MEMC2_MWE                          | AU10                                                                                                                         | 0        | GV <sub>DD</sub>   | —     |

| MEMC2_MRAS                         | AT11                                                                                                                         | 0        | GV <sub>DD</sub>   | —     |

| MEMC2_MCAS                         | AU11                                                                                                                         | 0        | GV <sub>DD</sub>   | —     |

|                                    | PCI                                                                                                                          |          |                    | •     |

| PCI_INTA/IRQ_OUT/CE_PF[5]          | A20                                                                                                                          | I/O      | LV <sub>DD</sub> 2 | 2     |

| PCI_RESET_OUT/CE_PF[6]             | E19                                                                                                                          | I/O      | LV <sub>DD</sub> 2 |       |

| PCI_AD[31:30]/CE_PG[31:30]         | D20, D21                                                                                                                     | I/O      | LV <sub>DD</sub> 2 |       |

| PCI_AD[29:25]/CE_PG[29:25]         | A24, B23, C23, E23, A26                                                                                                      | I/O      | OV <sub>DD</sub>   | —     |

| PCI_AD[24]/CE_PG[24]               | B21                                                                                                                          | I/O      | LV <sub>DD</sub> 2 | —     |

| PCI_AD[23:0]/CE_PG[23:0]           | C24, C25, D25, B25, E24, F24, A27, A28, F27, A30,<br>C30, D30, E29, B31, C31, D31, D32, A32, C33,<br>B33, F30, E31, A34, D33 | I/O      | OV <sub>DD</sub>   | -     |

| PCI_C/BE[3:0]/CE_PF[10:7]          | E22, B26, E28, F28                                                                                                           | I/O      | OV <sub>DD</sub>   | —     |

| PCI_PAR/CE_PF[11]                  | D28                                                                                                                          | I/O      | OV <sub>DD</sub>   | -     |

| PCI_FRAME/CE_PF[12]                | D26                                                                                                                          | I/O      | OV <sub>DD</sub>   | 5     |

| PCI_TRDY/CE_PF[13]                 | C27                                                                                                                          | I/O      | OV <sub>DD</sub>   | 5     |

| PCI_IRDY/CE_PF[14]                 | C28                                                                                                                          | I/O      | OV <sub>DD</sub>   | 5     |

| PCI_STOP/CE_PF[15]                 | B28                                                                                                                          | I/O      | OV <sub>DD</sub>   | 5     |

**Pinout Listings**

#### Table 66. MPC8360E TBGA Pinout Listing (continued)

| Signal                                         | Package Pin Number                | Pin Type | Power<br>Supply    | Notes |

|------------------------------------------------|-----------------------------------|----------|--------------------|-------|

| LCLK[2]/LCS[7]                                 | G37                               | 0        | OV <sub>DD</sub>   | —     |

| LSYNC_OUT                                      | F34                               | 0        | OV <sub>DD</sub>   | —     |

| LSYNC_IN                                       | G35                               | I        | OV <sub>DD</sub>   | _     |

|                                                | Programmable Interrupt Controller |          |                    | 1     |

| MCP_OUT                                        | E34                               | 0        | OV <sub>DD</sub>   | 2     |

| IRQ0/MCP_IN                                    | C37                               | I        | OV <sub>DD</sub>   | —     |

| IRQ[1]/M1SRCID[4]/M2SRCID[4]/<br>LSRCID[4]     | F35                               | I/O      | OV <sub>DD</sub>   | —     |

| IRQ[2]/M1DVAL/M2DVAL/LDVAL                     | F36                               | I/O      | OV <sub>DD</sub>   | —     |

| IRQ[3]/CORE_SRESET                             | H34                               | I/O      | OV <sub>DD</sub>   | —     |

| IRQ[4:5]                                       | G33, G32                          | I/O      | OV <sub>DD</sub>   | —     |

| IRQ[6]/LCS[6]/CKSTOP_OUT                       | E35                               | I/O      | OV <sub>DD</sub>   | —     |

| IRQ[7]/LCS[7]/CKSTOP_IN                        | H36                               | I/O      | OV <sub>DD</sub>   | —     |

|                                                | DUART                             |          |                    | 1     |

| UART1_SOUT/M1SRCID[0]/<br>M2SRCID[0]/LSRCID[0] | E32                               | 0        | OV <sub>DD</sub>   | —     |

| UART1_SIN/M1SRCID[1]/<br>M2SRCID[1]/LSRCID[1]  | B34                               | I/O      | OV <sub>DD</sub>   | _     |

| UART1_CTS/M1SRCID[2]/<br>M2SRCID[2]/LSRCID[2]  | C34                               | I/O      | OV <sub>DD</sub>   | —     |

| UART1_RTS/M1SRCID[3]/<br>M2SRCID[3]/LSRCID[3]  | A35                               | 0        | OV <sub>DD</sub>   | _     |

|                                                | I <sup>2</sup> C Interface        |          |                    |       |

| IIC1_SDA                                       | D34                               | I/O      | OV <sub>DD</sub>   | 2     |

| IIC1_SCL                                       | B35                               | I/O      | OV <sub>DD</sub>   | 2     |

| IIC2_SDA                                       | E33                               | I/O      | OV <sub>DD</sub>   | 2     |

| IIC2_SCL                                       | C35                               | I/O      | OV <sub>DD</sub>   | 2     |

|                                                | QUICC Engine Block                |          |                    |       |

| CE_PA[0]                                       | F8                                | I/O      | LV <sub>DD0</sub>  | _     |

| CE_PA[1:2]                                     | AH1, AG5                          | I/O      | OV <sub>DD</sub>   |       |

| CE_PA[3:7]                                     | F6, D4, C3, E5, A3                | I/O      | LV <sub>DD</sub> 0 | _     |

| CE_PA[8]                                       | AG3                               | I/O      | OV <sub>DD</sub>   |       |

| CE_PA[9:12]                                    | F7, B3, E6, B4                    | I/O      | LV <sub>DD</sub> 0 | _     |

| CE_PA[13:14]                                   | AG1, AF6                          | I/O      | OV <sub>DD</sub>   | _     |

| CE_PA[15]                                      | B2                                | I/O      | LV <sub>DD</sub> 0 | _     |

| CE_PA[16]                                      | AF4                               | I/O      | OV <sub>DD</sub>   | _     |

| CE_PA[17:21]                                   | B16, A16, E17, A17, B17           | I/O      | LV <sub>DD</sub> 1 | —     |

#### Table 67. MPC8358E TBGA Pinout Listing (continued)

| Signal                                 | Package Pin Number                                                                                                           | Pin Type | Power<br>Supply    | Notes |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------|--------------------|-------|

| MEMC_MWE                               | AT26                                                                                                                         | 0        | GV <sub>DD</sub>   | _     |

| MEMC_MRAS                              | AT29                                                                                                                         | 0        | GV <sub>DD</sub>   | —     |

| MEMC_MCAS                              | AT24                                                                                                                         | 0        | GV <sub>DD</sub>   | —     |

| MEMC_MCS[0:3]                          | AU27, AT27, AU8, AU7                                                                                                         | 0        | GV <sub>DD</sub>   | —     |

| MEMC_MCKE[0:1]                         | AL32, AU33                                                                                                                   | 0        | GV <sub>DD</sub>   | 3     |

| MEMC_MCK[0:5]                          | AK37, AT37, AN1, AR2, AN25, AK1                                                                                              | 0        | GV <sub>DD</sub>   | —     |

| MEMC_MCK[0:5]                          | AL37, AT36, AP2, AT2, AN24, AL1                                                                                              | 0        | GV <sub>DD</sub>   | —     |

| MDIC[0:1]                              | AH6, AP30                                                                                                                    | I/O      | GV <sub>DD</sub>   | 11    |

|                                        | PCI                                                                                                                          |          |                    | •     |

| PCI_INTA/IRQ_OUT/CE_PF[5]              | A20                                                                                                                          | I/O      | LV <sub>DD</sub> 2 | 2     |

| PCI_RESET_OUT/CE_PF[6]                 | E19                                                                                                                          | I/O      | LV <sub>DD</sub> 2 | _     |

| PCI_AD[31:30]/CE_PG[31:30]             | D20, D21                                                                                                                     | I/O      | LV <sub>DD</sub> 2 | —     |

| PCI_AD[29:25]/CE_PG[29:25]             | A24, B23, C23, E23, A26                                                                                                      | I/O      | OV <sub>DD</sub>   | —     |

| PCI_AD[24]/CE_PG[24]                   | B21                                                                                                                          | I/O      | LV <sub>DD</sub> 2 | —     |

| PCI_AD[23:0]/CE_PG[23:0]               | C24, C25, D25, B25, E24, F24, A27, A28, F27, A30,<br>C30, D30, E29, B31, C31, D31, D32, A32, C33,<br>B33, F30, E31, A34, D33 | I/O      | OV <sub>DD</sub>   | _     |

| PCI_C/BE[3:0]/CE_PF[10:7]              | E22, B26, E28, F28                                                                                                           | I/O      | OV <sub>DD</sub>   | —     |

| PCI_PAR/CE_PF[11]                      | D28                                                                                                                          | I/O      | OV <sub>DD</sub>   | —     |

| PCI_FRAME/CE_PF[12]                    | D26                                                                                                                          | I/O      | OV <sub>DD</sub>   | 5     |

| PCI_TRDY/CE_PF[13]                     | C27                                                                                                                          | I/O      | OV <sub>DD</sub>   | 5     |

| PCI_IRDY/CE_PF[14]                     | C28                                                                                                                          | I/O      | OV <sub>DD</sub>   | 5     |

| PCI_STOP/CE_PF[15]                     | B28                                                                                                                          | I/O      | OV <sub>DD</sub>   | 5     |

| PCI_DEVSEL/CE_PF[16]                   | E26                                                                                                                          | I/O      | OV <sub>DD</sub>   | 5     |

| PCI_IDSEL/CE_PF[17]                    | F22                                                                                                                          | I/O      | OV <sub>DD</sub>   | _     |

| PCI_SERR/CE_PF[18]                     | B29                                                                                                                          | I/O      | OV <sub>DD</sub>   | 5     |

| PCI_PERR/CE_PF[19]                     | A29                                                                                                                          | I/O      | OV <sub>DD</sub>   | 5     |

| PCI_REQ[0]/CE_PF[20]                   | F19                                                                                                                          | I/O      | LV <sub>DD</sub> 2 | _     |

| PCI_REQ[1]/CPCI_HS_ES/<br>CE_PF[21]    | A21                                                                                                                          | I/O      | LV <sub>DD</sub> 2 | —     |

| PCI_REQ[2]/CE_PF[22]                   | C21                                                                                                                          | I/O      | LV <sub>DD</sub> 2 | —     |

| PCI_GNT[0]/CE_PF[23]                   | E20                                                                                                                          | I/O      | LV <sub>DD</sub> 2 | —     |

| PCI_GNT[1]/CPCI1_HS_LED/<br>CE_PF[24]  | B20                                                                                                                          | I/O      | LV <sub>DD</sub> 2 | —     |

| PCI_GNT[2]/CPCI1_HS_ENUM/<br>CE_PF[25] | C20                                                                                                                          | I/O      | LV <sub>DD</sub> 2 | —     |

#### Table 67. MPC8358E TBGA Pinout Listing (continued)

| Signal             | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pin Type                                                        | Power<br>Supply    | Notes |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------|-------|

| PORESET            | L37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                               | OV <sub>DD</sub>   |       |

| HRESET             | L36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I/O                                                             | OV <sub>DD</sub>   | 1     |

| SRESET             | M33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I/O                                                             | OV <sub>DD</sub>   | 2     |

|                    | Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                 |                    |       |

| THERM0             | AP19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I                                                               | GV <sub>DD</sub>   | —     |

| THERM1             | AT31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I                                                               | GV <sub>DD</sub>   | —     |

|                    | Power and Ground Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                 |                    |       |

| AV <sub>DD</sub> 1 | K35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power for<br>LBIU DLL<br>(1.2 V)                                | AV <sub>DD</sub> 1 | _     |

| AV <sub>DD</sub> 2 | K36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power for<br>CE PLL<br>(1.2 V)                                  | AV <sub>DD</sub> 2 | _     |

| AV <sub>DD</sub> 5 | AM29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Power for<br>e300 PLL<br>(1.2 V)                                | AV <sub>DD</sub> 5 | _     |

| AV <sub>DD</sub> 6 | К37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power for<br>system<br>PLL (1.2 V)                              | AV <sub>DD</sub> 6 | _     |

| GND                | <ul> <li>A2, A8, A13, A19, A22, A25, A31, A33, A36, B7,<br/>B12, B24, B27, B30, C4, C6, C9, C15, C26, C32,<br/>D3, D8, D11, D14, D17, D19, D23, D27, E7, E13,<br/>E25, E30, E36, F4, F37, G34, H1, H5, H32, H33, J4,<br/>J32, J37, K1, L3, L5, L33, L34, M1, M34, M35, N37,<br/>P2, P5, P35, P36, R4, T3, U1, U5, U35, V37, W1,<br/>W4, W33, W36, Y34, AA3, AA5, AC3, AC32, AC35,<br/>AD1, AD37, AE4, AE34, AE36, AF33, AG4, AG6,<br/>AG32, AH35, AJ1, AJ4, AJ32, AJ35, AJ37, AK36,<br/>AL3, AL34, AM4, AN6, AN23, AN30, AP8, AP12,<br/>AP14, AP16, AP17, AP20, AP25, AR6, AR8, AR9,<br/>AR19, AR24, AR31, AR35, AR37, AT4, AT10, AT19,<br/>AT20, AT25, AU14, AU22, AU28, AU35</li> </ul> | _                                                               | _                  | -     |

| GV <sub>DD</sub>   | AD4, AE3, AF1, AF5, AF35, AF37, AG2, AG36,<br>AH33, AH34, AK5, AM1, AM35, AM37, AN2, AN10,<br>AN11, AN12, AN14, AN32, AN36, AP5, AP23,<br>AP28, AR1, AR7, AR10, AR12, AR21, AR25, AR27,<br>AR33, AT15, AT22, AT28, AT33, AU2, AU5, AU16,<br>AU31, AU36                                                                                                                                                                                                                                                                                                                                                                                                                                    | Power for<br>DDR<br>DRAM I/O<br>voltage<br>(2.5 or<br>1.8 V)    | GV <sub>DD</sub>   | _     |

| LV <sub>DD</sub> 0 | D5, D6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Power for<br>UCC1<br>Ethernet<br>interface<br>(2.5 V,<br>3.3 V) | LV <sub>DD</sub> 0 | _     |

System PLL Configuration

| RCWL[SPMF] | System PLL<br>Multiplication Factor |

|------------|-------------------------------------|

| 1100       | × 12                                |

| 1101       | × 13                                |

| 1110       | × 14                                |

| 1111       | × 15                                |

| Table 70. S | System PLL Mu | Itiplication | Factors | (continued) |

|-------------|---------------|--------------|---------|-------------|

|-------------|---------------|--------------|---------|-------------|

The RCWL[SVCOD] denotes the system PLL VCO internal frequency as shown in this table.

| ,           |             |

|-------------|-------------|

| RCWL[SVCOD] | VCO Divider |

| 00          | 4           |

| 01          | 8           |

| 10          | 2           |

| 11          | Reserved    |

#### Table 71. System PLL VCO Divider

#### NOTE

The VCO divider must be set properly so that the system VCO frequency is in the range of 600-1400 MHz.

The system VCO frequency is derived from the following equations:

- $csb_clk = \{PCI_SYNC_IN \times (1 + CFG_CLKIN_DIV)\} \times SPMF$

- System VCO Frequency = *csb\_clk* × VCO divider (if both RCWL[DDRCM] and RCWL[LBCM] are cleared) OR

- System VCO frequency =  $2 \times csb_clk \times$  VCO divider (if either RCWL[DDRCM] or RCWL[LBCM] are set).

As described in Section 21, "Clocking," the LBCM, DDRCM, and SPMF parameters in the reset configuration word low and the CFG\_CLKIN\_DIV configuration input signal select the ratio between the primary clock input (CLKIN or PCI\_CLK) and the internal coherent system bus clock (*csb\_clk*). This table shows the expected frequency values for the CSB frequency for select *csb\_clk* to CLKIN/PCI\_SYNC\_IN ratios.

|                                        |      |                                                    | In    | put Clock Fre           | quency (MHz | ) <sup>2</sup> |  |

|----------------------------------------|------|----------------------------------------------------|-------|-------------------------|-------------|----------------|--|

| CFG_CLKIN_DIV<br>at Reset <sup>1</sup> | SPMF | <i>csb_clk</i> :<br>Input Clock Ratio <sup>2</sup> | 16.67 | 25                      | 33.33       | 66.67          |  |

|                                        |      |                                                    |       | csb_clk Frequency (MHz) |             |                |  |

| Low                                    | 0010 | 2:1                                                |       |                         |             | 133            |  |

| Low                                    | 0011 | 3:1                                                |       |                         | 100         | 200            |  |

| Low                                    | 0100 | 4:1                                                |       | 100                     | 133         | 266            |  |

| Low                                    | 0101 | 5:1                                                |       | 125                     | 166         | 333            |  |

#### Table 72. CSB Frequency Options

Core PLL Configuration

# 21.2 Core PLL Configuration

RCWL[COREPLL] selects the ratio between the internal coherent system bus clock (*csb\_clk*) and the e300 core clock (*core\_clk*). This table shows the encodings for RCWL[COREPLL]. COREPLL values not listed in this table should be considered reserved.

| RCWL[COREPLL] |      | core_clk:csb_clk | VCO divider                                                       |                                                                   |

|---------------|------|------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|

| 0–1           | 2–5  | 6                | Ratio                                                             |                                                                   |

| nn            | 0000 | n                | PLL bypassed<br>(PLL off, <i>csb_clk</i><br>clocks core directly) | PLL bypassed<br>(PLL off, <i>csb_clk</i><br>clocks core directly) |

| 00            | 0001 | 0                | 1:1                                                               | ÷2                                                                |

| 01            | 0001 | 0                | 1:1                                                               | ÷4                                                                |

| 10            | 0001 | 0                | 1:1                                                               | ÷8                                                                |

| 11            | 0001 | 0                | 1:1                                                               | ÷8                                                                |

| 00            | 0001 | 1                | 1.5:1                                                             | ÷2                                                                |

| 01            | 0001 | 1                | 1.5:1                                                             | ÷4                                                                |

| 10            | 0001 | 1                | 1.5:1                                                             | ÷8                                                                |

| 11            | 0001 | 1                | 1.5:1                                                             | ÷8                                                                |

| 00            | 0010 | 0                | 2:1                                                               | ÷2                                                                |

| 01            | 0010 | 0                | 2:1                                                               | ÷4                                                                |

| 10            | 0010 | 0                | 2:1                                                               | ÷8                                                                |

| 11            | 0010 | 0                | 2:1                                                               | ÷8                                                                |

| 00            | 0010 | 1                | 2.5:1                                                             | ÷2                                                                |

| 01            | 0010 | 1                | 2.5:1                                                             | ÷4                                                                |

| 10            | 0010 | 1                | 2.5:1                                                             | ÷8                                                                |

| 11            | 0010 | 1                | 2.5:1                                                             | ÷8                                                                |

| 00            | 0011 | 0                | 3:1                                                               | ÷2                                                                |

| 01            | 0011 | 0                | 3:1                                                               | ÷4                                                                |

| 10            | 0011 | 0                | 3:1                                                               | ÷8                                                                |

| 11            | 0011 | 0                | 3:1                                                               | ÷8                                                                |

#### Table 73. e300 Core PLL Configuration

#### NOTE

Core VCO frequency = Core frequency  $\times$  VCO divider. The VCO divider (RCWL[COREPLL[0:1]]) must be set properly so that the core VCO frequency is in the range of 800–1800 MHz. Having a core frequency below the CSB frequency is not a possible option because the core frequency must be equal to or greater than the CSB frequency.

The QUICC Engine block VCO frequency is derived from the following equations:

$ce_clk = (primary clock input \times CEPMF) \div (1 + CEPDF)$

QE VCO Frequency =  $ce_clk \times VCO$  divider  $\times (1 + CEPDF)$

## 21.4 Suggested PLL Configurations