#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                       |

|---------------------------------|--------------------------------------------------------------|

| Core Processor                  | PowerPC e300                                                 |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                               |

| Speed                           | 667MHz                                                       |

| Co-Processors/DSP               | Communications; QUICC Engine, Security; SEC                  |

| RAM Controllers                 | DDR, DDR2                                                    |

| Graphics Acceleration           | Νο                                                           |

| Display & Interface Controllers | -                                                            |

| Ethernet                        | 10/100/1000Mbps (1)                                          |

| SATA                            | -                                                            |

| USB                             | USB 1.x (1)                                                  |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                             |

| Operating Temperature           | 0°C ~ 105°C (TA)                                             |

| Security Features               | Cryptography, Random Number Generator                        |

| Package / Case                  | 740-LBGA                                                     |

| Supplier Device Package         | 740-TBGA (37.5x37.5)                                         |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8360ezualfha |

|                                 |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

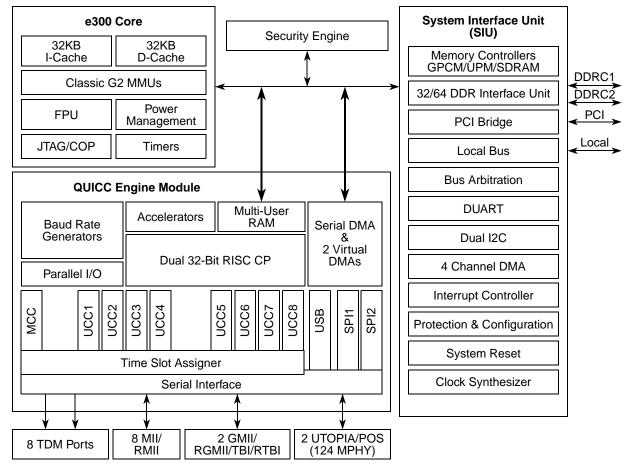

wide range of protocols including ATM, Ethernet, HDLC, and POS. The QUICC Engine module's enhanced interworking eases the transition and reduces investment costs from ATM to IP based systems. The other major features include a dual DDR SDRAM memory controller for the MPC8360E, which allows equipment providers to partition system parameters and data in an extremely efficient way, such as using one 32-bit DDR memory controller for control plane processing and the other for data plane processing. The MPC8358E has a single DDR SDRAM memory controller. The MPC8360E/58E also offers a 32-bit PCI controller, a flexible local bus, and a dedicated security engine.

This figure shows the MPC8360Eblock diagram.

Figure 1. MPC8360E Block Diagram

- Programmable highest priority request

- Four groups of interrupts with programmable priority

- External and internal interrupts directed to communication processor

- Redirects interrupts to external INTA pin when in core disable mode

- Unique vector number for each interrupt source

- Dual industry-standard I<sup>2</sup>C interfaces

- Two-wire interface

- Multiple master support

- Master or slave I<sup>2</sup>C mode support

- On-chip digital filtering rejects spikes on the bus

- System initialization data is optionally loaded from I<sup>2</sup>C-1 EPROM by boot sequencer embedded hardware

- DMA controller

- Four independent virtual channels

- Concurrent execution across multiple channels with programmable bandwidth control

- All channels accessible by local core and remote PCI masters

- Misaligned transfer capability

- Data chaining and direct mode

- Interrupt on completed segment and chain

- DMA external handshake signals: DMA\_DREQ[0:3]/DMA\_DACK[0:3]/DMA\_DONE[0:3]. There is one set for each DMA channel. The pins are multiplexed to the parallel IO pins with other QE functions.

- DUART

- Two 4-wire interfaces (RxD, TxD, RTS, CTS)

- Programming model compatible with the original 16450 UART and the PC16550D

- System timers

- Periodic interrupt timer

- Real-time clock

- Software watchdog timer

- Eight general-purpose timers

- IEEE Std. 1149.1<sup>™</sup>-compliant, JTAG boundary scan

- Integrated PCI bus and SDRAM clock generation

# 2 Electrical Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the MPC8360E/58E. The device is currently targeted to these specifications. Some of these specifications are independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer design specifications.

Power Sequencing

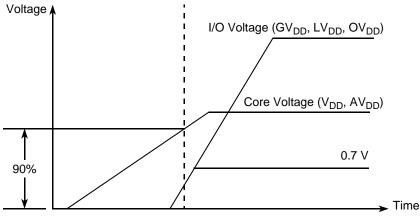

# 2.2.1 Power-Up Sequencing

MPC8360E/58E does not require the core supply voltage ( $V_{DD}$  and  $AV_{DD}$ ) and I/O supply voltages ( $GV_{DD}$ ,  $LV_{DD}$ , and  $OV_{DD}$ ) to be applied in any particular order. During the power ramp up, before the power supplies are stable and if the I/O voltages are supplied before the core voltage, there may be a period of time that all input and output pins are actively be driven and cause contention and excessive current from 3A to 5A. In order to avoid actively driving the I/O pins and to eliminate excessive current draw, apply the core voltage ( $V_{DD}$ ) before the I/O voltage ( $GV_{DD}$ ,  $LV_{DD}$ , and  $OV_{DD}$ ) and assert PORESET before the power supplies fully ramp up. In the case where the core voltage is applied first, the core voltage supply must rise to 90% of its nominal value before the I/O supplies reach 0.7 V, see this figure.

Figure 5. Power Sequencing Example

I/O voltage supplies (GV<sub>DD</sub>, LV<sub>DD</sub>, and OV<sub>DD</sub>) do not have any ordering requirements with respect to one another.

## 2.2.2 Power-Down Sequencing

The MPC8360E/58E does not require the core supply voltage and I/O supply voltages to be powered down in any particular order.

# **3 Power Characteristics**

The estimated typical power dissipation values are shown in these tables.

| Table 4. MPC8360E TBG/ | Core Power Dissipation <sup>1</sup> |

|------------------------|-------------------------------------|

|------------------------|-------------------------------------|

| Core<br>Frequency (MHz) | CSB<br>Frequency (MHz) | QUICC Engine<br>Frequency (MHz) | Typical | Maximum | Unit | Notes      |

|-------------------------|------------------------|---------------------------------|---------|---------|------|------------|

| 266                     | 266                    | 500                             | 5.0     | 5.6     | W    | 2, 3, 5    |

| 400                     | 266                    | 400                             | 4.5     | 5.0     | W    | 2, 3, 4    |

| 533                     | 266                    | 400                             | 4.8     | 5.3     | W    | 2, 3, 4    |

| 667                     | 333                    | 400                             | 5.8     | 6.3     | W    | 3, 6, 7, 8 |

| 500                     | 333                    | 500                             | 5.9     | 6.4     | W    | 3, 6, 7, 8 |

### **Power Sequencing**

This table shows the estimated typical I/O power dissipation for the device.

| Interface                                | Parameter                   | GV <sub>DD</sub><br>(1.8 V) | GV <sub>DD</sub><br>(2.5 V) | OV <sub>DD</sub><br>(3.3 V) | LV <sub>DD</sub><br>(3.3 V) | LV <sub>DD</sub><br>(2.5 V) | Unit | Comments    |

|------------------------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|------|-------------|

| DDR I/O                                  | 200 MHz, 1 $\times$ 32 bits | 0.3                         | 0.46                        |                             | _                           | _                           | W    | —           |

| 65% utilization<br>R <sub>s</sub> = 20 Ω | 200 MHz, 1 $\times$ 64 bits | 0.4                         | 0.58                        | _                           | _                           | _                           | W    | —           |

| $R_t = 50 \Omega$<br>2 pairs of clocks   | 200 MHz, $2 \times 32$ bits | 0.6                         | 0.92                        | _                           | _                           | _                           | W    | —           |

|                                          | 266 MHz, 1 $\times$ 32 bits | 0.35                        | 0.56                        | _                           | _                           | _                           | W    | —           |

|                                          | 266 MHz, 1 $\times$ 64 bits | 0.46                        | 0.7                         | _                           | _                           | _                           | W    | —           |

|                                          | 266 MHz, $2 \times 32$ bits | 0.7                         | 1.11                        | _                           | _                           | _                           | W    | —           |

|                                          | 333 MHz, 1 $\times$ 32 bits | 0.4                         | 0.65                        | _                           | _                           | _                           | W    | —           |

|                                          | 333 MHz, 1 $\times$ 64 bits | 0.53                        | 0.82                        | _                           | _                           | _                           | W    | —           |

|                                          | 333 MHz, $2 \times 32$ bits | 0.81                        | 1.3                         | _                           | _                           | _                           | W    | —           |

| Local Bus I/O                            | 133 MHz, 32 bits            | _                           | _                           | 0.22                        | _                           | _                           | W    | —           |

| Load = 25 pf<br>3 pairs of clocks        | 83 MHz, 32 bits             | _                           | _                           | 0.14                        | _                           | _                           | W    | —           |

|                                          | 66 MHz, 32 bits             | —                           | _                           | 0.12                        | _                           | _                           | W    | —           |

|                                          | 50 MHz, 32 bits             | _                           | _                           | 0.09                        | _                           | _                           | W    | —           |

| PCI I/O                                  | 33 MHz, 32 bits             | _                           | _                           | 0.05                        | _                           | _                           | W    | —           |

| Load = 30 pF                             | 66 MHz, 32 bits             | _                           |                             | 0.07                        | _                           | _                           | W    | —           |

| 10/100/1000                              | MII or RMII                 | —                           | _                           |                             | 0.01                        | —                           | W    | Multiply by |

| Ethernet I/O<br>Load = 20 pF             | GMII or TBI                 | _                           | <u> </u>                    |                             | W                           | number of interfaces used.  |      |             |

|                                          | RGMII or RTBI               | _                           |                             |                             |                             | 0.04                        | W    | 1           |

| Other I/O                                | —                           | _                           |                             | 0.1                         |                             |                             | W    | —           |

Table 6. Estimated Typical I/O Power Dissipation

# 4 Clock Input Timing

This section provides the clock input DC and AC electrical characteristics for the MPC8360E/58E.

## NOTE

The rise/fall time on QUICC Engine block input pins should not exceed 5 ns. This should be enforced especially on clock signals. Rise time refers to signal transitions from 10% to 90% of  $V_{DD}$ ; fall time refers to transitions from 90% to 10% of  $V_{DD}$ .

#### **DDR and DDR2 SDRAM AC Electrical Characteristics**

This table provides the input AC timing specifications for the DDR SDRAM interface when  $GV_{DD}(typ) = 2.5 \text{ V}$ .

### Table 19. DDR SDRAM Input AC Timing Specifications

At recommended operating conditions with  $GV_{DD}$  of 2.5 V ± 5%.

| Parameter             | Symbol          | Min                      | Мах                      | Unit | Notes |

|-----------------------|-----------------|--------------------------|--------------------------|------|-------|

| AC input low voltage  | V <sub>IL</sub> | _                        | MV <sub>REF</sub> – 0.31 | V    | —     |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.31 | _                        | V    | —     |

### Table 20. DDR and DDR2 SDRAM Input AC Timing Specifications Mode

At recommended operating conditions with  $GV_{DD}$  of (1.8 or 2.5 V) ± 5%.

| Parameter                                                          | Symbol | Min                    | Мах                 | Unit | Notes |

|--------------------------------------------------------------------|--------|------------------------|---------------------|------|-------|

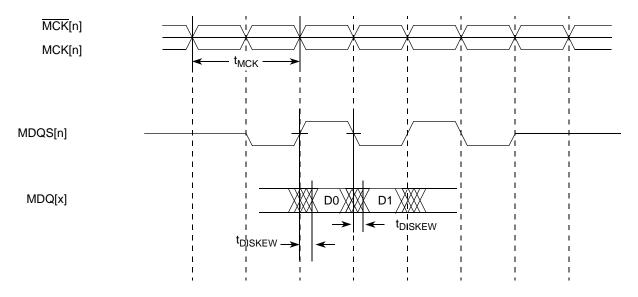

| MDQS—MDQ/MECC input skew per byte<br>333 MHz<br>266 MHz<br>200 MHz |        | -750<br>-1125<br>-1250 | 750<br>1125<br>1250 | ps   | 1, 2  |

### Notes:

1. AC timing values are based on the DDR data rate, which is twice the DDR memory bus frequency.

Maximum possible skew between a data strobe (MDQS[n]) and any corresponding bit of data (MDQ[8n + {0...7}] if 0 ≤n ≤7) or ECC (MECC[{0...7}] if n = 8).

This figure shows the input timing diagram for the DDR controller.

Figure 6. DDR Input Timing Diagram

DDR and DDR2 SDRAM AC Electrical Characteristics

# 6.2.2 DDR and DDR2 SDRAM Output AC Timing Specifications

Table 21 and Table 22 provide the output AC timing specifications and measurement conditions for the DDR and DDR2 SDRAM interface.

# Table 21. DDR and DDR2 SDRAM Output AC Timing Specifications for Source Synchronous Mode

At recommended operating conditions with  $\text{GV}_{\text{DD}}$  of (1.8 V or 2.5 V) ± 5%.

| Parameter <sup>8</sup>                                                                         | Symbol <sup>1</sup> | Min                         | Мах                               | Unit | Notes |

|------------------------------------------------------------------------------------------------|---------------------|-----------------------------|-----------------------------------|------|-------|

| MCK[n] cycle time, (MCK[n]/MCK[n] crossing)                                                    | t <sub>MCK</sub>    | 6                           | 10                                | ns   | 2     |

| Skew between any MCK to ADDR/CMD<br>333 MHz<br>266 MHz<br>200 MHz                              |                     | -1.0<br>-1.1<br>-1.2        | 0.2<br>0.3<br>0.4                 | ns   | 3     |

| ADDR/CMD output setup with respect to MCK<br>333 MHz<br>266 MHz<br>200 MHz                     |                     | 2.1<br>2.8<br>3.5           | _                                 | ns   | 4     |

| ADDR/CMD output hold with respect to MCK<br>333 MHz<br>266 MHz—DDR1<br>266 MHz—DDR2<br>200 MHz |                     | 2.0<br>2.7<br>2.8<br>3.5    | _                                 | ns   | 4     |

| MCS(n) output setup with respect to MCK<br>333 MHz<br>266 MHz<br>200 MHz                       |                     | 2.1<br>2.8<br>3.5           | _                                 | ns   | 4     |

| MCS(n) output hold with respect to MCK<br>333 MHz<br>266 MHz<br>200 MHz                        |                     | 2.0<br>2.7<br>3.5           | _                                 | ns   | 4     |

| MCK to MDQS                                                                                    | t <sub>DDKHMH</sub> | -0.8                        | 0.7                               | ns   | 5, 9  |

| MDQ/MECC/MDM output setup with respect to MDQS<br>333 MHz<br>266 MHz<br>200 MHz                | 2211220             | 0.7<br>1.0<br>1.2           | _                                 | ns   | 6     |

| MDQ/MECC/MDM output hold with respect to MDQS<br>333 MHz<br>266 MHz<br>200 MHz                 | DDICEDX             | 0.7<br>1.0<br>1.2           | _                                 | ns   | 6     |

| MDQS preamble start                                                                            | t <sub>DDKHMP</sub> | $-0.5 \times t_{MCK} - 0.6$ | $-0.5\timest_{\text{MCK}}^{}+0.6$ | ns   | 7     |

# Table 21. DDR and DDR2 SDRAM Output AC Timing Specifications for Source Synchronous Mode (continued)

At recommended operating conditions with  $GV_{DD}$  of (1.8 V or 2.5 V) ± 5%.

| Parameter <sup>8</sup> | Symbol <sup>1</sup> | Min  | Мах | Unit | Notes |

|------------------------|---------------------|------|-----|------|-------|

| MDQS epilogue end      | t <sub>DDKHME</sub> | -0.6 | 0.9 | ns   | 7     |

#### Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are setup (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

</sub>

- 2. All MCK/ $\overline{MCK}$  referenced measurements are made from the crossing of the two signals ±0.1 V.

- In the source synchronous mode, MCK/MCK can be shifted in ¼ applied cycle increments through the clock control register. For the skew measurements referenced for t<sub>AOSKEW</sub> it is assumed that the clock adjustment is set to align the address/command valid with the rising edge of MCK.

- ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ/MECC/MDM/MDQS. For the ADDR/CMD setup and hold specifications, it is assumed that the clock control register is set to adjust the memory clocks by ½ applied cycle.

- 5. Note that t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK(n) clock (KH) until the MDQS signal is valid (MH). t<sub>DDKHMH</sub> can be modified through control of the DQSS override bits in the TIMING\_CFG\_2 register. In source synchronous mode, this is typically set to the same delay as the clock adjust in the CLK\_CNTL register. The timing parameters listed in the table assume that these two parameters have been set to the same adjustment value. Refer MPC8360E PowerQUICC II Pro Integrated Communications Processor Reference Manual for a description and understanding of the timing modifications enabled by use of these bits.

- Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe should be centered inside of the data eye at the pins of the device.

- All outputs are referenced to the rising edge of MCK(n) at the pins of the device. Note that t<sub>DDKHMP</sub> follows the symbol conventions described in note 1.

- 8. AC timing values are based on the DDR data rate, which is twice the DDR memory bus frequency.

- In rev. 2.0 silicon, t<sub>DDKHMH</sub> maximum meets the specification of 0.6 ns. In rev. 2.0 silicon, due to errata, t<sub>DDKHMH</sub> minimum is –0.9 ns. Refer to Errata DDR18 in *Chip Errata for the MPC8360E, Rev. 1*.

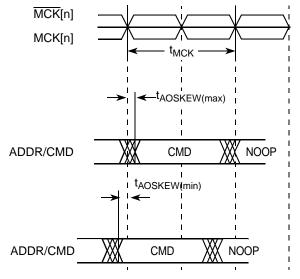

This figure shows the DDR SDRAM output timing for address skew with respect to any MCK.

GMII, MII, RMII, TBI, RGMII, and RTBI AC Timing Specifications

## 8.2.1.2 GMII Receive AC Timing Specifications

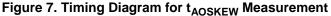

This table provides the GMII receive AC timing specifications.

## Table 28. GMII Receive AC Timing Specifications

At recommended operating conditions with LV\_{DD}/OV\_{DD} of 3.3 V  $\pm$  10%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit | Notes |

|---------------------------------------------|-------------------------------------|-----|-----|-----|------|-------|

| RX_CLK clock period                         | t <sub>GRX</sub>                    | _   | 8.0 | _   | ns   | —     |

| RX_CLK duty cycle                           | t <sub>GRXH</sub> /t <sub>GRX</sub> | 40  | —   | 60  | %    | _     |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>GRDVKH</sub>                 | 2.0 | —   | _   | ns   | _     |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>GRDXKH</sub>                 | 0.2 | —   | _   | ns   | 2     |

| RX_CLK clock rise time, (20% to 80%)        | t <sub>GRXR</sub>                   | _   | —   | 1.0 | ns   | _     |

| RX_CLK clock fall time, (80% to 20%)        | t <sub>GRXF</sub>                   | _   |     | 1.0 | ns   | _     |

### Notes:

- 1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>GRDVKH</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>RX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>RX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>GRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GRX</sub> represents the GMII (G) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- In rev. 2.0 silicon, due to errata, t<sub>GRDXKH</sub> minimum is 0.5 which is not compliant with the standard. Refer to Errata QE\_ENET18 in Chip Errata for the MPC8360E, Rev. 1.

This figure shows the GMII receive AC timing diagram.

Figure 11. GMII Receive AC Timing Diagram

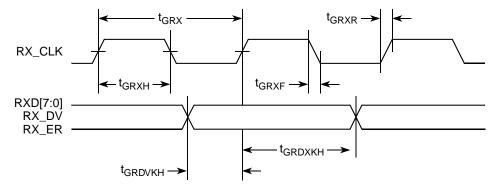

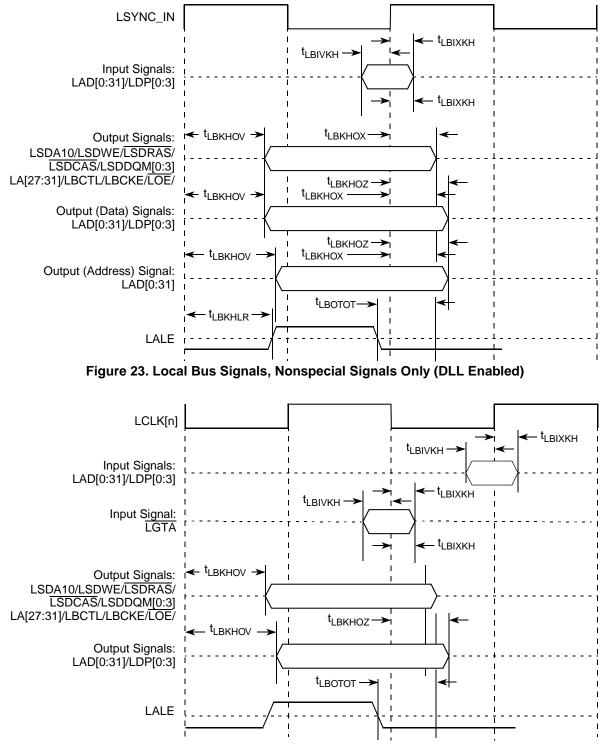

These figures show the local bus signals.

Figure 24. Local Bus Signals, Nonspecial Signals Only (DLL Bypass Mode)

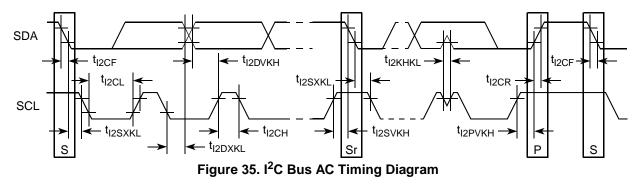

This figure provides the AC test load for the  $I^2C$ .

Figure 34. I<sup>2</sup>C AC Test Load

This figure shows the AC timing diagram for the  $I^2C$  bus.

# 12 PCI

This section describes the DC and AC electrical specifications for the PCI bus of the MPC8360E/58E.

# 12.1 PCI DC Electrical Characteristics

This table provides the DC electrical characteristics for the PCI interface of the device.

## **Table 46. PCI DC Electrical Characteristics**

| Parameter                 | Symbol          | Test Condition                                      | Min                 | Мах                    | Unit |

|---------------------------|-----------------|-----------------------------------------------------|---------------------|------------------------|------|

| High-level input voltage  | V <sub>IH</sub> | $V_{OUT} \ge V_{OH}$ (min) or                       | $0.5 	imes OV_{DD}$ | OV <sub>DD</sub> + 0.5 | V    |

| Low-level input voltage   | V <sub>IL</sub> | V <sub>OUT</sub> ⊴V <sub>OL</sub> (max)             | -0.5                | $0.3 	imes OV_{DD}$    | V    |

| High-level output voltage | V <sub>OH</sub> | I <sub>OH</sub> = -500 μA                           | $0.9 	imes OV_{DD}$ | —                      | V    |

| Low-level output voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 1500 μA                           | —                   | $0.1 	imes OV_{DD}$    | V    |

| Input current             | I <sub>IN</sub> | 0 V ≤V <sub>IN</sub> <sup>1</sup> ≤OV <sub>DD</sub> | —                   | ±10                    | μA   |

# 12.2 PCI AC Electrical Specifications

This section describes the general AC timing parameters of the PCI bus of the device. Note that the PCI\_CLK or PCI\_SYNC\_IN signal is used as the PCI input clock depending on whether the device is configured as a host or agent device. This table provides the PCI AC timing specifications at 66 MHz.

| Parameter              | Symbol <sup>1</sup> | Min | Мах | Unit | Notes |

|------------------------|---------------------|-----|-----|------|-------|

| Clock to output valid  | t <sub>PCKHOV</sub> | —   | 6.0 | ns   | 2, 5  |

| Output hold from clock | t <sub>PCKHOX</sub> | 1   | _   | ns   | 2     |

## Table 47. PCI AC Timing Specifications at 66 MHz

## Table 60. UTOPIA AC Timing Specifications<sup>1</sup> (continued)

| Characteristic                               | Symbol <sup>2</sup> | Min | Мах | Unit | Notes |

|----------------------------------------------|---------------------|-----|-----|------|-------|

| UTOPIA inputs—Internal clock input hold time | t <sub>UIIXKH</sub> | 2.4 | —   | ns   | —     |

| UTOPIA inputs—External clock input hold time | t <sub>UEIXKH</sub> | 1   | —   | ns   | 3     |

Notes:

- 1. Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are measured at the pin.

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>UIKHOX</sub> symbolizes the UTOPIA outputs internal timing (UI) for the time t<sub>UTOPIA</sub> memory clock reference (K) goes from the high state (H) until outputs (O) are invalid (X).

</sub>

- 3. In rev. 2.0 silicon, due to errata, t<sub>UEIVKH</sub> minimum is 4.3 ns and t<sub>UEIXKH</sub> minimum is 1.4 ns under specific conditions. Refer to Errata QE\_UPC3 in *Chip Errata for the MPC8360E, Rev. 1*.

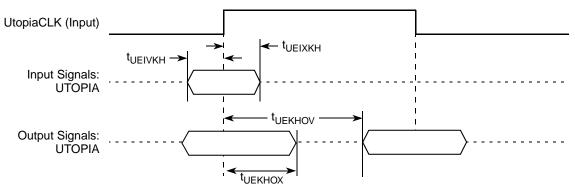

This figure provides the AC test load for the UTOPIA.

Figure 46. UTOPIA AC Test Load

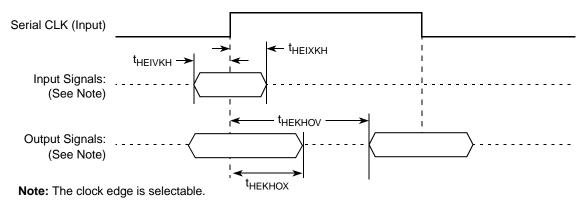

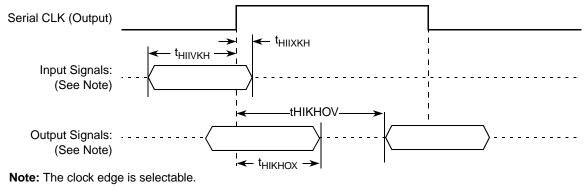

These figures represent the AC timing from Table 56. Note that although the specifications generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge is the active edge.

This figure shows the UTOPIA timing with external clock.

Figure 47. UTOPIA AC Timing (External Clock) Diagram

# 18.3 AC Test Load

These figures represent the AC timing from Table 62 and Table 63. Note that although the specifications generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge is the active edge.

This figure shows the timing with external clock.

Figure 50. AC Timing (External Clock) Diagram

This figure shows the timing with internal clock.

Figure 51. AC Timing (Internal Clock) Diagram

## Table 66. MPC8360E TBGA Pinout Listing (continued)

| Signal                                 | Package Pin Number                                                                                                                                                         | Pin Type | Power<br>Supply    | Notes |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------|-------|

| PCI_DEVSEL/CE_PF[16]                   | E26                                                                                                                                                                        | I/O      | OV <sub>DD</sub>   | 5     |

| PCI_IDSEL/CE_PF[17]                    | F22                                                                                                                                                                        | I/O      | OV <sub>DD</sub>   | —     |

| PCI_SERR/CE_PF[18]                     | B29                                                                                                                                                                        | I/O      | OV <sub>DD</sub>   | 5     |

| PCI_PERR/CE_PF[19]                     | A29                                                                                                                                                                        | I/O      | OV <sub>DD</sub>   | 5     |

| PCI_REQ[0]/CE_PF[20]                   | F19                                                                                                                                                                        | I/O      | LV <sub>DD</sub> 2 | —     |

| PCI_REQ[1]/CPCI_HS_ES/<br>CE_PF[21]    | A21                                                                                                                                                                        | I/O      | LV <sub>DD</sub> 2 | —     |

| PCI_REQ[2]/CE_PF[22]                   | C21                                                                                                                                                                        | I/O      | LV <sub>DD</sub> 2 | —     |

| PCI_GNT[0]/CE_PF[23]                   | E20                                                                                                                                                                        | I/O      | LV <sub>DD</sub> 2 | —     |

| PCI_GNT[1]/CPCI1_HS_LED/<br>CE_PF[24]  | B20                                                                                                                                                                        | I/O      | LV <sub>DD</sub> 2 |       |

| PCI_GNT[2]/CPCI1_HS_ENUM/<br>CE_PF[25] | C20                                                                                                                                                                        | I/O      | LV <sub>DD</sub> 2 | _     |

| PCI_MODE                               | D36                                                                                                                                                                        | I        | OV <sub>DD</sub>   | —     |

| M66EN/CE_PF[4]                         | B37                                                                                                                                                                        | I/O      | OV <sub>DD</sub>   | —     |

|                                        | Local Bus Controller Interface                                                                                                                                             |          |                    |       |

| LAD[0:31]                              | N32, N33, N35, N36, P37, P32, P34, R36, R35,<br>R34, R33, T37, T35, T34, T33, U37, T32, U36, U34,<br>V36, V35, W37, W35, V33, V32, W34, Y36, W32,<br>AA37, Y33, AA35, AA34 | I/O      | OV <sub>DD</sub>   | —     |

| LDP[0]/CKSTOP_OUT                      | AB37                                                                                                                                                                       | I/O      | OV <sub>DD</sub>   | —     |

| LDP[1]/CKSTOP_IN                       | AB36                                                                                                                                                                       | I/O      | OV <sub>DD</sub>   | - I   |

| LDP[2]/LCS[6]                          | AB35                                                                                                                                                                       | I/O      | OV <sub>DD</sub>   | —     |

| LDP[3]/LCS[7]                          | AA33                                                                                                                                                                       | I/O      | OV <sub>DD</sub>   | —     |

| LA[27:31]                              | AC37, AA32, AC36, AC34, AD36                                                                                                                                               | 0        | OV <sub>DD</sub>   | —     |

| LCS[0:5]                               | AD33, AG37, AF34, AE33, AD32, AH37                                                                                                                                         | 0        | OV <sub>DD</sub>   | —     |

| LWE[0:3]/LSDDQM[0:3]/LBS[0:3]          | AG35, AG34, AH36, AE32                                                                                                                                                     | 0        | OV <sub>DD</sub>   | —     |

| LBCTL                                  | AD35                                                                                                                                                                       | 0        | OV <sub>DD</sub>   | —     |

| LALE                                   | M37                                                                                                                                                                        | 0        | OV <sub>DD</sub>   | —     |

| LGPL0/LSDA10/cfg_reset_source0         | AB32                                                                                                                                                                       | I/O      | OV <sub>DD</sub>   | —     |

| LGPL1/LSDWE/cfg_reset_source1          | AE37                                                                                                                                                                       | I/O      | OV <sub>DD</sub>   | —     |

| LGPL2/LSDRAS/LOE                       | AC33                                                                                                                                                                       | 0        | OV <sub>DD</sub>   | —     |

| LGPL3/LSDCAS/cfg_reset_source2         | AD34                                                                                                                                                                       | I/O      | OV <sub>DD</sub>   | —     |

| LGPL4/LGTA/LUPWAIT/LPBSE               | AE35                                                                                                                                                                       | I/O      | OV <sub>DD</sub>   | -     |

| LGPL5/cfg_clkin_div                    | AF36                                                                                                                                                                       | I/O      | OV <sub>DD</sub>   | —     |

| LCKE                                   | G36                                                                                                                                                                        | 0        | OV <sub>DD</sub>   | —     |

| LCLK[0]                                | J33                                                                                                                                                                        | 0        | OV <sub>DD</sub>   | —     |

| LCLK[1]/LCS[6]                         | J34                                                                                                                                                                        | 0        | OV <sub>DD</sub>   | —     |

**Pinout Listings**

## Table 66. MPC8360E TBGA Pinout Listing (continued)

| Signal             | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pin Type                                                     | Power<br>Supply     | Notes |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------|-------|

|                    | РМС                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                            |                     | 1     |

| QUIESCE            | B36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                            | OV <sub>DD</sub>    | _     |

|                    | System Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                              |                     |       |

| PORESET            | L37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                            | $OV_{DD}$           | _     |

| HRESET             | L36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I/O                                                          | $OV_{DD}$           | 1     |

| SRESET             | M33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I/O                                                          | $OV_DD$             | 2     |

|                    | Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                              |                     |       |

| THERM0             | AP19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I                                                            | GV <sub>DD</sub>    | _     |

| THERM1             | AT31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I                                                            | ${\rm GV}_{\rm DD}$ | —     |

|                    | Power and Ground Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                              |                     |       |

| AV <sub>DD</sub> 1 | K35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power for<br>LBIU DLL<br>(1.2 V)                             | AV <sub>DD</sub> 1  | _     |

| AV <sub>DD</sub> 2 | K36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power for<br>CE PLL<br>(1.2 V)                               | AV <sub>DD</sub> 2  | -     |

| AV <sub>DD</sub> 5 | AM29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Power for<br>e300 PLL<br>(1.2 V)                             | AV <sub>DD</sub> 5  | —     |

| AV <sub>DD</sub> 6 | K37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power for<br>system<br>PLL (1.2 V)                           | AV <sub>DD</sub> 6  | —     |

| GND                | <ul> <li>A2, A8, A13, A19, A22, A25, A31, A33, A36, B7,<br/>B12, B24, B27, B30, C4, C6, C9, C15, C26, C32,<br/>D3, D8, D11, D14, D17, D19, D23, D27, E7, E13,<br/>E25, E30, E36, F4, F37, G34, H1, H5, H32, H33, J4,<br/>J32, J37, K1, L3, L5, L33, L34, M1, M34, M35, N37,<br/>P2, P5, P35, P36, R4, T3, U1, U5, U35, V37, W1,<br/>W4, W33, W36, Y34, AA3, AA5, AC3, AC32, AC35,<br/>AD1, AD37, AE4, AE34, AE36, AF33, AG4, AG6,<br/>AG32, AH35, AJ1, AJ4, AJ32, AJ35, AJ37, AK36,<br/>AL3, AL34, AM4, AN6, AN23, AN30, AP8, AP12,<br/>AP14, AP16, AP17, AP20, AP25, AR6, AR8, AR9,<br/>AR19, AR24, AR31, AR35, AR37, AT4, AT10, AT19,<br/>AT20, AT25, AU14, AU22, AU28, AU35</li> </ul> | _                                                            | _                   | _     |

| GV <sub>DD</sub>   | AD4, AE3, AF1, AF5, AF35, AF37, AG2, AG36,<br>AH33, AH34, AK5, AM1, AM35, AM37, AN2, AN10,<br>AN11, AN12, AN14, AN32, AN36, AP5, AP23,<br>AP28, AR1, AR7, AR10, AR12, AR21, AR25, AR27,<br>AR33, AT15, AT22, AT28, AT33, AU2, AU5, AU16,<br>AU31, AU36                                                                                                                                                                                                                                                                                                                                                                                                                                    | Power for<br>DDR<br>DRAM I/O<br>voltage<br>(2.5 or<br>1.8 V) | GV <sub>DD</sub>    | _     |

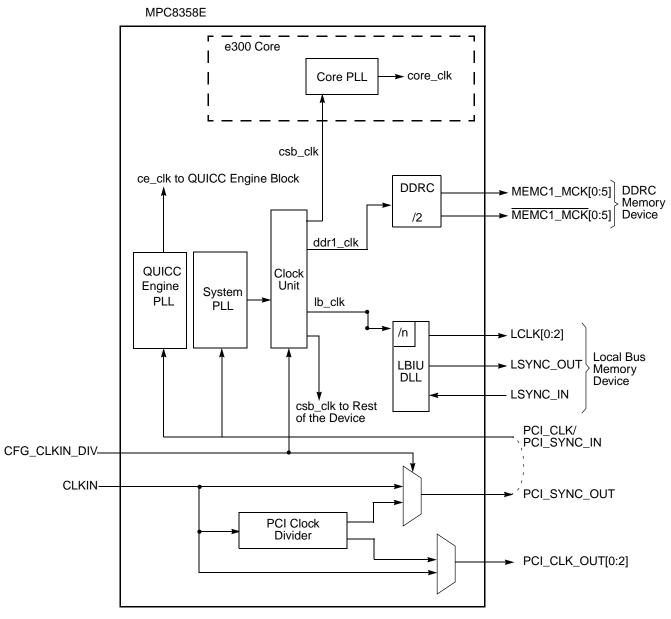

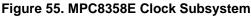

This figure shows the internal distribution of clocks within the MPC8358E.

The primary clock source for the device can be one of two inputs, CLKIN or PCI\_CLK, depending on whether the device is configured in PCI host or PCI agent mode. Note that in PCI host mode, the primary clock input also depends on whether PCI clock outputs are selected with RCWH[PCICKDRV]. When the device is configured as a PCI host device (RCWH[PCIHOST] = 1) and PCI clock output is selected (RCWH[PCICKDRV] = 1), CLKIN is its primary input clock. CLKIN feeds the PCI clock divider ( $\div$ 2) and the multiplexors for PCI\_SYNC\_OUT and PCI\_CLK\_OUT. The CFG\_CLKIN\_DIV configuration input selects whether CLKIN or CLKIN/2 is driven out on the PCI\_SYNC\_OUT signal. The OCCR[PCIOEN*n*] parameters enable the PCI\_CLK\_OUT*n*, respectively.

PCI\_SYNC\_OUT is connected externally to PCI\_SYNC\_IN to allow the internal clock subsystem to synchronize to the system PCI clocks. PCI\_SYNC\_OUT must be connected properly to PCI\_SYNC\_IN, with equal delay to all PCI agent devices in the system, to allow the device to function. When the device is configured as a PCI agent device, PCI\_CLK is the primary input

#### Pinout Listings

clock. When the device is configured as a PCI agent device the CLKIN and the CFG\_CLKIN\_DIV signals should be tied to GND.

When the device is configured as a PCI host device (RCWH[PCIHOST] = 1) and PCI clock output is disabled (RCWH[PCICKDRV] = 0), clock distribution and balancing done externally on the board. Therefore, PCI\_SYNC\_IN is the primary input clock.

As shown in Figure 54 and Figure 55, the primary clock input (frequency) is multiplied by the QUICC Engine block phase-locked loop (PLL), the system PLL, and the clock unit to create the QUICC Engine clock ( $ce_clk$ ), the coherent system bus clock ( $csb_clk$ ), the internal DDRC1 controller clock ( $ddr1_clk$ ), and the internal clock for the local bus interface unit and DDR2 memory controller ( $lb_clk$ ).

The *csb\_clk* frequency is derived from a complex set of factors that can be simplified into the following equation:

$$csb\_clk = \{PCI\_SYNC\_IN \times (1 + CFG\_CLKIN\_DIV)\} \times SPMF$$

In PCI host mode, PCI\_SYNC\_IN  $\times$  (1 + CFG\_CLKIN\_DIV) is the CLKIN frequency; in PCI agent mode, CFG\_CLKIN\_DIV must be pulled down (low), so PCI\_SYNC\_IN  $\times$  (1 + CFG\_CLKIN\_DIV) is the PCI\_CLK frequency.

The *csb\_clk* serves as the clock input to the e300 core. A second PLL inside the e300 core multiplies up the *csb\_clk* frequency to create the internal clock for the e300 core (*core\_clk*). The system and core PLL multipliers are selected by the SPMF and COREPLL fields in the reset configuration word low (RCWL) which is loaded at power-on reset or by one of the hard-coded reset options. See Chapter 4, "Reset, Clocking, and Initialization," in the *MPC8360E PowerQUICC II Pro Integrated Communications Processor Reference Manual* for more information on the clock subsystem.

The *ce\_clk* frequency is determined by the QUICC Engine PLL multiplication factor (RCWL[CEPMF) and the QUICC Engine PLL division factor (RCWL[CEPDF]) according to the following equation:

$ce_clk = (primary clock input \times CEPMF) \div (1 + CEPDF)$

The internal *ddr1\_clk* frequency is determined by the following equation:

$ddr1_clk = csb_clk \times (1 + RCWL[DDR1CM])$

Note that the lb\_clk clock frequency (for DDRC2) is determined by RCWL[LBCM]. The *internal ddr1\_clk* frequency is not the external memory bus frequency; *ddr1\_clk* passes through the DDRC1 clock divider ( $\div$ 2) to create the differential DDRC1 memory bus clock outputs (MEMC1\_MCK and MEMC1\_MCK). However, the data rate is the same frequency as *ddr1\_clk*.

The internal *lb\_clk* frequency is determined by the following equation:

$lb\_clk = csb\_clk \times (1 + \text{RCWL[LBCM]})$

Note that *lb\_clk* is not the external local bus or DDRC2 frequency; *lb\_clk* passes through the a LB clock divider to create the external local bus clock outputs (LSYNC\_OUT and LCLK[0:2]). The LB clock divider ratio is controlled by LCRR[CLKDIV].

Additionally, some of the internal units may be required to be shut off or operate at lower frequency than the *csb\_clk* frequency. Those units have a default clock ratio that can be configured by a memory mapped register after the device comes out of reset. This table specifies which units have a configurable clock frequency.

| Unit                | Unit Default<br>Frequency |                                                     |

|---------------------|---------------------------|-----------------------------------------------------|

| Security core       | csb_clk/3                 | Off, csb_clk <sup>1</sup> , csb_clk/2,<br>csb_clk/3 |

| PCI and DMA complex | csb_clk                   | Off, <i>csb_clk</i>                                 |

| Table 68 | Configurable | <b>Clock Units</b> |

|----------|--------------|--------------------|

|----------|--------------|--------------------|

<sup>1</sup> With limitation, only for slow csb\_clk rates, up to 166 MHz.

This table provides the operating frequencies for the TBGA package under recommended operating conditions (see Table 2). All frequency combinations shown in the table below may not be available. Maximum operating frequencies depend on the part

QUICC Engine Block PLL Configuration

| RCWL[CEPMF] | RCWL[CEPDF] | QUICC Engine PLL<br>Multiplication Factor = RCWL[CEPMF]/<br>(1 + RCWL[CEPDF]) |

|-------------|-------------|-------------------------------------------------------------------------------|

| 11101       | 0           | × 29                                                                          |

| 11110       | 0           | × 30                                                                          |

| 11111       | 0           | × 31                                                                          |

| 00011       | 1           | × 1.5                                                                         |

| 00101       | 1           | × 2.5                                                                         |

| 00111       | 1           | × 3.5                                                                         |

| 01001       | 1           | × 4.5                                                                         |

| 01011       | 1           | × 5.5                                                                         |

| 01101       | 1           | × 6.5                                                                         |

| 01111       | 1           | × 7.5                                                                         |

| 10001       | 1           | × 8.5                                                                         |

| 10011       | 1           | × 9.5                                                                         |

| 10101       | 1           | × 10.5                                                                        |

| 10111       | 1           | × 11.5                                                                        |

| 11001       | 1           | × 12.5                                                                        |

| 11011       | 1           | × 13.5                                                                        |

| 11101       | 1           | × 14.5                                                                        |

Table 74. QUICC Engine Block PLL Multiplication Factors (continued)

Note:

1. Reserved modes are not listed.

The RCWL[CEVCOD] denotes the QUICC Engine Block PLL VCO internal frequency as shown in this table.

Table 75. QUICC Engine Block PLL VCO Divider

| RCWL[CEVCOD] | VCO Divider |

|--------------|-------------|

| 00           | 4           |

| 01           | 8           |

| 10           | 2           |

| 11           | Reserved    |

## NOTE

The VCO divider (RCWL[CEVCOD]) must be set properly so that the QUICC Engine block VCO frequency is in the range of 600–1400 MHz. The QUICC Engine block frequency is not restricted by the CSB and core frequencies. The CSB, core, and QUICC Engine block frequencies should be selected according to the performance requirements.

Suggested PLL Configurations

| Conf<br>No. <sup>1</sup> | SPMF                             | CORE<br>PLL | CEPMF | CEPDF | Input<br>Clock Freq<br>(MHz) | CSB Freq<br>(MHz) | Core Freq<br>(MHz) | QUICC<br>Engine<br>Freq (MHz) | 400<br>(MHz) | 533<br>(MHz) | 667<br>(MHz) |

|--------------------------|----------------------------------|-------------|-------|-------|------------------------------|-------------------|--------------------|-------------------------------|--------------|--------------|--------------|

| c5                       | æ                                | æ           | 10000 | 0     | 33                           | —                 | —                  | 533                           | _            | 8            | 8            |

| c6                       | æ                                | æ           | 10001 | 0     | 33                           | —                 | —                  | 566                           | _            | —            | 8            |

|                          | 66 MHz CLKIN/PCI_SYNC_IN Options |             |       |       |                              |                   |                    |                               |              |              |              |

| s1h                      | 0011                             | 0000110     | æ     | æ     | 66                           | 200               | 400                | —                             | ~            | 8            | 8            |

| s2h                      | 0011                             | 0000101     | æ     | æ     | 66                           | 200               | 500                | _                             | _            | 8            | 8            |

| s3h                      | 0011                             | 0000110     | æ     | æ     | 66                           | 200               | 600                | _                             | _            | —            | 8            |

| s4h                      | 0100                             | 0000011     | æ     | æ     | 66                           | 266               | 400                | _                             | 8            | ∞            | 8            |

| s5h                      | 0100                             | 0000100     | æ     | æ     | 66                           | 266               | 533                | _                             | _            | ∞            | 8            |

| s6h                      | 0100                             | 0000101     | æ     | æ     | 66                           | 266               | 667                | _                             | _            | —            | 8            |

| s7h                      | 0101                             | 0000010     | æ     | æ     | 66                           | 333               | 333                | _                             | 8            | ∞            | 8            |

| s8h                      | 0101                             | 0000011     | æ     | æ     | 66                           | 333               | 500                | _                             | _            | ∞            | 8            |

| s9h                      | 0101                             | 0000100     | 8     | æ     | 66                           | 333               | 667                |                               |              | —            | 8            |

| c1h                      | æ                                | æ           | 00101 | 0     | 66                           | —                 | —                  | 333                           | 8            | 8            | 8            |

| c2h                      | æ                                | æ           | 00110 | 0     | 66                           | —                 | _                  | 400                           | 8            | 8            | 8            |

| c3h                      | æ                                | æ           | 00111 | 0     | 66                           | —                 | _                  | 466                           |              | 8            | 8            |

| c4h                      | æ                                | æ           | 01000 | 0     | 66                           | —                 | _                  | 533                           | _            | 8            | 8            |

| c5h                      | æ                                | æ           | 01001 | 0     | 66                           |                   |                    | 600                           | _            |              | 8            |

Table 76. Suggested PLL Configurations (continued)

Note:

1. The Conf No. consist of prefix, an index and a postfix. The prefix "s" and "c" stands for "syset" and "ce" respectively. The postfix "h" stands for "high input clock." The index is a serial number.

The following steps describe how to use above table. See Example 1.

- 2. Choose the up or down sections in the table according to input clock rate 33 MHz or 66 MHz.

- 3. Select a suitable CSB and core clock rates from Table 76. Copy the SPMF and CORE PLL configuration bits.

- 4. Select a suitable QUICC Engine block clock rate from Table 76. Copy the CEPMF and CEPDF configuration bits.

- 5. Insert the chosen SPMF, COREPLL, CEPMF and CEPDF to the RCWL fields, respectively.

| Index | SPMF | CORE<br>PLL | CEPMF | CEPDF | Input Clock<br>(MHz) | CSB Freq<br>(MHz) | Core Freq<br>(MHz) | QUICC<br>Engine Freq<br>(MHz) | 400<br>(MHz) | 533<br>(MHz) | 667<br>(MHz) |

|-------|------|-------------|-------|-------|----------------------|-------------------|--------------------|-------------------------------|--------------|--------------|--------------|

| Α     | 1000 | 0000011     | 01001 | 0     | 33                   | 266               | 400                | 300                           | 8            | 8            | 8            |

| В     | 0100 | 0000100     | 00110 | 0     | 66                   | 266               | 533                | 400                           | 8            | 8            | 8            |

Example 1. Sample Table Use

- **Example A.** To configure the device with CSB clock rate of 266 MHz, core rate of 400 MHz, and QUICC Engine clock rate 300 MHz while the input clock rate is 33 MHz. Conf No. 's10' and 'c1' are selected from Table 76. SPMF is 1000, CORPLL is 0000011, CEPMF is 01001, and CEPDF is 0.

- **Example B.** To configure the device with CSBCSB clock rate of 266 MHz, core rate of 533 MHz and QUICC Engine clock rate 400 MHz while the input clock rate is 66 MHz. Conf No. 's5h' and 'c2h' are selected from Table 76. SPMF is 0100, CORPLL is 0000100, CEPMF is 00110, and CEPDF is 0.

# 22 Thermal

This section describes the thermal specifications of the MPC8360E/58E.

# 22.1 Thermal Characteristics

This table provides the package thermal characteristics for the 37.5 mm  $\times$  37.5 mm 740-TBGA package.

Table 77. Package Thermal Characteristics for the TBGA Package

| Characteristic                                                    | Symbol                | Value | Unit  | Notes |

|-------------------------------------------------------------------|-----------------------|-------|-------|-------|

| Junction-to-ambient natural convection on single-layer board (1s) | R <sub>θJA</sub>      | 15    | ° C/W | 1, 2  |

| Junction-to-ambient natural convection on four-layer board (2s2p) | R <sub>θJA</sub>      | 11    | ° C/W | 1, 3  |

| Junction-to-ambient (@1 m/s) on single-layer board (1s)           | R <sub>θJMA</sub>     | 10    | ° C/W | 1, 3  |

| Junction-to-ambient (@ 1 m/s) on four-layer board (2s2p)          | R <sub>θJMA</sub>     | 8     | ° C/W | 1, 3  |

| Junction-to-ambient (@ 2 m/s) on single-layer board (1s)          | R <sub>θJMA</sub>     | 9     | ° C/W | 1, 3  |

| Junction-to-ambient (@ 2 m/s) on four-layer board (2s2p)          | R <sub>θJMA</sub>     | 7     | ° C/W | 1, 3  |

| Junction-to-board thermal                                         | $R_{	heta JB}$        | 4.5   | ° C/W | 4     |

| Junction-to-case thermal                                          | $R_{	extsf{	heta}JC}$ | 1.1   | ° C/W | 5     |

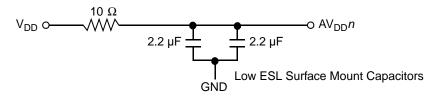

This figure shows the PLL power supply filter circuit.

Figure 56. PLL Power Supply Filter Circuit

# 23.3 Decoupling Recommendations

Due to large address and data buses as well as high operating frequencies, the device can generate transient power surges and high frequency noise in its power supply, especially while driving large capacitive loads. This noise must be prevented from reaching other components in the device system, and the device itself requires a clean, tightly regulated source of power. Therefore, it is recommended that the system designer place at least one decoupling capacitor at each  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  pins of the device. These decoupling capacitors should receive their power from separate  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and GND power planes in the PCB, utilizing short traces to minimize inductance. Capacitors may be placed directly under the device using a standard escape pattern. Others may surround the part.

These capacitors should have a value of 0.01 or 0.1  $\mu$ F. Only ceramic SMT (surface mount technology) capacitors should be used to minimize lead inductance, preferably 0402 or 0603 sizes.

Additionally, it is recommended that there be several bulk storage capacitors distributed around the PCB, feeding the  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  planes, to enable quick recharging of the smaller chip capacitors. These bulk capacitors should have a low ESR (equivalent series resistance) rating to ensure the quick response time necessary. They should also be connected to the power and ground planes through two vias to minimize inductance. Suggested bulk capacitors—100–330  $\mu$ F (AVX TPS tantalum or Sanyo OSCON).

# 23.4 Connection Recommendations

To ensure reliable operation, it is highly recommended to connect unused inputs to an appropriate signal level. Unused active low inputs should be tied to  $OV_{DD}$ ,  $GV_{DD}$ , or  $LV_{DD}$  as required. Unused active high inputs should be connected to GND. All NC (no-connect) signals must remain unconnected.

Power and ground connections must be made to all external V<sub>DD</sub>, GV<sub>DD</sub>, LV<sub>DD</sub>, OV<sub>DD</sub>, and GND pins of the device.

# 23.5 Output Buffer DC Impedance

The device drivers are characterized over process, voltage, and temperature. For all buses, the driver is a push-pull single-ended driver type (open drain for  $I^2C$ ).

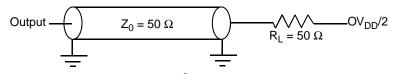

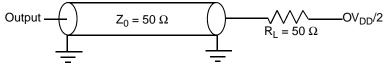

To measure  $Z_0$  for the single-ended drivers, an external resistor is connected from the chip pad to  $OV_{DD}$  or GND. Then, the value of each resistor is varied until the pad voltage is  $OV_{DD}/2$  (see Figure 57). The output impedance is the average of two components, the resistances of the pull-up and pull-down devices. When data is held high, SW1 is closed (SW2 is open) and  $R_p$  is trimmed until the voltage at the pad equals  $OV_{DD}/2$ .  $R_p$  then becomes the resistance of the pull-up devices.  $R_p$  and  $R_N$  are designed to be close to each other in value. Then,  $Z_0 = (R_P + R_N)/2$ .