#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                      |

|---------------------------------|-------------------------------------------------------------|

| Core Processor                  | PowerPC e300                                                |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                              |

| Speed                           | 400MHz                                                      |

| Co-Processors/DSP               | Communications; QUICC Engine                                |

| RAM Controllers                 | DDR, DDR2                                                   |

| Graphics Acceleration           | No                                                          |

| Display & Interface Controllers | -                                                           |

| Ethernet                        | 10/100/1000Mbps (1)                                         |

| SATA                            |                                                             |

| USB                             | USB 1.x (1)                                                 |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                            |

| Operating Temperature           | 0°C ~ 105°C (TA)                                            |

| Security Features               | -                                                           |

| Package / Case                  | 740-LBGA                                                    |

| Supplier Device Package         | 740-TBGA (37.5x37.5)                                        |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8360vvagdga |

|                                 |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

wide range of protocols including ATM, Ethernet, HDLC, and POS. The QUICC Engine module's enhanced interworking eases the transition and reduces investment costs from ATM to IP based systems. The other major features include a dual DDR SDRAM memory controller for the MPC8360E, which allows equipment providers to partition system parameters and data in an extremely efficient way, such as using one 32-bit DDR memory controller for control plane processing and the other for data plane processing. The MPC8358E has a single DDR SDRAM memory controller. The MPC8360E/58E also offers a 32-bit PCI controller, a flexible local bus, and a dedicated security engine.

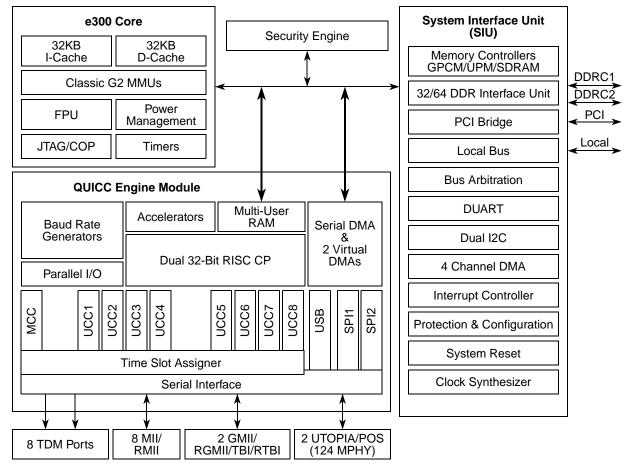

This figure shows the MPC8360Eblock diagram.

Figure 1. MPC8360E Block Diagram

- Eight TDM interfaces on the MPC8360E and four TDM interfaces on the MPC8358E with 1-bit mode for E3/T3 rates in clear channel

- Sixteen independent baud rate generators and 30 input clock pins for supplying clocks to UCC and MCC serial channels (MCC is only available on the MPC8360E)

- Four independent 16-bit timers that can be interconnected as four 32-bit timers

- Interworking functionality:

- Layer 2 10/100-Base T Ethernet switch

- ATM-to-ATM switching (AAL0, 2, 5)

- Ethernet-to-ATM switching with L3/L4 support

- PPP interworking

- Security engine is optimized to handle all the algorithms associated with IPSec, SSL/TLS, SRTP, 802.11i®, iSCSI, and IKE processing. The security engine contains four crypto-channels, a controller, and a set of crypto execution units (EUs).

- Public key execution unit (PKEU) supporting the following:

- RSA and Diffie-Hellman

- Programmable field size up to 2048 bits

- Elliptic curve cryptography

- F2m and F(p) modes

- Programmable field size up to 511 bits

- Data encryption standard execution unit (DEU)

- DES, 3DES

- Two key (K1, K2) or three key (K1, K2, K3)

- ECB and CBC modes for both DES and 3DES

- Advanced encryption standard unit (AESU)

- Implements the Rinjdael symmetric key cipher

- Key lengths of 128, 192, and 256 bits, two key

- ECB, CBC, CCM, and counter modes

- ARC four execution unit (AFEU)

- Implements a stream cipher compatible with the RC4 algorithm

- 40- to 128-bit programmable key

- Message digest execution unit (MDEU)

- SHA with 160-, 224-, or 256-bit message digest

- MD5 with 128-bit message digest

- HMAC with either SHA or MD5 algorithm

- Random number generator (RNG)

- Four crypto-channels, each supporting multi-command descriptor chains

- Static and/or dynamic assignment of crypto-execution units via an integrated controller

- Buffer size of 256 bytes for each execution unit, with flow control for large data sizes

- Storage/NAS XOR parity generation accelerator for RAID applications

- Dual DDR SDRAM memory controllers on the MPC8360E and a single DDR SDRAM memory controller on the MPC8358E

- Programmable timing supporting both DDR1 and DDR2 SDRAM

- On the MPC8360E, the DDR buses can be configured as two 32-bit buses or one 64-bit bus; on the MPC8358E, the DDR bus can be configured as a 32- or 64-bit bus

- 32- or 64-bit data interface, up to 333 MHz (for the MPC8360E) and 266 MHz (for the MPC8358E) data rate

- Four banks of memory, each up to 1 Gbyte

- DRAM chip configurations from 64 Mbits to 1 Gigabit with  $\times 8/\times 16$  data ports

- Full ECC support (when the MPC8360E is configured as 2×32-bit DDR memory controllers, both support ECC)

- Page mode support (up to 16 simultaneous open pages for DDR1, up to 32 simultaneous open pages for DDR2)

- Contiguous or discontiguous memory mapping

- Read-modify-write support

- Sleep mode support for self refresh SDRAM

- Supports auto refreshing

- Supports source clock mode

- On-the-fly power management using CKE

- Registered DIMM support

- 2.5-V SSTL2 compatible I/O for DDR1, 1.8-V SSTL2 compatible I/O for DDR2

- External driver impedance calibration

- On-die termination (ODT)

- PCI interface

- PCI Specification Revision 2.3 compatible

- Data bus widths:

- Single 32-bit data PCI interface that operates at up to 66 MHz

- PCI 3.3-V compatible (not 5-V compatible)

- PCI host bridge capabilities on both interfaces

- PCI agent mode supported on PCI interface

- Support for PCI-to-memory and memory-to-PCI streaming

- Memory prefetching of PCI read accesses and support for delayed read transactions

- Support for posting of processor-to-PCI and PCI-to-memory writes

- On-chip arbitration, supporting five masters on PCI

- Support for accesses to all PCI address spaces

- Parity support

- Selectable hardware-enforced coherency

- Address translation units for address mapping between host and peripheral

- Dual address cycle supported when the device is the target

- Internal configuration registers accessible from PCI

- Local bus controller (LBC)

- Multiplexed 32-bit address and data operating at up to 133 MHz

- Eight chip selects support eight external slaves

- Up to eight-beat burst transfers

- 32-, 16-, and 8-bit port sizes are controlled by an on-chip memory controller

- Three protocol engines available on a per chip select basis:

- General-purpose chip select machine (GPCM)

- Three user programmable machines (UPMs)

- Dedicated single data rate SDRAM controller

- Parity support

- Default boot ROM chip select with configurable bus width (8-, 16-, or 32-bit)

- Programmable interrupt controller (PIC)

- Functional and programming compatibility with the MPC8260 interrupt controller

- Support for 8 external and 35 internal discrete interrupt sources

- Support for one external (optional) and seven internal machine checkstop interrupt sources

| Characteristic                                                                                          | Symbol           | Recommended<br>Value   | Unit | Notes |

|---------------------------------------------------------------------------------------------------------|------------------|------------------------|------|-------|

| PCI, local bus, DUART, system control and power management, I <sup>2</sup> C, SPI, and JTAG I/O voltage | OV <sub>DD</sub> | 3.3 V ± 330 mV         | V    | Ι     |

| Junction temperature                                                                                    | TJ               | 0 to 105<br>-40 to 105 | °C   | 2     |

### Table 2. Recommended Operating Conditions (continued)

Notes:

- 1. GV<sub>DD</sub>, LV<sub>DD</sub>, OV<sub>DD</sub>, AV<sub>DD</sub>, and V<sub>DD</sub> must track each other and must vary in the same direction—either in the positive or negative direction.

- The operating conditions for junction temperature, T<sub>J</sub>, on the 600/333/400 MHz and 500/333/500 MHz on rev. 2.0 silicon is 0° to 70 °C. Refer to Errata General9 in *Chip Errata for the MPC8360E, Rev. 1*.

- 3. For more information on Part Numbering, refer to Table 80.

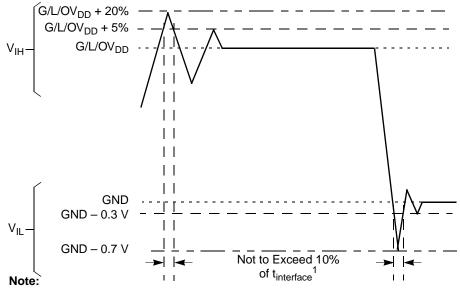

This figure shows the undershoot and overshoot voltages at the interfaces of the device.

1. Note that  $t_{\mbox{interface}}$  refers to the clock period associated with the bus clock interface.

Figure 3. Overshoot/Undershoot Voltage for  $GV_{DD}/OV_{DD}/LV_{DD}$

**DC Electrical Characteristics**

# 4.1 DC Electrical Characteristics

This table provides the clock input (CLKIN/PCI\_SYNC\_IN) DC timing specifications for the device.

| Parameter                 | Condition                                                                                   | Symbol          | Min  | Max                    | Unit |

|---------------------------|---------------------------------------------------------------------------------------------|-----------------|------|------------------------|------|

| Input high voltage        | —                                                                                           | V <sub>IH</sub> | 2.7  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage         | —                                                                                           | V <sub>IL</sub> | -0.3 | 0.4                    | V    |

| CLKIN input current       | 0 V ≤V <sub>IN</sub> ≤OV <sub>DD</sub>                                                      | I <sub>IN</sub> | —    | ±10                    | μA   |

| PCI_SYNC_IN input current | 0 V ≤V <sub>IN</sub> ≤0.5V or<br>OV <sub>DD</sub> – 0.5V ≤V <sub>IN</sub> ≤OV <sub>DD</sub> | I <sub>IN</sub> | _    | ±10                    | μA   |

| PCI_SYNC_IN input current | 0.5 V ≤V <sub>IN</sub> ≤OV <sub>DD</sub> – 0.5 V                                            | I <sub>IN</sub> | —    | ±100                   | μA   |

### 4.2 AC Electrical Characteristics

The primary clock source for the device can be one of two inputs, CLKIN or PCI\_CLK, depending on whether the device is configured in PCI host or PCI agent mode. This table provides the clock input (CLKIN/PCI\_CLK) AC timing specifications for the device.

| Table 8. | <b>CLKIN</b> | AC | Timing | Specifications |

|----------|--------------|----|--------|----------------|

|----------|--------------|----|--------|----------------|

| Parameter/Condition              | Symbol                               | Min | Typical | Max   | Unit | Notes |

|----------------------------------|--------------------------------------|-----|---------|-------|------|-------|

| CLKIN/PCI_CLK frequency          | f <sub>CLKIN</sub>                   | —   | _       | 66.67 | MHz  | 1     |

| CLKIN/PCI_CLK cycle time         | t <sub>CLKIN</sub>                   | 15  | —       | _     | ns   | —     |

| CLKIN/PCI_CLK rise and fall time | t <sub>KH</sub> , t <sub>KL</sub>    | 0.6 | 1.0     | 2.3   | ns   | 2     |

| CLKIN/PCI_CLK duty cycle         | t <sub>KHK</sub> /t <sub>CLKIN</sub> | 40  | —       | 60    | %    | 3     |

| CLKIN/PCI_CLK jitter             | _                                    | —   | —       | ±150  | ps   | 4, 5  |

### Notes:

- 1. **Caution:** The system, core, USB, security, and 10/100/1000 Ethernet must not exceed their respective maximum or minimum operating frequencies.

- 2. Rise and fall times for CLKIN/PCI\_CLK are measured at 0.4 V and 2.7 V.

- 3. Timing is guaranteed by design and characterization.

- 4. This represents the total input jitter-short term and long term-and is guaranteed by design.

- 5. The CLKIN/PCI\_CLK driver's closed loop jitter bandwidth should be <500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track CLKIN drivers with the specified jitter.

## 4.3 Gigabit Reference Clock Input Timing

This table provides the Gigabit reference clocks (GTX\_CLK125) AC timing specifications.

### Table 9. GTX\_CLK125 AC Timing Specifications

At recommended operating conditions with LV<sub>DD</sub> = 2.5  $\pm$  0.125 mV/ 3.3 V  $\pm$  165 mV

| Parameter/Condition   | Symbol            | Min | Typical | Max | Unit | Notes |

|-----------------------|-------------------|-----|---------|-----|------|-------|

| GTX_CLK125 frequency  | t <sub>G125</sub> | -   | 125     | _   | MHz  | —     |

| GTX_CLK125 cycle time | t <sub>G125</sub> |     | 8       |     | ns   | —     |

### 5.2 **RESET AC Electrical Characteristics**

This section describes the AC electrical specifications for the reset initialization timing requirements of the device. This table provides the reset initialization AC timing specifications for the DDR SDRAM component(s).

| Parameter/Condition                                                                                                                                        | Min | Max | Unit                     | Notes |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------------|-------|

| Required assertion time of $\overrightarrow{\text{HRESET}}$ or $\overrightarrow{\text{SRESET}}$ (input) to activate reset flow                             | 32  | -   | t <sub>PCI_SYNC_IN</sub> | 1     |

| Required assertion time of $\overrightarrow{\text{PORESET}}$ with stable clock applied to CLKIN when the device is in PCI host mode                        | 32  | -   | <sup>t</sup> CLKIN       | 2     |

| Required assertion time of PORESET with stable clock applied to PCI_SYNC_IN when the device is in PCI agent mode                                           | 32  | -   | t <sub>PCI_SYNC_IN</sub> | 1     |

| HRESET/SRESET assertion (output)                                                                                                                           | 512 | _   | t <sub>PCI_SYNC_IN</sub> | 1     |

| HRESET negation to SRESET negation (output)                                                                                                                | 16  | —   | t <sub>PCI_SYNC_IN</sub> | 1     |

| Input setup time for POR config signals (CFG_RESET_SOURCE[0:2] and CFG_CLKIN_DIV) with respect to negation of PORESET when the device is in PCI host mode  | 4   | —   | <sup>t</sup> CLKIN       | 2     |

| Input setup time for POR config signals (CFG_RESET_SOURCE[0:2] and CFG_CLKIN_DIV) with respect to negation of PORESET when the device is in PCI agent mode | 4   | -   | <sup>t</sup> PCI_SYNC_IN | 1     |

| Input hold time for POR config signals with respect to negation of $\overline{\text{HRESET}}$                                                              | 0   | —   | ns                       | —     |

| Time for the device to turn off POR config signals with respect to the assertion of HRESET                                                                 |     | 4   | ns                       | 3     |

| Time for the device to turn on POR config signals with respect to the negation of $\overrightarrow{HRESET}$                                                | 1   | -   | t <sub>PCI_SYNC_IN</sub> | 1, 3  |

### Table 11. RESET Initialization Timing Specifications

#### Notes:

- t<sub>PCI\_SYNC\_IN</sub> is the clock period of the input clock applied to PCI\_SYNC\_IN. When the device is In PCI host mode the primary clock is applied to the CLKIN input, and PCI\_SYNC\_IN period depends on the value of CFG\_CLKIN\_DIV. Refer MPC8360E PowerQUICC II Pro Integrated Communications Processor Reference Manual for more details.

- t<sub>CLKIN</sub> is the clock period of the input clock applied to CLKIN. It is only valid when the device is in PCI host mode. Refer MPC8360E PowerQUICC II Pro Integrated Communications Processor Reference Manual for more details.

- 3. POR config signals consists of CFG\_RESET\_SOURCE[0:2] and CFG\_CLKIN\_DIV.

This table provides the PLL and DLL lock times.

### Table 12. PLL and DLL Lock Times

| Parameter/Condition | Min  | Max     | Unit           | Notes |

|---------------------|------|---------|----------------|-------|

| PLL lock times      | —    | 100     | μs             |       |

| DLL lock times      | 7680 | 122,880 | csb_clk cycles | 1, 2  |

Notes:

1. DLL lock times are a function of the ratio between the output clock and the coherency system bus clock (csb\_clk). A 2:1 ratio results in the minimum and an 8:1 ratio results in the maximum.

2. The csb\_clk is determined by the CLKIN and system PLL ratio. See Section 21, "Clocking," for more information.

## 6.1 DDR and DDR2 SDRAM DC Electrical Characteristics

This table provides the recommended operating conditions for the DDR2 SDRAM component(s) of the device when  $GV_{DD}(typ) = 1.8 \text{ V}.$

| Parameter/Condition                                     | Symbol            | Min                       | Мах                               | Unit | Notes |

|---------------------------------------------------------|-------------------|---------------------------|-----------------------------------|------|-------|

| I/O supply voltage                                      | GV <sub>DD</sub>  | 1.71                      | 1.89                              | V    | 1     |

| I/O reference voltage                                   | MV <sub>REF</sub> | $0.49 	imes GV_{DD}$      | $0.51 	imes \text{GV}_{	ext{DD}}$ | V    | 2     |

| I/O termination voltage                                 | V <sub>TT</sub>   | MV <sub>REF</sub> - 0.04  | MV <sub>REF</sub> + 0.04          | V    | 3     |

| Input high voltage                                      | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.125 | GV <sub>DD</sub> + 0.3            | V    | _     |

| Input low voltage                                       | V <sub>IL</sub>   | -0.3                      | MV <sub>REF</sub> – 0.125         | V    | _     |

| Output leakage current                                  | I <sub>OZ</sub>   | _                         | ±10                               | μA   | 4     |

| Output high current (V <sub>OUT</sub> = 1.420 V)        | I <sub>OH</sub>   | -13.4                     | —                                 | mA   | _     |

| Output low current (V <sub>OUT</sub> = 0.280 V)         | I <sub>OL</sub>   | 13.4                      | —                                 | mA   | _     |

| MV <sub>REF</sub> input leakage current                 | I <sub>VREF</sub> | _                         | ±10                               | μA   | _     |

| Input current (0 V ≛/ <sub>IN</sub> ≤OV <sub>DD</sub> ) | I <sub>IN</sub>   | _                         | ±10                               | μA   | _     |

### Table 14. DDR2 SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 1.8 V

### Notes:

1.  $GV_{DD}$  is expected to be within 50 mV of the DRAM  $GV_{DD}$  at all times.

MV<sub>REF</sub> is expected to equal 0.5 × GV<sub>DD</sub>, and to track GV<sub>DD</sub> DC variations as measured at the receiver. Peak-to-peak noise on MV<sub>REF</sub> cannot exceed ±2% of the DC value.

V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to equal MV<sub>REF</sub>. This rail should track variations in the DC level of MV<sub>REF</sub>.

4. Output leakage is measured with all outputs disabled, 0 V  $\leq$ V<sub>OUT</sub>  $\leq$ GV<sub>DD</sub>.

This table provides the DDR2 capacitance when  $GV_{DD}(typ) = 1.8$  V.

### Table 15. DDR2 SDRAM Capacitance for GV<sub>DD</sub>(typ)=1.8 V

| Parameter/Condition                          | Symbol           | Min | Max | Unit | Notes |

|----------------------------------------------|------------------|-----|-----|------|-------|

| Input/output capacitance: DQ, DQS, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1     |

| Delta input/output capacitance: DQ, DQS, DQS | C <sub>DIO</sub> | —   | 0.5 | pF   | 1     |

#### Note:

1. This parameter is sampled.  $GV_{DD} = 1.8 \text{ V} \pm 0.090 \text{ V}$ , f = 1 MHz, T<sub>A</sub> = 25°C,  $V_{OUT} = GV_{DD}/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

This table provides the recommended operating conditions for the DDR SDRAM component(s) of the device when  $GV_{DD}(typ) = 2.5 \text{ V}.$

### Table 16. DDR SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 2.5 V

| Parameter/Condition     | Symbol            | Min                      | Max                               | Unit | Notes |

|-------------------------|-------------------|--------------------------|-----------------------------------|------|-------|

| I/O supply voltage      | GV <sub>DD</sub>  | 2.375                    | 2.625                             | V    | 1     |

| I/O reference voltage   | MV <sub>REF</sub> | $0.49 	imes GV_{DD}$     | $0.51 	imes \text{GV}_{	ext{DD}}$ | V    | 2     |

| I/O termination voltage | V <sub>TT</sub>   | MV <sub>REF</sub> – 0.04 | MV <sub>REF</sub> + 0.04          | V    | 3     |

GMII, MII, RMII, TBI, RGMII, and RTBI AC Timing Specifications

### 8.2.1.2 GMII Receive AC Timing Specifications

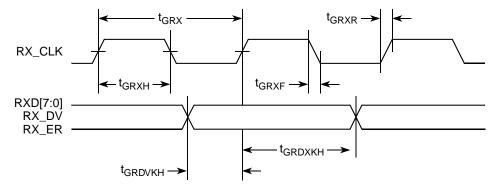

This table provides the GMII receive AC timing specifications.

### **Table 28. GMII Receive AC Timing Specifications**

At recommended operating conditions with LV\_{DD}/OV\_{DD} of 3.3 V  $\pm$  10%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit | Notes |

|---------------------------------------------|-------------------------------------|-----|-----|-----|------|-------|

| RX_CLK clock period                         | t <sub>GRX</sub>                    | _   | 8.0 | _   | ns   | —     |

| RX_CLK duty cycle                           | t <sub>GRXH</sub> /t <sub>GRX</sub> | 40  | —   | 60  | %    | —     |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>GRDVKH</sub>                 | 2.0 | —   | _   | ns   | _     |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>GRDXKH</sub>                 | 0.2 | —   | _   | ns   | 2     |

| RX_CLK clock rise time, (20% to 80%)        | t <sub>GRXR</sub>                   | _   | —   | 1.0 | ns   | _     |

| RX_CLK clock fall time, (80% to 20%)        | t <sub>GRXF</sub>                   | _   |     | 1.0 | ns   | _     |

### Notes:

- 1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>GRDVKH</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>RX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>RX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>GRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GRX</sub> represents the GMII (G) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- In rev. 2.0 silicon, due to errata, t<sub>GRDXKH</sub> minimum is 0.5 which is not compliant with the standard. Refer to Errata QE\_ENET18 in Chip Errata for the MPC8360E, Rev. 1.

This figure shows the GMII receive AC timing diagram.

Figure 11. GMII Receive AC Timing Diagram

### 8.2.2 MII AC Timing Specifications

This section describes the MII transmit and receive AC timing specifications.

### 8.2.2.1 MII Transmit AC Timing Specifications

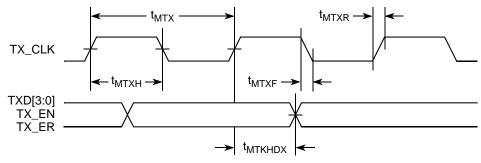

This table provides the MII transmit AC timing specifications.

### Table 29. MII Transmit AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/OV_{DD}$  of 3.3 V ± 10%.

| Parameter/Condition                             | Symbol <sup>1</sup>                        | Min | Тур | Max     | Unit |

|-------------------------------------------------|--------------------------------------------|-----|-----|---------|------|

| TX_CLK clock period 10 Mbps                     | t <sub>MTX</sub>                           | _   | 400 | —       | ns   |

| TX_CLK clock period 100 Mbps                    | t <sub>MTX</sub>                           | _   | 40  | _       | ns   |

| TX_CLK duty cycle                               | t <sub>MTXH</sub> /t <sub>MTX</sub>        | 35  | _   | 65      | %    |

| TX_CLK to MII data TXD[3:0], TX_ER, TX_EN delay | t <sub>MTKHDX</sub><br>t <sub>MTKHDV</sub> | 1   | 5   | —<br>15 | ns   |

| TX_CLK data clock rise time, (20% to 80%)       | t <sub>MTXR</sub>                          | 1.0 | _   | 4.0     | ns   |

| TX_CLK data clock fall time, (80% to 20%)       | t <sub>MTXF</sub>                          | 1.0 | _   | 4.0     | ns   |

#### Note:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub></sub>

This figure shows the MII transmit AC timing diagram.

Figure 12. MII Transmit AC Timing Diagram

#### **Ethernet Management Interface Electrical Characteristics**

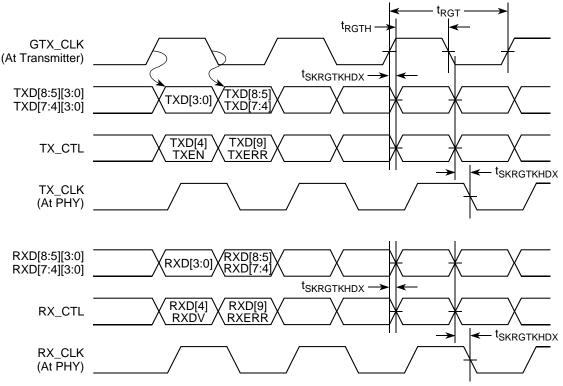

This figure shows the RGMII and RTBI AC timing and multiplexing diagrams.

Figure 20. RGMII and RTBI AC Timing and Multiplexing Diagrams

### 8.3 Ethernet Management Interface Electrical Characteristics

The electrical characteristics specified here apply to MII management interface signals MDIO (management data input/output) and MDC (management data clock). The electrical characteristics for GMII, RGMII, TBI, and RTBI are specified in Section 8.1, "Three-Speed Ethernet Controller (10/100/1000 Mbps)— GMII/MII/RMII/TBI/RGMII/RTBI Electrical Characteristics."

### 8.3.1 MII Management DC Electrical Characteristics

The MDC and MDIO are defined to operate at a supply voltage of 3.3 V. The DC electrical characteristics for MDIO and MDC are provided in this table.

| Parameter              | Symbol           | Conditions                             |                        | Min  | Мах                    | Unit |

|------------------------|------------------|----------------------------------------|------------------------|------|------------------------|------|

| Supply voltage (3.3 V) | OV <sub>DD</sub> | -                                      | _                      | 2.97 | 3.63                   | V    |

| Output high voltage    | V <sub>OH</sub>  | I <sub>OH</sub> = -1.0 mA              | $OV_{DD} = Min$        | 2.10 | OV <sub>DD</sub> + 0.3 | V    |

| Output low voltage     | V <sub>OL</sub>  | I <sub>OL</sub> = 1.0 mA               | OV <sub>DD</sub> = Min | GND  | 0.50                   | V    |

| Input high voltage     | V <sub>IH</sub>  | -                                      | _                      | 2.00 | _                      | V    |

| Input low voltage      | V <sub>IL</sub>  | —                                      |                        | _    | 0.80                   | V    |

| Input current          | I <sub>IN</sub>  | 0 V ≤V <sub>IN</sub> ≤OV <sub>DD</sub> |                        | _    | ±10                    | μA   |

| able 36. MII Management DC Electrical Characteristics When Powered at 3.3 V |

|-----------------------------------------------------------------------------|

|-----------------------------------------------------------------------------|

| Parameter                                                   | Symbol <sup>1</sup>  | Min | Мах | Unit | Notes |

|-------------------------------------------------------------|----------------------|-----|-----|------|-------|

| LUPWAIT input hold from local bus clock                     | t <sub>LBIXKH2</sub> | 1.0 | _   | ns   | 3, 4  |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT1</sub> | 1.5 |     | ns   | 5     |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT2</sub> | 3.0 |     | ns   | 6     |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT3</sub> | 2.5 |     | ns   | 7     |

| Local bus clock to LALE rise                                | t <sub>LBKHLR</sub>  | —   | 4.5 | ns   | _     |

| Local bus clock to output valid (except LAD/LDP and LALE)   | t <sub>LBKHOV1</sub> | —   | 4.5 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                   | t <sub>LBKHOV2</sub> | —   | 4.5 | ns   | 3     |

| Local bus clock to address valid for LAD                    | t <sub>LBKHOV3</sub> | —   | 4.5 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)  | t <sub>LBKHOX1</sub> | 1.0 | _   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                | t <sub>LBKHOX2</sub> | 1.0 | _   | ns   | 3     |

| Local bus clock to output high impedance for LAD/LDP        | t <sub>LBKHOZ</sub>  | —   | 3.8 | ns   | 8     |

### Table 40. Local Bus General Timing Parameters—DLL Enabled (continued)

### Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the output (O) going invalid (X) or output hold time.

</sub>

- 2. All timings are in reference to rising edge of LSYNC\_IN.

- 3. All signals are measured from  $OV_{DD}/2$  of the rising edge of LSYNC\_IN to  $0.4 \times OV_{DD}$  of the signal in question for 3.3-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. t<sub>LBOTOT1</sub> should be used when RCWH[LALE] is not set and when the load on LALE output pin is at least 10 pF less than the load on LAD output pins.

- t<sub>LBOTOT2</sub> should be used when RCWH[LALE] is set and when the load on LALE output pin is at least 10 pF less than the load on LAD output pins.

- 7. t<sub>LBOTOT3</sub> should be used when RCWH[LALE] is set and when the load on LALE output pin equals to the load on LAD output pins.

- 8. For purposes of active/float timing measurements, the Hi-Z or off-state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

This table describes the general timing parameters of the local bus interface of the device.

#### Table 41. Local Bus General Timing Parameters—DLL Bypass Mode<sup>9</sup>

| Parameter                                                   | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|-------------------------------------------------------------|----------------------|-----|-----|------|-------|

| Local bus cycle time                                        | t <sub>LBK</sub>     | 15  | —   | ns   | 2     |

| Input setup to local bus clock                              | t <sub>LBIVKH</sub>  | 7   | —   | ns   | 3, 4  |

| Input hold from local bus clock                             | t <sub>LBIXKH</sub>  | 1.0 | —   | ns   | 3, 4  |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT1</sub> | 1.5 | —   | ns   | 5     |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT2</sub> | 3   | —   | ns   | 6     |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT3</sub> | 2.5 | —   | ns   | 7     |

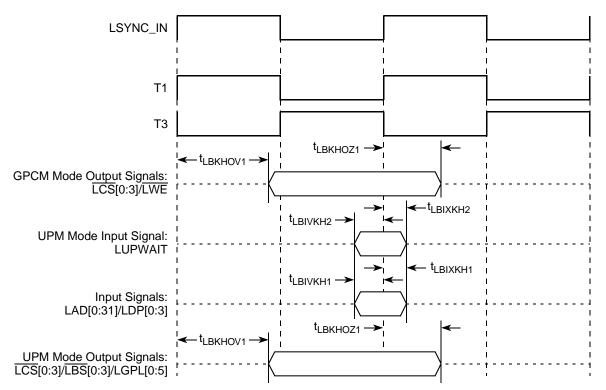

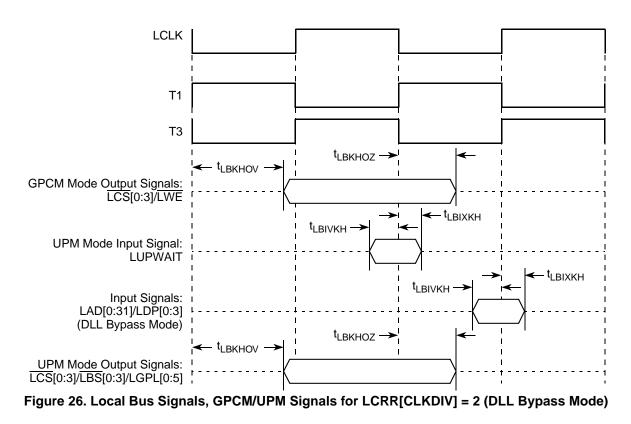

#### Local Bus AC Electrical Specifications

Figure 25. Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 2 (DLL Enabled)

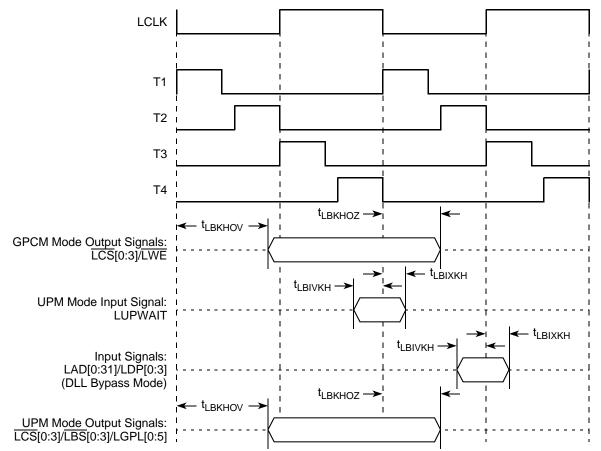

Figure 27. Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 4 (DLL Bypass Mode)

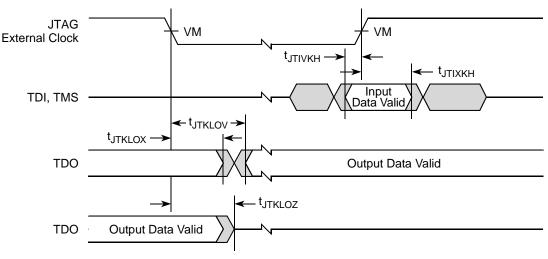

This figure provides the test access port timing diagram.

VM = Midpoint Voltage (OV<sub>DD</sub>/2)

Figure 33. Test Access Port Timing Diagram

# 11 I<sup>2</sup>C

This section describes the DC and AC electrical characteristics for the  $I^2C$  interface of the MPC8360E/58E.

# 11.1 I<sup>2</sup>C DC Electrical Characteristics

This table provides the DC electrical characteristics for the  $I^2C$  interface of the device.

### Table 44. I<sup>2</sup>C DC Electrical Characteristics

At recommended operating conditions with  $OV_{DD}$  of 3.3 V ± 10%.

| Parameter                                                                                     | Symbol              | Min                   | Max                    | Unit | Notes |

|-----------------------------------------------------------------------------------------------|---------------------|-----------------------|------------------------|------|-------|

| Input high voltage level                                                                      | V <sub>IH</sub>     | $0.7 	imes OV_{DD}$   | OV <sub>DD</sub> + 0.3 | V    | —     |

| Input low voltage level                                                                       | V <sub>IL</sub>     | -0.3                  | $0.3 	imes OV_{DD}$    | V    | —     |

| Low level output voltage                                                                      | V <sub>OL</sub>     | 0                     | 0.4                    | V    | 1     |

| Output fall time from $V_{IH}(min)$ to $V_{IL}(max)$ with a bus capacitance from 10 to 400 pF | t <sub>I2KLKV</sub> | $20 + 0.1 \times C_B$ | 250                    | ns   | 2     |

| Pulse width of spikes which must be suppressed by the input filter                            | t <sub>i2KHKL</sub> | 0                     | 50                     | ns   | 3     |

| Capacitance for each I/O pin                                                                  | CI                  | —                     | 10                     | pF   | —     |

| Input current (0 V ≤V <sub>IN</sub> ≤OV <sub>DD</sub> )                                       | I <sub>IN</sub>     | —                     | ±10                    | μA   | 4     |

### Notes:

1. Output voltage (open drain or open collector) condition = 3 mA sink current.

- 2.  $C_B$  = capacitance of one bus line in pF.

- 3. Refer to the MPC8360E Integrated Communications Processor Reference Manual for information on the digital filter used.

- 4. I/O pins obstruct the SDA and SCL lines if OV<sub>DD</sub> is switched off.

**I2C AC Electrical Specifications**

# 11.2 I<sup>2</sup>C AC Electrical Specifications

This table provides the AC timing parameters for the I<sup>2</sup>C interface of the device.

### Table 45. I<sup>2</sup>C AC Electrical Specifications

All values refer to  $V_{IH}$  (min) and  $V_{IL}$  (max) levels (see Table 44).

| Parameter                                                                                    | Symbol <sup>1</sup> | Min                                  | Max                  | Unit | Note |

|----------------------------------------------------------------------------------------------|---------------------|--------------------------------------|----------------------|------|------|

| SCL clock frequency                                                                          | f <sub>I2C</sub>    | 0                                    | 400                  | kHz  | 2    |

| Low period of the SCL clock                                                                  | t <sub>I2CL</sub>   | 1.3                                  | _                    | μs   | —    |

| High period of the SCL clock                                                                 | t <sub>I2CH</sub>   | 0.6                                  | _                    | μs   | —    |

| Setup time for a repeated START condition                                                    | t <sub>I2SVKH</sub> | 0.6                                  | _                    | μs   | —    |

| Hold time (repeated) START condition (after this period, the first clock pulse is generated) | t <sub>I2SXKL</sub> | 0.6                                  | _                    | μs   | _    |

| Data setup time                                                                              | t <sub>I2DVKH</sub> | 100                                  | —                    | ns   | 3    |

| Data hold time:<br>CBUS compatible masters<br>I <sup>2</sup> C bus devices                   | t <sub>I2DXKL</sub> | $\overline{0^2}$                     | <br>0.9 <sup>3</sup> | μs   | _    |

| Rise time of both SDA and SCL signals                                                        | t <sub>I2CR</sub>   | 20 + 0.1 C <sub>b</sub> <sup>4</sup> | 300                  | ns   | _    |

| Fall time of both SDA and SCL signals                                                        | t <sub>I2CF</sub>   | 20 + 0.1 C <sub>b</sub> <sup>4</sup> | 300                  | ns   | —    |

| Set-up time for STOP condition                                                               | t <sub>I2PVKH</sub> | 0.6                                  | _                    | μs   | —    |

| Bus free time between a STOP and START condition                                             | t <sub>I2KHDX</sub> | 1.3                                  | _                    | μs   | —    |

| Noise margin at the LOW level for each connected device (including hysteresis)               | V <sub>NL</sub>     | $0.1 \times \text{OV}_{\text{DD}}$   | _                    | V    | —    |

| Noise margin at the HIGH level for each connected device (including hysteresis)              | V <sub>NH</sub>     | $0.2 \times \text{OV}_{\text{DD}}$   | —                    | V    | —    |

#### Notes:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional</sub>

block)(signal)(state)(reference)(state) for inputs and t<sub>(first</sub> two letters of functional block)(reference)(state)(signal)(state) for outputs. For example,  $t_{I2DVKH}$  symbolizes I<sup>2</sup>C timing (I2) with respect to the time data input signals (D) reach the valid state (V) relative to the  $t_{I2C}$  clock reference (K) going to the high (H) state or setup time. Also,  $t_{I2SXKL}$  symbolizes I<sup>2</sup>C timing (I2) for the time that the data with respect to the start condition (S) went invalid (X) relative to the  $t_{I2C}$  clock reference (K) going to the low (L) state or hold time. Also,  $t_{I2PVKH}$  symbolizes I<sup>2</sup>C timing (I2) for the time that the data with respect to the start condition (S) went invalid (X) relative to the  $t_{I2C}$  clock reference (K) going to the low (L) state or hold time. Also,  $t_{I2PVKH}$  symbolizes I<sup>2</sup>C timing (I2) for the time that the data with respect to the stop condition (P) reaching the valid state (V) relative to the  $t_{I2C}$  clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

The device provides a hold time of at least 300 ns for the SDA signal (referred to the V<sub>IH</sub> min of the SCL signal) to bridge the undefined region of the falling edge of SCL.

3. The maximum  $t_{12DVKH}$  has only to be met if the device does not stretch the LOW period ( $t_{12CL}$ ) of the SCL signal.

4. C<sub>B</sub> = capacitance of one bus line in pF.

**TDM/SI DC Electrical Characteristics**

# 17 TDM/SI

This section describes the DC and AC electrical specifications for the time-division-multiplexed and serial interface of the MPC8360E/58E.

# 17.1 TDM/SI DC Electrical Characteristics

This table provides the DC electrical characteristics for the device TDM/SI.

Table 57. TDM/SI DC Electrical Characteristics

| Characteristic      | Symbol          | Condition                              | Min  | Мах                    | Unit |

|---------------------|-----------------|----------------------------------------|------|------------------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -2.0 mA              | 2.4  | _                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA               | _    | 0.5                    | V    |

| Input high voltage  | V <sub>IH</sub> | _                                      | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | _                                      | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | 0 V ≤V <sub>IN</sub> ≤OV <sub>DD</sub> | —    | ±10                    | μA   |

## 17.2 TDM/SI AC Timing Specifications

This table provides the TDM/SI input and output AC timing specifications.

| Table 58. | TDM/SI | AC | Timina                                | S | pecifications <sup>1</sup> | l |

|-----------|--------|----|---------------------------------------|---|----------------------------|---|

|           |        |    | · · · · · · · · · · · · · · · · · · · | - | o o o ni o a no no         |   |

| Characteristic                                | Symbol <sup>2</sup> | Min | Max <sup>3</sup> | Unit |

|-----------------------------------------------|---------------------|-----|------------------|------|

| TDM/SI outputs—External clock delay           | t <sub>SEKHOV</sub> | 2   | 10               | ns   |

| TDM/SI outputs—External clock high impedance  | t <sub>SEKHOX</sub> | 2   | 10               | ns   |

| TDM/SI inputs—External clock input setup time | t <sub>SEIVKH</sub> | 5   | —                | ns   |

| TDM/SI inputs—External clock input hold time  | t <sub>SEIXKH</sub> | 2   | —                | ns   |

Notes:

- 1. Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are measured at the pin.

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>SEKHOX</sub> symbolizes the TDM/SI outputs external timing (SE) for the time t<sub>TDM/SI</sub> memory clock reference (K) goes from the high state (H) until outputs (O) are invalid (X).

</sub>

- 3. Timings are measured from the positive or negative edge of the clock, according to SIxMR [CE] and SITXCEI[TXCEIx]. Refer *MPC8360E Integrated Communications Processor Reference Manual* for more details.

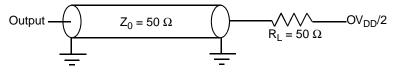

This figure provides the AC test load for the TDM/SI.

Figure 44. TDM/SI AC Test Load

Figure 45 represents the AC timing from Table 56. Note that although the specifications generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge is the active edge.

# 20 Package and Pin Listings

This section details package parameters, pin assignments, and dimensions. The MPC8360E/58E is available in a tape ball grid array (TBGA), see Section 20.1, "Package Parameters for the TBGA Package," and Section 20.2, "Mechanical Dimensions of the TBGA Package," for information on the package.

## 20.1 Package Parameters for the TBGA Package

The package parameters for rev. 2.0 silicon are as provided in the following list. The package type is  $37.5 \text{ mm} \times 37.5 \text{ mm}$ , 740 tape ball grid array (TBGA).

| Package outline         | 37.5 mm × 37.5 mm               |

|-------------------------|---------------------------------|

| Interconnects           | 740                             |

| Pitch                   | 1.00 mm                         |

| Module height (typical) | 1.46 mm                         |

| Solder Balls            | 62 Sn/36 Pb/2 Ag (ZU package)   |

|                         | 95.5 Sn/0.5 Cu/4Ag (VV package) |

| Ball diameter (typical) | 0.64 mm                         |

### Table 67. MPC8358E TBGA Pinout Listing (continued)

| Signal                                         | Package Pin Number         | Pin Type | Power<br>Supply    | Notes |  |  |  |  |

|------------------------------------------------|----------------------------|----------|--------------------|-------|--|--|--|--|

| IRQ[4:5]                                       | G33, G32                   | I/O      | OV <sub>DD</sub>   | —     |  |  |  |  |

| IRQ[6]/LCS[6]/CKSTOP_OUT                       | E35                        | I/O      | OV <sub>DD</sub>   | _     |  |  |  |  |

| IRQ[7]/LCS[7]/CKSTOP_IN                        | H36                        | I/O      | OV <sub>DD</sub>   | —     |  |  |  |  |

| DUART                                          |                            |          |                    |       |  |  |  |  |

| UART1_SOUT/M1SRCID[0]/<br>M2SRCID[0]/LSRCID[0] | E32                        | 0        | OV <sub>DD</sub>   | -     |  |  |  |  |

| UART1_SIN/M1SRCID[1]/<br>M2SRCID[1]/LSRCID[1]  | B34                        | I/O      | OV <sub>DD</sub>   | —     |  |  |  |  |

| UART1_CTS/M1SRCID[2]/<br>M2SRCID[2]/LSRCID[2]  | C34                        | I/O      | OV <sub>DD</sub>   | —     |  |  |  |  |

| UART1_RTS/M1SRCID[3]/<br>M2SRCID[3]/LSRCID[3]  | A35                        | 0        | OV <sub>DD</sub>   | —     |  |  |  |  |

|                                                | I <sup>2</sup> C Interface |          |                    |       |  |  |  |  |

| IIC1_SDA                                       | D34                        | I/O      | OV <sub>DD</sub>   | 2     |  |  |  |  |

| IIC1_SCL                                       | B35                        | I/O      | OV <sub>DD</sub>   | 2     |  |  |  |  |

| IIC2_SDA                                       | E33                        | I/O      | OV <sub>DD</sub>   | 2     |  |  |  |  |

| IIC2_SCL                                       | C35                        | I/O      | OV <sub>DD</sub>   | 2     |  |  |  |  |

|                                                | QUICC Engine               |          |                    |       |  |  |  |  |

| CE_PA[0]                                       | F8                         | I/O      | LV <sub>DD0</sub>  | _     |  |  |  |  |

| CE_PA[1:2]                                     | AH1, AG5                   | I/O      | OV <sub>DD</sub>   | _     |  |  |  |  |

| CE_PA[3:7]                                     | F6, D4, C3, E5, A3         | I/O      | LV <sub>DD</sub> 0 | —     |  |  |  |  |

| CE_PA[8]                                       | AG3                        | I/O      | OV <sub>DD</sub>   | _     |  |  |  |  |

| CE_PA[9:12]                                    | F7, B3, E6, B4             | I/O      | LV <sub>DD</sub> 0 |       |  |  |  |  |

| CE_PA[13:14]                                   | AG1, AF6                   | I/O      | OV <sub>DD</sub>   | —     |  |  |  |  |

| CE_PA[15]                                      | B2                         | I/O      | LV <sub>DD</sub> 0 | —     |  |  |  |  |

| CE_PA[16]                                      | AF4                        | I/O      | OV <sub>DD</sub>   | _     |  |  |  |  |

| CE_PA[17:21]                                   | B16, A16, E17, A17, B17    | I/O      | LV <sub>DD</sub> 1 |       |  |  |  |  |

| CE_PA[22]                                      | AF3                        | I/O      | OV <sub>DD</sub>   | _     |  |  |  |  |

| CE_PA[23:26]                                   | C18, D18, E18, A18         | I/O      | LV <sub>DD</sub> 1 | —     |  |  |  |  |

| CE_PA[27:28]                                   | AF2, AE6                   | I/O      | OV <sub>DD</sub>   | —     |  |  |  |  |

| CE_PA[29]                                      | B19                        | I/O      | LV <sub>DD</sub> 1 | _     |  |  |  |  |

| CE_PA[30]                                      | AE5                        | I/O      | OV <sub>DD</sub>   | —     |  |  |  |  |

| CE_PA[31]                                      | F16                        | I/O      | LV <sub>DD</sub> 1 | —     |  |  |  |  |

Pinout Listings

| Signal             | Package Pin Number                                                                                                                                                                                                                                                                                       | Pin Type                                                                    | Power<br>Supply             | Notes |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------|-------|--|

| LV <sub>DD</sub> 1 | C17, D16                                                                                                                                                                                                                                                                                                 | Power for<br>UCC2<br>Ethernet<br>interface<br>option 1<br>(2.5 V,<br>3.3 V) | LV <sub>DD</sub> 1          | 9     |  |

| LV <sub>DD</sub> 2 | B18, E21                                                                                                                                                                                                                                                                                                 | Power for<br>UCC2<br>Ethernet<br>interface<br>option 2<br>(2.5 V,<br>3.3 V) | LV <sub>DD</sub> 2          | 9     |  |

| V <sub>DD</sub>    | C36, D29, D35, E16, F9, F12, F15, F17, F18, F20,<br>F21, F23, F25, F26, F29, F31, F32, F33, G6, J6,<br>K32, M32, N6, P33, R6, R32, U32, V6, Y5, Y32,<br>AB6, AB33, AD6, AF32, AK6, AL6, AM7, AM9,<br>AM10, AM11, AM12, AM13, AM14, AM15, AM18,<br>AM21, AM25, AM28, AM32, AN15, AN21, AN26,<br>AU9, AU17 | Power for<br>core<br>(1.2 V)                                                | V <sub>DD</sub>             | _     |  |

| OV <sub>DD</sub>   | A10, B9, B15, B32, C1, C12, C22, C29, D24, E3,<br>E10, E27, G4, H35, J1, J35, K2, M4, N3, N34, R2,<br>R37, T36, U2, U33, V4, V34, W3, Y35, Y37, AA1,<br>AA36, AB2, AB34                                                                                                                                  | PCI,<br>10/100<br>Ethernet,<br>and other<br>standard<br>(3.3 V)             | OV <sub>DD</sub>            | _     |  |

| MVREF1             | AN20                                                                                                                                                                                                                                                                                                     | I                                                                           | DDR<br>reference<br>voltage | _     |  |

| MVREF2             | AU32                                                                                                                                                                                                                                                                                                     | I                                                                           | DDR<br>reference<br>voltage | —     |  |

|                    |                                                                                                                                                                                                                                                                                                          |                                                                             |                             |       |  |

| SPARE1             | B11                                                                                                                                                                                                                                                                                                      | I/O                                                                         | OV <sub>DD</sub>            | 8     |  |

| SPARE3             | AH32                                                                                                                                                                                                                                                                                                     | —                                                                           | GV <sub>DD</sub>            | 8     |  |

| SPARE4             | AU18                                                                                                                                                                                                                                                                                                     |                                                                             | GV <sub>DD</sub>            | 7     |  |

| SPARE5             | AP1                                                                                                                                                                                                                                                                                                      | —                                                                           | GV <sub>DD</sub>            | 8     |  |

### Table 67. MPC8358E TBGA Pinout Listing (continued)

Suggested PLL Configurations

| Conf<br>No. <sup>1</sup>         | SPMF | CORE<br>PLL | CEPMF | CEPDF | Input<br>Clock Freq<br>(MHz) | CSB Freq<br>(MHz) | Core Freq<br>(MHz) | QUICC<br>Engine<br>Freq (MHz) | 400<br>(MHz) | 533<br>(MHz) | 667<br>(MHz) |

|----------------------------------|------|-------------|-------|-------|------------------------------|-------------------|--------------------|-------------------------------|--------------|--------------|--------------|

| c5                               | æ    | æ           | 10000 | 0     | 33                           | —                 | —                  | 533                           | _            | 8            | 8            |

| c6                               | æ    | æ           | 10001 | 0     | 33                           | —                 | —                  | 566                           | _            | —            | 8            |

| 66 MHz CLKIN/PCI_SYNC_IN Options |      |             |       |       |                              |                   |                    |                               |              |              |              |

| s1h                              | 0011 | 0000110     | æ     | æ     | 66                           | 200               | 400                | —                             | ~            | 8            | 8            |

| s2h                              | 0011 | 0000101     | æ     | æ     | 66                           | 200               | 500                | _                             | _            | 8            | 8            |

| s3h                              | 0011 | 0000110     | æ     | æ     | 66                           | 200               | 600                | _                             | _            | —            | 8            |

| s4h                              | 0100 | 0000011     | æ     | æ     | 66                           | 266               | 400                | _                             | 8            | ∞            | 8            |

| s5h                              | 0100 | 0000100     | æ     | æ     | 66                           | 266               | 533                | _                             | _            | ∞            | 8            |

| s6h                              | 0100 | 0000101     | æ     | æ     | 66                           | 266               | 667                | _                             | _            | —            | 8            |

| s7h                              | 0101 | 0000010     | æ     | æ     | 66                           | 333               | 333                | _                             | 8            | ∞            | 8            |

| s8h                              | 0101 | 0000011     | æ     | æ     | 66                           | 333               | 500                | _                             | _            | ∞            | 8            |

| s9h                              | 0101 | 0000100     | æ     | æ     | 66                           | 333               | 667                | _                             |              | —            | 8            |

| c1h                              | æ    | æ           | 00101 | 0     | 66                           | —                 | —                  | 333                           | 8            | 8            | 8            |

| c2h                              | æ    | æ           | 00110 | 0     | 66                           | —                 | _                  | 400                           | 8            | 8            | 8            |

| c3h                              | æ    | æ           | 00111 | 0     | 66                           | —                 | _                  | 466                           |              | 8            | 8            |

| c4h                              | æ    | æ           | 01000 | 0     | 66                           | —                 | _                  | 533                           | _            | 8            | 8            |

| c5h                              | æ    | æ           | 01001 | 0     | 66                           |                   |                    | 600                           | _            |              | 8            |

Table 76. Suggested PLL Configurations (continued)

Note:

1. The Conf No. consist of prefix, an index and a postfix. The prefix "s" and "c" stands for "syset" and "ce" respectively. The postfix "h" stands for "high input clock." The index is a serial number.

The following steps describe how to use above table. See Example 1.

- 2. Choose the up or down sections in the table according to input clock rate 33 MHz or 66 MHz.

- 3. Select a suitable CSB and core clock rates from Table 76. Copy the SPMF and CORE PLL configuration bits.

- 4. Select a suitable QUICC Engine block clock rate from Table 76. Copy the CEPMF and CEPDF configuration bits.

- 5. Insert the chosen SPMF, COREPLL, CEPMF and CEPDF to the RCWL fields, respectively.