# E·XFL

### NXP USA Inc. - MPC8360VVAJDG Datasheet

#### Welcome to E-XFL.COM

### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | PowerPC e300                                                          |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 533MHz                                                                |

| Co-Processors/DSP               | Communications; QUICC Engine                                          |

| RAM Controllers                 | DDR, DDR2                                                             |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100/1000Mbps (1)                                                   |

| SATA                            | -                                                                     |

| USB                             | USB 1.x (1)                                                           |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                      |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | -                                                                     |

| Package / Case                  | 740-LBGA                                                              |

| Supplier Device Package         | 740-TBGA (37.5x37.5)                                                  |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8360vvajdg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

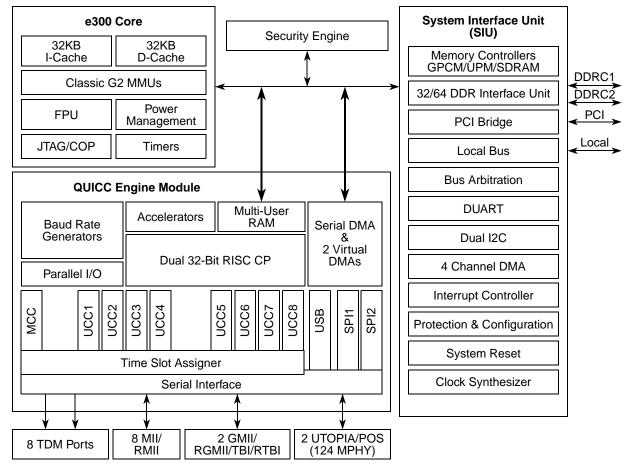

wide range of protocols including ATM, Ethernet, HDLC, and POS. The QUICC Engine module's enhanced interworking eases the transition and reduces investment costs from ATM to IP based systems. The other major features include a dual DDR SDRAM memory controller for the MPC8360E, which allows equipment providers to partition system parameters and data in an extremely efficient way, such as using one 32-bit DDR memory controller for control plane processing and the other for data plane processing. The MPC8358E has a single DDR SDRAM memory controller. The MPC8360E/58E also offers a 32-bit PCI controller, a flexible local bus, and a dedicated security engine.

This figure shows the MPC8360Eblock diagram.

Figure 1. MPC8360E Block Diagram

- Programmable highest priority request

- Four groups of interrupts with programmable priority

- External and internal interrupts directed to communication processor

- Redirects interrupts to external INTA pin when in core disable mode

- Unique vector number for each interrupt source

- Dual industry-standard I<sup>2</sup>C interfaces

- Two-wire interface

- Multiple master support

- Master or slave I<sup>2</sup>C mode support

- On-chip digital filtering rejects spikes on the bus

- System initialization data is optionally loaded from I<sup>2</sup>C-1 EPROM by boot sequencer embedded hardware

- DMA controller

- Four independent virtual channels

- Concurrent execution across multiple channels with programmable bandwidth control

- All channels accessible by local core and remote PCI masters

- Misaligned transfer capability

- Data chaining and direct mode

- Interrupt on completed segment and chain

- DMA external handshake signals: DMA\_DREQ[0:3]/DMA\_DACK[0:3]/DMA\_DONE[0:3]. There is one set for each DMA channel. The pins are multiplexed to the parallel IO pins with other QE functions.

- DUART

- Two 4-wire interfaces (RxD, TxD, RTS, CTS)

- Programming model compatible with the original 16450 UART and the PC16550D

- System timers

- Periodic interrupt timer

- Real-time clock

- Software watchdog timer

- Eight general-purpose timers

- IEEE Std. 1149.1<sup>™</sup>-compliant, JTAG boundary scan

- Integrated PCI bus and SDRAM clock generation

## 2 Electrical Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the MPC8360E/58E. The device is currently targeted to these specifications. Some of these specifications are independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer design specifications.

### DDR and DDR2 SDRAM AC Electrical Characteristics

| Parameter/Condition                                     | Symbol            | Min                      | Мах                      | Unit | Notes |

|---------------------------------------------------------|-------------------|--------------------------|--------------------------|------|-------|

| Input high voltage                                      | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.18 | GV <sub>DD</sub> + 0.3   | V    |       |

| Input low voltage                                       | V <sub>IL</sub>   | -0.3                     | MV <sub>REF</sub> – 0.18 | V    | _     |

| Output leakage current                                  | I <sub>OZ</sub>   | —                        | ±10                      | μA   | 4     |

| Output high current (V <sub>OUT</sub> = 1.95 V)         | I <sub>ОН</sub>   | -15.2                    |                          | mA   | —     |

| Output low current (V <sub>OUT</sub> = 0.35 V)          | I <sub>OL</sub>   | 15.2                     | _                        | mA   | _     |

| MV <sub>REF</sub> input leakage current                 | I <sub>VREF</sub> | —                        | ±10                      | μA   | —     |

| Input current (0 V ≰⁄ <sub>IN</sub> ≤OV <sub>DD</sub> ) | I <sub>IN</sub>   | —                        | ±10                      | μA   | _     |

### Table 16. DDR SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 2.5 V (continued)

### Notes:

1.  $GV_{DD}$  is expected to be within 50 mV of the DRAM  $GV_{DD}$  at all times.

- 2.  $MV_{REF}$  is expected to be equal to  $0.5 \times GV_{DD}$ , and to track  $GV_{DD}$  DC variations as measured at the receiver. Peak-to-peak noise on  $MV_{REF}$  may not exceed ±2% of the DC value.

- 3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail should track variations in the DC level of MV<sub>REF</sub>.

- 4. Output leakage is measured with all outputs disabled, 0 V  $\leq$ V<sub>OUT</sub>  $\leq$ GV<sub>DD</sub>.

This table provides the DDR capacitance when  $GV_{DD}(typ) = 2.5$  V.

### Table 17. DDR SDRAM Capacitance for GV<sub>DD</sub>(typ) = 2.5 V

| Parameter/Condition                     | Symbol           | Min | Мах | Unit | Notes |

|-----------------------------------------|------------------|-----|-----|------|-------|

| Input/output capacitance: DQ, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1     |

| Delta input/output capacitance: DQ, DQS | C <sub>DIO</sub> | —   | 0.5 | pF   | 1     |

Note:

1. This parameter is sampled.  $GV_{DD}$  = 2.5 V ± 0.125 V, f = 1 MHz, T<sub>A</sub> = 25°C, V<sub>OUT</sub> =  $GV_{DD}/2$ , V<sub>OUT</sub> (peak-to-peak) = 0.2 V.

## 6.2 DDR and DDR2 SDRAM AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR and DDR2 SDRAM interface.

### 6.2.1 DDR and DDR2 SDRAM Input AC Timing Specifications

This table provides the input AC timing specifications for the DDR2 SDRAM interface when  $GV_{DD}(typ) = 1.8 V$ .

### Table 18. DDR2 SDRAM Input AC Timing Specifications for GV<sub>DD</sub>(typ) = 1.8 V

At recommended operating conditions with  $GV_{DD}$  of 1.8 V ± 5%.

| Parameter             | Symbol          | Min                      | Мах                      | Unit | Notes |

|-----------------------|-----------------|--------------------------|--------------------------|------|-------|

| AC input low voltage  | V <sub>IL</sub> | _                        | MV <sub>REF</sub> – 0.25 | V    | —     |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.25 |                          | V    | —     |

### GMII, MII, RMII, TBI, RGMII, and RTBI AC Timing Specifications

Physical Layer Device Specification Version 1.2a (9/22/2000). The electrical characteristics for the MDIO and MDC are specified in Section 8.3, "Ethernet Management Interface Electrical Characteristics."

### 8.1.1 10/100/1000 Ethernet DC Electrical Characteristics

The electrical characteristics specified here apply to media independent interface (MII), reduced gigabit media independent interface (RGMII), reduced ten-bit interface (RTBI), reduced media independent interface (RMII) signals, management data input/output (MDIO) and management data clock (MDC).

The MII and RMII interfaces are defined for 3.3 V, while the RGMII and RTBI interfaces can be operated at 2.5 V. The RGMII and RTBI interfaces follow the *Reduced Gigabit Media-Independent Interface (RGMII) Specification Version 1.3*. The RMII interface follows the *RMII Consortium RMII Specification Version 1.2*.

Table 25. RGMII/RTBI, GMII, TBI, MII, and RMII DC Electrical Characteristics (when operating at 3.3 V)

| Parameter            | Symbol           | Conditions                             |                        | Min  | Max                    | Unit | Notes |

|----------------------|------------------|----------------------------------------|------------------------|------|------------------------|------|-------|

| Supply voltage 3.3 V | LV <sub>DD</sub> | —                                      |                        | 2.97 | 3.63                   | V    | 1     |

| Output high voltage  | V <sub>OH</sub>  | I <sub>OH</sub> = -4.0 mA              | LV <sub>DD</sub> = Min | 2.40 | LV <sub>DD</sub> + 0.3 | V    | _     |

| Output low voltage   | V <sub>OL</sub>  | I <sub>OL</sub> = 4.0 mA               | LV <sub>DD</sub> = Min | GND  | 0.50                   | V    | _     |

| Input high voltage   | V <sub>IH</sub>  | _                                      | —                      | 2.0  | LV <sub>DD</sub> + 0.3 | V    | _     |

| Input low voltage    | V <sub>IL</sub>  | _                                      | —                      | -0.3 | 0.90                   | V    | _     |

| Input current        | I <sub>IN</sub>  | 0 V ≤V <sub>IN</sub> ≤LV <sub>DD</sub> |                        | —    | ±10                    | μA   | _     |

### Note:

1. GMII/MII pins that are not needed for RGMII, RMII, or RTBI operation are powered by the OV<sub>DD</sub> supply.

| Table 26. RGMII/RTBI DC Electrical Characteristics | (when operating at 2.5 V) |

|----------------------------------------------------|---------------------------|

|----------------------------------------------------|---------------------------|

| Parameters           | Symbol           | Conditions                                      |                 | Min       | Max                    | Unit |

|----------------------|------------------|-------------------------------------------------|-----------------|-----------|------------------------|------|

| Supply voltage 2.5 V | LV <sub>DD</sub> | -                                               | _               | 2.37      | 2.63                   | V    |

| Output high voltage  | V <sub>OH</sub>  | $I_{OH} = -1.0 \text{ mA}$ $LV_{DD} = Min$      |                 | 2.00      | LV <sub>DD</sub> + 0.3 | V    |

| Output low voltage   | V <sub>OL</sub>  | I <sub>OL</sub> = 1.0 mA LV <sub>DD</sub> = Min |                 | GND – 0.3 | 0.40                   | V    |

| Input high voltage   | V <sub>IH</sub>  | — LV <sub>DD</sub> = Min                        |                 | 1.7       | LV <sub>DD</sub> + 0.3 | V    |

| Input low voltage    | V <sub>IL</sub>  | —                                               | $LV_{DD} = Min$ | -0.3      | 0.70                   | V    |

| Input current        | I <sub>IN</sub>  | 0 V ≤V <sub>IN</sub> ≤LV <sub>DD</sub>          |                 | —         | ±10                    | μA   |

## 8.2 GMII, MII, RMII, TBI, RGMII, and RTBI AC Timing Specifications

The AC timing specifications for GMII, MII, TBI, RGMII, and RTBI are presented in this section.

### 8.2.1 GMII Timing Specifications

This sections describe the GMII transmit and receive AC timing specifications.

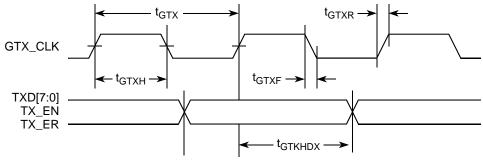

### 8.2.1.1 GMII Transmit AC Timing Specifications

This table provides the GMII transmit AC timing specifications.

### Table 27. GMII Transmit AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/OV_{DD}$  of 3.3 V ± 10%.

| Parameter/Condition                                                  | Symbol <sup>1</sup>                        | Min | Тур | Max     | Unit | Notes |

|----------------------------------------------------------------------|--------------------------------------------|-----|-----|---------|------|-------|

| GTX_CLK clock period                                                 | t <sub>GTX</sub>                           | —   | 8.0 | _       | ns   | —     |

| GTX_CLK duty cycle                                                   | t <sub>GTXH/tGTX</sub>                     | 40  | —   | 60      | %    | —     |

| GTX_CLK to GMII data TXD[7:0], TX_ER, TX_EN delay                    | <sup>t</sup> GTKHDX<br><sup>t</sup> GTKHDV | 0.5 | _   | <br>5.0 | ns   | 3     |

| GTX_CLK clock rise time, (20% to 80%)                                | t <sub>GTXR</sub>                          | —   | —   | 1.0     | ns   | —     |

| GTX_CLK clock fall time, (80% to 20%)                                | t <sub>GTXF</sub>                          | —   | —   | 1.0     | ns   | —     |

| GTX_CLK125 clock period                                              | t <sub>G125</sub>                          | —   | 8.0 | —       | ns   | 2     |

| GTX_CLK125 reference clock duty cycle measured at LV <sub>DD/2</sub> | t <sub>G125H</sub> /t <sub>G125</sub>      | 45  | —   | 55      | %    | 2     |

Notes:

- 1. The symbols used for timing specifications follow the pattern t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>GTKHDV</sub> symbolizes GMII transmit timing (GT) with respect to the t<sub>GTX</sub> clock reference (K) going to the high state (H) relative to the time date input signals (D) reaching the valid state (V) to state or setup time. Also, t<sub>GTKHDX</sub> symbolizes GMII transmit timing (GT) with respect to the t<sub>GTX</sub> clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GTX</sub> represents the GMII(G) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- 2. This symbol is used to represent the external GTX\_CLK125 signal and does not follow the original symbol naming convention.

- In rev. 2.0 silicon, due to errata, t<sub>GTKHDX</sub> minimum and t<sub>GTKHDV</sub> maximum are not supported when the GTX\_CLK is selected. Refer to Errata QE\_ENET18 in Chip Errata for the MPC8360E, Rev. 1.

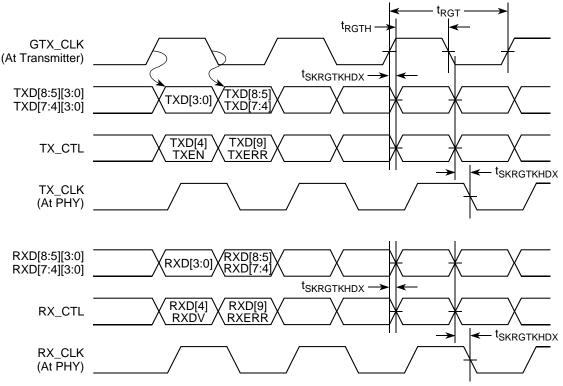

This figure shows the GMII transmit AC timing diagram.

Figure 10. GMII Transmit AC Timing Diagram

GMII, MII, RMII, TBI, RGMII, and RTBI AC Timing Specifications

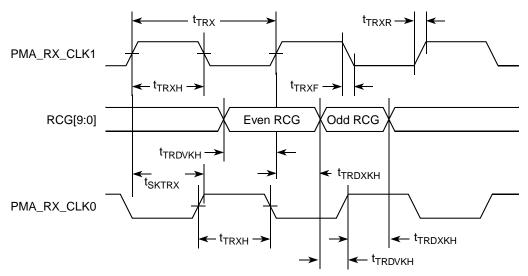

### 8.2.4.2 TBI Receive AC Timing Specifications

This table provides the TBI receive AC timing specifications.

### Table 34. TBI Receive AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/OV_{DD}$  of 3.3 V ± 10%.

| Parameter/Condition                                    | Symbol <sup>1</sup>                 | Min | Тур  | Мах | Unit | Notes |

|--------------------------------------------------------|-------------------------------------|-----|------|-----|------|-------|

| PMA_RX_CLK clock period                                | t <sub>TRX</sub>                    | _   | 16.0 | _   | ns   | —     |

| PMA_RX_CLK skew                                        | t <sub>SKTRX</sub>                  | 7.5 | —    | 8.5 | ns   | —     |

| RX_CLK duty cycle                                      | t <sub>TRXH</sub> /t <sub>TRX</sub> | 40  | —    | 60  | %    | —     |

| RCG[9:0] setup time to rising PMA_RX_CLK               | t <sub>TRDVKH</sub>                 | 2.5 | —    | _   | ns   | 2     |

| RCG[9:0] hold time to rising PMA_RX_CLK                | t <sub>TRDXKH</sub>                 | 1.0 | —    | _   | ns   | 2     |

| RX_CLK clock rise time, $V_{IL}(min)$ to $V_{IH}(max)$ | t <sub>TRXR</sub>                   | 0.7 | —    | 2.4 | ns   | —     |

| RX_CLK clock fall time, $V_{IH}(max)$ to $V_{IL}(min)$ | t <sub>TRXF</sub>                   | 0.7 | —    | 2.4 | ns   | _     |

Notes:

- 1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>TRDVKH</sub> symbolizes TBI receive timing (TR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>TRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>TRDXKH</sub> symbolizes TBI receive timing (TR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>TRX</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>TRX</sub> represents the TBI (T) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall). For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (TRX).</sub>

- 2. Setup and hold time of even numbered RCG are measured from riding edge of PMA\_RX\_CLK1. Setup and hold time of odd numbered RCG are measured from riding edge of PMA\_RX\_CLK0.

This figure shows the TBI receive AC timing diagram.

Figure 19. TBI Receive AC Timing Diagram

### **Ethernet Management Interface Electrical Characteristics**

This figure shows the RGMII and RTBI AC timing and multiplexing diagrams.

Figure 20. RGMII and RTBI AC Timing and Multiplexing Diagrams

### 8.3 Ethernet Management Interface Electrical Characteristics

The electrical characteristics specified here apply to MII management interface signals MDIO (management data input/output) and MDC (management data clock). The electrical characteristics for GMII, RGMII, TBI, and RTBI are specified in Section 8.1, "Three-Speed Ethernet Controller (10/100/1000 Mbps)— GMII/MII/RMII/TBI/RGMII/RTBI Electrical Characteristics."

### 8.3.1 MII Management DC Electrical Characteristics

The MDC and MDIO are defined to operate at a supply voltage of 3.3 V. The DC electrical characteristics for MDIO and MDC are provided in this table.

| Parameter              | Symbol           | Conditions                             |                        | Min  | Мах                    | Unit |

|------------------------|------------------|----------------------------------------|------------------------|------|------------------------|------|

| Supply voltage (3.3 V) | OV <sub>DD</sub> | —                                      |                        | 2.97 | 3.63                   | V    |

| Output high voltage    | V <sub>OH</sub>  | I <sub>OH</sub> = -1.0 mA              | $OV_{DD} = Min$        | 2.10 | OV <sub>DD</sub> + 0.3 | V    |

| Output low voltage     | V <sub>OL</sub>  | I <sub>OL</sub> = 1.0 mA               | OV <sub>DD</sub> = Min | GND  | 0.50                   | V    |

| Input high voltage     | V <sub>IH</sub>  | -                                      |                        |      | _                      | V    |

| Input low voltage      | V <sub>IL</sub>  | —                                      |                        | _    | 0.80                   | V    |

| Input current          | I <sub>IN</sub>  | 0 V ≤V <sub>IN</sub> ≤OV <sub>DD</sub> |                        | _    | ±10                    | μA   |

| able 36. MII Management DC Electrical Characteristics When Powered at 3.3 V |

|-----------------------------------------------------------------------------|

|-----------------------------------------------------------------------------|

| Parameter                                                   | Symbol <sup>1</sup>  | Min | Мах | Unit | Notes |

|-------------------------------------------------------------|----------------------|-----|-----|------|-------|

| LUPWAIT input hold from local bus clock                     | t <sub>LBIXKH2</sub> | 1.0 | _   | ns   | 3, 4  |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT1</sub> | 1.5 |     | ns   | 5     |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT2</sub> | 3.0 |     | ns   | 6     |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT3</sub> | 2.5 |     | ns   | 7     |

| Local bus clock to LALE rise                                | t <sub>LBKHLR</sub>  | —   | 4.5 | ns   | _     |

| Local bus clock to output valid (except LAD/LDP and LALE)   | t <sub>LBKHOV1</sub> | —   | 4.5 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                   | t <sub>LBKHOV2</sub> | —   | 4.5 | ns   | 3     |

| Local bus clock to address valid for LAD                    | t <sub>LBKHOV3</sub> | —   | 4.5 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)  | t <sub>LBKHOX1</sub> | 1.0 | _   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                | t <sub>LBKHOX2</sub> | 1.0 | _   | ns   | 3     |

| Local bus clock to output high impedance for LAD/LDP        | t <sub>LBKHOZ</sub>  | —   | 3.8 | ns   | 8     |

### Table 40. Local Bus General Timing Parameters—DLL Enabled (continued)

### Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the output (O) going invalid (X) or output hold time.

</sub>

- 2. All timings are in reference to rising edge of LSYNC\_IN.

- 3. All signals are measured from  $OV_{DD}/2$  of the rising edge of LSYNC\_IN to  $0.4 \times OV_{DD}$  of the signal in question for 3.3-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. t<sub>LBOTOT1</sub> should be used when RCWH[LALE] is not set and when the load on LALE output pin is at least 10 pF less than the load on LAD output pins.

- t<sub>LBOTOT2</sub> should be used when RCWH[LALE] is set and when the load on LALE output pin is at least 10 pF less than the load on LAD output pins.

- 7. t<sub>LBOTOT3</sub> should be used when RCWH[LALE] is set and when the load on LALE output pin equals to the load on LAD output pins.

- 8. For purposes of active/float timing measurements, the Hi-Z or off-state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

This table describes the general timing parameters of the local bus interface of the device.

### Table 41. Local Bus General Timing Parameters—DLL Bypass Mode<sup>9</sup>

| Parameter                                                   | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|-------------------------------------------------------------|----------------------|-----|-----|------|-------|

| Local bus cycle time                                        | t <sub>LBK</sub>     | 15  | —   | ns   | 2     |

| Input setup to local bus clock                              | t <sub>LBIVKH</sub>  | 7   | —   | ns   | 3, 4  |

| Input hold from local bus clock                             | t <sub>LBIXKH</sub>  | 1.0 | —   | ns   | 3, 4  |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT1</sub> | 1.5 | —   | ns   | 5     |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT2</sub> | 3   | —   | ns   | 6     |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT3</sub> | 2.5 | —   | ns   | 7     |

### Local Bus AC Electrical Specifications

| Parameter                                            | Symbol <sup>1</sup> | Min | Max | Unit | Notes |

|------------------------------------------------------|---------------------|-----|-----|------|-------|

| Local bus clock to output valid                      | t <sub>LBKHOV</sub> | —   | 3   | ns   | 3     |

| Local bus clock to output high impedance for LAD/LDP | t <sub>LBKHOZ</sub> | —   | 4   | ns   | 8     |

### Table 41. Local Bus General Timing Parameters—DLL Bypass Mode<sup>9</sup> (continued)

Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the to the output (O) going invalid (X) or output hold time.

</sub>

- 2. All timings are in reference to falling edge of LCLK0 (for all outputs and for LGTA and LUPWAIT inputs) or rising edge of LCLK0 (for all other inputs).

- 3. All signals are measured from OV<sub>DD</sub>/2 of the rising/falling edge of LCLK0 to 0.4 × OV<sub>DD</sub> of the signal in question for 3.3-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. t<sub>LBOTOT1</sub> should be used when RCWH[LALE] is not set and when the load on LALE output pin is at least 10 pF less than the load on LAD output pins.

- t<sub>LBOTOT2</sub> should be used when RCWH[LALE] is set and when the load on LALE output pin is at least 10 pF less than the load on LAD output pins.

- 7. t<sub>LBOTOT3</sub> should be used when RCWH[LALE] is set and when the load on LALE output pin equals to the load on LAD output pins.

- 8. For purposes of active/float timing measurements, the Hi-Z or off-state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 9. DLL bypass mode is not recommended for use at frequencies above 66 MHz.

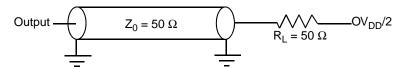

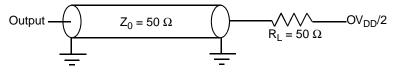

This figure provides the AC test load for the local bus.

Figure 22. Local Bus C Test Load

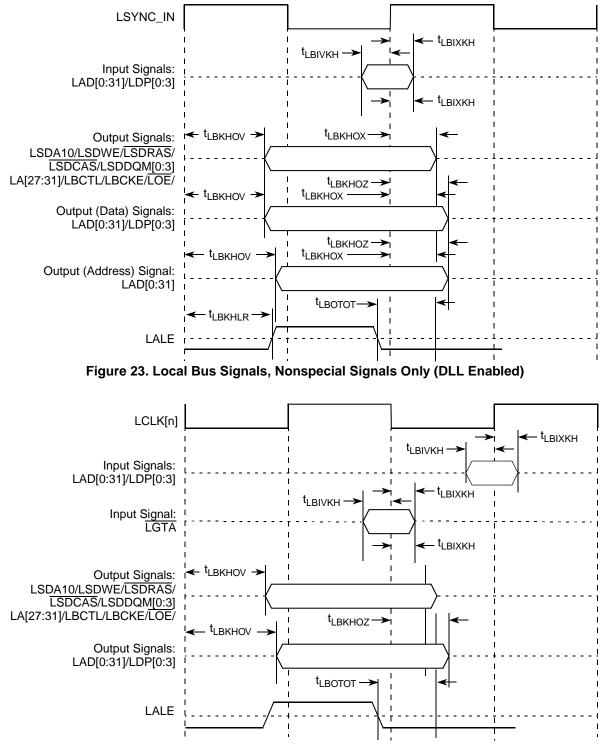

These figures show the local bus signals.

Figure 24. Local Bus Signals, Nonspecial Signals Only (DLL Bypass Mode)

**IPIC AC Timing Specifications**

## 15.2 IPIC AC Timing Specifications

This table provides the IPIC input and output AC timing specifications.

### Table 54. IPIC Input AC Timing Specifications<sup>1</sup>

| Characteristic                  | Symbol <sup>2</sup> | Min | Unit |

|---------------------------------|---------------------|-----|------|

| IPIC inputs—minimum pulse width | t <sub>PIWID</sub>  | 20  | ns   |

### Notes:

1. Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of CLKIN. Timings are measured at the pin.

IPIC inputs and outputs are asynchronous to any visible clock. IPIC outputs should be synchronized before use by any

external synchronous logic. IPIC inputs are required to be valid for at least t<sub>PIWID</sub> ns to ensure proper operation when

working in edge triggered mode.

## 16 SPI

This section describes the DC and AC electrical specifications for the SPI of the MPC8360E/58E.

## 16.1 SPI DC Electrical Characteristics

This table provides the DC electrical characteristics for the device SPI.

### Table 55. SPI DC Electrical Characteristics

| Characteristic      | Symbol          | Condition                              | Min  | Max                    | Unit |

|---------------------|-----------------|----------------------------------------|------|------------------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -6.0 mA              | 2.4  | _                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 6.0 mA               | —    | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA               | —    | 0.4                    | V    |

| Input high voltage  | V <sub>IH</sub> | —                                      | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                                      | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | 0 V ≤V <sub>IN</sub> ≤OV <sub>DD</sub> | —    | ±10                    | μA   |

## 16.2 SPI AC Timing Specifications

This table and provide the SPI input and output AC timing specifications.

Table 56. SPI AC Timing Specifications<sup>1</sup>

| Characteristic                                           | Symbol <sup>2</sup>                        | Min | Max   | Unit |

|----------------------------------------------------------|--------------------------------------------|-----|-------|------|

| SPI outputs—Master mode (internal clock) delay           | t <sub>NIKHOX</sub><br>t <sub>NIKHOV</sub> | 0.3 | 8     | ns   |

| SPI outputs—Slave mode (external clock) delay            | t <sub>NEKHOX</sub><br>t <sub>NEKHOV</sub> | 2   | <br>8 | ns   |

| SPI inputs—Master mode (internal clock) input setup time | t <sub>NIIVKH</sub>                        | 8   | —     | ns   |

| SPI inputs—Master mode (internal clock) input hold time  | t <sub>NIIXKH</sub>                        | 0   | —     | ns   |

| SPI inputs—Slave mode (external clock) input setup time  | t <sub>NEIVKH</sub>                        | 4   |       | ns   |

**TDM/SI DC Electrical Characteristics**

## 17 TDM/SI

This section describes the DC and AC electrical specifications for the time-division-multiplexed and serial interface of the MPC8360E/58E.

## 17.1 TDM/SI DC Electrical Characteristics

This table provides the DC electrical characteristics for the device TDM/SI.

Table 57. TDM/SI DC Electrical Characteristics

| Characteristic      | Symbol          | Condition                              | Min  | Мах                    | Unit |

|---------------------|-----------------|----------------------------------------|------|------------------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -2.0 mA              | 2.4  | _                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA               | _    | 0.5                    | V    |

| Input high voltage  | V <sub>IH</sub> | _                                      | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | _                                      | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | 0 V ≤V <sub>IN</sub> ≤OV <sub>DD</sub> | —    | ±10                    | μA   |

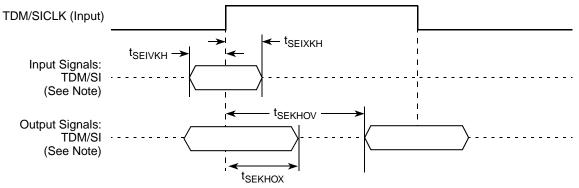

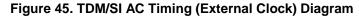

## 17.2 TDM/SI AC Timing Specifications

This table provides the TDM/SI input and output AC timing specifications.

| Table 58. | TDM/SI | AC | Timina                                | S | pecifications <sup>1</sup> | l |

|-----------|--------|----|---------------------------------------|---|----------------------------|---|

|           |        |    | · · · · · · · · · · · · · · · · · · · | - | o o o ni o a no no         |   |

| Characteristic                                | Symbol <sup>2</sup> | Min | Max <sup>3</sup> | Unit |

|-----------------------------------------------|---------------------|-----|------------------|------|

| TDM/SI outputs—External clock delay           | t <sub>SEKHOV</sub> | 2   | 10               | ns   |

| TDM/SI outputs—External clock high impedance  | t <sub>SEKHOX</sub> | 2   | 10               | ns   |

| TDM/SI inputs—External clock input setup time | t <sub>SEIVKH</sub> | 5   | —                | ns   |

| TDM/SI inputs—External clock input hold time  | t <sub>SEIXKH</sub> | 2   | —                | ns   |

Notes:

- 1. Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are measured at the pin.

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>SEKHOX</sub> symbolizes the TDM/SI outputs external timing (SE) for the time t<sub>TDM/SI</sub> memory clock reference (K) goes from the high state (H) until outputs (O) are invalid (X).

</sub>

- 3. Timings are measured from the positive or negative edge of the clock, according to SIxMR [CE] and SITXCEI[TXCEIx]. Refer *MPC8360E Integrated Communications Processor Reference Manual* for more details.

This figure provides the AC test load for the TDM/SI.

Figure 44. TDM/SI AC Test Load

Figure 45 represents the AC timing from Table 56. Note that although the specifications generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge is the active edge.

This figure shows the TDM/SI timing with external clock.

Note: The clock edge is selectable on TDM/SI

## 17.3 UTOPIA/POS

This section describes the DC and AC electrical specifications for the UTOPIA/POS of the MPC8360E/58E.

## **17.4 UTOPIA/POS DC Electrical Characteristics**

This table provides the DC electrical characteristics for the device UTOPIA.

Table 59. UTOPIA DC Electrical Characteristics

| Characteristic      | Symbol          | Condition                              | Min  | Мах                    | Unit |

|---------------------|-----------------|----------------------------------------|------|------------------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA              | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA               | —    | 0.5                    | V    |

| Input high voltage  | V <sub>IH</sub> | —                                      | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                                      | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | 0 V ≤V <sub>IN</sub> ≤OV <sub>DD</sub> | —    | ±10                    | μA   |

### 17.5 UTOPIA/POS AC Timing Specifications

This table provides the UTOPIA input and output AC timing specifications.

Table 60. UTOPIA AC Timing Specifications<sup>1</sup>

| Characteristic                                | Symbol <sup>2</sup> | Min | Max  | Unit | Notes |

|-----------------------------------------------|---------------------|-----|------|------|-------|

| UTOPIA outputs—Internal clock delay           | t <sub>UIKHOV</sub> | 0   | 11.5 | ns   | —     |

| UTOPIA outputs—External clock delay           | t <sub>UEKHOV</sub> | 1   | 11.6 | ns   | _     |

| UTOPIA outputs—Internal clock high impedance  | t <sub>UIKHOX</sub> | 0   | 8.0  | ns   | _     |

| UTOPIA outputs—External clock high impedance  | t <sub>UEKHOX</sub> | 1   | 10.0 | ns   | _     |

| UTOPIA inputs—Internal clock input setup time | t <sub>UIIVKH</sub> | 6   | _    | ns   | _     |

| UTOPIA inputs—External clock input setup time | t <sub>UEIVKH</sub> | 4   | _    | ns   | 3     |

# NP

## 20.3 Pinout Listings

Refer to AN3097, "MPC8360/MPC8358E PowerQUICC Design Checklist," for proper pin termination and usage.

This table shows the pin list of the MPC8360E TBGA package.

| Signal                                        | Package Pin Number                                                                                                                                                                                         | Pin Type | Power<br>Supply  | Notes |  |  |  |  |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|--|--|--|--|

| Primary DDR SDRAM Memory Controller Interface |                                                                                                                                                                                                            |          |                  |       |  |  |  |  |

| MEMC1_MDQ[0:31]                               | AJ34, AK33, AL33, AL35, AJ33, AK34, AK32,<br>AM36, AN37, AN35, AR34, AT34, AP37, AP36,<br>AR36, AT35, AP34, AR32, AP32, AM31, AN33,<br>AM34, AM33, AM30, AP31, AM27, AR30, AT32,<br>AN29, AP29, AN27, AR29 | I/O      | GV <sub>DD</sub> | _     |  |  |  |  |

| MEMC1_MDQ[32:63]/<br>MEMC2_MDQ[0:31]          | AN8, AN7, AM8, AM6, AP9, AN9, AT7, AP7, AU6,<br>AP6, AR4, AR3, AT6, AT5, AR5, AT3, AP4, AM5,<br>AP3, AN3, AN5, AL5, AN4, AM2, AL2, AH5, AK3,<br>AJ2, AJ3, AH4, AK4, AH3                                    | I/O      | GV <sub>DD</sub> | _     |  |  |  |  |

| MEMC1_MECC[0:4]/<br>MSRCID[0:4]               | AP24, AN22, AM19, AN19, AM24                                                                                                                                                                               | I/O      | GV <sub>DD</sub> | -     |  |  |  |  |

| MEMC1_MECC[5]/<br>MDVAL                       | AM23                                                                                                                                                                                                       | I/O      | GV <sub>DD</sub> | _     |  |  |  |  |

| MEMC1_MECC[6:7]                               | AM22, AN18                                                                                                                                                                                                 | I/O      | GV <sub>DD</sub> | —     |  |  |  |  |

| MEMC1_MDM[0:3]                                | AL36, AN34, AP33, AN28                                                                                                                                                                                     | 0        | GV <sub>DD</sub> | —     |  |  |  |  |

| MEMC1_MDM[4:7]/<br>MEMC2_MDM[0:3]             | AT9, AU4, AM3, AJ6                                                                                                                                                                                         | 0        | GV <sub>DD</sub> | _     |  |  |  |  |

| MEMC1_MDM[8]                                  | AP27                                                                                                                                                                                                       | 0        | GV <sub>DD</sub> | —     |  |  |  |  |

| MEMC1_MDQS[0:3]                               | AK35, AP35, AN31, AM26                                                                                                                                                                                     | I/O      | GV <sub>DD</sub> | —     |  |  |  |  |

| MEMC1_MDQS[4:7]/<br>MEMC2_MDQS[0:3]           | AT8, AU3, AL4, AJ5                                                                                                                                                                                         | I/O      | GV <sub>DD</sub> | _     |  |  |  |  |

| MEMC1_MDQS[8]                                 | AP26                                                                                                                                                                                                       | I/O      | GV <sub>DD</sub> | —     |  |  |  |  |

| MEMC1_MBA[0:1]                                | AU29, AU30                                                                                                                                                                                                 | 0        | GV <sub>DD</sub> |       |  |  |  |  |

| MEMC1_MBA[2]                                  | AT30                                                                                                                                                                                                       | 0        | GV <sub>DD</sub> | —     |  |  |  |  |

| MEMC1_MA[0:14]                                | AU21, AP22, AP21, AT21, AU25, AU26, AT23,<br>AR26, AU24, AR23, AR28, AU23, AR22, AU20,<br>AR18                                                                                                             | 0        | GV <sub>DD</sub> | —     |  |  |  |  |

| MEMC1_MODT[0:1]                               | AG33, AJ36                                                                                                                                                                                                 | 0        | GV <sub>DD</sub> | 6     |  |  |  |  |

| MEMC1_MODT[2:3]/<br>MEMC2_MODT[0:1]           | AT1, AK2                                                                                                                                                                                                   | 0        | GV <sub>DD</sub> | 6     |  |  |  |  |

| MEMC1_MWE                                     | AT26                                                                                                                                                                                                       | 0        | GV <sub>DD</sub> | —     |  |  |  |  |

| MEMC1_MRAS                                    | AT29                                                                                                                                                                                                       | 0        | GV <sub>DD</sub> | —     |  |  |  |  |

| MEMC1_MCAS                                    | AT24                                                                                                                                                                                                       | 0        | GV <sub>DD</sub> | —     |  |  |  |  |

| MEMC1_MCS[0:1]                                | AU27, AT27                                                                                                                                                                                                 | 0        | GV <sub>DD</sub> | —     |  |  |  |  |

| MEMC1_MCS[2:3]/<br>MEMC2_MCS[0:1]             | AU8, AU7                                                                                                                                                                                                   | 0        | GV <sub>DD</sub> | _     |  |  |  |  |

### Table 66. MPC8360E TBGA Pinout Listing

### Table 67. MPC8358E TBGA Pinout Listing (continued)

| Signal                                         | Package Pin Number         | Pin Type | Power<br>Supply    | Notes |

|------------------------------------------------|----------------------------|----------|--------------------|-------|

| IRQ[4:5]                                       | G33, G32                   | I/O      | OV <sub>DD</sub>   | —     |

| IRQ[6]/LCS[6]/CKSTOP_OUT                       | E35                        | I/O      | OV <sub>DD</sub>   | _     |

| IRQ[7]/LCS[7]/CKSTOP_IN                        | H36                        | I/O      | OV <sub>DD</sub>   | —     |

|                                                | DUART                      |          |                    |       |

| UART1_SOUT/M1SRCID[0]/<br>M2SRCID[0]/LSRCID[0] | E32                        | 0        | OV <sub>DD</sub>   | -     |

| UART1_SIN/M1SRCID[1]/<br>M2SRCID[1]/LSRCID[1]  | B34                        | I/O      | OV <sub>DD</sub>   | —     |

| UART1_CTS/M1SRCID[2]/<br>M2SRCID[2]/LSRCID[2]  | C34                        | I/O      | OV <sub>DD</sub>   | —     |

| UART1_RTS/M1SRCID[3]/<br>M2SRCID[3]/LSRCID[3]  | A35                        | 0        | OV <sub>DD</sub>   | —     |

|                                                | I <sup>2</sup> C Interface |          |                    |       |

| IIC1_SDA                                       | D34                        | I/O      | OV <sub>DD</sub>   | 2     |

| IIC1_SCL                                       | B35                        | I/O      | OV <sub>DD</sub>   | 2     |

| IIC2_SDA                                       | E33                        | I/O      | OV <sub>DD</sub>   | 2     |

| IIC2_SCL                                       | C35                        | I/O      | OV <sub>DD</sub>   | 2     |

|                                                | QUICC Engine               |          |                    |       |

| CE_PA[0]                                       | F8                         | I/O      | LV <sub>DD0</sub>  | _     |

| CE_PA[1:2]                                     | AH1, AG5                   | I/O      | OV <sub>DD</sub>   | _     |

| CE_PA[3:7]                                     | F6, D4, C3, E5, A3         | I/O      | LV <sub>DD</sub> 0 | —     |

| CE_PA[8]                                       | AG3                        | I/O      | OV <sub>DD</sub>   | _     |

| CE_PA[9:12]                                    | F7, B3, E6, B4             | I/O      | LV <sub>DD</sub> 0 |       |

| CE_PA[13:14]                                   | AG1, AF6                   | I/O      | OV <sub>DD</sub>   | —     |

| CE_PA[15]                                      | B2                         | I/O      | LV <sub>DD</sub> 0 |       |

| CE_PA[16]                                      | AF4                        | I/O      | OV <sub>DD</sub>   | _     |

| CE_PA[17:21]                                   | B16, A16, E17, A17, B17    | I/O      | LV <sub>DD</sub> 1 |       |

| CE_PA[22]                                      | AF3                        | I/O      | OV <sub>DD</sub>   | _     |

| CE_PA[23:26]                                   | C18, D18, E18, A18         | I/O      | LV <sub>DD</sub> 1 | —     |

| CE_PA[27:28]                                   | AF2, AE6                   | I/O      | OV <sub>DD</sub>   | —     |

| CE_PA[29]                                      | B19                        | I/O      | LV <sub>DD</sub> 1 | _     |

| CE_PA[30]                                      | AE5                        | I/O      | OV <sub>DD</sub>   | —     |

| CE_PA[31]                                      | F16                        | I/O      | LV <sub>DD</sub> 1 | —     |

### Table 67. MPC8358E TBGA Pinout Listing (continued)

| Signal             | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pin Type                                                        | Power<br>Supply    | Notes |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------|-------|

| PORESET            | L37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                               | OV <sub>DD</sub>   |       |

| HRESET             | L36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I/O                                                             | OV <sub>DD</sub>   | 1     |

| SRESET             | M33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I/O                                                             | OV <sub>DD</sub>   | 2     |

|                    | Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                 |                    |       |

| THERM0             | AP19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I                                                               | GV <sub>DD</sub>   | —     |

| THERM1             | AT31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I                                                               | GV <sub>DD</sub>   | —     |

|                    | Power and Ground Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                 |                    |       |

| AV <sub>DD</sub> 1 | K35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power for<br>LBIU DLL<br>(1.2 V)                                | AV <sub>DD</sub> 1 | _     |

| AV <sub>DD</sub> 2 | K36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power for<br>CE PLL<br>(1.2 V)                                  | AV <sub>DD</sub> 2 | _     |

| AV <sub>DD</sub> 5 | AM29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Power for<br>e300 PLL<br>(1.2 V)                                | AV <sub>DD</sub> 5 | _     |

| AV <sub>DD</sub> 6 | К37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power for<br>system<br>PLL (1.2 V)                              | AV <sub>DD</sub> 6 | _     |

| GND                | <ul> <li>A2, A8, A13, A19, A22, A25, A31, A33, A36, B7,<br/>B12, B24, B27, B30, C4, C6, C9, C15, C26, C32,<br/>D3, D8, D11, D14, D17, D19, D23, D27, E7, E13,<br/>E25, E30, E36, F4, F37, G34, H1, H5, H32, H33, J4,<br/>J32, J37, K1, L3, L5, L33, L34, M1, M34, M35, N37,<br/>P2, P5, P35, P36, R4, T3, U1, U5, U35, V37, W1,<br/>W4, W33, W36, Y34, AA3, AA5, AC3, AC32, AC35,<br/>AD1, AD37, AE4, AE34, AE36, AF33, AG4, AG6,<br/>AG32, AH35, AJ1, AJ4, AJ32, AJ35, AJ37, AK36,<br/>AL3, AL34, AM4, AN6, AN23, AN30, AP8, AP12,<br/>AP14, AP16, AP17, AP20, AP25, AR6, AR8, AR9,<br/>AR19, AR24, AR31, AR35, AR37, AT4, AT10, AT19,<br/>AT20, AT25, AU14, AU22, AU28, AU35</li> </ul> | _                                                               | _                  | -     |

| GV <sub>DD</sub>   | AD4, AE3, AF1, AF5, AF35, AF37, AG2, AG36,<br>AH33, AH34, AK5, AM1, AM35, AM37, AN2, AN10,<br>AN11, AN12, AN14, AN32, AN36, AP5, AP23,<br>AP28, AR1, AR7, AR10, AR12, AR21, AR25, AR27,<br>AR33, AT15, AT22, AT28, AT33, AU2, AU5, AU16,<br>AU31, AU36                                                                                                                                                                                                                                                                                                                                                                                                                                    | Power for<br>DDR<br>DRAM I/O<br>voltage<br>(2.5 or<br>1.8 V)    | GV <sub>DD</sub>   | _     |

| LV <sub>DD</sub> 0 | D5, D6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Power for<br>UCC1<br>Ethernet<br>interface<br>(2.5 V,<br>3.3 V) | LV <sub>DD</sub> 0 | _     |

Core PLL Configuration

## 21.2 Core PLL Configuration

RCWL[COREPLL] selects the ratio between the internal coherent system bus clock (*csb\_clk*) and the e300 core clock (*core\_clk*). This table shows the encodings for RCWL[COREPLL]. COREPLL values not listed in this table should be considered reserved.

| RCWL[COREPLL] |      | core_clk:csb_clk | VCO divider                                                       |                                                                   |  |

|---------------|------|------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|--|

| 0–1           | 2–5  | 6                | Ratio                                                             |                                                                   |  |

| nn            | 0000 | n                | PLL bypassed<br>(PLL off, <i>csb_clk</i><br>clocks core directly) | PLL bypassed<br>(PLL off, <i>csb_clk</i><br>clocks core directly) |  |

| 00            | 0001 | 0                | 1:1                                                               | ÷2                                                                |  |

| 01            | 0001 | 0                | 1:1                                                               | ÷4                                                                |  |

| 10            | 0001 | 0                | 1:1                                                               | ÷8                                                                |  |

| 11            | 0001 | 0                | 1:1                                                               | ÷8                                                                |  |

| 00            | 0001 | 1                | 1.5:1                                                             | ÷2                                                                |  |

| 01            | 0001 | 1                | 1.5:1                                                             | ÷4                                                                |  |

| 10            | 0001 | 1                | 1.5:1                                                             | ÷8                                                                |  |

| 11            | 0001 | 1                | 1.5:1                                                             | ÷8                                                                |  |

| 00            | 0010 | 0                | 2:1                                                               | ÷2                                                                |  |

| 01            | 0010 | 0                | 2:1                                                               | ÷4                                                                |  |

| 10            | 0010 | 0                | 2:1                                                               | ÷8                                                                |  |

| 11            | 0010 | 0                | 2:1                                                               | ÷8                                                                |  |

| 00            | 0010 | 1                | 2.5:1                                                             | ÷2                                                                |  |

| 01            | 0010 | 1                | 2.5:1                                                             | ÷4                                                                |  |

| 10            | 0010 | 1                | 2.5:1                                                             | ÷8                                                                |  |

| 11            | 0010 | 1                | 2.5:1                                                             | ÷8                                                                |  |

| 00            | 0011 | 0                | 3:1                                                               | ÷2                                                                |  |

| 01            | 0011 | 0                | 3:1                                                               | ÷4                                                                |  |

| 10            | 0011 | 0                | 3:1                                                               | ÷8                                                                |  |

| 11            | 0011 | 0                | 3:1                                                               | ÷8                                                                |  |

### Table 73. e300 Core PLL Configuration

### NOTE

Core VCO frequency = Core frequency  $\times$  VCO divider. The VCO divider (RCWL[COREPLL[0:1]]) must be set properly so that the core VCO frequency is in the range of 800–1800 MHz. Having a core frequency below the CSB frequency is not a possible option because the core frequency must be equal to or greater than the CSB frequency.

### **Thermal Management Information**

This table shows heat sinks and junction-to-ambient thermal resistance for TBGA package.

| Table 78. Heat Sinks and Junction-to-Ambient | Thermal Resistance of TBGA Package |

|----------------------------------------------|------------------------------------|

|----------------------------------------------|------------------------------------|

|                                                         |                    | 35	imes35 mm TBGA                         |  |

|---------------------------------------------------------|--------------------|-------------------------------------------|--|

| Heat Sink Assuming Thermal Grease                       | Airflow            | Junction-to-Ambient<br>Thermal Resistance |  |

| AAVID 30 × 30 × 9.4 mm pin fin                          | Natural convention | 10.7                                      |  |

| AAVID 30 × 30 × 9.4 mm pin fin                          | 1 m/s              | 6.2                                       |  |

| AAVID 30 × 30 × 9.4 mm pin fin                          | 2 m/s              | 5.3                                       |  |

| AAVID 31 × 35 × 23 mm pin fin                           | Natural convention | 8.1                                       |  |

| AAVID 31 × 35 × 23 mm pin fin                           | 1 m/s              | 4.4                                       |  |

| AAVID 31 × 35 × 23 mm pin fin                           | 2 m/s              | 3.7                                       |  |

| Wakefield, 53 × 53 × 25 mm pin fin                      | Natural convention | 5.4                                       |  |

| Wakefield, 53 × 53 × 25 mm pin fin                      | 1 m/s              | 3.2                                       |  |

| Wakefield, 53 × 53 × 25 mm pin fin                      | 2 m/s              | 2.4                                       |  |

| MEI, 75 x 85 x 12 no adjacent board, extrusion          | Natural convention | 6.4                                       |  |

| MEI, 75 x 85 x 12 no adjacent board, extrusion          | 1 m/s              | 3.8                                       |  |

| MEI, 75 x 85 x 12 no adjacent board, extrusion          | 2 m/s              | 2.5                                       |  |

| MEI, 75 x 85 x 12 mm, adjacent board, 40 mm side bypass | 1 m/s              | 2.8                                       |  |

Accurate thermal design requires thermal modeling of the application environment using computational fluid dynamics software which can model both the conduction cooling and the convection cooling of the air moving through the application. Simplified thermal models of the packages can be assembled using the junction-to-case and junction-to-board thermal resistances listed in the thermal resistance table. More detailed thermal models can be made available on request.

Heat sink vendors include the following:

| Aavid Thermalloy<br>80 Commercial St.<br>Concord, NH 03301<br>Internet: www.aavidthermalloy.com                              | 603-224-9988 |

|------------------------------------------------------------------------------------------------------------------------------|--------------|

| Alpha Novatech<br>473 Sapena Ct. #15<br>Santa Clara, CA 95054<br>Internet: www.alphanovatech.com                             | 408-749-7601 |

| International Electronic Research Corporation (IERC)<br>413 North Moss St.<br>Burbank, CA 91502<br>Internet: www.ctscorp.com | 818-842-7277 |

### 23.7 Pull-Up Resistor Requirements

The device requires high resistance pull-up resistors (10 k $\Omega$  is recommended) on open drain type pins including I<sup>2</sup>C pins, Ethernet Management MDIO pin, and EPIC interrupt pins.

For more information on required pull-up resistors and the connections required for the JTAG interface, see *MPC8360E/MPC8358E PowerQUICC Design Checklist* (AN3097).

## 24 Ordering Information

## 24.1 Part Numbers Fully Addressed by this Document

This table provides the Freescale part numbering nomenclature for the MPC8360E/58E. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. Additionally to the processor frequency, the part numbering scheme also includes an application modifier, which may specify special application conditions. Each part number also contains a revision code that refers to the die mask revision number.

| MPC                                  | nnnn               | е                                       | t                                                                            | рр                                  | aa                                                              | а                          | а                            | Α                       |

|--------------------------------------|--------------------|-----------------------------------------|------------------------------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------|----------------------------|------------------------------|-------------------------|

| Product<br>Code                      | Part<br>Identifier | Encryption<br>Acceleration              | Temperature<br>Range                                                         | Package <sup>2</sup>                | Processor<br>Frequency <sup>3</sup>                             | Platform<br>Frequency      | QUICC<br>Engine<br>Frequency | Die<br>Revision         |

| MPC                                  | 8358               | Blank = not<br>included<br>E = included | Blank = $0^{\circ}$ C<br>T <sub>A</sub> to $105^{\circ}$ C<br>T <sub>J</sub> | ZU = TBGA<br>VV = TBGA<br>(no lead) | e300 core speed<br>AD = 266 MHz<br>AG = 400 MHz                 | D = 266 MHz                | E = 300 MHz<br>G = 400 MHz   | A = rev. 2.1<br>silicon |

|                                      | 8360               |                                         | C= -40° C T <sub>A</sub><br>to 105° C T <sub>J</sub>                         | / <b>\</b>                          | e300 core speed<br>AG = 400 MHz<br>AJ = 533 MHz<br>AL = 667 MHz | D = 266 MHz<br>F = 333 MHz | G = 400 MHz<br>H = 500 MHz   | A = rev. 2.1<br>silicon |

| MPC<br>(rev. 2.0<br>silicon<br>only) | 8360               | Blank = not<br>included<br>E = included | 0° C T <sub>A</sub> to<br>70° C T <sub>J</sub>                               | ZU = TBGA<br>VV = TBGA<br>(no lead) | e300 core speed<br>AH = 500 MHz<br>AL = 667 MHz                 | F = 333 MHz                | G = 400 MHz<br>H = 500 MHz   | —                       |

### Table 80. Part Numbering Nomenclature<sup>1</sup>

### Notes:

1. Not all processor, platform, and QUICC Engine block frequency combinations are supported. For available frequency combinations, contact your local Freescale sales office or authorized distributor.

2. See Section 20, "Package and Pin Listings," for more information on available package types.

Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by part number specifications may support other maximum core frequencies.

This table shows the SVR settings by device and package type.

| Table 8 <sup>-</sup> | 1. SVR | Settings |

|----------------------|--------|----------|

|----------------------|--------|----------|

| Device   | Package | SVR<br>(Rev. 2.0) | SVR<br>(Rev. 2.1) |

|----------|---------|-------------------|-------------------|

| MPC8360E | TBGA    | 0x8048_0020       | 0x8048_0021       |

| MPC8360  | TBGA    | 0x8049_0020       | 0x8049_0021       |

### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center 1-800 441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.