# E·XFL

## NXP USA Inc. - MPC8360ZUAHFH Datasheet

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8360zuahfh |

|---------------------------------|-----------------------------------------------------------------------|

| Supplier Device Package         | 740-TBGA (37.5x37.5)                                                  |

| Package / Case                  | 740-LBGA                                                              |

| Security Features               |                                                                       |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                      |

| USB                             | USB 1.x (1)                                                           |

| SATA                            | · · · · · · · · · · · · · · · · · · ·                                 |

| Ethernet                        | 10/100/1000Mbps (1)                                                   |

| Display & Interface Controllers | · · · · · · · · · · · · · · · · · · ·                                 |

| Graphics Acceleration           | No                                                                    |

| RAM Controllers                 | DDR, DDR2                                                             |

| Co-Processors/DSP               | Communications; QUICC Engine                                          |

| Speed                           | 500MHz                                                                |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Core Processor                  | PowerPC e300                                                          |

| Product Status                  | Obsolete                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- DRAM chip configurations from 64 Mbits to 1 Gigabit with  $\times 8/\times 16$  data ports

- Full ECC support (when the MPC8360E is configured as 2×32-bit DDR memory controllers, both support ECC)

- Page mode support (up to 16 simultaneous open pages for DDR1, up to 32 simultaneous open pages for DDR2)

- Contiguous or discontiguous memory mapping

- Read-modify-write support

- Sleep mode support for self refresh SDRAM

- Supports auto refreshing

- Supports source clock mode

- On-the-fly power management using CKE

- Registered DIMM support

- 2.5-V SSTL2 compatible I/O for DDR1, 1.8-V SSTL2 compatible I/O for DDR2

- External driver impedance calibration

- On-die termination (ODT)

- PCI interface

- PCI Specification Revision 2.3 compatible

- Data bus widths:

- Single 32-bit data PCI interface that operates at up to 66 MHz

- PCI 3.3-V compatible (not 5-V compatible)

- PCI host bridge capabilities on both interfaces

- PCI agent mode supported on PCI interface

- Support for PCI-to-memory and memory-to-PCI streaming

- Memory prefetching of PCI read accesses and support for delayed read transactions

- Support for posting of processor-to-PCI and PCI-to-memory writes

- On-chip arbitration, supporting five masters on PCI

- Support for accesses to all PCI address spaces

- Parity support

- Selectable hardware-enforced coherency

- Address translation units for address mapping between host and peripheral

- Dual address cycle supported when the device is the target

- Internal configuration registers accessible from PCI

- Local bus controller (LBC)

- Multiplexed 32-bit address and data operating at up to 133 MHz

- Eight chip selects support eight external slaves

- Up to eight-beat burst transfers

- 32-, 16-, and 8-bit port sizes are controlled by an on-chip memory controller

- Three protocol engines available on a per chip select basis:

- General-purpose chip select machine (GPCM)

- Three user programmable machines (UPMs)

- Dedicated single data rate SDRAM controller

- Parity support

- Default boot ROM chip select with configurable bus width (8-, 16-, or 32-bit)

- Programmable interrupt controller (PIC)

- Functional and programming compatibility with the MPC8260 interrupt controller

- Support for 8 external and 35 internal discrete interrupt sources

- Support for one external (optional) and seven internal machine checkstop interrupt sources

# 6.1 DDR and DDR2 SDRAM DC Electrical Characteristics

This table provides the recommended operating conditions for the DDR2 SDRAM component(s) of the device when  $GV_{DD}(typ) = 1.8 \text{ V}.$

| Parameter/Condition                                     | Symbol            | Min                       | Мах                               | Unit | Notes |

|---------------------------------------------------------|-------------------|---------------------------|-----------------------------------|------|-------|

| I/O supply voltage                                      | GV <sub>DD</sub>  | 1.71                      | 1.89                              | V    | 1     |

| I/O reference voltage                                   | MV <sub>REF</sub> | $0.49 	imes GV_{DD}$      | $0.51 	imes \text{GV}_{	ext{DD}}$ | V    | 2     |

| I/O termination voltage                                 | V <sub>TT</sub>   | MV <sub>REF</sub> - 0.04  | MV <sub>REF</sub> + 0.04          | V    | 3     |

| Input high voltage                                      | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.125 | GV <sub>DD</sub> + 0.3            | V    | _     |

| Input low voltage                                       | V <sub>IL</sub>   | -0.3                      | MV <sub>REF</sub> – 0.125         | V    | _     |

| Output leakage current                                  | I <sub>OZ</sub>   | _                         | ±10                               | μA   | 4     |

| Output high current (V <sub>OUT</sub> = 1.420 V)        | I <sub>OH</sub>   | -13.4                     | —                                 | mA   | _     |

| Output low current (V <sub>OUT</sub> = 0.280 V)         | I <sub>OL</sub>   | 13.4                      | —                                 | mA   | _     |

| MV <sub>REF</sub> input leakage current                 | I <sub>VREF</sub> | _                         | ±10                               | μA   | _     |

| Input current (0 V ≛/ <sub>IN</sub> ≤OV <sub>DD</sub> ) | I <sub>IN</sub>   | _                         | ±10                               | μA   | _     |

### Table 14. DDR2 SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 1.8 V

### Notes:

1.  $GV_{DD}$  is expected to be within 50 mV of the DRAM  $GV_{DD}$  at all times.

MV<sub>REF</sub> is expected to equal 0.5 × GV<sub>DD</sub>, and to track GV<sub>DD</sub> DC variations as measured at the receiver. Peak-to-peak noise on MV<sub>REF</sub> cannot exceed ±2% of the DC value.

V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to equal MV<sub>REF</sub>. This rail should track variations in the DC level of MV<sub>REF</sub>.

4. Output leakage is measured with all outputs disabled, 0 V  $\leq$ V<sub>OUT</sub>  $\leq$ GV<sub>DD</sub>.

This table provides the DDR2 capacitance when  $GV_{DD}(typ) = 1.8$  V.

### Table 15. DDR2 SDRAM Capacitance for GV<sub>DD</sub>(typ)=1.8 V

| Parameter/Condition                          | Symbol           | Min | Max | Unit | Notes |

|----------------------------------------------|------------------|-----|-----|------|-------|

| Input/output capacitance: DQ, DQS, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1     |

| Delta input/output capacitance: DQ, DQS, DQS | C <sub>DIO</sub> | —   | 0.5 | pF   | 1     |

#### Note:

1. This parameter is sampled.  $GV_{DD} = 1.8 \text{ V} \pm 0.090 \text{ V}$ , f = 1 MHz, T<sub>A</sub> = 25°C,  $V_{OUT} = GV_{DD}/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

This table provides the recommended operating conditions for the DDR SDRAM component(s) of the device when  $GV_{DD}(typ) = 2.5 \text{ V}.$

### Table 16. DDR SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 2.5 V

| Parameter/Condition     | Symbol            | Min                      | Max                               | Unit | Notes |

|-------------------------|-------------------|--------------------------|-----------------------------------|------|-------|

| I/O supply voltage      | GV <sub>DD</sub>  | 2.375                    | 2.625                             | V    | 1     |

| I/O reference voltage   | MV <sub>REF</sub> | $0.49 	imes GV_{DD}$     | $0.51 	imes \text{GV}_{	ext{DD}}$ | V    | 2     |

| I/O termination voltage | V <sub>TT</sub>   | MV <sub>REF</sub> – 0.04 | MV <sub>REF</sub> + 0.04          | V    | 3     |

#### DDR and DDR2 SDRAM AC Electrical Characteristics

| Parameter/Condition                                     | Symbol            | Min                      | Мах                      | Unit | Notes |

|---------------------------------------------------------|-------------------|--------------------------|--------------------------|------|-------|

| Input high voltage                                      | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.18 | GV <sub>DD</sub> + 0.3   | V    |       |

| Input low voltage                                       | V <sub>IL</sub>   | -0.3                     | MV <sub>REF</sub> – 0.18 | V    | _     |

| Output leakage current                                  | I <sub>OZ</sub>   | —                        | ±10                      | μA   | 4     |

| Output high current (V <sub>OUT</sub> = 1.95 V)         | I <sub>ОН</sub>   | -15.2                    |                          | mA   | —     |

| Output low current (V <sub>OUT</sub> = 0.35 V)          | I <sub>OL</sub>   | 15.2                     | _                        | mA   | _     |

| MV <sub>REF</sub> input leakage current                 | I <sub>VREF</sub> | —                        | ±10                      | μA   | —     |

| Input current (0 V ≰⁄ <sub>IN</sub> ≤OV <sub>DD</sub> ) | I <sub>IN</sub>   | —                        | ±10                      | μA   | _     |

## Table 16. DDR SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 2.5 V (continued)

### Notes:

1.  $GV_{DD}$  is expected to be within 50 mV of the DRAM  $GV_{DD}$  at all times.

- 2.  $MV_{REF}$  is expected to be equal to  $0.5 \times GV_{DD}$ , and to track  $GV_{DD}$  DC variations as measured at the receiver. Peak-to-peak noise on  $MV_{REF}$  may not exceed ±2% of the DC value.

- 3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail should track variations in the DC level of MV<sub>REF</sub>.

- 4. Output leakage is measured with all outputs disabled, 0 V  $\leq$ V<sub>OUT</sub>  $\leq$ GV<sub>DD</sub>.

This table provides the DDR capacitance when  $GV_{DD}(typ) = 2.5$  V.

### Table 17. DDR SDRAM Capacitance for GV<sub>DD</sub>(typ) = 2.5 V

| Parameter/Condition                     | Symbol           | Min | Мах | Unit | Notes |

|-----------------------------------------|------------------|-----|-----|------|-------|

| Input/output capacitance: DQ, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1     |

| Delta input/output capacitance: DQ, DQS | C <sub>DIO</sub> | —   | 0.5 | pF   | 1     |

Note:

1. This parameter is sampled.  $GV_{DD}$  = 2.5 V ± 0.125 V, f = 1 MHz, T<sub>A</sub> = 25°C, V<sub>OUT</sub> =  $GV_{DD}/2$ , V<sub>OUT</sub> (peak-to-peak) = 0.2 V.

# 6.2 DDR and DDR2 SDRAM AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR and DDR2 SDRAM interface.

## 6.2.1 DDR and DDR2 SDRAM Input AC Timing Specifications

This table provides the input AC timing specifications for the DDR2 SDRAM interface when  $GV_{DD}(typ) = 1.8 V$ .

### Table 18. DDR2 SDRAM Input AC Timing Specifications for GV<sub>DD</sub>(typ) = 1.8 V

At recommended operating conditions with  $GV_{DD}$  of 1.8 V ± 5%.

| Parameter             | Symbol          | Min                      | Мах                      | Unit | Notes |

|-----------------------|-----------------|--------------------------|--------------------------|------|-------|

| AC input low voltage  | V <sub>IL</sub> | _                        | MV <sub>REF</sub> – 0.25 | V    | —     |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.25 |                          | V    | —     |

# Table 21. DDR and DDR2 SDRAM Output AC Timing Specifications for Source Synchronous Mode (continued)

At recommended operating conditions with  $GV_{DD}$  of (1.8 V or 2.5 V) ± 5%.

| Parameter <sup>8</sup> | Symbol <sup>1</sup> | Min  | Мах | Unit | Notes |

|------------------------|---------------------|------|-----|------|-------|

| MDQS epilogue end      | t <sub>DDKHME</sub> | -0.6 | 0.9 | ns   | 7     |

### Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are setup (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

</sub>

- 2. All MCK/ $\overline{MCK}$  referenced measurements are made from the crossing of the two signals ±0.1 V.

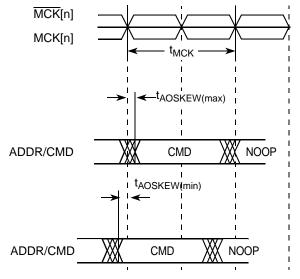

- In the source synchronous mode, MCK/MCK can be shifted in ¼ applied cycle increments through the clock control register. For the skew measurements referenced for t<sub>AOSKEW</sub> it is assumed that the clock adjustment is set to align the address/command valid with the rising edge of MCK.

- ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ/MECC/MDM/MDQS. For the ADDR/CMD setup and hold specifications, it is assumed that the clock control register is set to adjust the memory clocks by ½ applied cycle.

- 5. Note that t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK(n) clock (KH) until the MDQS signal is valid (MH). t<sub>DDKHMH</sub> can be modified through control of the DQSS override bits in the TIMING\_CFG\_2 register. In source synchronous mode, this is typically set to the same delay as the clock adjust in the CLK\_CNTL register. The timing parameters listed in the table assume that these two parameters have been set to the same adjustment value. Refer MPC8360E PowerQUICC II Pro Integrated Communications Processor Reference Manual for a description and understanding of the timing modifications enabled by use of these bits.

- Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe should be centered inside of the data eye at the pins of the device.

- All outputs are referenced to the rising edge of MCK(n) at the pins of the device. Note that t<sub>DDKHMP</sub> follows the symbol conventions described in note 1.

- 8. AC timing values are based on the DDR data rate, which is twice the DDR memory bus frequency.

- In rev. 2.0 silicon, t<sub>DDKHMH</sub> maximum meets the specification of 0.6 ns. In rev. 2.0 silicon, due to errata, t<sub>DDKHMH</sub> minimum is –0.9 ns. Refer to Errata DDR18 in *Chip Errata for the MPC8360E, Rev. 1*.

This figure shows the DDR SDRAM output timing for address skew with respect to any MCK.

This section describes the DC and AC electrical specifications for the DUART interface of the MPC8360E/58E.

# 7.1 DUART DC Electrical Characteristics

This table provides the DC electrical characteristics for the DUART interface of the device.

## Table 23. DUART DC Electrical Characteristics

| Parameter                                               | Symbol          | Min                    | Max                    | Unit | Notes |

|---------------------------------------------------------|-----------------|------------------------|------------------------|------|-------|

| High-level input voltage                                | V <sub>IH</sub> | 2                      | OV <sub>DD</sub> + 0.3 | V    | —     |

| Low-level input voltage OV <sub>DD</sub>                | V <sub>IL</sub> | -0.3                   | 0.8                    | V    | _     |

| High-level output voltage, I <sub>OH</sub> = −100 μA    | V <sub>OH</sub> | OV <sub>DD</sub> - 0.4 | _                      | V    | —     |

| Low-level output voltage, I <sub>OL</sub> = 100 μA      | V <sub>OL</sub> | —                      | 0.2                    | V    | —     |

| Input current (0 V ≰⁄ <sub>IN</sub> ≤OV <sub>DD</sub> ) | I <sub>IN</sub> | —                      | ±10                    | μA   | 1     |

### Note:

1. Note that the symbol V<sub>IN</sub>, in this case, represents the OV<sub>IN</sub> symbol referenced in Table 1 and Table 2.

## 7.2 DUART AC Electrical Specifications

This table provides the AC timing parameters for the DUART interface of the device.

| Parameter         | Value      | Unit | Notes |

|-------------------|------------|------|-------|

| Minimum baud rate | 256        | baud | —     |

| Maximum baud rate | >1,000,000 | baud | 1     |

| Oversample rate   | 16         |      | 2     |

### Notes:

- 1. Actual attainable baud rate is limited by the latency of interrupt processing.

- 2. The middle of a start bit is detected as the eighth sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled each sixteenth sample.

# 8 UCC Ethernet Controller: Three-Speed Ethernet, MII Management

This section provides the AC and DC electrical characteristics for three-speed, 10/100/1000, and MII management.

# 8.1 Three-Speed Ethernet Controller (10/100/1000 Mbps)— GMII/MII/RMII/TBI/RGMII/RTBI Electrical Characteristics

The electrical characteristics specified here apply to all GMII (gigabit media independent interface), MII (media independent interface), RMII (reduced media independent interface), TBI (ten-bit interface), RGMII (reduced gigabit media independent interface), and RTBI (reduced ten-bit interface) signals except MDIO (management data input/output) and MDC (management data clock). The MII, RMII, GMII, and TBI interfaces are only defined for 3.3 V, while the RGMII and RTBI interfaces are only defined for 2.5 V. The RGMII and RTBI interfaces follow the Hewlett-Packard reduced pin-count interface for Gigabit Ethernet

## 8.2.4.1 TBI Transmit AC Timing Specifications

This table provides the TBI transmit AC timing specifications.

### Table 33. TBI Transmit AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/OV_{DD}$  of 3.3 V ± 10%.

| Parameter/Condition                   | Symbol <sup>1</sup>                        | Min | Тур | Мах     | Unit | Notes |

|---------------------------------------|--------------------------------------------|-----|-----|---------|------|-------|

| GTX_CLK clock period                  | t <sub>TTX</sub>                           |     | 8.0 | —       | ns   | —     |

| GTX_CLK duty cycle                    | t <sub>TTXH</sub> /t <sub>TTX</sub>        | 40  | —   | 60      | %    | —     |

| GTX_CLK to TBI data TCG[9:0] delay    | <sup>t</sup> тткнdx<br><sup>t</sup> тткнdv | 1.0 | —   | <br>5.0 | ns   | 3     |

| GTX_CLK clock rise time, (20% to 80%) | t <sub>TTXR</sub>                          | _   | —   | 1.0     | ns   | —     |

| GTX_CLK clock fall time, (80% to 20%) | t <sub>TTXF</sub>                          | _   | —   | 1.0     | ns   | —     |

| GTX_CLK125 reference clock period     | t <sub>G125</sub>                          | _   | 8.0 | _       | ns   | 2     |

| GTX_CLK125 reference clock duty cycle | t <sub>G125H</sub> /t <sub>G125</sub>      | 45  | —   | 55      | ns   | —     |

Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>TTKHDV</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the valid state (V) or setup time. Also, t<sub>TTKHDX</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the valid state (V) or setup time. Also, t<sub>TTKHDX</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the invalid state (X) or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>TTX</sub> represents the TBI (T) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- 2. This symbol is used to represent the external GTX\_CLK125 and does not follow the original symbol naming convention.

- 3. In rev. 2.0 silicon, due to errata, t<sub>TTKHDX</sub> minimum is 0.7 ns for UCC1. Refer to Errata QE\_ENET19 in Chip Errata for the MPC8360E, Rev. 1.

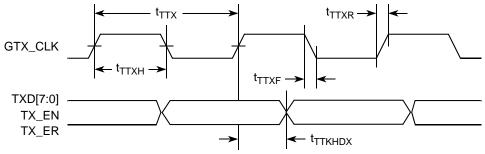

This figure shows the TBI transmit AC timing diagram.

Figure 18. TBI Transmit AC Timing Diagram

## 8.2.5 RGMII and RTBI AC Timing Specifications

This table presents the RGMII and RTBI AC timing specifications.

### Table 35. RGMII and RTBI AC Timing Specifications

At recommended operating conditions with  $LV_{DD}$  of 2.5 V ± 5%.

| Parameter/Condition                        | Symbol <sup>1</sup>                              | Min      | Тур | Мах      | Unit | Notes |

|--------------------------------------------|--------------------------------------------------|----------|-----|----------|------|-------|

| Data to clock output skew (at transmitter) | t <sub>SKRGTKHDX</sub><br>t <sub>SKRGTKHDV</sub> | -0.5<br> | —   | —<br>0.5 | ns   | 7     |

| Data to clock input skew (at receiver)     | t <sub>SKRGDXKH</sub><br>t <sub>SKRGDVKH</sub>   | 1.0      | —   | <br>2.6  | ns   | 2     |

| Clock cycle duration                       | t <sub>RGT</sub>                                 | 7.2      | 8.0 | 8.8      | ns   | 3     |

| Duty cycle for 1000Base-T                  | t <sub>RGTH</sub> /t <sub>RGT</sub>              | 45       | 50  | 55       | %    | 4, 5  |

| Duty cycle for 10BASE-T and 100BASE-TX     | t <sub>RGTH</sub> /t <sub>RGT</sub>              | 40       | 50  | 60       | %    | 3, 5  |

| Rise time (20–80%)                         | t <sub>RGTR</sub>                                | _        | —   | 0.75     | ns   | —     |

| Fall time (20–80%)                         | t <sub>RGTF</sub>                                | _        | —   | 0.75     | ns   | —     |

| GTX_CLK125 reference clock period          | t <sub>G125</sub>                                | _        | 8.0 | _        | ns   | 6     |

| GTX_CLK125 reference clock duty cycle      | t <sub>G125H</sub> /t <sub>G125</sub>            | 47       | —   | 53       | %    | —     |

Notes:

- Note that, in general, the clock reference symbol representation for this section is based on the symbols RGT to represent RGMII and RTBI timing. For example, the subscript of t<sub>RGT</sub> represents the TBI (T) receive (Rx) clock. Note also that the notation for rise (R) and fall (F) times follows the clock symbol that is being represented. For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (RGT).

- 2. This implies that PC board design requires clocks to be routed such that an additional trace delay of greater than 1.5 ns can be added to the associated clock signal.

- 3. For 10 and 100 Mbps,  $t_{RGT}$  scales to 400 ns ± 40 ns and 40 ns ± 4 ns, respectively.

- 4. Duty cycle may be stretched/shrunk during speed changes or while transitioning to a received packet's clock domains as long as the minimum duty cycle is not violated and stretching occurs for no more than three t<sub>RGT</sub> of the lowest speed transitioned between.

- 5. Duty cycle reference is LV<sub>DD</sub>/2.

- 6. This symbol is used to represent the external GTX\_CLK125 and does not follow the original symbol naming convention.

- 7. In rev. 2.0 silicon, due to errata, t<sub>SKRGTKHDX</sub> minimum is –2.3 ns and t<sub>SKRGTKHDV</sub> maximum is 1 ns for UCC1, 1.2 ns for UCC2 option 1, and 1.8 ns for UCC2 option 2. In rev. 2.1 silicon, due to errata, t<sub>SKRGTKHDX</sub> minimum is –0.65 ns for UCC2 option 1 and –0.9 for UCC2 option 2, and t<sub>SKRGTKHDV</sub> maximum is 0.75 ns for UCC1 and UCC2 option 1 and 0.85 for UCC2 option 2. Refer to Errata QE\_ENET10 in *Chip Errata for the MPC8360E, Rev. 1*. UCC1 does meet t<sub>SKRGTKHDX</sub> minimum for rev. 2.1 silicon.

**JTAG DC Electrical Characteristics**

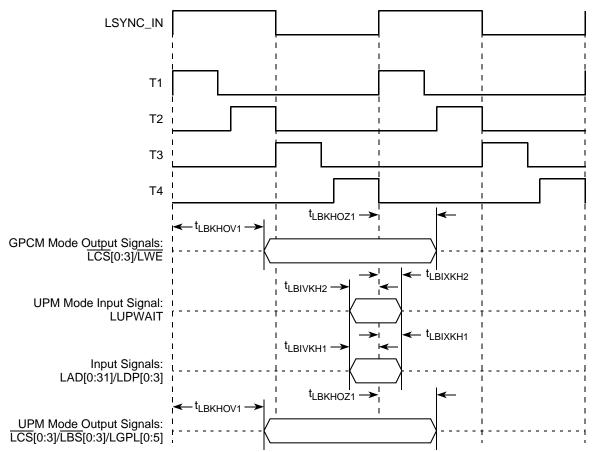

Figure 28. Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 4 (DLL Enabled)

# 10 JTAG

This section describes the DC and AC electrical specifications for the IEEE 1149.1 (JTAG) interface of the MPC8360E/58E.

# **10.1 JTAG DC Electrical Characteristics**

This table provides the DC electrical characteristics for the IEEE 1149.1 (JTAG) interface of the device.

| Characteristic      | Symbol          | Condition                      | Min  | Мах                    | Unit |

|---------------------|-----------------|--------------------------------|------|------------------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -6.0 mA      | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 6.0 mA       | _    | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA       | _    | 0.4                    | V    |

| Input high voltage  | V <sub>IH</sub> | —                              | 2.5  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                              | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | $0 V \leq V_{IN} \leq OV_{DD}$ | _    | ±10                    | μA   |

### **JTAG AC Electrical Characteristics**

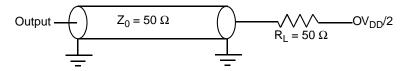

This figure provides the AC test load for TDO and the boundary-scan outputs of the device.

Figure 29. AC Test Load for the JTAG Interface

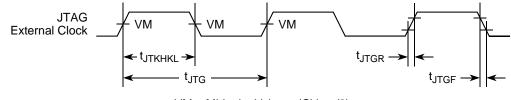

This figure provides the JTAG clock input timing diagram.

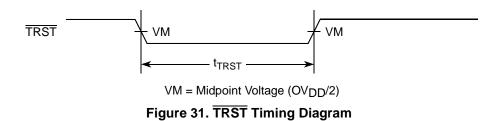

VM = Midpoint Voltage (OV<sub>DD</sub>/2)

## Figure 30. JTAG Clock Input Timing Diagram

This figure provides the  $\overline{\text{TRST}}$  timing diagram.

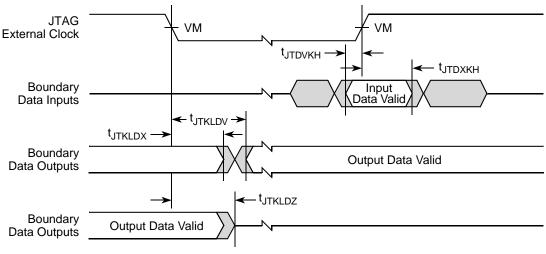

This figure provides the boundary-scan timing diagram.

VM = Midpoint Voltage (OV<sub>DD</sub>/2)

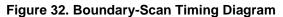

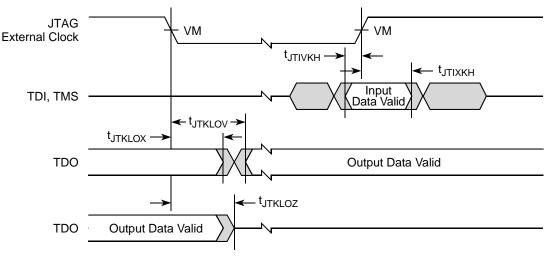

This figure provides the test access port timing diagram.

VM = Midpoint Voltage (OV<sub>DD</sub>/2)

Figure 33. Test Access Port Timing Diagram

# 11 I<sup>2</sup>C

This section describes the DC and AC electrical characteristics for the  $I^2C$  interface of the MPC8360E/58E.

# 11.1 I<sup>2</sup>C DC Electrical Characteristics

This table provides the DC electrical characteristics for the  $I^2C$  interface of the device.

## Table 44. I<sup>2</sup>C DC Electrical Characteristics

At recommended operating conditions with  $OV_{DD}$  of 3.3 V ± 10%.

| Parameter                                                                                     | Symbol              | Min                   | Max                    | Unit | Notes |

|-----------------------------------------------------------------------------------------------|---------------------|-----------------------|------------------------|------|-------|

| Input high voltage level                                                                      | V <sub>IH</sub>     | $0.7 	imes OV_{DD}$   | OV <sub>DD</sub> + 0.3 | V    | —     |

| Input low voltage level                                                                       | V <sub>IL</sub>     | -0.3                  | $0.3 	imes OV_{DD}$    | V    | —     |

| Low level output voltage                                                                      | V <sub>OL</sub>     | 0                     | 0.4                    | V    | 1     |

| Output fall time from $V_{IH}(min)$ to $V_{IL}(max)$ with a bus capacitance from 10 to 400 pF | t <sub>I2KLKV</sub> | $20 + 0.1 \times C_B$ | 250                    | ns   | 2     |

| Pulse width of spikes which must be suppressed by the input filter                            | t <sub>i2KHKL</sub> | 0                     | 50                     | ns   | 3     |

| Capacitance for each I/O pin                                                                  | Cl                  | —                     | 10                     | pF   | —     |

| Input current (0 V ≤V <sub>IN</sub> ≤OV <sub>DD</sub> )                                       | I <sub>IN</sub>     | —                     | ±10                    | μA   | 4     |

### Notes:

1. Output voltage (open drain or open collector) condition = 3 mA sink current.

- 2.  $C_B$  = capacitance of one bus line in pF.

- 3. Refer to the MPC8360E Integrated Communications Processor Reference Manual for information on the digital filter used.

- 4. I/O pins obstruct the SDA and SCL lines if OV<sub>DD</sub> is switched off.

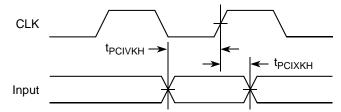

This figure shows the PCI input AC timing conditions.

Figure 37. PCI Input AC Timing Measurement Conditions

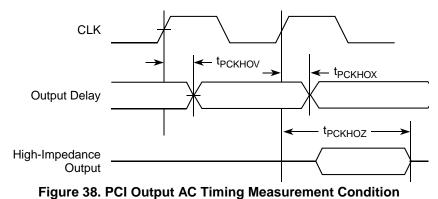

This figure shows the PCI output AC timing conditions.

# 13 Timers

This section describes the DC and AC electrical specifications for the timers of the MPC8360E/58E.

## **13.1 Timers DC Electrical Characteristics**

This table provides the DC electrical characteristics for the device timer pins, including TIN, TOUT, TGATE, and RTC\_CLK.

**Table 49. Timers DC Electrical Characteristics**

| Characteristic      | Symbol          | Condition                      | Min  | Мах                    | Unit |

|---------------------|-----------------|--------------------------------|------|------------------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -6.0 mA      | 2.4  |                        | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 6.0 mA       | _    | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA       | _    | 0.4                    | V    |

| Input high voltage  | V <sub>IH</sub> | —                              | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                              | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | $0 V \leq V_{IN} \leq OV_{DD}$ | _    | ±10                    | μA   |

**IPIC AC Timing Specifications**

# 15.2 IPIC AC Timing Specifications

This table provides the IPIC input and output AC timing specifications.

### Table 54. IPIC Input AC Timing Specifications<sup>1</sup>

| Characteristic                  | Symbol <sup>2</sup> | Min | Unit |

|---------------------------------|---------------------|-----|------|

| IPIC inputs—minimum pulse width | t <sub>PIWID</sub>  | 20  | ns   |

### Notes:

1. Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of CLKIN. Timings are measured at the pin.

IPIC inputs and outputs are asynchronous to any visible clock. IPIC outputs should be synchronized before use by any

external synchronous logic. IPIC inputs are required to be valid for at least t<sub>PIWID</sub> ns to ensure proper operation when

working in edge triggered mode.

# 16 SPI

This section describes the DC and AC electrical specifications for the SPI of the MPC8360E/58E.

# 16.1 SPI DC Electrical Characteristics

This table provides the DC electrical characteristics for the device SPI.

### Table 55. SPI DC Electrical Characteristics

| Characteristic      | Symbol          | Condition                              | Min  | Max                    | Unit |

|---------------------|-----------------|----------------------------------------|------|------------------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -6.0 mA              | 2.4  | _                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 6.0 mA               | —    | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA               | —    | 0.4                    | V    |

| Input high voltage  | V <sub>IH</sub> | —                                      | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                                      | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | 0 V ≤V <sub>IN</sub> ≤OV <sub>DD</sub> | —    | ±10                    | μA   |

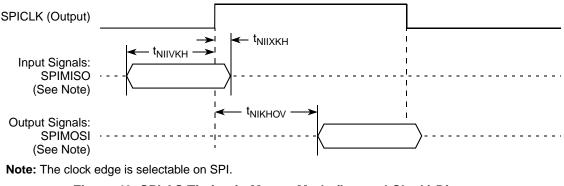

# 16.2 SPI AC Timing Specifications

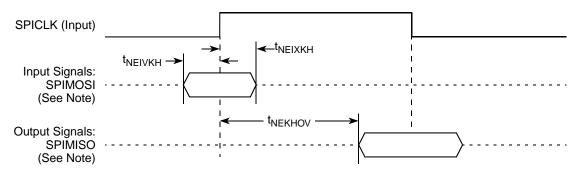

This table and provide the SPI input and output AC timing specifications.

Table 56. SPI AC Timing Specifications<sup>1</sup>

| Characteristic                                           | Symbol <sup>2</sup>                        | Min | Max   | Unit |

|----------------------------------------------------------|--------------------------------------------|-----|-------|------|

| SPI outputs—Master mode (internal clock) delay           | t <sub>NIKHOX</sub><br>t <sub>NIKHOV</sub> | 0.3 | 8     | ns   |

| SPI outputs—Slave mode (external clock) delay            | t <sub>NEKHOX</sub><br>t <sub>NEKHOV</sub> | 2   | <br>8 | ns   |

| SPI inputs—Master mode (internal clock) input setup time | t <sub>NIIVKH</sub>                        | 8   | —     | ns   |

| SPI inputs—Master mode (internal clock) input hold time  | t <sub>NIIXKH</sub>                        | 0   | —     | ns   |

| SPI inputs—Slave mode (external clock) input setup time  | t <sub>NEIVKH</sub>                        | 4   |       | ns   |

### **SPI AC Timing Specifications**

| Table 56. | SPI AC | Timing | Specifications <sup>1</sup> |

|-----------|--------|--------|-----------------------------|

|-----------|--------|--------|-----------------------------|

| Characteristic                                         | Symbol <sup>2</sup> | Min | Max | Unit |

|--------------------------------------------------------|---------------------|-----|-----|------|

| SPI inputs—Slave mode (external clock) input hold time | t <sub>NEIXKH</sub> | 2   | —   | ns   |

Notes:

- 1. Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are measured at the pin.

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>NIKHOV</sub> symbolizes the NMSI outputs internal timing (NI) for the time t<sub>SPI</sub> memory clock reference (K) goes from the high state (H) until outputs (O) are valid (V).

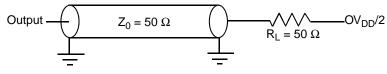

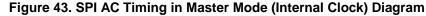

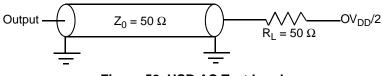

This figure provides the AC test load for the SPI.

Figure 41. SPI AC Test Load

These figures represent the AC timing from Table 56. Note that although the specifications generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge is the active edge.

This figure shows the SPI timing in slave mode (external clock).

Note: The clock edge is selectable on SPI.

### Figure 42. SPI AC Timing in Slave Mode (External Clock) Diagram

This figure shows the SPI timing in Master mode (internal clock).

**USB DC Electrical Characteristics**

# 19 USB

This section provides the AC and DC electrical specifications for the USB interface of the MPC8360E/58E.

# **19.1 USB DC Electrical Characteristics**

This table provides the DC electrical characteristics for the USB interface.

## **Table 64. USB DC Electrical Characteristics**

| Parameter                                            | Symbol          | Min                    | Мах                    | Unit |

|------------------------------------------------------|-----------------|------------------------|------------------------|------|

| High-level input voltage                             | V <sub>IH</sub> | 2                      | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                              | V <sub>IL</sub> | -0.3                   | 0.8                    | V    |

| High-level output voltage, I <sub>OH</sub> = −100 μA | V <sub>OH</sub> | OV <sub>DD</sub> - 0.4 | _                      | V    |

| Low-level output voltage, I <sub>OL</sub> = 100 μA   | V <sub>OL</sub> | —                      | 0.2                    | V    |

| Input current                                        | I <sub>IN</sub> | —                      | ±10                    | μA   |

## **19.2 USB AC Electrical Specifications**

This table describes the general timing parameters of the USB interface of the device.

Table 65. USB General Timing Parameters

| Parameter                    | Symbol <sup>1</sup>  | Min    | Max | Unit | Notes                  | Note |

|------------------------------|----------------------|--------|-----|------|------------------------|------|

| USB clock cycle time         | t <sub>USCK</sub>    | 20.83  | —   | ns   | Full speed 48 MHz      | —    |

| USB clock cycle time         | t <sub>USCK</sub>    | 166.67 | —   | ns   | Low speed 6 MHz        | _    |

| Skew between TXP and TXN     | t <sub>USTSPN</sub>  | —      | 5   | ns   | —                      | 2    |

| Skew among RXP, RXN, and RXD | t <sub>USRSPND</sub> | —      | 10  | ns   | Full speed transitions | 2    |

| Skew among RXP, RXN, and RXD | t <sub>USRPND</sub>  | —      | 100 | ns   | Low speed transitions  | 2    |

### Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(state)(signal)</sub> for receive signals and t<sub>(first two letters of functional block)(state)(signal)</sub> for transmit signals. For example, t<sub>USRSPND</sub> symbolizes USB timing (US) for the USB receive signals skew (RS) among RXP, RXN, and RXD (PND). Also, t<sub>USTSPN</sub> symbolizes USB timing (US) for the USB transmit signals skew (TS) between TXP and TXN (PN).

2. Skew measurements are done at  $OV_{DD}/2$  of the rising or falling edge of the signals.

This figure provide the AC test load for the USB.

Figure 52. USB AC Test Load

**Pinout Listings**

| Signal                                                                                                                                     | Package Pin Number                                                                             | Pin Type | Power<br>Supply    | Notes |  |

|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------|--------------------|-------|--|

| MEMC1_MCKE[0:1]                                                                                                                            | AL32, AU33                                                                                     | 0        | GV <sub>DD</sub>   | 3     |  |

| MEMC1_MCK[0:1]                                                                                                                             | AK37, AT37                                                                                     | 0        | GV <sub>DD</sub>   | —     |  |

| MEMC1_MCK[2:3]/<br>MEMC2_MCK[0:1]                                                                                                          | AN1, AR2                                                                                       | 0        | GV <sub>DD</sub>   | _     |  |

| MEMC1_MCK[4:5]/<br>MEMC2_MCKE[0:1]                                                                                                         | AN25, AK1                                                                                      | 0        | GV <sub>DD</sub>   | _     |  |

| MEMC1_MCK[0:1]                                                                                                                             | AL37, AT36                                                                                     | 0        | GV <sub>DD</sub>   | —     |  |

| MEMC1_MCK[2:3]/<br>MEMC2_MCK[0:1]                                                                                                          | AP2, AT2                                                                                       | 0        | GV <sub>DD</sub>   |       |  |

| MEMC1_MCK[4]/<br>MEMC2_MDM[8]                                                                                                              | AN24                                                                                           | 0        | GV <sub>DD</sub>   | —     |  |

| MEMC1_MCK[5]/<br>MEMC2_MDQS[8]                                                                                                             | AL1                                                                                            | 0        | GV <sub>DD</sub>   | —     |  |

| MDIC[0:1]                                                                                                                                  | AH6, AP30                                                                                      | I/O      | GV <sub>DD</sub>   | 10    |  |

| S                                                                                                                                          | Secondary DDR SDRAM Memory Controller Interface                                                |          |                    | 1     |  |

| MEMC2_MECC[0:7]                                                                                                                            | AN16, AP18, AM16, AM17, AN17, AP13, AP15, AN13                                                 | I/O      | GV <sub>DD</sub>   | -     |  |

| MEMC2_MBA[0:2]                                                                                                                             | AU12, AU15, AU13                                                                               | 0        | GV <sub>DD</sub>   | _     |  |

| MEMC2_MA[0:14]                                                                                                                             | AT12, AP11, AT13, AT14, AR13, AR15, AR16,<br>AT16, AT18, AT17, AP10, AR20, AR17, AR14,<br>AR11 | 0        | GV <sub>DD</sub>   | -     |  |

| MEMC2_MWE                                                                                                                                  | AU10                                                                                           | 0        | GV <sub>DD</sub>   | —     |  |

| MEMC2_MRAS                                                                                                                                 | AT11                                                                                           | 0        | GV <sub>DD</sub>   | —     |  |

| MEMC2_MCAS AU11                                                                                                                            |                                                                                                | 0        | GV <sub>DD</sub>   | —     |  |

|                                                                                                                                            | PCI                                                                                            |          |                    | •     |  |

| PCI_INTA/IRQ_OUT/CE_PF[5]                                                                                                                  | A20                                                                                            | I/O      | LV <sub>DD</sub> 2 | 2     |  |

| PCI_RESET_OUT/CE_PF[6]                                                                                                                     | E19                                                                                            | I/O      | LV <sub>DD</sub> 2 |       |  |

| PCI_AD[31:30]/CE_PG[31:30]                                                                                                                 | D20, D21                                                                                       | I/O      | LV <sub>DD</sub> 2 |       |  |

| PCI_AD[29:25]/CE_PG[29:25]                                                                                                                 | A24, B23, C23, E23, A26                                                                        | I/O      | OV <sub>DD</sub>   | —     |  |

| PCI_AD[24]/CE_PG[24]                                                                                                                       | B21                                                                                            | I/O      | LV <sub>DD</sub> 2 | —     |  |

| C24, C25, D25, B25, E24, F24, A27, A28, F27, A30,           C30, D30, E29, B31, C31, D31, D32, A32, C33,           B33, F30, E31, A34, D33 |                                                                                                | I/O      | OV <sub>DD</sub>   | -     |  |

| PCI_C/BE[3:0]/CE_PF[10:7]                                                                                                                  | E22, B26, E28, F28                                                                             | I/O      | OV <sub>DD</sub>   | —     |  |

| PCI_PAR/CE_PF[11]                                                                                                                          | D28                                                                                            |          | OV <sub>DD</sub>   | -     |  |

| PCI_FRAME/CE_PF[12]                                                                                                                        | D26 I/O                                                                                        |          | OV <sub>DD</sub>   | 5     |  |

| PCI_TRDY/CE_PF[13]                                                                                                                         | C27                                                                                            | I/O      | OV <sub>DD</sub>   | 5     |  |

| PCI_IRDY/CE_PF[14]                                                                                                                         | C28                                                                                            | I/O      | OV <sub>DD</sub>   | 5     |  |

| PCI_STOP/CE_PF[15]                                                                                                                         | B28                                                                                            | I/O      | OV <sub>DD</sub>   | 5     |  |

## Table 66. MPC8360E TBGA Pinout Listing (continued)

| Signal                                 | Package Pin Number                                                                                                                                                         | Pin Type | Power<br>Supply    | Notes |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------|-------|

| PCI_DEVSEL/CE_PF[16]                   | E26                                                                                                                                                                        | I/O      | OV <sub>DD</sub>   | 5     |

| PCI_IDSEL/CE_PF[17]                    | F22                                                                                                                                                                        | I/O      | OV <sub>DD</sub>   | —     |

| PCI_SERR/CE_PF[18]                     | B29                                                                                                                                                                        | I/O      | OV <sub>DD</sub>   | 5     |

| PCI_PERR/CE_PF[19]                     | A29                                                                                                                                                                        | I/O      | OV <sub>DD</sub>   | 5     |

| PCI_REQ[0]/CE_PF[20]                   | F19                                                                                                                                                                        | I/O      | LV <sub>DD</sub> 2 | —     |

| PCI_REQ[1]/CPCI_HS_ES/<br>CE_PF[21]    | A21                                                                                                                                                                        | I/O      | LV <sub>DD</sub> 2 | —     |

| PCI_REQ[2]/CE_PF[22]                   | C21                                                                                                                                                                        | I/O      | LV <sub>DD</sub> 2 | —     |

| PCI_GNT[0]/CE_PF[23]                   | E20                                                                                                                                                                        | I/O      | LV <sub>DD</sub> 2 | —     |

| PCI_GNT[1]/CPCI1_HS_LED/<br>CE_PF[24]  | B20                                                                                                                                                                        | I/O      | LV <sub>DD</sub> 2 |       |

| PCI_GNT[2]/CPCI1_HS_ENUM/<br>CE_PF[25] | C20                                                                                                                                                                        | I/O      | LV <sub>DD</sub> 2 | _     |

| PCI_MODE                               | D36                                                                                                                                                                        | I        | OV <sub>DD</sub>   | —     |

| M66EN/CE_PF[4]                         | B37                                                                                                                                                                        | I/O      | OV <sub>DD</sub>   | —     |

|                                        | Local Bus Controller Interface                                                                                                                                             |          |                    |       |

| LAD[0:31]                              | N32, N33, N35, N36, P37, P32, P34, R36, R35,<br>R34, R33, T37, T35, T34, T33, U37, T32, U36, U34,<br>V36, V35, W37, W35, V33, V32, W34, Y36, W32,<br>AA37, Y33, AA35, AA34 | I/O      | OV <sub>DD</sub>   | —     |

| LDP[0]/CKSTOP_OUT                      | AB37                                                                                                                                                                       | I/O      | OV <sub>DD</sub>   | —     |

| LDP[1]/CKSTOP_IN                       | AB36                                                                                                                                                                       | I/O      | OV <sub>DD</sub>   | - I   |

| LDP[2]/LCS[6]                          | AB35                                                                                                                                                                       | I/O      | OV <sub>DD</sub>   | —     |

| LDP[3]/LCS[7]                          | AA33                                                                                                                                                                       | I/O      | OV <sub>DD</sub>   | —     |

| LA[27:31]                              | AC37, AA32, AC36, AC34, AD36                                                                                                                                               | 0        | OV <sub>DD</sub>   | —     |

| LCS[0:5]                               | AD33, AG37, AF34, AE33, AD32, AH37                                                                                                                                         | 0        | OV <sub>DD</sub>   | —     |

| LWE[0:3]/LSDDQM[0:3]/LBS[0:3]          | AG35, AG34, AH36, AE32                                                                                                                                                     | 0        | OV <sub>DD</sub>   | —     |

| LBCTL                                  | AD35                                                                                                                                                                       | 0        | OV <sub>DD</sub>   | —     |

| LALE                                   | M37                                                                                                                                                                        | 0        | OV <sub>DD</sub>   | —     |

| LGPL0/LSDA10/cfg_reset_source0         | AB32                                                                                                                                                                       | I/O      | OV <sub>DD</sub>   | —     |

| LGPL1/LSDWE/cfg_reset_source1          | AE37                                                                                                                                                                       | I/O      | OV <sub>DD</sub>   | —     |

| LGPL2/LSDRAS/LOE                       | AC33                                                                                                                                                                       | 0        | OV <sub>DD</sub>   | —     |

| LGPL3/LSDCAS/cfg_reset_source2         | AD34                                                                                                                                                                       | I/O      | OV <sub>DD</sub>   | —     |

| LGPL4/LGTA/LUPWAIT/LPBSE               | AE35                                                                                                                                                                       | I/O      | OV <sub>DD</sub>   | -     |

| LGPL5/cfg_clkin_div                    | AF36 I/O O                                                                                                                                                                 |          | OV <sub>DD</sub>   | —     |

| LCKE                                   | G36                                                                                                                                                                        | 0        | OV <sub>DD</sub>   | —     |

| LCLK[0]                                | J33                                                                                                                                                                        | 0        | OV <sub>DD</sub>   | —     |

| LCLK[1]/LCS[6]                         | J34                                                                                                                                                                        | 0        | OV <sub>DD</sub>   | —     |

Pinout Listings

| Signal             | Package Pin Number                                                                                                                                                                                                                                                                                       | Pin Type                                                                    | Power<br>Supply             | Notes |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------|-------|

| LV <sub>DD</sub> 1 | C17, D16                                                                                                                                                                                                                                                                                                 | Power for<br>UCC2<br>Ethernet<br>interface<br>option 1<br>(2.5 V,<br>3.3 V) | LV <sub>DD</sub> 1          | 9     |

| LV <sub>DD</sub> 2 | B18, E21                                                                                                                                                                                                                                                                                                 | Power for<br>UCC2<br>Ethernet<br>interface<br>option 2<br>(2.5 V,<br>3.3 V) | LV <sub>DD</sub> 2          | 9     |

| V <sub>DD</sub>    | C36, D29, D35, E16, F9, F12, F15, F17, F18, F20,<br>F21, F23, F25, F26, F29, F31, F32, F33, G6, J6,<br>K32, M32, N6, P33, R6, R32, U32, V6, Y5, Y32,<br>AB6, AB33, AD6, AF32, AK6, AL6, AM7, AM9,<br>AM10, AM11, AM12, AM13, AM14, AM15, AM18,<br>AM21, AM25, AM28, AM32, AN15, AN21, AN26,<br>AU9, AU17 | Power for<br>core<br>(1.2 V)                                                | V <sub>DD</sub>             | _     |

| OV <sub>DD</sub>   | A10, B9, B15, B32, C1, C12, C22, C29, D24, E3,<br>E10, E27, G4, H35, J1, J35, K2, M4, N3, N34, R2,<br>R37, T36, U2, U33, V4, V34, W3, Y35, Y37, AA1,<br>AA36, AB2, AB34                                                                                                                                  | PCI,<br>10/100<br>Ethernet,<br>and other<br>standard<br>(3.3 V)             | OV <sub>DD</sub>            | _     |

| MVREF1             | AN20                                                                                                                                                                                                                                                                                                     | I                                                                           | DDR<br>reference<br>voltage | _     |

| MVREF2             | AU32                                                                                                                                                                                                                                                                                                     | I                                                                           | DDR<br>reference<br>voltage | —     |

|                    |                                                                                                                                                                                                                                                                                                          |                                                                             |                             |       |

| SPARE1             | B11                                                                                                                                                                                                                                                                                                      | I/O                                                                         | OV <sub>DD</sub>            | 8     |

| SPARE3             | AH32                                                                                                                                                                                                                                                                                                     | —                                                                           | GV <sub>DD</sub>            | 8     |

| SPARE4             | AU18                                                                                                                                                                                                                                                                                                     |                                                                             | GV <sub>DD</sub>            | 7     |

| SPARE5             | AP1                                                                                                                                                                                                                                                                                                      | _                                                                           | GV <sub>DD</sub>            | 8     |

## Table 67. MPC8358E TBGA Pinout Listing (continued)

System PLL Configuration

|                                        |      |                                                    | li    | nput Clock Fre | equency (MHz | ) <sup>2</sup> |

|----------------------------------------|------|----------------------------------------------------|-------|----------------|--------------|----------------|

| CFG_CLKIN_DIV<br>at Reset <sup>1</sup> | SPMF | <i>csb_clk</i> :<br>Input Clock Ratio <sup>2</sup> | 16.67 | 25             | 33.33        | 66.67          |

|                                        |      |                                                    |       | csb_clk Fred   | quency (MHz) |                |

| Low                                    | 0110 | 6:1                                                | 100   | 150            | 200          |                |

| Low                                    | 0111 | 7:1                                                | 116   | 175            | 233          |                |

| Low                                    | 1000 | 8:1                                                | 133   | 200            | 266          |                |

| Low                                    | 1001 | 9:1                                                | 150   | 225            | 300          |                |

| Low                                    | 1010 | 10:1                                               | 166   | 250            | 333          |                |

| Low                                    | 1011 | 11:1                                               | 183   | 275            |              |                |

| Low                                    | 1100 | 12:1                                               | 200   | 300            |              |                |

| Low                                    | 1101 | 13:1                                               | 216   | 325            |              |                |

| Low                                    | 1110 | 14:1                                               | 233   |                | <u> </u>     |                |

| Low                                    | 1111 | 15:1                                               | 250   | 1              |              |                |

| Low                                    | 0000 | 16:1                                               | 266   | 1              |              |                |

| High                                   | 0010 | 2:1                                                |       |                |              | 133            |

| High                                   | 0011 | 3:1                                                |       |                | 100          | 200            |

| High                                   | 0100 | 4:1                                                |       |                | 133          | 266            |

| High                                   | 0101 | 5:1                                                |       |                | 166          | 333            |

| High                                   | 0110 | 6:1                                                |       |                | 200          |                |

| High                                   | 0111 | 7:1                                                |       |                | 233          |                |

| High                                   | 1000 | 8:1                                                |       |                |              |                |

| High                                   | 1001 | 9:1                                                |       |                |              |                |

| High                                   | 1010 | 10:1                                               |       |                |              |                |

| High                                   | 1011 | 11:1                                               |       |                |              |                |

| High                                   | 1100 | 12:1                                               |       |                |              |                |

| High                                   | 1101 | 13:1                                               |       |                |              |                |

| High                                   | 1110 | 14:1                                               |       |                |              |                |

| High                                   | 1111 | 15:1                                               |       |                |              |                |

| High                                   | 0000 | 16:1                                               |       |                |              |                |

## Table 72. CSB Frequency Options (continued)

<sup>1</sup> CFG\_CLKIN\_DIV is only used for host mode; CLKIN must be tied low and CFG\_CLKIN\_DIV must be pulled down (low) in agent mode.

$^2\,$  CLKIN is the input clock in host mode; PCI\_CLK is the input clock in agent mode.

## 23.7 Pull-Up Resistor Requirements

The device requires high resistance pull-up resistors (10 k $\Omega$  is recommended) on open drain type pins including I<sup>2</sup>C pins, Ethernet Management MDIO pin, and EPIC interrupt pins.

For more information on required pull-up resistors and the connections required for the JTAG interface, see *MPC8360E/MPC8358E PowerQUICC Design Checklist* (AN3097).

# 24 Ordering Information

# 24.1 Part Numbers Fully Addressed by this Document

This table provides the Freescale part numbering nomenclature for the MPC8360E/58E. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. Additionally to the processor frequency, the part numbering scheme also includes an application modifier, which may specify special application conditions. Each part number also contains a revision code that refers to the die mask revision number.

| MPC                                  | nnnn               | е                                       | t                                                                            | рр                                  | aa                                                              | а                          | а                            | Α                       |

|--------------------------------------|--------------------|-----------------------------------------|------------------------------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------|----------------------------|------------------------------|-------------------------|

| Product<br>Code                      | Part<br>Identifier | Encryption<br>Acceleration              | Temperature<br>Range                                                         | Package <sup>2</sup>                | Processor<br>Frequency <sup>3</sup>                             | Platform<br>Frequency      | QUICC<br>Engine<br>Frequency | Die<br>Revision         |

| MPC                                  | 8358               | Blank = not<br>included<br>E = included | Blank = $0^{\circ}$ C<br>T <sub>A</sub> to $105^{\circ}$ C<br>T <sub>J</sub> | ZU = TBGA<br>VV = TBGA<br>(no lead) | e300 core speed<br>AD = 266 MHz<br>AG = 400 MHz                 | D = 266 MHz                | E = 300 MHz<br>G = 400 MHz   | A = rev. 2.1<br>silicon |

|                                      | 8360               |                                         | C= -40° C T <sub>A</sub><br>to 105° C T <sub>J</sub>                         |                                     | e300 core speed<br>AG = 400 MHz<br>AJ = 533 MHz<br>AL = 667 MHz | D = 266 MHz<br>F = 333 MHz | G = 400 MHz<br>H = 500 MHz   | A = rev. 2.1<br>silicon |

| MPC<br>(rev. 2.0<br>silicon<br>only) | 8360               | Blank = not<br>included<br>E = included | 0° C T <sub>A</sub> to<br>70° C T <sub>J</sub>                               | ZU = TBGA<br>VV = TBGA<br>(no lead) | e300 core speed<br>AH = 500 MHz<br>AL = 667 MHz                 | F = 333 MHz                | G = 400 MHz<br>H = 500 MHz   | —                       |

## Table 80. Part Numbering Nomenclature<sup>1</sup>

### Notes:

1. Not all processor, platform, and QUICC Engine block frequency combinations are supported. For available frequency combinations, contact your local Freescale sales office or authorized distributor.

2. See Section 20, "Package and Pin Listings," for more information on available package types.

Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by part number specifications may support other maximum core frequencies.

This table shows the SVR settings by device and package type.

| Table 8 <sup>-</sup> | 1. SVR | Settings |

|----------------------|--------|----------|

|----------------------|--------|----------|

| Device   | Package | SVR<br>(Rev. 2.0) | SVR<br>(Rev. 2.1) |

|----------|---------|-------------------|-------------------|

| MPC8360E | TBGA    | 0x8048_0020       | 0x8048_0021       |

| MPC8360  | TBGA    | 0x8049_0020       | 0x8049_0021       |

Part Numbers Fully Addressed by this Document

| Device   | Package | SVR<br>(Rev. 2.0) | SVR<br>(Rev. 2.1) |

|----------|---------|-------------------|-------------------|

| MPC8358E | TBGA    | 0x804A_0020       | 0x804A_0021       |

| MPC8358  | TBGA    | 0x804B_0020       | 0x804B_0021       |

# 25 Document Revision History

This table provides a revision history for this document.

## Table 82. Revision History

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5              | 09/2011 | <ul> <li>Section 2.2.1, "Power-Up Sequencing", added the current limitation "3A to 5A" for the excessive current.</li> <li>Section 2.1.2, "Power Supply Voltage Specification, Updated the Characteristic for TBGA (MPC8358 &amp; MPC8360 Device) with specific frequency for Core and PLL voltages.</li> <li>Added table footnote 3 to Table 2.</li> <li>Applied table footnotes 1 and 2 to Table 10.</li> <li>Removed table footnotes from Table 19.</li> <li>Applied table footnotes 8 and 9 to Table 40.</li> <li>Applied table footnotes 2 and 3 to Table 41.</li> <li>Applied table footnotes from Table 46.</li> <li>Applied table footnote to last three rows of Table 65.</li> </ul> |

| 4              | 01/2011 | <ul> <li>Updated references to the LCRR register throughout</li> <li>Removed references to DDR DLL mode in Section 6.2.2, "DDR and DDR2 SDRAM Output AC Timing Specifications."</li> <li>Changed "Junction-to-Case" to "Junction-to-Ambient" in Section 22.2.4, "Heat Sinks and Junction-to-Ambient Thermal Resistance," and Table 78, "Heat Sinks and Junction-to-Ambient Thermal Resistance of TBGA Package," titles.</li> </ul>                                                                                                                                                                                                                                                            |