Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, I²S, POR, PWM, WDT                                               |

| Number of I/O              | 51                                                                    |

| Program Memory Size        | 384KB (384K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 64K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f302rdt7 |

| Table 47. | Asynchronous non-multiplexed SRAM/PSRAM/NOR write timings                   | 92  |

|-----------|-----------------------------------------------------------------------------|-----|

| Table 48. | Asynchronous non-multiplexed SRAM/PSRAM/NOR write-NWAIT timings             | 93  |

| Table 49. | Asynchronous multiplexed PSRAM/NOR read-NWAIT timings                       | 93  |

| Table 50. | Asynchronous multiplexed PSRAM/NOR read timings                             | 94  |

| Table 51. | Asynchronous multiplexed PSRAM/NOR write timings                            | 96  |

| Table 52. | Asynchronous multiplexed PSRAM/NOR write-NWAIT timings                      | 96  |

| Table 53. | Synchronous multiplexed NOR/PSRAM read timings                              | 97  |

| Table 54. | Synchronous multiplexed PSRAM write timings                                 | 99  |

| Table 55. | Synchronous non-multiplexed NOR/PSRAM read timings                          | 100 |

| Table 56. | Synchronous non-multiplexed PSRAM write timings                             | 102 |

| Table 57. | Switching characteristics for PC Card/CF read and write cycles              |     |

|           | in attribute/common space                                                   | 103 |

| Table 58. | Switching characteristics for PC Card/CF read and write cycles in I/O space | 106 |

| Table 59. | Switching characteristics for NAND Flash read cycles                        | 109 |

| Table 60. | Switching characteristics for NAND Flash write cycles                       | 109 |

| Table 61. | EMS characteristics                                                         | 110 |

| Table 62. | EMI characteristics                                                         | 111 |

| Table 63. | ESD absolute maximum ratings                                                | 111 |

| Table 64. | Electrical sensitivities                                                    | 112 |

| Table 65. | I/O current injection susceptibility                                        | 112 |

| Table 66. | I/O static characteristics                                                  | 113 |

| Table 67. | Output voltage characteristics                                              | 116 |

| Table 68. | I/O AC characteristics                                                      | 117 |

| Table 69. | NRST pin characteristics                                                    | 118 |

| Table 70. | TIMx characteristics                                                        | 119 |

| Table 71. | IWDG min/max timeout period at 40 kHz (LSI)                                 |     |

| Table 72. | WWDG min-max timeout value @72 MHz (PCLK)                                   | 120 |

| Table 73. | I2C analog filter characteristics                                           | 121 |

| Table 74. | SPI characteristics                                                         | 121 |

| Table 75. | I <sup>2</sup> S characteristics                                            | 124 |

| Table 76. | USB startup time                                                            | 126 |

| Table 77. | USB DC electrical characteristics                                           | 126 |

| Table 78. | USB: full-speed electrical characteristics                                  | 126 |

| Table 79. | ADC characteristics                                                         | 127 |

| Table 80. | Maximum ADC RAIN                                                            |     |

| Table 81. | ADC accuracy - limited test conditions, 100-/144-pin packages               | 132 |

| Table 82. | ADC accuracy, 100-pin/144-pin packages                                      |     |

| Table 83. | ADC accuracy - limited test conditions, 64-pin packages                     | 135 |

| Table 84. | ADC accuracy, 64-pin packages                                               |     |

| Table 85. | ADC accuracy at 1MSPS                                                       |     |

| Table 86. | DAC characteristics                                                         |     |

| Table 87. | Comparator characteristics                                                  |     |

| Table 88. | Operational amplifier characteristics                                       |     |

| Table 89. | TS characteristics                                                          |     |

| Table 90. | Temperature sensor calibration values                                       |     |

| Table 91. | V <sub>BAT</sub> monitoring characteristics                                 |     |

| Table 92. | LQFP144 mechanical data                                                     |     |

| Table 93. | UFBGA100 package mechanical data                                            |     |

| Table 94. | UFBGA100 recommended PCB design rules (0.5 mm pitch BGA)                    |     |

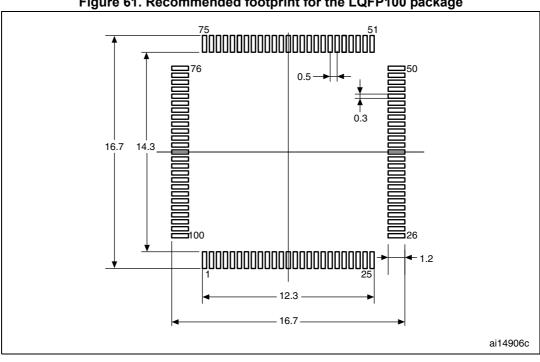

| Table 95. | LQPF100 package mechanical data                                             |     |

| Table 96. | WLCSP100 package mechanical data                                            |     |

| Table 97. | WLCSP100 recommended PCB design rules (0.4 mm pitch)                        | 159 |

## List of tables

## STM32F302xD STM32F302xE

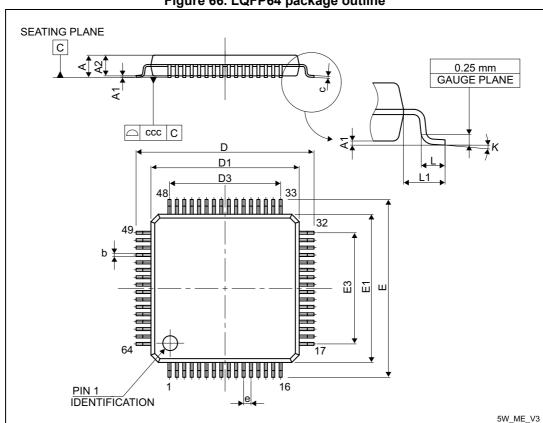

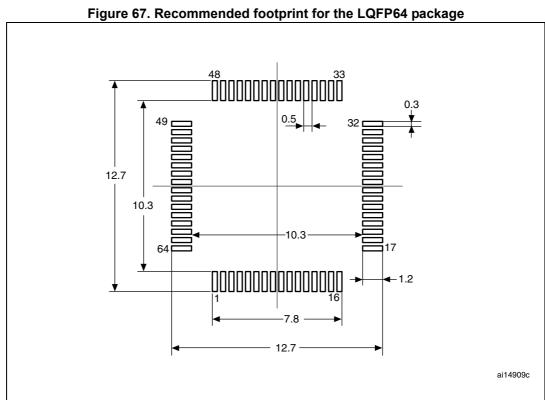

| Table 98.  | LQFP64 package mechanical data  | 160 |

|------------|---------------------------------|-----|

|            | Package thermal characteristics |     |

| Table 100. | Ordering information scheme     | 166 |

| Table 101. | Document revision history       | 167 |

## 3.7.4 Low-power modes

The STM32F302xD/E supports three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and wake up the CPU when an interrupt/event occurs.

Stop mode

Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

The device can be woken up from Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the PVD output, the USB wakeup, the RTC alarm, COMPx, I2Cx or U(S)ARTx.

Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and register contents are lost except for registers in the Backup domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin or an RTC alarm occurs.

The RTC, the IWDG and the corresponding clock sources are not stopped by entering Stop

or Standby mode.

Note:

#### 3.8 Interconnect matrix

Several peripherals have direct connections between them. This allows autonomous communication between peripherals, saving CPU resources thus power supply consumption. In addition, these hardware connections allow fast and predictable latency.

Interconnect Interconnect source Interconnect action destination TIMx Timers synchronization or chaining **ADC**x Conversion triggers DAC1 TIMx DMA Memory to memory transfer trigger Compx Comparator output blanking **COMPx** TIMx Timer input: OCREF\_CLR input, input capture **ADCx** TIMx Timer triggered by analog watchdog

Table 4. STM32F302xD/E peripheral interconnect matrix

- External triggers for conversion

- Input voltage reference VREF+

## 3.16 Operational amplifier (OPAMP)

The STM32F302xD/E embed two operational amplifiers (OPAMP1 and OPAMP2) with external or internal follower routing and PGA capability (or even amplifier and filter capability with external components). When an operational amplifier is selected, an external ADC channel is used to enable output measurement.

The operational amplifier features:

- 8.2 MHz bandwidth

- 0.5 mA output capability

- Rail-to-rail input/output

- In PGA mode, the gain is programmed to be 2, 4, 8 or 16.

## 3.17 Ultra-fast comparators (COMP)

The STM32F302xD/E devices embed four ultra-fast rail-to-rail comparators (COMP1, 2, 4, 6) with programmable reference voltage (internal or external) and selectable output polarity.

The reference voltage can be one of the following:

- External I/O

- DAC output pin

- Internal reference voltage or submultiple (1/4, 1/2, 3/4). Refer to *Table 23: Embedded internal reference voltage* for the value and precision of the internal reference voltage.

All comparators can wake up from STOP mode, generate interrupts and breaks for the timers.

## 3.18 Timers and watchdogs

The STM32F302xD/E include one advanced control timer, up to six general-purpose timers, one basic timer, two watchdog timers and one SysTick timer. The table below compares the features of the advanced control, general purpose and basic timers.

Table 5. Timer feature comparison

| Timer type          | Timer | Counter resolution | Counter<br>type      | Prescaler<br>factor                   | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complementary outputs |

|---------------------|-------|--------------------|----------------------|---------------------------------------|------------------------------|---------------------------------|-----------------------|

| Advanced            | TIM1  | 16-bit             | Up, Down,<br>Up/Down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | Yes                   |

| General-<br>purpose | TIM2  | 32-bit             | Up, Down,<br>Up/Down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | No                    |

| Timer type          | Timer          | Counter resolution | Counter<br>type      | Prescaler<br>factor                   | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complementary outputs |

|---------------------|----------------|--------------------|----------------------|---------------------------------------|------------------------------|---------------------------------|-----------------------|

| General-<br>purpose | TIM3, TIM4     | 16-bit             | Up, Down,<br>Up/Down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | No                    |

| General-<br>purpose | TIM15          | 16-bit             | Up                   | Any integer<br>between 1<br>and 65536 | Yes                          | 2                               | 1                     |

| General-<br>purpose | 1 TIM16. TIM17 |                    | Up                   | Any integer<br>between 1<br>and 65536 | Yes                          | 1                               | 1                     |

| Basic TIM6          |                | 16-bit             | Up                   | Any integer<br>between 1<br>and 65536 | Yes                          | 0                               | No                    |

Table 5. Timer feature comparison (continued)

Note: TIM

TIM1/2/3/4/15/16/17 can have PLL as clock source, and therefore can be clocked at 144 MHz.

## 3.18.1 Advanced timers (TIM1)

The advanced-control timer (TIM1) can be seen as a three-phase PWM multiplexed on six channels. It has complementary PWM outputs with programmable inserted dead-times. It can also be seen as a complete general-purpose timer. The four independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge or center-aligned modes) with full modulation capability (0-100%)

- One-pulse mode output

In debug mode, the advanced-control timer counter can be frozen and the PWM outputs disabled to turn off any power switches driven by these outputs.

Many features are shared with those of the general-purpose TIM timer (described in Section 3.18.2) using the same architecture, so the advanced-control timers can work together with the TIM timers via the Timer Link feature for synchronization or event chaining.

## 3.18.2 General-purpose timers (TIM2, TIM3, TIM4, TIM15, TIM16, TIM17)

There are up to six synchronizable general-purpose timers embedded in the STM32F302xD/E (see *Table 5* for differences). Each general-purpose timer can be used to generate PWM outputs, or act as a simple time base.

Drawbacks

Wakeup from Stop on address

filter is enabled.

match is not available when digital

All  $I^2C$  bus interfaces support 7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (2 addresses, 1 with configurable mask). They also include programmable analog and digital noise filters.

| -                                | Analog filter          | Digital filter                                                          |

|----------------------------------|------------------------|-------------------------------------------------------------------------|

| Pulse width of suppressed spikes | ≥ 50 ns                | Programmable length from 1 to 15 I <sup>2</sup> C peripheral clocks     |

| Benefits                         | Available in Stop mode | Extra filtering capability vs. standard requirements.     Stable length |

Table 6. Comparison of I<sup>2</sup>C analog and digital filters

In addition, they provide hardware support for SMBUS 2.0 and PMBUS 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. They also have a clock domain independent from the CPU clock, allowing the I2Cx (x=1,2,3) to wake up the MCU from Stop mode on address match.

The I<sup>2</sup>C interfaces can be served by the DMA controller.

Refer to *Table 7* for the features available in I2C1, I2C2 and I2C3.

Variations depending on

temperature, voltage, process

I<sup>2</sup>C features<sup>(1)</sup> **I2C1 I2C2 12C3** 7-bit addressing mode Χ Х Χ Χ Χ Χ 10-bit addressing mode Standard mode (up to 100 kbit/s) Х Χ Χ Fast mode (up to 400 kbit/s) Х Х Χ Fast Mode Plus with 20mA output drive I/Os (up to 1 Mbit/s) Χ Χ Х Independent clock Χ Χ Χ **SMBus** Х Χ Χ Wakeup from STOP Χ Χ Χ

Table 7. STM32F302xD/E |2C implementation

# 3.21 Universal synchronous/asynchronous receiver transmitter (USART)

The STM32F302xD/E devices have three embedded universal synchronous/asynchronous receiver transmitters (USART1, USART2 and USART3).

The USART interfaces are able to communicate at speeds of up to 9 Mbit/s.

They provide hardware management of the CTS and RTS signals, they support IrDA SIR ENDEC, the multiprocessor communication mode, the single-wire half-duplex

X = supported.

| SPI features <sup>(1)</sup> | SPI1 | SPI2 | SPI3 | SPI4 |

|-----------------------------|------|------|------|------|

| Hardware CRC calculation    | Х    | Х    | Х    | Х    |

| Rx/Tx FIFO                  | Х    | Х    | Х    | Х    |

| NSS pulse mode              | Х    | Х    | Х    | Х    |

| I <sup>2</sup> S mode       | -    | Х    | Х    | -    |

| TI mode                     | Х    | Х    | Х    | Х    |

Table 9. STM32F302xD/E SPI/I<sup>2</sup>S implementation

## 3.24 Controller area network (CAN)

The CAN is compliant with specifications 2.0A and B (active) with a bit rate up to 1 Mbit/s. It can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. It has three transmit mailboxes, two receive FIFOs with 3 stages and 14 scalable filter banks.

## 3.25 Universal serial bus (USB)

The STM32F302xD/E embeds a full-speed USB device peripheral compliant with the USB specification version 2.0. The USB interface implements a full-speed (12 Mbit/s) function interface with added support for USB 2.0 Link Power Management. It has software-configurable endpoint setting with packet memory up-to 1 Kbyte (256 bytes are used for CAN peripheral if enabled) and suspend/resume support.

The dedicated 48 MHz clock is generated from the internal main PLL (the clock source must use a HSE crystal oscillator).

## 3.26 Infrared transmitter

The STM32F302xD/E devices provide an infrared transmitter solution. The solution is based on internal connections between TIM16 and TIM17 as shown in the figure below.

TIM17 is used to provide the carrier frequency and TIM16 provides the main signal to be sent. The infrared output signal is available on PB9 or PA13.

To generate the infrared remote control signals, TIM16 channel 1 and TIM17 channel 1 must be properly configured to generate correct waveforms. All standard IR pulse modulation modes can be obtained by programming the two timers output compare channels.

<sup>1.</sup> X = supported.

# 4 Pinout and pin description

<u>\_\_\_\_\_\_</u> 64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 🗖 VDD VBAT ☐ 1 47 🗖 VSS PC13 🗖 2 PC14-OSC32\_IN ☐ 3 46 🗖 PA13 PC15-OSC32 OUT 4 45 🗖 PA12 PF0-OSC\_IN ☐ 5 44 🏻 PA11 PF1-OSC\_OUT ☐ 6 43 PA10 NRST □ 7 42 PA9 PC0 🗖 8 41 🗖 PA8 LQFP64 PC1 **□** 9 40 PC9 PC2 🗖 10 39 PC8 PC3 🗖 11 38 🗖 PC7 37 🗖 PC6 VSSA 🗖 12 36 🗖 PB15 VDDA 🗖 13 35 Þ PB14 PA0 14 PA1 🗖 15 34 🏳 PB13 PA2 33 🗖 PB12 16 \ 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

PA3 VSS VDD PA4 PA5 PA7 PC4 PC5 PB10 PB10 PB11 VSS VDD

Figure 4. STM32F302xD/E LQFP64 pinout

MS34908V1

Table 13. STM32F302xD/E pin definitions (continued)

|        | Pin number   Pin n |                  |         |                                       |          |               |       |                                                                                      |                       |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------|---------------------------------------|----------|---------------|-------|--------------------------------------------------------------------------------------|-----------------------|

| LQFP64 | LQFP100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | WLCSP100         | LQFP144 | Pin name<br>(function<br>after reset) | Pin type | I/O structure | Notes | Alternate functions                                                                  | Additional functions  |

| -      | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | F8               | 58      | PE7                                   | I/O      | ТТа           | (1)   | EVENTOUT, TIM1_ETR,<br>FMC_D4                                                        | -                     |

| -      | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | E6               | 59      | PE8                                   | I/O      | ТТа           | (1)   | EVENTOUT, TIM1_CH1N, FMC_D5                                                          | COMP4_INM             |

| -      | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                | 60      | PE9                                   | I/O      | TTa           | (1)   | EVENTOUT, TIM1_CH1, FMC_D6                                                           | -                     |

| -      | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -                | 61      | VSS                                   | S        | -             | (1)   | -                                                                                    | -                     |

| -      | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -                | 62      | VDD                                   | S        | -             | (1)   | -                                                                                    | -                     |

| -      | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                | 63      | PE10                                  | I/O      | TTa           | (1)   | EVENTOUT, TIM1_CH2N, FMC_D7                                                          | -                     |

| -      | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | H5               | 64      | PE11                                  | I/O      | TTa           | (1)   | EVENTOUT, TIM1_CH2,<br>SPI4_NSS, FMC_D8                                              | -                     |

| -      | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | G5               | 65      | PE12                                  | I/O      | TTa           | (1)   | EVENTOUT, TIM1_CH3N,<br>SPI4_SCK, FMC_D9                                             | -                     |

| -      | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                | 66      | PE13                                  | I/O      | TTa           | (1)   | EVENTOUT, TIM1_CH3,<br>SPI4_MISO, FMC_D10                                            | -                     |

| -      | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                | 67      | PE14                                  | I/O      | ТТа           | (1)   | EVENTOUT, TIM1_CH4,<br>SPI4_MOSI, TIM1_BKIN2,<br>FMC_D11                             | -                     |

| -      | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                | 68      | PE15                                  | I/O      | ТТа           | (1)   | EVENTOUT, TIM1_BKIN,<br>USART3_RX, FMC_D12                                           | -                     |

| 29     | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | K4               | 69      | PB10                                  | I/O      | TTa           | -     | TIM2_CH3, TSC_SYNC,<br>USART3_TX, EVENTOUT                                           | -                     |

| 30     | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | K3               | 70      | PB11                                  | I/O      | TTa           | -     | TIM2_CH4, TSC_G6_IO1,<br>USART3_RX, EVENTOUT                                         | ADC12_IN14, COMP6_INP |

| 31     | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | K1,<br>J1,<br>K2 | 71      | VSS                                   | S        | -             | -     | -                                                                                    | -                     |

| 32     | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | J5               | 72      | VDD                                   | S        | -             | -     | -                                                                                    | -                     |

| 33     | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | J4               | 73      | PB12                                  | I/O      | ТТа           | (5)   | TSC_G6_IO2,<br>I2C2_SMBAL,<br>SPI2_NSS/I2S2_WS,<br>TIM1_BKIN, USART3_CK,<br>EVENTOUT | -                     |

Pinout and pin description

Table 14. STM32F302xD/E alternate function mapping (continued)

|        |      | AF0    | AF1                         | AF2                                         | AF3              | AF4                         | AF5                                                            | AF6                                                | AF7                            | AF8                            | AF9               | AF10              | AF11   | AF12          | AF13 | AF14 | AF15  |

|--------|------|--------|-----------------------------|---------------------------------------------|------------------|-----------------------------|----------------------------------------------------------------|----------------------------------------------------|--------------------------------|--------------------------------|-------------------|-------------------|--------|---------------|------|------|-------|

| ı      | Port | SYS_AF | TIM2/15/<br>16/17/E<br>VENT | I2C3/TIM1<br>/2/3/4/8/20<br>/15/GPCO<br>MP1 | 12C3//15/<br>TSC | I2C1/2/TI<br>M1/8/16/<br>17 | SPI1/SPI2<br>/I2S2/SPI3<br>/I2S3/SPI4<br>/UART4/5/<br>Infrared | SPI2/I2S2/<br>SPI3/I2S3/<br>TIM1/8/20/<br>Infrared | USART1/2<br>/3/CAN/GP<br>COMP6 | I2C3/GPC<br>OMP1/2/3/<br>4/5/6 | CAN/TIM1<br>/8/15 | TIM2/3/<br>4/8/17 | TIM1/8 | FSMC<br>/TIM1 | -    | -    | EVENT |

|        | PH0  | -      | EVENT<br>OUT                | -                                           | -                | -                           | -                                                              | -                                                  | -                              | -                              | -                 | -                 | -      | FMC_A0        | -    | -    | -     |

| Port H | PH1  | -      | EVENT<br>OUT                | -                                           | -                | -                           | -                                                              | -                                                  | -                              | -                              | -                 | -                 | -      | FMC_A1        | -    | -    | -     |

|        | PH2  | -      | EVENT<br>OUT                | -                                           | -                | -                           | -                                                              | -                                                  | -                              | -                              | -                 | -                 | -      | -             | -    | -    | -     |

Table 33. Peripheral current consumption (continued)

|                 | Typical consumption <sup>(1)</sup> |        |

|-----------------|------------------------------------|--------|

| Peripheral      | I <sub>DD</sub>                    | Unit   |

| APB1-Bridge (3) | 6.7                                |        |

| TIM2            | 39.2                               |        |

| TIM3            | 30.8                               |        |

| TIM4            | 31.3                               |        |

| TIM6            | 4.3                                |        |

| WWDG            | 1.3                                |        |

| SPI2            | 33.6                               |        |

| SPI3            | 33.9                               |        |

| USART2          | 39.3                               |        |

| USART3          | 39.3                               |        |

| UART4           | 29.8                               | μA/MHz |

| UART5           | 27.0                               |        |

| I2C1            | 6.7                                |        |

| 12C2            | 6.4                                |        |

| USB             | 14.7                               |        |

| CAN             | 25.6                               |        |

| PWR             | 3.7                                |        |

| DAC             | 22.1                               |        |

| I2C3            | 6.8                                |        |

The power consumption of the analog part (I<sub>DDA</sub>) of peripherals such as ADC, DAC, Comparators, OpAmp is not included. Refer to the tables of characteristics in the subsequent sections.

<sup>2.</sup> BusMatrix is automatically active when at least one master is ON (CPU, DMA1 or DMA2).

<sup>3.</sup> The APBx bridge is automatically active when at least one peripheral is ON on the same bus.

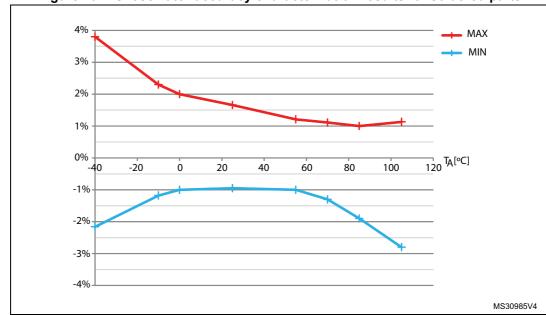

Figure 19. HSI oscillator accuracy characterization results for soldered parts

Low-speed internal (LSI) RC oscillator

Table 41. LSI oscillator characteristics<sup>(1)</sup>

| Symbol                              | Parameter                        | Min | Тур  | Max | Unit |

|-------------------------------------|----------------------------------|-----|------|-----|------|

| f <sub>LSI</sub>                    | Frequency                        | 30  | 40   | 50  | kHz  |

| t <sub>su(LSI)</sub> <sup>(2)</sup> | LSI oscillator startup time      | -   | -    | 85  | μs   |

| I <sub>DD(LSI)</sub> <sup>(2)</sup> | LSI oscillator power consumption | -   | 0.75 | 1.2 | μA   |

<sup>1.</sup>  $V_{DDA}$  = 3.3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

## 6.3.9 PLL characteristics

The parameters given in *Table 42* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 19*.

**Table 42. PLL characteristics**

| Symbol               | Parameter                      |                   | Unit |                    |       |

|----------------------|--------------------------------|-------------------|------|--------------------|-------|

| Symbol               | raiailletei                    | Min               | Тур  | Max                | Oilit |

| f                    | PLL input clock <sup>(1)</sup> | 1 <sup>(2)</sup>  | -    | 24 <sup>(2)</sup>  | MHz   |

| f <sub>PLL_IN</sub>  | PLL input clock duty cycle     | 40 <sup>(2)</sup> | -    | 60 <sup>(2)</sup>  | %     |

| f <sub>PLL_OUT</sub> | PLL multiplier output clock    | 16 <sup>(2)</sup> | -    | 72                 | MHz   |

| t <sub>LOCK</sub>    | PLL lock time                  | -                 | -    | 200 <sup>(2)</sup> | μs    |

| Jitter               | Cycle-to-cycle jitter          | -                 | -    | 300 <sup>(2)</sup> | ps    |

Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by f<sub>PLL\_OUT</sub>.

5//

<sup>2.</sup> Guaranteed by design, not tested in production.

<sup>2.</sup> Guaranteed by design, not tested in production.

**Symbol Parameter** Min Max Unit FMC CLK period 2THCLK-1 t<sub>w(CLK)</sub> FMC CLK low to FMC NEx low (x=0..2) 6 t<sub>d(CLKL-NExL)</sub> FMC CLK high to FMC NEx high THCLK+1.5 t<sub>d(CLKH-NExH)</sub> (x = 0...2)FMC CLK low to FMC NADV low 7.5 t<sub>d(CLKL-NADVL)</sub> FMC CLK low to FMC NADV high 0 t<sub>d(CLKL-NADVH)</sub> FMC CLK low to FMC Ax valid 6.5 t<sub>d(CLKL-AV)</sub> (x=16...25)FMC CLK high to FMC Ax invalid 0 t<sub>d(CLKH-AIV)</sub> ns (x=16...25)FMC CLK low to FMC NWE low 0 t<sub>d</sub>(CLKL-NWEL) FMC CLK high to FMC NWE high THCLK+2 t<sub>d(CLKH-NWEH)</sub> FMC D[15:0] valid data after FMC CLK 7.5 t<sub>d(CLKL-Data)</sub> FMC CLK low to FMC NBL low 7 t<sub>d</sub>(CLKL-NBLL) FMC CLK high to FMC NBL high THCLK+0.5 \_ t<sub>d(CLKH-NBLH)</sub> FMC NWAIT valid before FMC CLK high 2 t<sub>su(NWAIT-CLKH)</sub> FMC NWAIT valid after FMC CLK high 4 th(CLKH-NWAIT)

Table 56. Synchronous non-multiplexed PSRAM write timings<sup>(1)</sup>

#### PC Card/CompactFlash controller waveforms and timings

Figure 28 to Figure 33 present the PC Card/Compact Flash controller waveforms, and Table 57 to Table 58 provide the corresponding timings. The results shown in this table are obtained with the following FSMC configuration:

- COM.FMC SetupTime = 0x04;

- COM.FMC\_WaitSetupTime = 0x07;

- COM.FMC\_HoldSetupTime = 0x04;

- COM.FMC HiZSetupTime = 0x05;

- ATT.FMC\_SetupTime = 0x04;

- ATT.FMC WaitSetupTime = 0x07;

- ATT.FMC HoldSetupTime = 0x04;

- ATT.FMC\_HiZSetupTime = 0x05;

- IO.FMC SetupTime = 0x04;

- IO.FMC WaitSetupTime = 0x07;

- IO.FMC HoldSetupTime = 0x04;

- IO.FMC HiZSetupTime = 0x05;

- TCLRSetupTime = 0;

- TARSetupTime = 0.

In all timing tables, the THCLK is the HCLK clock period.

<sup>1.</sup> Based on characterization, not tested in production.

#### 6.3.12 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

## Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling two LEDs through I/O ports), the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 61*. They are based on the EMS levels and classes defined in application note AN1709.

Level/ **Symbol Parameter Conditions** Class  $V_{DD} = 3.3 \text{ V, LQFP144, T}_{A} = +25^{\circ}\text{C,}$ Voltage limits to be applied on any I/O pin to f<sub>HCLK</sub> = 72 MHz 2B  $V_{FESD}$ induce a functional disturbance conforms to IEC 61000-4-2  $V_{DD} = 3.3 \text{ V, LQFP144, T}_{A} = +25^{\circ}\text{C,}$ Fast transient voltage burst limits to be f<sub>HCLK</sub> = 72 MHz  $\mathsf{V}_{\mathsf{EFTB}}$ applied through 100 pF on V<sub>DD</sub> and V<sub>SS</sub> 4A pins to induce a functional disturbance conforms to IEC 61000-4-4

**Table 61. EMS characteristics**

## Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and pre qualification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- · Corrupted program counter

- Unexpected reset

110/168

Critical Data corruption (control registers...)

DocID026900 Rev 4

| Symbol           | Parameter                                         | Conditions                                                                   | onditions Min |    | Max  | Unit |

|------------------|---------------------------------------------------|------------------------------------------------------------------------------|---------------|----|------|------|

|                  |                                                   | TC, FT and FTf I/O<br>TTa I/O in digital mode $V_{SS} \le V_{IN} \le V_{DD}$ | -             | -  | ±0.1 |      |

| l <sub>lkg</sub> | Input leakage current <sup>(3)</sup>              | TTa I/O in digital mode  V <sub>DD</sub> ≤V <sub>IN</sub> ≤V <sub>DDA</sub>  | -             | -  | 1    |      |

|                  |                                                   | TTa I/O in analog mode V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DDA</sub>    | -             | -  | ±0.2 | μA   |

|                  |                                                   | FT and FTf I/O <sup>(4)</sup><br>V <sub>DD</sub> ≤V <sub>IN</sub> ≤5 V       | -             | -  | 10   |      |

| R <sub>PU</sub>  | Weak pull-up equivalent resistor <sup>(5)</sup>   | $V_{IN} = V_{SS}$                                                            | 25            | 40 | 55   | kΩ   |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(5)</sup> | $V_{IN} = V_{DD}$                                                            | 25            | 40 | 55   | kΩ   |

| C <sub>IO</sub>  | I/O pin capacitance                               | -                                                                            | -             | 5  | -    | pF   |

Table 66. I/O static characteristics (continued)

- 1. Data based on design simulation.

- 2. Tested in production.

- Leakage could be higher than the maximum value, if negative current is injected on adjacent pins. Refer to Table 65: I/O current injection susceptibility.

- 4. To sustain a voltage higher than  $V_{DD}$  +0.3 V, the internal pull-up/pull-down resistors must be disabled.

- Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimum (~10% order).

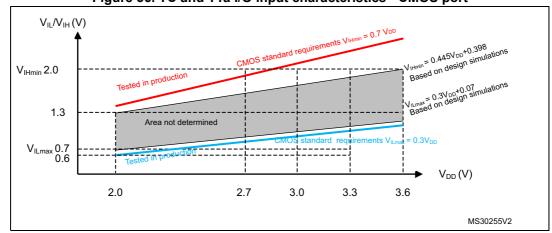

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 36* and *Figure 37* for standard I/Os.

Figure 36. TC and TTa I/O input characteristics - CMOS port

47/

| Table 75. I <sup>2</sup> S characteristics <sup>(1)</sup> |                                |                                        |          |                       |      |  |  |  |

|-----------------------------------------------------------|--------------------------------|----------------------------------------|----------|-----------------------|------|--|--|--|

| Symbol                                                    | Parameter                      | Conditions                             | Min      | Max                   | Unit |  |  |  |

| f <sub>MCK</sub>                                          | I2S Main clock output          | -                                      | 256 x 8K | 256xFs <sup>(2)</sup> | MHz  |  |  |  |

| £                                                         | ICC clock fraguency            | Master data: 32 bits                   | -        | 64xFs                 | MHz  |  |  |  |

| f <sub>CK</sub>                                           | I2S clock frequency            | Slave data: 32 bits                    | -        | 64xFs                 | -    |  |  |  |

| D <sub>CK</sub>                                           | I2S clock frequency duty cycle | Slave receiver                         | 30       | 70                    | %    |  |  |  |

| t <sub>v(WS)</sub>                                        | WS valid time                  | Master mode                            | -        | 20                    |      |  |  |  |

| t <sub>h(WS)</sub>                                        | WS hold time                   | Master mode                            | 2        | -                     |      |  |  |  |

| t <sub>su(WS)</sub>                                       | WS setup time                  | Slave mode                             | 0        | -                     |      |  |  |  |

| t <sub>h(WS)</sub>                                        | WS hold time                   | Slave mode                             | 4        | -                     |      |  |  |  |

| t <sub>su(SD_MR)</sub>                                    | Data input setup time          | Master receiver                        | 1        | -                     |      |  |  |  |

| t <sub>su(SD_SR)</sub>                                    | - Data input setup time        | Slave receiver                         | 1        | -                     |      |  |  |  |

| t <sub>h(SD_MR)</sub>                                     | Data input hold time           | Master receiver                        | 8        | -                     |      |  |  |  |

| t <sub>h(SD_SR)</sub>                                     |                                | Slave receiver                         | 2.5      | -                     | ns   |  |  |  |

| t <sub>v(SD_ST)</sub>                                     | - Data output valid time       | Slave transmitter (after enable edge)  | -        | 50                    |      |  |  |  |

| t <sub>v(SD_MT)</sub>                                     | - Data output valid time       | Master transmitter (after enable edge) | -        | 22                    |      |  |  |  |