Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                |

|----------------------------|---------------------------------------------------------------------------------------|

| Core Processor             | 78K/0                                                                                 |

| Core Size                  | 8-Bit                                                                                 |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                                    |

| Number of I/O              | 23                                                                                    |

| Program Memory Size        | 8KB (8K x 8)                                                                          |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | <u> </u>                                                                              |

| RAM Size                   | 512 x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 4x10b                                                                             |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 30-LSSOP (0.240", 6.10mm Width)                                                       |

| Supplier Device Package    | -                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0500amc-cab-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# (2) Non-port functions (2/2): 78K0/KD2

| Function Na           | ame I/O | Function                                                                                                                                                     | After Reset | Alternate Function               |

|-----------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------|

| T1000                 | Input   | External count clock input to 16-bit timer/event counter 00<br>Capture trigger input to capture registers (CR000, CR010) of<br>16-bit timer/event counter 00 | Input port  | P00                              |

| TI010                 |         | Capture trigger input to capture register (CR000) of 16-bit timer/event counter 00                                                                           |             | P01/TO00                         |

| TI50                  | Input   | External count clock input to 8-bit timer/event counter 50                                                                                                   | Input port  | P17/TO50                         |

| TI51                  |         | External count clock input to 8-bit timer/event counter 51                                                                                                   |             | P33/TO51/INTP4                   |

| ТО00                  | Output  | 16-bit timer/event counter 00 output                                                                                                                         | Input port  | P01/TI010                        |

| TO50                  | Output  | 8-bit timer/event counter 50 output                                                                                                                          | Input port  | P17/TI50                         |

| TO51                  |         | 8-bit timer/event counter 51 output                                                                                                                          |             | P33/TI51/INTP4                   |

| TOH0                  |         | 8-bit timer H0 output                                                                                                                                        |             | P15                              |

| TOH1                  |         | 8-bit timer H1 output                                                                                                                                        |             | P16/INTP5                        |

| R> X1                 | -       | Connecting resonator for main system clock                                                                                                                   | Input port  | P121/OCD0A <sup>Note</sup>       |

| X2                    | -       |                                                                                                                                                              |             | P122/EXCLK/OCD0B <sup>Note</sup> |

| EXCLK                 | Input   | External clock input for main system clock                                                                                                                   | Input port  | P122/X2/OCD0B <sup>Note</sup>    |

| R> XT1                | -       | Connecting resonator for subsystem clock                                                                                                                     | Input port  | P123                             |

| XT2                   | -       |                                                                                                                                                              | Input port  | P124/EXCLKS                      |

| EXCLKS                | Input   | External clock input for subsystem clock                                                                                                                     | Input port  | P124/XT2                         |

| VDD                   | -       | Positive power supply for pins other than P20 to P27                                                                                                         | -           | -                                |

| R> AV <sub>REF</sub>  | -       | A/D converter reference voltage input and positive power supply for P20 to P27 and A/D converter                                                             | _           | -                                |

| Vss                   | -       | Ground potential for pins other than P20 to P27                                                                                                              | -           | -                                |

| AVss                  | -       | A/D converter ground potential. Make the same potential as Vss.                                                                                              | -           | -                                |

| OCD0A <sup>Note</sup> | Input   | Connection for on-chip debug mode setting pins                                                                                                               | Input port  | P121/X1                          |

| OCD1A <sup>Note</sup> |         | (µPD78F0527D and 78F0527DA only)                                                                                                                             |             | P31/INTP2                        |

| OCD0B <sup>Note</sup> | -       | 1                                                                                                                                                            |             | P122/X2/EXCLK                    |

| OCD1B <sup>Note</sup> |         |                                                                                                                                                              |             | P32/INTP3                        |

Note  $\mu$ PD78F0527D and 78F0527DA (product with on-chip debug function) only

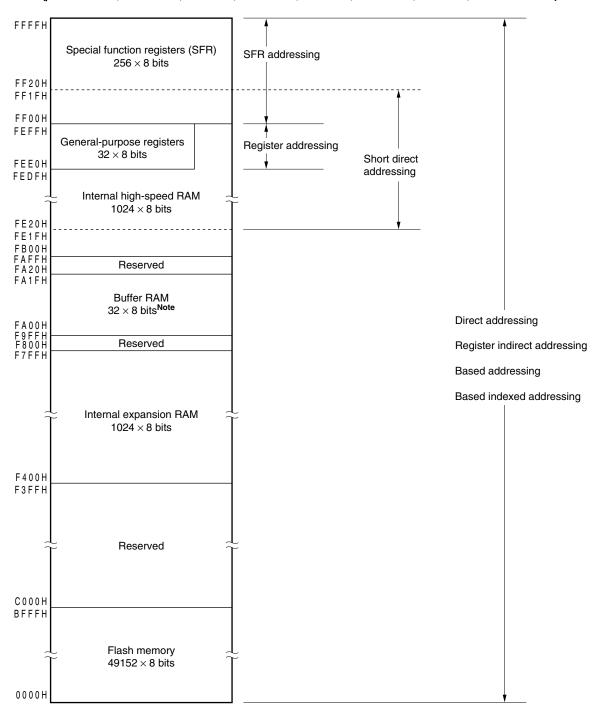

# Figure 3-16. Correspondence Between Data Memory and Addressing (*μ*PD78F0514, 78F0514A, 78F0524A, 78F0524A, 78F0534A, 78F0534A, 78F0544A, and 78F0544A)

**Note** The buffer RAM is incorporated only in the  $\mu$ PD78F0544 and 78F0544A (78K0/KF2). The area from FA00H to FA1FH cannot be used with the  $\mu$ PD78F0514, 78F0514A, 78F0524, 78F0524A, 78F0534, and 78F0534A.

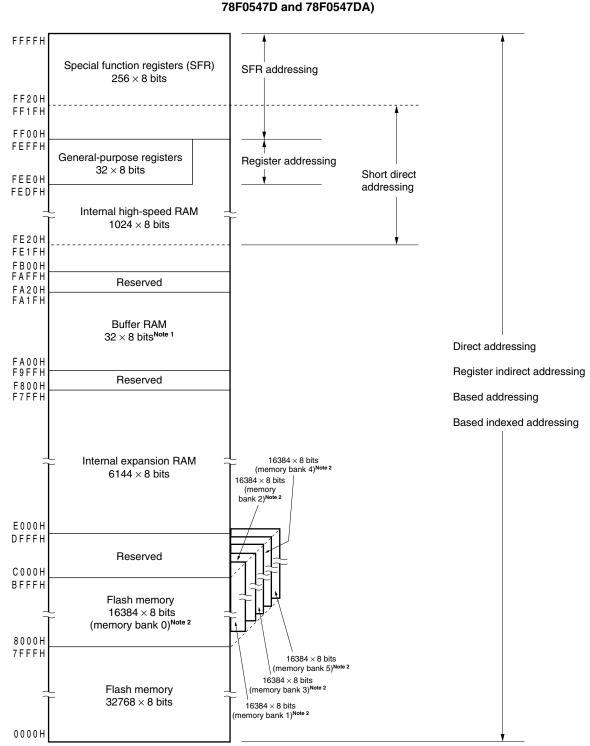

# Figure 3-19. Correspondence Between Data Memory and Addressing (μPD78F0527, 78F0527A, 78F0537, 78F0537A, 78F0547, 78F0547A, 78F0527D, 78F0527DA, 78F0537D, 78F0537DA, 78F0547D and 78F0547DA)

- **Notes 1.** The buffer RAM is incorporated only in the  $\mu$ PD78F0547, 78F0547A, 78F0547D and 78F0547DA (78K0/KF2). The area from FA00H to FA1FH cannot be used with the  $\mu$ PD78F0527, 78F0527A, 78F0527A, 78F0527DA, 78F0537D and 78F0537DA.

- 2. To branch to or address a memory bank that is not set by the memory bank select register (BANK), change the setting of the memory bank by using BANK.

RENESAS

| Address | Special Function Register (SFR) Name           | Sv    | mbol | R/W | Manip        | ulatable     | Bit Unit     | After                 | К            | К            | К            | K              | К            |

|---------|------------------------------------------------|-------|------|-----|--------------|--------------|--------------|-----------------------|--------------|--------------|--------------|----------------|--------------|

|         |                                                | ,     |      |     | 1 Bit        | 8 Bits       | 16 Bits      | Reset                 | В            | С            | D            | Е              | F            |

|         |                                                |       |      |     |              |              |              |                       | 2            | 2            | 2            | 2              | 2            |

| FFA5H   | IIC shift register 0                           | IIC0  |      | R/W | _            |              | -            | 00H                   |              |              |              | $\checkmark$   |              |

| FFA6H   | IIC control register 0                         | IICC0 |      | R/W | $\checkmark$ | $\checkmark$ | -            | 00H                   |              |              |              | $\checkmark$   | $\checkmark$ |

| FFA7H   | Slave address register 0                       | SVA0  |      | R/W | -            |              | -            | 00H                   |              |              |              | $\checkmark$   |              |

| FFA8H   | IIC clock selection register 0                 | IICCL | 0    | R/W | $\checkmark$ |              | -            | 00H                   |              |              | $\checkmark$ | $\checkmark$   |              |

| FFA9H   | IIC function expansion register 0              | IICX0 |      | R/W | $\checkmark$ |              | -            | 00H                   |              |              | $\checkmark$ | $\checkmark$   | $\checkmark$ |

| FFAAH   | IIC status register 0                          | IICS0 |      | R   | $\checkmark$ |              | -            | 00H                   |              |              | $\checkmark$ | $\checkmark$   | $\checkmark$ |

| FFABH   | IIC flag register 0                            | IICF0 |      | R/W | $\checkmark$ |              | -            | 00H                   |              |              | $\checkmark$ | $\checkmark$   | $\checkmark$ |

| FFACH   | Reset control flag register                    | RESF  | •    | R   | -            |              | -            | $00H^{Note 1}$        |              |              | $\checkmark$ | $\checkmark$   |              |

| FFB0H   | 16-bit timer counter 01                        | TM01  |      | R   | -            | -            | $\checkmark$ | 0000H                 | _            | -            | -            | Note           |              |

| FFB1H   |                                                |       |      |     |              |              |              |                       |              |              |              | 2              |              |

| FFB2H   | 16-bit timer capture/compare register          | CR00  | 1    | R/W | -            | -            | $\checkmark$ | 0000H                 | -            | -            | -            | Note           | $\checkmark$ |

| FFB3H   | 001                                            |       |      |     |              |              |              |                       |              |              |              | 2              |              |

| FFB4H   | 16-bit timer capture/compare register          | CR01  | 1    | R/W | -            | -            | $\checkmark$ | 0000H                 | -            | -            | -            | Note           | $\checkmark$ |

| FFB5H   | 011                                            |       |      |     |              |              |              |                       |              |              |              | 2              |              |

| FFB6H   | 16-bit timer mode control register 01          | тмсо  | )1   | R/W | V            | V            | -            | 00H                   | -            | -            | -            | Note<br>2      | V            |

| FFB7H   | Prescaler mode register 01                     | PRMC  | )1   | R/W | V            | V            | -            | 00H                   | _            | _            | _            | Note<br>2      | V            |

| FFB8H   | Capture/compare control register 01            | CRCC  | )1   | R/W | $\checkmark$ | $\checkmark$ | -            | 00H                   | -            | -            | -            | -<br>Note<br>2 | $\checkmark$ |

| FFB9H   | 16-bit timer output control register 01        | тосо  | 1    | R/W | $\checkmark$ | V            | -            | 00H                   | -            | _            | _            | Note           | $\checkmark$ |

| FFBAH   | 16-bit timer mode control register 00          | тмсо  | 0    | R/W | $\checkmark$ |              | _            | 00H                   |              |              |              | √              |              |

| FFBBH   | Prescaler mode register 00                     | PRMC  | 00   | R/W | $\checkmark$ |              | -            | 00H                   |              |              |              |                |              |

| FFBCH   | Capture/compare control register 00            | CRCC  | 0    | R/W | $\checkmark$ |              | _            | 00H                   |              |              |              |                |              |

| FFBDH   | 16-bit timer output control register 00        | TOCO  | 0    | R/W |              |              | _            | 00H                   |              |              |              |                |              |

| FFBEH   | Low-voltage detection register                 | LVIM  |      | R/W | $\checkmark$ |              | _            | 00H <sup>Note 3</sup> |              |              |              |                |              |

| FFBFH   | Low-voltage detection level selection register | LVIS  |      | R/W | V            | V            | -            | 00H <sup>Note 3</sup> | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$   | $\checkmark$ |

| FFE0H   | Interrupt request flag register 0L             | IF0   | IF0L | R/W | $\checkmark$ |              |              | 00H                   |              |              |              |                |              |

| FFE1H   | Interrupt request flag register 0H             | 1     | IF0H | R/W | $\checkmark$ |              | 1            | 00H                   |              |              |              |                |              |

| FFE2H   | Interrupt request flag register 1L             | IF1   | IF1L | R/W | $\checkmark$ |              |              | 00H                   |              |              |              |                |              |

| FFE3H   | Interrupt request flag register 1H             |       | IF1H | R/W | $\checkmark$ |              | 1            | 00H                   |              |              |              |                |              |

| FFE4H   | Interrupt mask flag register 0L                | MK0   | MK0L | R/W | $\checkmark$ |              |              | FFH                   |              |              | $\checkmark$ |                |              |

| FFE5H   | Interrupt mask flag register 0H                |       | МКОН | R/W | $\checkmark$ |              | 1            | FFH                   |              | V            |              | V              |              |

| FFE6H   | Interrupt mask flag register 1L                | MK1   | MK1L | R/W | $\checkmark$ |              |              | FFH                   |              |              |              |                |              |

| FFE7H   | Interrupt mask flag register 1H                |       | MK1H | R/W |              |              | 1            | FFH                   | V            | V            |              | v              |              |

Table 3-8.

Special Function Register List (4/5)

Notes 1. The reset value of RESF varies depending on the reset source.

- 2. This register is incorporated only in products whose flash memory is at least 48 KB.

- 3. The reset values of LVIM and LVIS vary depending on the reset source.

#### • Software example

| RAMD<br>R_BNKA:<br>R_BNKN:<br>R_BNKRN:<br>RSAVEAX: | DS<br>DS                                                                       | SADDR<br>2<br>1<br>1<br>2                                                                                                | ; Secures RAM for specifying an address at the calling destination.<br>; Secures RAM for specifying a memory bank number at the calling destination.<br>; Secures RAM for saving a memory bank number at the calling source.<br>; Secures RAM for saving the AX register.                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ETRC<br>ENTRY:                                     | CSEG<br>MOV<br>MOVW<br>CALL                                                    | UNIT<br>R_BNKN,#BANKNUM TEST<br>R_BNKA,#TEST<br>!BNKCAL<br>:<br>:                                                        | ; Store the memory bank number at the calling destination in RAM.<br>; Stores the address at the calling destination in RAM.<br>; Branches to an inter-memory bank calling processing routine.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BNKC<br>BNKCAL:                                    | CSEG<br>MOVW<br>MOV<br>XCH<br>MOV<br>CALL<br>MOVW<br>XCH<br>MOV<br>MOVW<br>RET | AT 7000H<br>RSAVEAX,AX<br>A,R_BNKN<br>A,BANK<br>R_BNKRN,A<br>IBNKCALS<br>RSAVEAX,AX<br>A,R_BNKRN<br>BANK,A<br>AX,RSAVEAX | <ul> <li>; Inter-memory bank calling processing routine</li> <li>; Saves the AX register.</li> <li>; Acquires the memory bank number at the calling destination.</li> <li>; Changes the bank and acquires the memory bank number at the calling source.</li> <li>; Saves the memory bank number at the calling source to RAM.</li> <li>; Calls a subroutine to branch to the calling destination.</li> <li>; Saves the AX register.</li> <li>; Acquires the memory bank number at the calling source.</li> <li>; Specifies the memory bank number at the calling source.</li> <li>; Restores the AX register.</li> <li>; Returns to the calling source.</li> </ul> |

| BNKCALS:                                           | MOVW<br>PUSH<br>MOVW<br>RET                                                    | AX,R_BNKA<br>AX<br>AX,RSAVEAX                                                                                            | ; Specifies the address at the calling destination.<br>; Sets the address at the calling destination to stack.<br>; Restores source AX register.<br>; Branches to the calling destination.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| BN3<br>TEST:                                       | CSEG<br>MOV ····<br>:<br>RET                                                   | BANK3                                                                                                                    | ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| END                                                |                                                                                |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Remark In the software example above, multiplexed processing is not supported.

| Symbol | 7   | 6   | 5   | 4                    | 3                    | 2                    | 1                    | 0    | Address | After reset        | R/W |

|--------|-----|-----|-----|----------------------|----------------------|----------------------|----------------------|------|---------|--------------------|-----|

| P0     | 0   | 0   | 0   | 0                    | P03                  | P02                  | P01                  | P00  | FF00H   | 00H (output latch) | R/W |

|        |     |     |     |                      |                      |                      |                      |      |         |                    |     |

| P1     | P17 | P16 | P15 | P14                  | P13                  | P12                  | P11                  | P10  | FF01H   | 00H (output latch) | R/W |

|        |     |     |     |                      |                      |                      |                      |      | -       |                    |     |

| P2     | P27 | P26 | P25 | P24                  | P23                  | P22                  | P21                  | P20  | FF02H   | 00H (output latch) | R/W |

|        |     |     |     |                      |                      |                      |                      |      |         |                    |     |

| P3     | 0   | 0   | 0   | 0                    | P33                  | P32                  | P31                  | P30  | FF03H   | 00H (output latch) | R/W |

|        |     |     |     |                      |                      |                      |                      |      |         |                    |     |

| P4     | 0   | 0   | 0   | 0                    | 0                    | 0                    | P41                  | P40  | FF04H   | 00H (output latch) | R/W |

|        |     |     |     |                      |                      |                      |                      |      |         |                    |     |

| P6     | 0   | 0   | 0   | 0                    | P63                  | P62                  | P61                  | P60  | FF06H   | 00H (output latch) | R/W |

|        |     |     |     |                      |                      |                      |                      |      |         |                    |     |

| P7     | P77 | P76 | P75 | P74                  | P73                  | P72                  | P71                  | P70  | FF07H   | 00H (output latch) | R/W |

|        |     |     |     |                      |                      |                      |                      |      |         |                    |     |

| P12    | 0   | 0   | 0   | P124 <sup>Note</sup> | P123 <sup>Note</sup> | P122 <sup>Note</sup> | P121 <sup>Note</sup> | P120 | FF0CH   | 00H (output latch) | R/W |

|        |     |     |     |                      |                      |                      |                      |      |         |                    |     |

| P13    | 0   | 0   | 0   | 0                    | 0                    | 0                    | 0                    | P130 | FF0DH   | 00H (output latch) | R/W |

|        |     |     |     |                      |                      |                      |                      |      | -       |                    |     |

| P14    | 0   | 0   | 0   | 0                    | 0                    | 0                    | 0                    | P140 | FF0EH   | 00H (output latch) | R/W |

|        |     |     |     |                      |                      |                      |                      |      | -       |                    |     |

# Figure 5-36. Format of Port Register (78K0/KD2)

| Pmn | m = 0 to 4, 6, 7, 12 to 14; n = 0 to 7 |                                 |  |  |

|-----|----------------------------------------|---------------------------------|--|--|

|     | Output data control (in output mode)   | Input data read (in input mode) |  |  |

| 0   | Output 0                               | Input low level                 |  |  |

| 1   | Output 1                               | Input high level                |  |  |

Note "0" is always read from the output latch of P121 to P124 if the pin is in the external clock input mode.

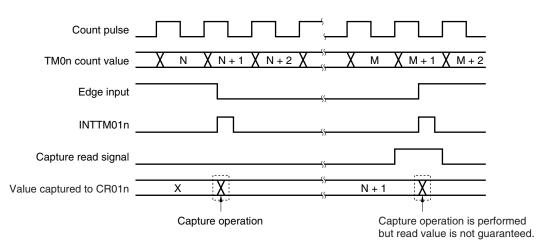

## (4) Timing of holding data by capture register

(a) When the valid edge is input to the TI00n/TI01n pin and the reverse phase of the TI00n pin is detected while CR00n/CR01n is read, CR01n performs a capture operation but the read value of CR00n/CR01n is not guaranteed. At this time, an interrupt signal (INTTM00n/INTTM01n) is generated when the valid edge of the TI00n/TI01n pin is detected (the interrupt signal is not generated when the reverse-phase edge of the TI00n pin is detected).

When the count value is captured because the valid edge of the TI00n/TI01n pin was detected, read the value of CR00n/CR01n after INTTM00n/INTTM01n is generated.

(b) The values of CR00n and CR01n are not guaranteed after 16-bit timer/event counter 0n stops.

## (5) Setting valid edge

Set the valid edge of the TI00n pin while the timer operation is stopped (TMC0n3 and TMC0n2 = 00). Set the valid edge by using ES0n0 and ES0n1.

#### (6) Re-triggering one-shot pulse

Make sure that the trigger is not generated while an active level is being output in the one-shot pulse output mode. Be sure to input the next trigger after the current active level is output.

- **Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

- n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

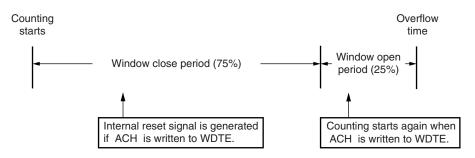

## 11.4.3 Setting window open period of watchdog timer

Set the window open period of the watchdog timer by using bits 6 and 5 (WINDOW1, WINDOW0) of the option byte (0080H). The outline of the window is as follows.

- If "ACH" is written to WDTE during the window open period, the watchdog timer is cleared and starts counting again.

- Even if "ACH" is written to WDTE during the window close period, an abnormality is detected and an internal reset signal is generated.

Example: If the window open period is 25%

# Caution The first writing to WDTE after a reset release clears the watchdog timer, if it is made before the overflow time regardless of the timing of the writing, and the watchdog timer starts counting again.

The window open period to be set is as follows.

| WINDOW1 | WINDOW0 | Window Open Period of Watchdog Timer |

|---------|---------|--------------------------------------|

| 0       | 0       | 25%                                  |

| 0       | 1       | 50%                                  |

| 1       | 0       | 75%                                  |

| 1       | 1       | 100%                                 |

#### Table 11-4. Setting Window Open Period of Watchdog Timer

Cautions 1. The combination of WDCS2 = WDCS1 = WDCS0 = 0 and WINDOW1 = WINDOW0 = 0 is prohibited.

- 2. Setting WINDOW1 = WINDOW0 = 0 is prohibited when using the watchdog timer at 1.8 V  $\leq$  V<sub>DD</sub> < 2.7 V.

- 3. The watchdog timer continues its operation during self-programming and EEPROM emulation of the flash memory. During processing, the interrupt acknowledge time is delayed. Set the overflow time and window size taking this delay into consideration.

# CHAPTER 17 SERIAL INTERFACE CSIA0

|                  | 78K0/KB2 | 78K0/KC2 | 78K0/KD2 | 78K0/KE2 | 78K0/KF2 |

|------------------|----------|----------|----------|----------|----------|

| Serial interface |          | -        | -        |          |          |

| CSIA0            |          |          |          |          |          |

#### **Remark** $\sqrt{:}$ Mounted, -: Not mounted

# 17.1 Functions of Serial Interface CSIA0

Serial interface CSIA0 has the following three modes.

## (1) Operation stop mode

This mode is used when serial communication is not performed and can enable a reduction in the power consumption.

For details, see 17.4.1 Operation stop mode.

#### (2) 3-wire serial I/O mode (MSB/LSB-first selectable)

This mode is to communicate data successively in 8-bit units, by using three lines: serial clock (SCKA0) and serial data (SIA0 and SOA0) lines.

The processing time of data communication can be shortened in the 3-wire serial I/O mode because transmission and reception can be simultaneously executed.

In addition, whether 8-bit data is communicated MSB or LSB first can be specified, so this interface can be connected to any device.

For details, see 17.4.2 3-wire serial I/O mode.

#### (3) 3-wire serial I/O mode with automatic transmit/receive function (MSB/LSB-first selectable)

This mode is used to communicate data continuously in 8-bit units using three lines: a serial clock line (SCKA0) and two serial data lines (SIA0 and SOA0).

The processing time of data communication can be shortened in the 3-wire serial I/O mode with automatic transmit/receive function because transmission and reception can be simultaneously executed.

In addition, whether 8-bit data is communicated MSB or LSB first can be specified, so this interface can be connected to any device.

Data can be communicated to/from a display driver etc. without using software since a 32-byte transfer buffer RAM is incorporated. Also, the incorporation of handshake pins (STB0, BUSY0) used in the master mode has made connection to peripheral ICs easy.

For details, see 17.4.3 3-wire serial I/O mode with automatic transmit/receive function.

| BUSYE0 | Busy signal detection enable/disable                                            |

|--------|---------------------------------------------------------------------------------|

| 0      | Busy signal detection disabled (input via BUSY0 pin is ignored)                 |

| 1      | Busy signal detection enabled and communication wait by busy signal is executed |

# Figure 17-3. Format of Serial Status Register 0 (CSIS0) (2/2)

| BUSYLV0 <sup>Note 1</sup> | Busy signal active level setting |

|---------------------------|----------------------------------|

| 0                         | Low level                        |

| 1                         | High level                       |

| ERRE0 <sup>Note 2</sup> | Bit error detection enable/disable |

|-------------------------|------------------------------------|

| 0                       | Error detection disabled           |

| 1                       | Error detection enabled            |

| ERRF0 | Bit error detection flag                                                                                                                                                                                                                                  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | <ul> <li>Bit 7 (CSIAE0) of serial operation mode specification register 0 (CSIMA0) = 0</li> <li>At reset input</li> <li>When communication is started by setting bit 0 (ATSTA0) of serial trigger register 0 (CSIT0) to 1 or writing to SIOA0.</li> </ul> |

| 1     | Bit error detected (when ERRE0 = 1, the level specified by BUSYLV0 during the data bit transfer period is detected via BUSY0 pin input).                                                                                                                  |

| TSF0 | Transfer status detection flag                                                                                                                                                                                                                                                |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | <ul> <li>Bit 7 (CSIAE0) of serial operation mode specification register 0 (CSIMA0) = 0</li> <li>At reset input</li> <li>At the end of the specified transfer</li> <li>When transfer is stopped by setting bit 1 (ATSTP0) of serial trigger register 0 (CSIT0) to 1</li> </ul> |

| 1    | From the transfer start to the end of the specified transfer                                                                                                                                                                                                                  |

Notes 1. In bit error detection by busy input, the active level specified by BUSYLV0 is detected.

- **2.** The ERRE0 setting is valid even when BUSYE0 = 0.

- Caution During transfer (TSF0 = 1), rewriting serial operation mode specification register 0 (CSIMA0), serial status register 0 (CSIS0), divisor selection register 0 (BRGCA0), automatic data transfer address point specification register 0 (ADTP0), automatic data transfer interval specification register 0 (ADTI0), and serial I/O shift register 0 (SIOA0) are prohibited. However, these registers can be read and re-written to the same value. In addition, the buffer RAM can be rewritten during transfer.

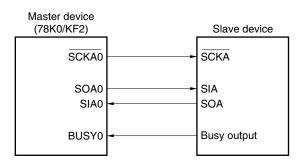

# (4) Synchronization control

Busy control and strobe control are functions used to synchronize transmission/reception between the master device and a slave device.

By using these functions, a shift in bits being transmitted or received can be detected.

## (a) Busy control option

Busy control is a function to keep the serial transmission/reception by the master device waiting while the busy signal output by a slave device to the master is active.

When using this busy control option, the following conditions must be satisfied.

- Bit 6 (ATE0) of serial operation mode specification register 0 (CSIMA0) is set to 1.

- Bit 4 (BUSYE0) of serial status register 0 (CSIS0) is set to 1.

Figure 17-23 shows the system configuration of the master device and slave device when the busy control option is used.

## Figure 17-23. System Configuration When Busy Control Option Is Used

The master device inputs the busy signal output by the slave device to the BUSY0/BUZ/INTP7/P141 pin. The master device samples the input busy signal in synchronization with the falling of the serial clock. Even if the busy signal becomes active while 8-bit data is being transmitted or received, transmission/reception by the master is not kept waiting. If the busy signal is active at the rising edge of the serial clock one clock after completion of transmission/reception of the 8-bit data, the busy input becomes valid. After that, the master transmission/reception is kept waiting while the busy signal is active.

The active level of the busy signal is set by bit 3 (BUSYLV0) of CSIS0.

BUSYLV0 = 1: Active-high BUSYLV0 = 0: Active-low

When using the busy control option, select the master mode. Control with the busy signal cannot be implemented in the slave mode.

Figure 17-24 shows the example of the operation timing when the busy control option is used.

Caution Busy control cannot be used simultaneously with the interval time control function of automatic data transfer interval specification register 0 (ADTI0).

# (b) Start ~ Address ~ Data ~ Start ~ Address ~ Data ~ Stop (restart)

# (i) When WTIM0 = 0

|                                                     | STT0 = 1<br>↓                                                                                         |                                              |                           |                                       |                       |         |                                     |     |     |          | SP  | T0 = 1<br>↓ | I  |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------------------|---------------------------------------|-----------------------|---------|-------------------------------------|-----|-----|----------|-----|-------------|----|

| ST                                                  | AD6 to AD0                                                                                            | R/W                                          | ACK                       | D7 to D0                              | ACK                   | ST      | AD6 to AD0                          | R/W | ĀCK | D7 to D0 | ACk | K SF        | 2  |

|                                                     |                                                                                                       |                                              |                           | 1 4                                   | 2                     | 3       |                                     |     |     | 4        | ▲5  | ▲6          | ∆7 |

| ▲2: 110<br>▲3: 110<br>▲4: 110<br>▲5: 110<br>▲6: 110 | CS0 = 1000×<br>CS0 = 1000×<br>CS0 = 1000×<br>CS0 = 1000×<br>CS0 = 1000×<br>CS0 = 1000×<br>CS0 = 00000 | 000B (<br>×00B (<br>110B<br>000B (<br>×00B ( | Clear<br>Sets \           | s WTIM0 to<br>WTIM0 to 1 <sup>*</sup> | 0 <sup>Note 2</sup> , | sets \$ | STT0 to 1)                          |     |     |          |     |             |    |

| Notes                                               | interrupt<br>2. Clear W                                                                               | t reque:<br>TIM0 to<br>erate a               | st sigi<br>o 0 to<br>stop | nal.<br>restore the<br>condition, s   | origina               | al sett | to 1 and ch<br>ting.<br>to 1 and ch |     |     |          |     |             |    |

| Rema                                                |                                                                                                       |                                              | l only                    | ed<br>when SPIE(                      | 0 = 1                 |         |                                     |     |     |          |     |             |    |

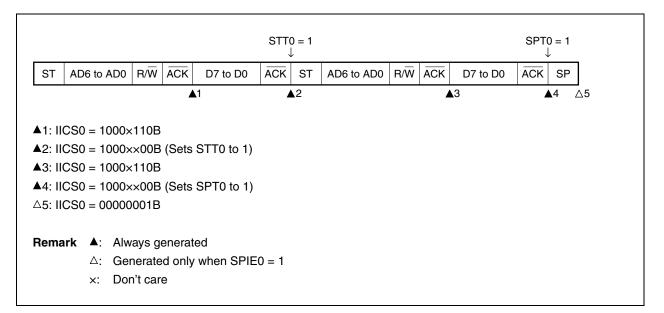

(ii) When WTIM0 = 1

| Address: FFE0H After reset: 00H R/W |             |              |               |                |               |         |       |                                              |  |  |  |  |

|-------------------------------------|-------------|--------------|---------------|----------------|---------------|---------|-------|----------------------------------------------|--|--|--|--|

| Symbol                              | <7>         | <6>          | <5>           | <4>            | <3>           | <2>     | <1>   | <0>                                          |  |  |  |  |

| IF0L                                | SREIF6      | PIF5         | PIF4          | PIF3           | PIF2          | PIF1    | PIF0  | LVIIF                                        |  |  |  |  |

|                                     |             |              |               |                |               |         |       | <u>.                                    </u> |  |  |  |  |

| Address: FFE1H After reset: 00H R/W |             |              |               |                |               |         |       |                                              |  |  |  |  |

| Symbol                              | <7>         | <6>          | <5>           | <4>            | <3>           | <2>     | <1>   | <0>                                          |  |  |  |  |

| IF0H                                | TMIF010     | TMIF000      | TMIF50        | TMIFH0         | TMIFH1        | DUALIF0 | STIF6 | SRIF6                                        |  |  |  |  |

|                                     |             |              |               |                |               | CSIIF10 |       |                                              |  |  |  |  |

|                                     |             |              |               |                |               | STIF0   |       |                                              |  |  |  |  |

|                                     |             |              |               |                |               |         |       |                                              |  |  |  |  |

| Address: FFI                        | E2H After r | eset: 00H    | R/W           |                |               |         |       |                                              |  |  |  |  |

| Symbol                              | 7           | <6>          | <5>           | <4>            | <3>           | <2>     | <1>   | <0>                                          |  |  |  |  |

| IF1L                                | 0           | PIF6         | WTIF          | KRIF           | TMIF51        | WTIIF   | SRIF0 | ADIF                                         |  |  |  |  |

|                                     |             |              |               |                |               |         |       |                                              |  |  |  |  |

| Address: FFI                        | E3H After r | eset: 00H    | R/W           |                |               |         |       |                                              |  |  |  |  |

| Symbol                              | 7           | 6            | 5             | 4              | 3             | 2       | 1     | <0>                                          |  |  |  |  |

| IF1H                                | 0           | 0            | 0             | 0              | 0             | 0       | 0     | IICIF0                                       |  |  |  |  |

|                                     |             |              |               |                |               |         |       | DMUIF <sup>Note</sup>                        |  |  |  |  |

|                                     | <u>-</u>    | •            |               | •              |               | •       |       |                                              |  |  |  |  |

|                                     | XXIFX       |              |               | Inte           | rrupt request | flag    |       |                                              |  |  |  |  |

|                                     | 0           | No interrupt | request signa | I is generated |               |         |       |                                              |  |  |  |  |

|                                     |             |              |               |                |               |         |       |                                              |  |  |  |  |

Interrupt request is generated, interrupt request status

# Figure 20-4. Format of Interrupt Request Flag Registers (IF0L, IF0H, IF1L, IF1H) (78K0/KD2)

Note Products whose flash memory is at least 48 KB only.

1

Caution Be sure to clear bit 7 of 1F1L and bits 1 to 7 of IF1H to 0.

| Address: FFI           | E8H After r        | eset: FFH I      | R/W                                           |        |                         |                             |                         |                                 |  |  |  |  |  |  |

|------------------------|--------------------|------------------|-----------------------------------------------|--------|-------------------------|-----------------------------|-------------------------|---------------------------------|--|--|--|--|--|--|

| Symbol                 | <7>                | <6>              | <5>                                           | <4>    | <3>                     | <2>                         | <1>                     | <0>                             |  |  |  |  |  |  |

| PR0L                   | SREPR6             | PPR5             | PPR4                                          | PPR3   | PPR2                    | PPR1                        | PPR0                    | LVIPR                           |  |  |  |  |  |  |

| Address: FFI           | E9H After r        | eset: FFH I      | R/W                                           |        |                         |                             |                         |                                 |  |  |  |  |  |  |

| Symbol                 | <7>                | <6>              | <5>                                           | <4>    | <3>                     | <2>                         | <1>                     | <0>                             |  |  |  |  |  |  |

| PROH                   | TMPR010            | TMPR000          | TMPR50                                        | TMPRH0 | TMPRH1                  | DUALPR0<br>CSIPR10<br>STPR0 | STPR6                   | SRPR6                           |  |  |  |  |  |  |

| Address: FFI<br>Symbol | EAH After r<br><7> | eset: FFH<br><6> | R/W<br><5>                                    | <4>    | <3>                     | <2>                         | <1>                     | <0>                             |  |  |  |  |  |  |

| PR1L                   | PPR7               | PPR6             | WTPR                                          | KRPR   | TMPR51                  | WTIPR                       | SRPR0                   | ADPR                            |  |  |  |  |  |  |

| Address: FFI<br>Symbol | EBH After r<br>7   | eset: FFH<br>6   | R/W<br>5                                      | 4      | <3>                     | <2>                         | <1>                     | <0>                             |  |  |  |  |  |  |

| PR1H                   | 1                  | 1                | 1                                             | 1      | TMPR011 <sup>Note</sup> | TMPR001 <sup>Note</sup>     | CSIPR11 <sup>Note</sup> | IICPR0<br>DMUPR <sup>Note</sup> |  |  |  |  |  |  |

|                        | XXPRX              |                  |                                               | Pric   | rity level seled        | ction                       |                         |                                 |  |  |  |  |  |  |

|                        | 0                  | High priority    | Priority level selection<br>gh priority level |        |                         |                             |                         |                                 |  |  |  |  |  |  |

|                        | 1                  | Low priority     | evel                                          |        |                         |                             |                         |                                 |  |  |  |  |  |  |

# Figure 20-15. Format of Priority Specification Flag Registers (PR0L, PR0H, PR1L, PR1H) (78K0/KE2)

Note Products whose flash memory is at least 48 KB only.

Caution Be sure to set bits 1 to 7 of PR1H to 1 for the products whose flash memory is less than 32 KB. Be sure to set bits 4 to 7 of PR1H to 1 for the products whose flash memory is at least 48 KB.

# CHAPTER 23 RESET FUNCTION

The reset function is mounted onto all 78K0/Kx2 microcontroller products. The following four operations are available to generate a reset signal.

- (1) External reset input via RESET pin

- (2) Internal reset by watchdog timer program loop detection

- (3) Internal reset by comparison of supply voltage and detection voltage of power-on-clear (POC) circuit

- (4) Internal reset by comparison of supply voltage and detection voltage of low-power-supply detector (LVI)

External and internal resets have no functional differences. In both cases, program execution starts at the address at 0000H and 0001H when the reset signal is generated.

A reset is applied when a low level is input to the RESET pin, the watchdog timer overflows, or by POC and LVI circuit voltage detection, and each item of hardware is set to the status shown in Tables 23-1 and 23-2. Each pin is high impedance during reset signal generation or during the oscillation stabilization time just after a reset release, except for P130, which is low-level output.

When a low level is input to the  $\overrightarrow{RESET}$  pin, the device is reset. It is released from the reset status when a high level is input to the  $\overrightarrow{RESET}$  pin and program execution is started with the internal high-speed oscillation clock after reset processing. A reset by the watchdog timer is automatically released, and program execution starts using the internal high-speed oscillation clock (see **Figures 23-2** to **23-4**) after reset processing. Reset by POC and LVI circuit power supply detection is automatically released when  $V_{DD} \ge V_{POC}$  or  $V_{DD} \ge V_{LVI}$  after the reset, and program execution starts using the internal high-speed oscillation clock (see **CHAPTER 24 POWER-ON-CLEAR CIRCUIT** and **CHAPTER 25 LOW-VOLTAGE DETECTOR**) after reset processing.

#### Cautions 1. For an external reset, input a low level for 10 $\mu$ s or more to the RESET pin.

- 2. During reset signal generation, the X1 clock, XT1 clock<sup>Note 1</sup>, internal high-speed oscillation clock, and internal low-speed oscillation clock stop oscillating. External main system clock input and external subsystem clock<sup>Note 1</sup> input become invalid.

- 3. When the STOP mode is released by a reset, the STOP mode contents are held during reset input. However, the port pins become high-impedance, except for P130<sup>Note 2</sup>, which is set to low-level output.

- Notes 1. The 78K0/KB2 is not provided with XT1 clock and external subsystem clock.

- 2. P130 pin is not mounted onto 38-pin and 44-pin products of the 78K0/KC2 and 78K0/KB2.

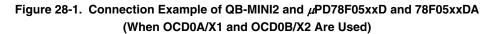

# CHAPTER 28 ON-CHIP DEBUG FUNCTION (µPD78F05xxD and 78F05xxDA ONLY)

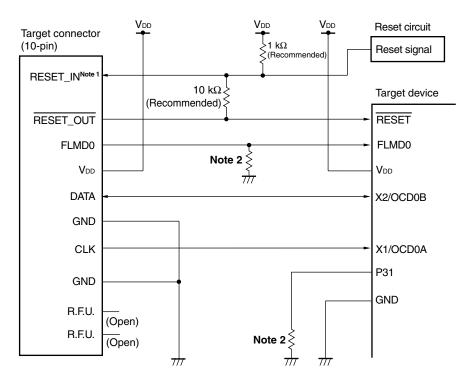

# 28.1 Connecting QB-MINI2 to $\mu$ PD78F05xxD and 78F05xxDA

The  $\mu$ PD78F05xxD and 78F05xxDA use the V<sub>DD</sub>, FLMD0, RESET, OCD0A/X1 (or OCD1A/P31), OCD0B/X2 (or OCD1B/P32), and Vss pins to communicate with the host machine via an on-chip debug emulator (QB-MINI2). Whether OCD0A/X1 and OCD1A/P31, or OCD0B/X2 and OCD1B/P32 are used can be selected.

- Caution The  $\mu$ PD78F05xxD and 78F05xxDA have an on-chip debug function, which is provided for development and evaluation. Do not use the on-chip debug function in products designated for mass production, because the guaranteed number of rewritable times of the flash memory may be exceeded when this function is used, and product reliability therefore cannot be guaranteed. Renesas Electronics is not liable for problems occurring when the on-chip debug function is used.

- RemarkμPD78F05xxD:μPD78F0503D, 78F0513D, 78F0515D, 78F0527D, 78F0537D, 78F0547DμPD78F05xxDA:μPD78F0503DA, 78F0513DA, 78F0515DA, 78F0527DA, 78F0537DA, 78F0547DA

- **Notes 1.** This connection is designed assuming that the reset signal is output from the N-ch open-drain buffer (output resistance: 100  $\Omega$  or less). For details, refer to **QB-MINI2 User's Manual (U18371E)**.

- **2.** Make pull-down resistor 470  $\Omega$  or more (10 k $\Omega$ : recommended).

## Cautions 1. Input the clock from the OCD0A/X1 pin during on-chip debugging.

2. Control the OCD0A/X1 and OCD0B/X2 pins by externally pulling down the OCD1A/P31 pin or by using an external circuit using the P130 pin (that outputs a low level when the device is reset).

Caution The pins mounted depend on the product. Refer to Caution at the beginning of this chapter.

## X1 Oscillator Characteristics

$(T_A = -40 \text{ to } +110^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{DD} = \text{EV}_{DD} \le 5.5 \text{ V}, \text{V}_{SS} = \text{EV}_{SS} = \text{AV}_{SS} = 0 \text{ V})$

| Resonator                          | Recommended Circuit | Parameter                                       | Co                                                | MIN.                                  | TYP.                  | MAX. | Unit |     |

|------------------------------------|---------------------|-------------------------------------------------|---------------------------------------------------|---------------------------------------|-----------------------|------|------|-----|

| Ceramic                            |                     | X1 clock                                        | Conventional-                                     | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ | 1.0 <sup>Note 2</sup> |      | 20.0 | MHz |

| resonator,<br>Crystal<br>resonator |                     | oscillation<br>frequency (fx) <sup>Note 1</sup> | specification<br>Products<br>(µPD78F05xx<br>(A2)) | $2.7~V \leq V_{\text{DD}} < 4.0~V$    | 1.0 <sup>Note 2</sup> |      | 10.0 |     |

|                                    |                     |                                                 | Expanded-spec<br>(µPD78F05xxA(                    | ification Products<br>(A2))           | 1.0 <sup>Note 2</sup> |      | 20.0 | MHz |

Notes 1. Indicates only oscillator characteristics. Refer to AC Characteristics for instruction execution time.

It is 2.0 MHz (MIN.) when programming on the board via UART6.

Cautions 1. When using the X1 oscillator, wire as follows in the area enclosed by the broken lines in the above figures to avoid an adverse effect from wiring capacitance.

- Keep the wiring length as short as possible.

- Do not cross the wiring with the other signal lines.

- Do not route the wiring near a signal line through which a high fluctuating current flows.

- Always make the ground point of the oscillator capacitor the same potential as Vss.

- Do not ground the capacitor to a ground pattern through which a high current flows.

- Do not fetch signals from the oscillator.

- 2. Since the CPU is started by the internal high-speed oscillation clock after a reset release, check the X1 clock oscillation stabilization time using the oscillation stabilization time counter status register (OSTC) by the user. Determine the oscillation stabilization time of the OSTC register and oscillation stabilization time select register (OSTS) after sufficiently evaluating the oscillation stabilization time with the resonator to be used.

- **Remark** For the resonator selection and oscillator constant, customers are requested to either evaluate the oscillation themselves or apply to the resonator manufacturer for evaluation.

Caution The pins mounted depend on the product. Refer to Caution at the beginning of this chapter.

## A/D Converter Characteristics

$(T_{A} = -40 \text{ to } +125^{\circ}\text{C}, 2.7 \text{ V} \le AV_{REF} \le V_{DD} = EV_{DD} \le 5.5 \text{ V}, \text{ Vss} = EV_{SS} = AV_{SS} = 0 \text{ V})$

| Parameter                                      | Symbol        | Cor                                                | nditions                                                   | MIN. | TYP. | MAX.  | Unit |

|------------------------------------------------|---------------|----------------------------------------------------|------------------------------------------------------------|------|------|-------|------|

| Resolution                                     | Res           |                                                    |                                                            |      |      | 10    | bit  |

| Overall error <sup>Notes 1, 2</sup>            | AINL          | $4.0~V \leq AV_{\text{REF}} \leq 5.5$              | 5 V                                                        |      |      | ±0.4  | %FSR |

|                                                |               | $2.7 \text{ V} \leq AV_{\text{REF}} < 4.0$         | ) V                                                        |      |      | ±0.6  | %FSR |

| Conversion time                                | <b>t</b> CONV | Conventional-                                      | $4.0~V \leq AV_{\text{REF}} \leq 5.5~V$                    | 6.1  |      | 36.7  | μS   |

|                                                |               | specification<br>Products<br>(µPD78F05xx(A2))      | $2.7~V \leq AV_{\text{REF}} < 4.0~V$                       | 12.2 |      | 36.7  | μs   |

|                                                |               | Expanded-                                          | $4.0~V \leq AV_{\text{REF}} \leq 5.5~V$                    | 6.1  |      | 66.6  | μs   |

|                                                |               | specification<br>Products<br>(µPD78F05xxA<br>(A2)) | $2.7 \text{ V} \le \text{AV}_{\text{REF}} < 4.0 \text{ V}$ | 12.2 |      | 66.6  | μs   |

| Zero-scale error <sup>Notes 1, 2</sup>         | Ezs           | $4.0 \text{ V} \leq AV_{\text{REF}} \leq 5.5$      | 5 V                                                        |      |      | ±0.4  | %FSR |

|                                                |               | $2.7 \text{ V} \leq AV_{\text{REF}} < 4.0$         | ) V                                                        |      |      | ±0.6  | %FSR |

| Full-scale error <sup>Notes 1, 2</sup>         | Efs           | $4.0~V \leq AV_{\text{REF}} \leq 5.5$              | 5 V                                                        |      |      | ±0.4  | %FSR |

|                                                |               | $2.7 \text{ V} \leq AV_{\text{REF}} < 4.0$         |                                                            |      | ±0.6 | %FSR  |      |

| Integral non-linearity error <sup>Note 1</sup> | ILE           | $4.0~V \leq AV_{\text{REF}} \leq 5.5$              | 5 V                                                        |      |      | ±2.5  | LSB  |

|                                                |               | $2.7 \text{ V} \leq AV_{\text{REF}} < 4.0$         |                                                            |      | ±4.5 | LSB   |      |

| Differential non-linearity error Note 1        | DLE           | $4.0~V \leq AV_{\text{REF}} \leq 5.5$              | 5 V                                                        |      |      | ±1.5  | LSB  |

|                                                |               | $2.7 \text{ V} \leq AV_{\text{REF}} < 4.0$         | V                                                          |      |      | ±2.0  | LSB  |

| Analog input voltage                           | VAIN          |                                                    |                                                            | AVss |      | AVREF | V    |

**Notes 1.** Excludes quantization error ( $\pm 1/2$  LSB).

2. This value is indicated as a ratio (%FSR) to the full-scale value.

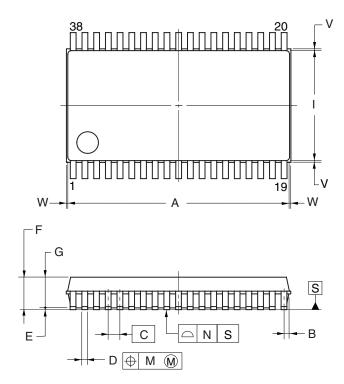

# 34.2 78K0/KC2

- µPD78F0511AMC-GAA-AX, 78F0512AMC-GAA-AX, 78F0513AMC-GAA-AX, 78F0513DAMC-GAA-AX

- µPD78F0511AMCA-GAA-G, 78F0512AMCA-GAA-G, 78F0513AMCA-GAA-G

- μPD78F0511AMCA2-GAA-G, 78F0512AMCA2-GAA-G, 78F0513AMCA2-GAA-G

38-PIN PLASTIC SSOP (7.62mm (300))

# NOTE

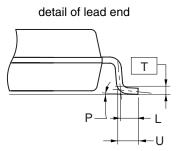

Each lead centerline is located within 0.10 mm of its true position (T.P.) at maximum material condition.

|      | (UNIT:mm)                       |

|------|---------------------------------|

| ITEM | DIMENSIONS                      |

| А    | 12.30±0.10                      |

| В    | 0.30                            |

| С    | 0.65 (T.P.)                     |

| D    | $0.30\substack{+0.10\\-0.05}$   |

| E    | 0.125±0.075                     |

| F    | 2.00 MAX.                       |

| G    | 1.70±0.10                       |

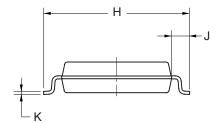

| Н    | 8.10±0.20                       |

| I    | 6.10±0.10                       |

| J    | 1.00±0.20                       |

| к    | $0.15\substack{+0.10 \\ -0.05}$ |

| L    | 0.50                            |

| М    | 0.10                            |

| Ν    | 0.10                            |

| Р    | 3° <sup>+5°</sup><br>-3°        |

| Т    | 0.25(T.P.)                      |

| U    | 0.60±0.15                       |

| V    | 0.25 MAX.                       |

| W    | 0.15 MAX.                       |

|      | P38MC-65-GAA                    |

|            | _              | <b>—</b>                           |                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | T        |              | 5/30) |

|------------|----------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------|-------|

| Chapter    | Classification | Function                           | Details of<br>Function                                                                                                                                                                 | Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          | Pag          | e     |

| Chapter 14 | Soft           | Serial<br>interface<br>UART0       | UART mode                                                                                                                                                                              | If clock supply to serial interface UART0 is not stopped (e.g., in the HALT mode),<br>normal operation continues. If clock supply to serial interface UART0 is stopped (e.g.,<br>in the STOP mode), each register stops operating, and holds the value immediately<br>before clock supply was stopped. The TxD0 pin also holds the value immediately<br>before clock supply was stopped and outputs it. However, the operation is not<br>guaranteed after clock supply is resumed. Therefore, reset the circuit so that<br>POWER0 = 0, RXE0 = 0, and TXE0 = 0. | p.       | 432          |       |

|            |                |                                    |                                                                                                                                                                                        | Set POWER0 = 1 and then set TXE0 = 1 (transmission) or RXE0 = 1 (reception) to start communication.                                                                                                                                                                                                                                                                                                                                                                                                                                                            | p.       | 432          |       |

|            |                |                                    |                                                                                                                                                                                        | TXE0 and RXE0 are synchronized by the base clock ( $f_{XCLK0}$ ) set by BRGC0. To<br>enable transmission or reception again, set TXE0 or RXE0 to 1 at least two clocks of<br>base clock after TXE0 or RXE0 has been cleared to 0. If TXE0 or RXE0 is set within<br>two clocks of base clock, the transmission circuit or reception circuit may not be<br>initialized.                                                                                                                                                                                          | p.       | 432          |       |

|            |                |                                    |                                                                                                                                                                                        | Set transmit data to TXS0 at least one base clock (fxcLk0) after setting TXE0 = 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | рр<br>43 | ). 432<br>85 | 2, 🗌  |

|            |                |                                    | TXS0: Transmit<br>shift register 0                                                                                                                                                     | Do not write the next transmit data to TXS0 before the transmission completion interrupt signal (INTST0) is generated.                                                                                                                                                                                                                                                                                                                                                                                                                                         | p.       | 435          |       |

|            |                |                                    | ASIM0:<br>Asynchronous                                                                                                                                                                 | To start the transmission, set POWER0 to 1 and then set TXE0 to 1. To stop the transmission, clear TXE0 to 0, and then clear POWER0 to 0.                                                                                                                                                                                                                                                                                                                                                                                                                      | p.       | 437          |       |

|            | c              | serial interface<br>operation mode | To start the reception, set POWER0 to 1 and then set RXE0 to 1. To stop the reception, clear RXE0 to 0, and then clear POWER0 to 0.                                                    | p.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 437      |              |       |

|            |                | register 0                         | Set POWER0 to 1 and then set RXE0 to 1 while a high level is input to the RxD0 pin.<br>If POWER0 is set to 1 and RXE0 is set to 1 while a low level is input, reception is<br>started. | p.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 437      |              |       |

|            |                |                                    |                                                                                                                                                                                        | TXE0 and RXE0 are synchronized by the base clock (fxCLK0) set by BRGC0. To enable transmission or reception again, set TXE0 or RXE0 to 1 at least two clocks of base clock after TXE0 or RXE0 has been cleared to 0. If TXE0 or RXE0 is set within two clocks of base clock, the transmission circuit or reception circuit may not be initialized.                                                                                                                                                                                                             | p.       | 437          |       |

|            |                |                                    |                                                                                                                                                                                        | Set transmit data to TXS0 at least one base clock (fxcLk0) after setting TXE0 = 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | p.       | 437          |       |

|            |                |                                    |                                                                                                                                                                                        | Clear the TXE0 and RXE0 bits to 0 before rewriting the PS01, PS00, and CL0 bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | p.       | 437          |       |

|            |                |                                    |                                                                                                                                                                                        | Make sure that $TXE0 = 0$ when rewriting the SL0 bit. Reception is always performed with "number of stop bits = 1", and therefore, is not affected by the set value of the SL0 bit.                                                                                                                                                                                                                                                                                                                                                                            | p.       | 437          |       |