# E·XF Renesas Electronics America Inc - <u>UPD78F0501AFC-AA3-A Datasheet</u>

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 20MHz                                                                                |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                                   |

| Number of I/O              | 23                                                                                   |

| Program Memory Size        | 16KB (16K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 768 x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 4x10b                                                                            |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

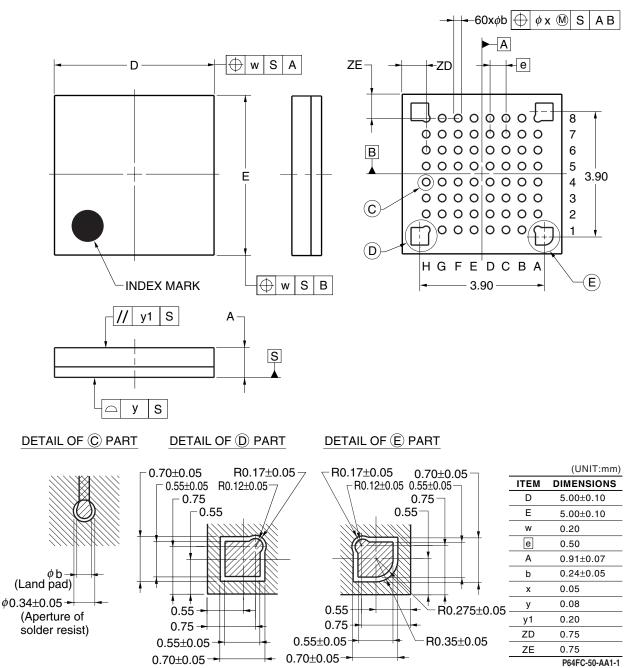

| Package / Case             | 36-VFLGA                                                                             |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0501afc-aa3-a |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# How to Use This Manual

**Readers** This manual is intended for user engineers who wish to understand the functions of the 78K0/Kx2 microcontrollers and design and develop application systems and programs for these devices. The target products are as follows.

|          | Conventional-specification Products           | Expanded-specification Products           |

|----------|-----------------------------------------------|-------------------------------------------|

| 78K0/KB2 | μPD78F0500, 78F0501, 78F0502, 78F0503,        | μPD78F0500A, 78F0501A, 78F0502A,          |

|          | 78F0503D, 78F0500(A), 78F0501(A), 78F0502(A), | 78F0503A, 78F0503DA, 78F0500A(A),         |

|          | 78F0503(A), 78F0500(A2), 78F0501(A2),         | 78F0501A(A), 78F0502A(A), 78F0503A(A),    |

|          | 78F0502(A2), 78F0503(A2)                      | 78F0500A(A2), 78F0501A(A2), 78F0502A(A2), |

|          |                                               | 78F0503A(A2)                              |

| 78K0/KC2 | μPD78F0511, 78F0512, 78F0513, 78F0514,        | μPD78F0511A, 78F0512A, 78F0513A,          |

|          | 78F0515, 78F0513D, 78F0515D, 78F0511(A),      | 78F0514A, 78F0515A, 78F0513DA, 78F0515DA, |

|          | 78F0512(A), 78F0513(A), 78F0514(A),           | 78F0511A(A), 78F0512A(A), 78F0513A(A),    |

|          | 78F0515(A), 78F0511(A2), 78F0512(A2),         | 78F0514A(A), 78F0515A(A), 78F0511A(A2),   |

|          | 78F0513(A2), 78F0514(A2), 78F0515(A2)         | 78F0512A(A2), 78F0513A(A2), 78F0514A(A2), |

|          |                                               | 78F0515A(A2)                              |

| 78K0/KD2 | μPD78F0521, 78F0522, 78F0523, 78F0524,        | μPD78F0521A, 78F0522A, 78F0523A,          |

|          | 78F0525, 78F0526, 78F0527, 78F0527D,          | 78F0524A, 78F0525A, 78F0526A, 78F0527A,   |

|          | 78F0521(A), 78F0522(A), 78F0523(A),           | 78F0527DA, 78F0521A(A), 78F0522A(A),      |

|          | 78F0524(A), 78F0525(A), 78F0526(A),           | 78F0523A(A), 78F0524A(A), 78F0525A(A),    |

|          | 78F0527(A), 78F0521(A2), 78F0522(A2),         | 78F0526A(A), 78F0527A(A), 78F0521A(A2),   |

|          | 78F0523(A2), 78F0524(A2), 78F0525(A2),        | 78F0522A(A2), 78F0523A(A2), 78F0524A(A2), |

|          | 78F0526(A2), 78F0527(A2)                      | 78F0525A(A2), 78F0526A(A2), 78F0527A(A2)  |

| 78K0/KE2 | μPD78F0531, 78F0532, 78F0533, 78F0534,        | μPD78F0531A, 78F0532A, 78F0533A,          |

|          | 78F0535, 78F0536, 78F0537, 78F0537D,          | 78F0534A, 78F0535A, 78F0536A, 78F0537A,   |

|          | 78F0531(A), 78F0532(A), 78F0533(A),           | 78F0537DA, 78F0531A(A), 78F0532A(A),      |

|          | 78F0534(A), 78F0535(A), 78F0536(A),           | 78F0533A(A), 78F0534A(A), 78F0535A(A),    |

|          | 78F0537(A), 78F0531(A2), 78F0532(A2),         | 78F0536A(A), 78F0537A(A), 78F0531A(A2),   |

|          | 78F0533(A2), 78F0534(A2), 78F0535(A2),        | 78F0532A(A2), 78F0533A(A2), 78F0534A(A2), |

|          | 78F0536(A2), 78F0537(A2)                      | 78F0535A(A2), 78F0536A(A2), 78F0537A(A2)  |

| 78K0/KF2 | μPD78F0544, 78F0545, 78F0546, 78F0547,        | μPD78F0544A, 78F0545A, 78F0546A,          |

|          | 78F0547D, 78F0544(A), 78F0545(A),             | 78F0547A, 78F0547DA, 78F0544A(A),         |

|          | 78F0546(A), 78F0547(A), 78F0544(A2),          | 78F0545A(A), 78F0546A(A), 78F0547A(A),    |

|          | 78F0545(A2), 78F0546(A2), 78F0547(A2)         | 78F0544A(A2), 78F0545A(A2), 78F0546A(A2), |

|          |                                               | 78F0547A(A2)                              |

| СНАРТ                                                         | ER 7 16-BIT TIMER/EVENT COUNTERS 00 AND 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                   |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 7.1                                                           | Functions of 16-Bit Timer/Event Counters 00 and 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                   |

|                                                               | Configuration of 16-Bit Timer/Event Counters 00 and 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                   |

| 7.3                                                           | Registers Controlling 16-Bit Timer/Event Counters 00 and 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                   |

| 7.4                                                           | Operation of 16-Bit Timer/Event Counters 00 and 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                   |

|                                                               | 7.4.1 Interval timer operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                   |

|                                                               | 7.4.2 Square-wave output operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                   |

|                                                               | 7.4.3 External event counter operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                   |

|                                                               | 7.4.4 Operation in clear & start mode entered by TI00n pin valid edge input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                   |

|                                                               | 7.4.5 Free-running timer operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                   |

|                                                               | 7.4.6 PPG output operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 321                                                                                                                               |

|                                                               | 7.4.7 One-shot pulse output operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                   |

|                                                               | 7.4.8 Pulse width measurement operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                   |

| 7.5                                                           | Special Use of TM0n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                   |

|                                                               | 7.5.1 Rewriting CR01n during TM0n operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                   |

|                                                               | 7.5.2 Setting LVS0n and LVR0n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                   |

| 7.6                                                           | Cautions for 16-Bit Timer/Event Counters 00 and 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                   |

| СПУП                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0.45                                                                                                                              |

| CHAPI                                                         | ER 8 8-BIT TIMER/EVENT COUNTERS 50 AND 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                   |

|                                                               | ER 8 8-BIT TIMER/EVENT COUNTERS 50 AND 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                   |

| 8.1                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                   |

| 8.1<br>8.2                                                    | Functions of 8-Bit Timer/Event Counters 50 and 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                   |

| 8.1<br>8.2<br>8.3                                             | Functions of 8-Bit Timer/Event Counters 50 and 51<br>Configuration of 8-Bit Timer/Event Counters 50 and 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                   |

| 8.1<br>8.2<br>8.3                                             | Functions of 8-Bit Timer/Event Counters 50 and 51<br>Configuration of 8-Bit Timer/Event Counters 50 and 51<br>Registers Controlling 8-Bit Timer/Event Counters 50 and 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                   |

| 8.1<br>8.2<br>8.3                                             | Functions of 8-Bit Timer/Event Counters 50 and 51<br>Configuration of 8-Bit Timer/Event Counters 50 and 51<br>Registers Controlling 8-Bit Timer/Event Counters 50 and 51<br>Operations of 8-Bit Timer/Event Counters 50 and 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                   |

| 8.1<br>8.2<br>8.3                                             | Functions of 8-Bit Timer/Event Counters 50 and 51<br>Configuration of 8-Bit Timer/Event Counters 50 and 51<br>Registers Controlling 8-Bit Timer/Event Counters 50 and 51<br>Operations of 8-Bit Timer/Event Counters 50 and 51<br>8.4.1 Operation as interval timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                   |

| 8.1<br>8.2<br>8.3                                             | Functions of 8-Bit Timer/Event Counters 50 and 51<br>Configuration of 8-Bit Timer/Event Counters 50 and 51<br>Registers Controlling 8-Bit Timer/Event Counters 50 and 51<br>Operations of 8-Bit Timer/Event Counters 50 and 51<br>8.4.1 Operation as interval timer<br>8.4.2 Operation as external event counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 345<br>345<br>348<br>354<br>354<br>356<br>357                                                                                     |

| 8.1<br>8.2<br>8.3<br>8.4                                      | Functions of 8-Bit Timer/Event Counters 50 and 51<br>Configuration of 8-Bit Timer/Event Counters 50 and 51<br>Registers Controlling 8-Bit Timer/Event Counters 50 and 51<br>Operations of 8-Bit Timer/Event Counters 50 and 51<br>8.4.1 Operation as interval timer<br>8.4.2 Operation as external event counter<br>8.4.3 Square-wave output operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 345<br>345<br>348<br>354<br>354<br>354<br>356<br>357<br>358                                                                       |