# E·XF Renesas Electronics America Inc - <u>UPD78F0503AFC-AA3-A Datasheet</u>

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 20MHz                                                                                |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                                   |

| Number of I/O              | 23                                                                                   |

| Program Memory Size        | 32KB (32K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 1K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 4x10b                                                                            |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 36-VFLGA                                                                             |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0503afc-aa3-a |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Differences Between Conventional-specification Products and Expanded-specification Products

The differences between the conventional-specification products ( $\mu$ PD78F05xx, 78F05xxD) and expanded-specification products ( $\mu$ PD78F05xxA, 78F05xxDA) of the 78K0/Kx2 microcontrollers are described below.

- A/D conversion time

- X1 oscillator characteristics

- Instruction cycle, peripheral hardware clock frequency, external main system clock frequency, external main system clock input high-level width, and external main system clock input low-level width (AC characteristics)

- The number of flash memory rewrites and retention time

- Processing time of the self programming library

- Interrupt response time of the self programming library

# For details, see 1.1 Differences Between Conventional-specification Products ( $\mu$ PD78F05xx, 78F05xxD) and Expanded-specification Products ( $\mu$ PD78F05xxA, 78F05xxDA).

Purpose This manual is intended to give users an understanding of the functions described in the Organization below. Organization The manual for the 78K0/Kx2 microcontrollers is separated into two parts: this manual and the instructions edition (common to the 78K0 microcontrollers). 78K0/Kx2 78K/0 Series User's Manual **User's Manual** (This Manual) Instructions • Pin functions • CPU functions Internal block functions Instruction set Interrupts · Explanation of each instruction Other on-chip peripheral functions • Electrical specifications How to Read This Manual It is assumed that the readers of this manual have general knowledge of electrical engineering, logic circuits, and microcontrollers. • When using this manual as the manual for (A) grade products and (A2) grade products of the 78K0/Kx2 microcontrollers:  $\rightarrow$ Only the quality grade differs between standard products and (A), (A2) grade products. Read the part number as follows. •  $\mu$ PD78F05xx $\rightarrow \mu$ PD78F05xx(A), 78F05xx(A2) •  $\mu$ PD78F05xxA $\rightarrow \mu$ PD78F05xxA(A), 78F05xxA(A2) • To gain a general understanding of functions:  $\rightarrow$  Read this manual in the order of the **CONTENTS**. The mark "<R>" shows major revised points. The revised points can be easily searched by copying an "<R>" in the PDF file and specifying it in the "Find what:" field. How to interpret the register format:  $\rightarrow$  For a bit number enclosed in angle brackets, the bit name is defined as a reserved word in the RA78K0, and is defined as an sfr variable using the #pragma sfr directive in the CC78K0. • To check the details of a register when you know the register name: → See APPENDIX C REGISTER INDEX.

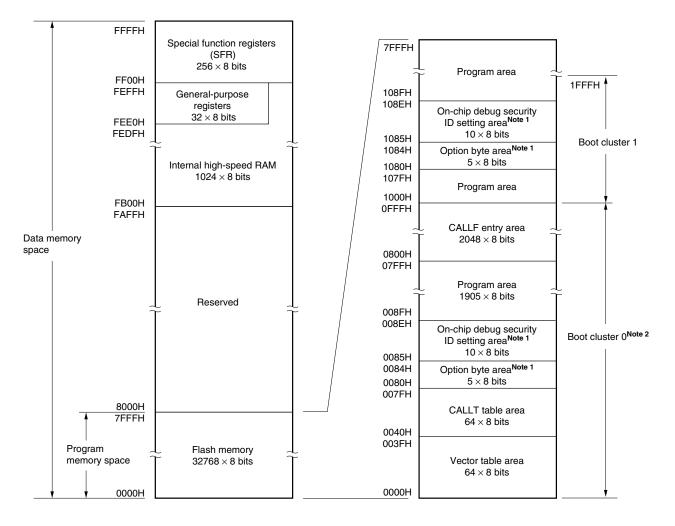

Figure 3-5. Memory Map (µPD78F0503D, 78F0503DA, 78F0513D, and 78F0513DA)

Notes 1. When boot swap is not used: Set the option bytes to 0080H to 0084H, and the on-chip debug security IDs to 0085H to 008EH.

When boot swap is used: Set the option bytes to 0080H to 0084H and 1080H to 1084H, and the on-chip debug security IDs to 0085H to 008EH and 1085H to 108EH.

- 2. Writing boot cluster 0 can be prohibited depending on the setting of security (see 27.8 Security Settings).

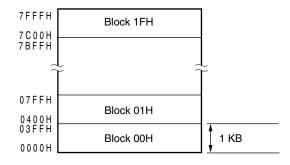

- **Remark** The flash memory is divided into blocks (one block = 1 KB). For the address values and block numbers, see **Table 3-3 Correspondence Between Address Values and Block Numbers in Flash Memory**.

#### 3.1.4 Special function register (SFR) area

On-chip peripheral hardware special function registers (SFRs) are allocated in the area FF00H to FFFFH (see **Table 3-8 Special Function Register List** in **3.2.3 Special function registers (SFRs)**).

#### Caution Do not access addresses to which SFRs are not assigned.

#### 3.1.5 Data memory addressing

Addressing refers to the method of specifying the address of the instruction to be executed next or the address of the register or memory relevant to the execution of instructions.

Several addressing modes are provided for addressing the memory relevant to the execution of instructions for the 78K0/Kx2 microcontrollers, based on operability and other considerations. For areas containing data memory in particular, special addressing methods designed for the functions of special function registers (SFR) and general-purpose registers are available for use. Figures 3-12 to 3-19 show correspondence between data memory and addressing. For details of each addressing mode, see **3.4 Operand Address Addressing**.

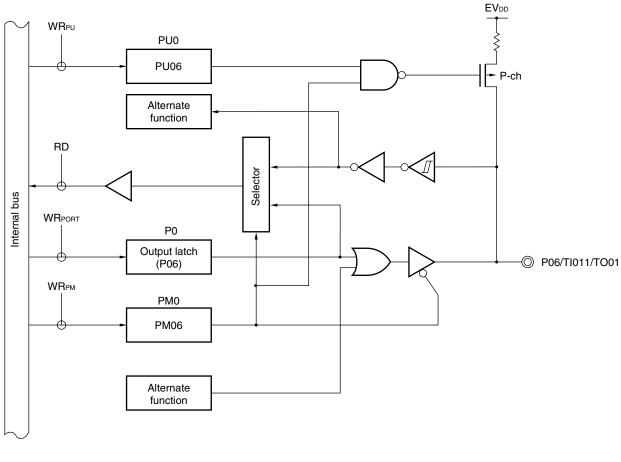

Figure 5-6. Block Diagram of P06 (2/2)

P0: Port register 0

PU0: Pull-up resistor option register 0

PM0: Port mode register 0

RD: Read signal

WR××: Write signal

**Remark** With products not provided with an EVDD or EVss pin, replace EVDD with VDD, or replace EVss with Vss.

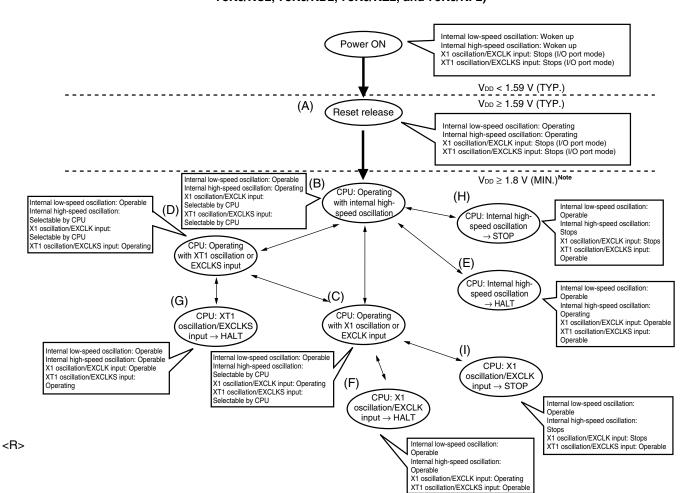

- Note Standard and (A) grade products: 1.8 V, (A2) grade products: 2.7 V

- **Remark** In the 2.7 V/1.59 V POC mode (option byte: POCMODE = 1), the CPU clock status changes to (A) in the above figure when the supply voltage exceeds 2.7 V (TYP.), and to (B) after reset processing (11 to  $45 \ \mu$ s).

### Table 6-6. CPU Clock Transition and SFR Register Setting Examples (2/5)

#### (4) CPU clock changing from internal high-speed oscillation clock (B) to high-speed system clock (C)

| (Setting sequence of SFR registers)                                                     |                      |       |        |       |                     |                      |      |

|-----------------------------------------------------------------------------------------|----------------------|-------|--------|-------|---------------------|----------------------|------|

| Setting Flag of SFR Register                                                            | AMPH <sup>Note</sup> | EXCLK | OSCSEL | MSTOP | OSTC<br>Register    | XSEL <sup>Note</sup> | MCM0 |

| (B) $\rightarrow$ (C) (X1 clock: 1 MHz $\leq$ fxH $\leq$ 10 MHz)                        | 0                    | 0     | 1      | 0     | Must be<br>checked  | 1                    | 1    |

| (B) $\rightarrow$ (C) (external main clock: 1 MHz $\leq$ f <sub>XH</sub> $\leq$ 10 MHz) | 0                    | 1     | 1      | 0     | Must not be checked | 1                    | 1    |

| (B) $\rightarrow$ (C) (X1 clock: 10 MHz < fxH $\leq$ 20 MHz)                            | 1                    | 0     | 1      | 0     | Must be checked     | 1                    | 1    |

| (B) $\rightarrow$ (C) (external main clock: 10 MHz < f <sub>XH</sub> $\leq$ 20 MHz)     | 1                    | 1     | 1      | 0     | Must not be checked | 1                    | 1    |

|                                                                                         | $\subseteq$          |       |        |       |                     |                      |      |

Unnecessary if these registers Unnecessary if the are already set

CPU is operating with the high-speed system clock

- Note The value of this flag can be changed only once after a reset release. This setting is not necessary if it has already been set.

- Caution Set the X1 clock after the supply voltage has reached the operable voltage of the clock to be used (see CHAPTER 30 ELECTRICAL SPECIFICATIONS (STANDARD PRODUCTS) to CHAPTER 33 ELECTRICAL SPECIFICATIONS ((A2) GRADE PRODUCTS: TA = -40 to +125°C)).

- (5) CPU clock changing from internal high-speed oscillation clock (B) to subsystem clock (D)<sup>Note</sup>

Note The 78K0/KB2 is not provided with a subsystem clock.

| (Setting sequence of SFR registers)              |         |        |         |               |     |

|--------------------------------------------------|---------|--------|---------|---------------|-----|

| Setting Flag of SFR Register                     | XTSTART | EXCLKS | OSCSELS | Waiting for   | CSS |

|                                                  |         |        |         | Oscillation   |     |

| Status Transition                                |         |        |         | Stabilization |     |

| $(B) \rightarrow (D) (XT1 clock)$                | 0       | 0      | 1       | Necessary     | 1   |

|                                                  | 1       | ×      | ×       |               |     |

| (B) $\rightarrow$ (D) (external subsystem clock) | 0       | 1      | 1       | Unnecessary   | 1   |

|                                                  |         |        |         | )             |     |

(C - H)-.......

Unnecessary if the CPU is operating

with the subsystem clock

Remarks 1. (A) to (I) in Table 6-6 correspond to (A) to (I) in Figure 6-17 and 6-18.

2. EXCLK, OSCSEL, EXCLKS, OSCSELS, AMPH:

|               | Bits 7 to 4 and 0 of the clock operation mode select register (OSCCTL) |

|---------------|------------------------------------------------------------------------|

| MSTOP:        | Bit 7 of the main OSC control register (MOC)                           |

| XSEL, MCM0:   | Bits 2 and 0 of the main clock mode register (MCM)                     |

| XTSTART, CSS: | Bits 6 and 4 of the processor clock control register (PCC)             |

| ×:            | Don't care                                                             |

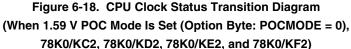

#### Figure 9-12. Operation Timing in PWM Output Mode (1/4)

- <1> The count operation is enabled by setting the TMHEn bit to 1. Start the 8-bit timer counter Hn by masking one count clock to count up. At this time, PWM output outputs an inactive level.

- <2> When the values of the 8-bit timer counter Hn and the CMP0n register match, an active level is output. At this time, the value of the 8-bit timer counter Hn is cleared, and the INTTMHn signal is output.

- <3> When the values of the 8-bit timer counter Hn and the CMP1n register match, an inactive level is output. At this time, the 8-bit timer counter value is not cleared and the INTTMHn signal is not output.

- <4> Clearing the TMHEn bit to 0 during timer Hn operation sets the INTTMHn signal to the default and PWM output to an inactive level.

**Remark** n = 0, 1

### 14.4 Operation of Serial Interface UART0

Serial interface UART0 has the following two modes.

- Operation stop mode

- Asynchronous serial interface (UART) mode

#### 14.4.1 Operation stop mode

In this mode, serial communication cannot be executed, thus reducing the power consumption. In addition, the pins can be used as ordinary port pins in this mode. To set the operation stop mode, clear bits 7, 6, and 5 (POWER0, TXE0, and RXE0) of ASIM0 to 0.

#### (1) Register used

The operation stop mode is set by asynchronous serial interface operation mode register 0 (ASIM0). ASIM0 can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets this register to 01H.

Address: FF70H After reset: 01H R/W

| Symbol | <7>    | <6>  | <5>  | 4    | 3    | 2   | 1   | 0 |

|--------|--------|------|------|------|------|-----|-----|---|

| ASIM0  | POWER0 | TXE0 | RXE0 | PS01 | PS00 | CL0 | SL0 | 1 |

| POWER0              | Enables/disables operation of internal operation clock                                               |

|---------------------|------------------------------------------------------------------------------------------------------|

| 0 <sup>Note 1</sup> | Disables operation of the internal operation clock (fixes the clock to low level) and asynchronously |

|                     | resets the internal circuit <sup>Note 2</sup> .                                                      |

| TXE0 | Enables/disables transmission                                          |

|------|------------------------------------------------------------------------|

| 0    | Disables transmission (synchronously resets the transmission circuit). |

| RXE0 | Enables/disables reception                                       |

|------|------------------------------------------------------------------|

| 0    | Disables reception (synchronously resets the reception circuit). |

**Notes 1.** The input from the RxD0 pin is fixed to high level when POWER0 = 0.

- 2. Asynchronous serial interface reception error status register 0 (ASIS0), transmit shift register 0 (TXS0), and receive buffer register 0 (RXB0) are reset.

- Caution Clear POWER0 to 0 after clearing TXE0 and RXE0 to 0 to set the operation stop mode. To start the communication, set POWER0 to 1, and then set TXE0 or RXE0 to 1.

- **Remark** To use the RxD0/SI10/P11 and TxD0/SCK10/P10 pins as general-purpose port pins, see **CHAPTER 5 PORT FUNCTIONS**.

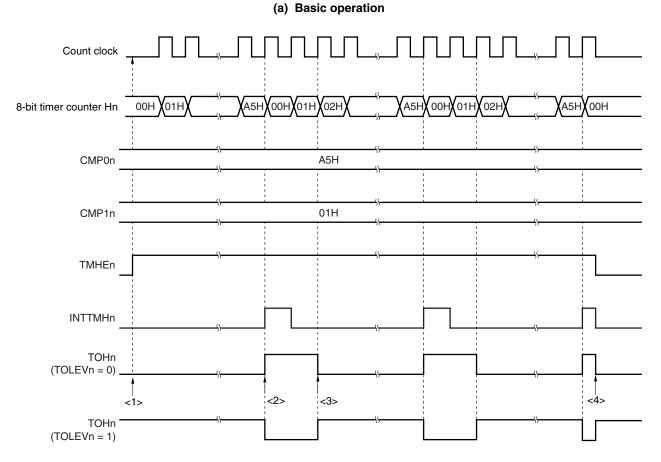

#### Figure 16-8. Format of Port Mode Register 1 (PM1)

| Address: FF21H After reset: FFH R/W |                                              |      |      |      |      |      |      |      |

|-------------------------------------|----------------------------------------------|------|------|------|------|------|------|------|

| Symbol                              | 7                                            | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| PM1                                 | PM17                                         | PM16 | PM15 | PM14 | PM13 | PM12 | PM11 | PM10 |

| -                                   |                                              |      |      |      |      |      |      |      |

|                                     | PM1n P1n pin I/O mode selection (n = 0 to 7) |      |      |      |      |      |      |      |

|                                     | 0 Output mode (output buffer on)             |      |      |      |      |      |      |      |

1 Input mode (output buffer off)

### 16.4 Operation of Serial Interfaces CSI10 and CSI11

Serial interfaces CSI10 and CSI11 can be used in the following two modes.

- Operation stop mode

- 3-wire serial I/O mode

#### 16.4.1 Operation stop mode

Serial communication is not executed in this mode. Therefore, the power consumption can be reduced. In addition, the P10/SCK10/TxD0, P11/SI10/RxD0, P12/SO10, P02/SO11, P03/SI11, and P04/SCK11 pins can be used as ordinary I/O port pins in this mode.

#### (1) Register used

The operation stop mode is set by serial operation mode register 1n (CSIM1n). To set the operation stop mode, clear bit 7 (CSIE1n) of CSIM1n to 0.

#### (a) Serial operation mode register 1n (CSIM1n)

CSIM1n can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation clears CSIM1n to 00H.

**Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KE2 products

• Serial operation mode register 10 (CSIM10)

#### Address: FF80H After reset: 00H R/W

| Symbol | <7>    | 6                                           | 5                                                                                                       | 4     | 3 | 2 | 1 | 0      |  |  |  |  |

|--------|--------|---------------------------------------------|---------------------------------------------------------------------------------------------------------|-------|---|---|---|--------|--|--|--|--|

| CSIM10 | CSIE10 | TRMD10                                      | 0                                                                                                       | DIR10 | 0 | 0 | 0 | CSOT10 |  |  |  |  |

|        |        |                                             |                                                                                                         |       |   |   |   |        |  |  |  |  |

|        | CSIE10 | Operation control in 3-wire serial I/O mode |                                                                                                         |       |   |   |   |        |  |  |  |  |

|        | 0      | Disables oper                               | Disables operation <sup>Note 1</sup> and asynchronously resets the internal circuit <sup>Note 2</sup> . |       |   |   |   |        |  |  |  |  |

- **Notes 1.** To use P10/SCK10/TxD0 and P12/SO10 as general-purpose ports, set CSIM10 in the default status (00H).

- 2. Bit 0 (CSOT10) of CSIM10 and serial I/O shift register 10 (SIO10) are reset.

### 18.5 I<sup>2</sup>C Bus Definitions and Control Methods

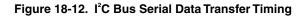

The following section describes the  $l^2C$  bus's serial data communication format and the signals used by the  $l^2C$  bus. Figure 18-12 shows the transfer timing for the "start condition", "address", "data", and "stop condition" output via the  $l^2C$  bus's serial data bus.

The master device generates the start condition, slave address, and stop condition.

The acknowledge (ACK) can be generated by either the master or slave device (normally, it is output by the device that receives 8-bit data).

The serial clock (SCL0) is continuously output by the master device. However, in the slave device, the SCL0's low level period can be extended and a wait can be inserted.

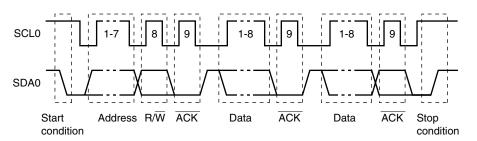

#### 18.5.1 Start conditions

A start condition is met when the SCL0 pin is at high level and the SDA0 pin changes from high level to low level. The start conditions for the SCL0 pin and SDA0 pin are signals that the master device generates to the slave device when starting a serial transfer. When the device is used as a slave, start conditions can be detected.

#### Figure 18-13. Start Conditions

A start condition is output when bit 1 (STT0) of IIC control register 0 (IICC0) is set (to 1) after a stop condition has been detected (SPD0: Bit 0 = 1 in IIC status register 0 (IICS0)). When a start condition is detected, bit 1 (STD0) of IICS0 is set (to 1).

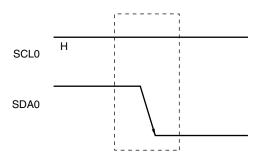

# Figure 18-27. Example of Master to Slave Communication (When 9-Clock Wait Is Selected for Both Master and Slave) (1/3)

#### (1) Start condition ~ address

Notes 1. Write data to IICO, not setting WRELO, in order to cancel a wait state during master transmission.2. To cancel slave wait, write "FFH" to IICO or set WRELO.

| Address: FFE8H After reset: FFH R/W |                                     |                          |        |        |        |         |       |                       |  |  |  |  |

|-------------------------------------|-------------------------------------|--------------------------|--------|--------|--------|---------|-------|-----------------------|--|--|--|--|

| Symbol                              | <7>                                 | <6>                      | <5>    | <4>    | <3>    | <2>     | <1>   | <0>                   |  |  |  |  |

| PR0L                                | SREPR6                              | PPR5                     | PPR4   | PPR3   | PPR2   | PPR1    | PPR0  | LVIPR                 |  |  |  |  |

|                                     |                                     |                          |        |        |        |         |       |                       |  |  |  |  |

| Address: FF                         | Address: FFE9H After reset: FFH R/W |                          |        |        |        |         |       |                       |  |  |  |  |

| Symbol                              | <7>                                 | <6>                      | <5>    | <4>    | <3>    | <2>     | <1>   | <0>                   |  |  |  |  |

| PR0H                                | TMPR010                             | TMPR000                  | TMPR50 | TMPRH0 | TMPRH1 | DUALPR0 | STPR6 | SRPR6                 |  |  |  |  |

|                                     |                                     |                          |        |        |        | CSIPR10 |       |                       |  |  |  |  |

|                                     |                                     |                          |        |        |        | STPR0   |       |                       |  |  |  |  |

|                                     |                                     |                          |        |        |        |         |       |                       |  |  |  |  |

| Address: FF                         | EAH After r                         | eset: FFH                | R/W    |        |        |         |       |                       |  |  |  |  |

| Symbol                              | 7                                   | <6>                      | <5>    | <4>    | <3>    | <2>     | <1>   | <0>                   |  |  |  |  |

| PR1L                                | 1                                   | PPR6                     | WTPR   | KRPR   | TMPR51 | WTIPR   | SRPR0 | ADPR                  |  |  |  |  |

|                                     |                                     |                          |        |        |        |         |       |                       |  |  |  |  |

| Address: FF                         | EBH After r                         | eset: FFH                | R/W    |        |        |         |       |                       |  |  |  |  |

| Symbol                              | 7                                   | 6                        | 5      | 4      | 3      | 2       | 1     | <0>                   |  |  |  |  |

| PR1H                                | 1                                   | 1                        | 1      | 1      | 1      | 1       | 1     | IICPR0                |  |  |  |  |

|                                     |                                     |                          |        |        |        |         |       | DMUPR <sup>Note</sup> |  |  |  |  |

|                                     |                                     | -                        |        |        |        |         |       |                       |  |  |  |  |

|                                     | XXPRX                               | Priority level selection |        |        |        |         |       |                       |  |  |  |  |

|                                     | 0                                   | High priority level      |        |        |        |         |       |                       |  |  |  |  |

|                                     |                                     | Low priority level       |        |        |        |         |       |                       |  |  |  |  |

#### Figure 20-14. Format of Priority Specification Flag Registers (PR0L, PR0H, PR1L, PR1H) (78K0/KD2)

Note Products whose flash memory is at least 48 KB only.

Caution Be sure to set bit 7 of PR1L and bits 1 to 7 of PR1H to 1.

#### (3) 0084H/1084H

- O On-chip debug operation control

- Disabling on-chip debug operation

- Enabling on-chip debug operation and erasing data of the flash memory in case authentication of the on-chip debug security ID fails

- Enabling on-chip debug operation and not erasing data of the flash memory even in case authentication of the on-chip debug security ID fails

- Cautions 1. Be sure to set 00H (disabling on-chip debug operation) to 0084H for products not equipped with the on-chip debug function (µPD78F05xx and 78F05xxA). Also set 00H to 1084H because 0084H and 1084H are switched during the boot operation.

- 2. To use the on-chip debug function with a product equipped with the on-chip debug function  $(\mu PD78F05xxD \text{ and } 78F05xxDA)$ , set 02H or 03H to 0084H. Set a value that is the same as that of 0084H to 1084H because 0084H and 1084H are switched during the boot operation.

#### 26.2 Format of Option Byte

The format of the option byte is shown below.

# Table 27-13. Processing Time for Self Programming Library(Conventional-specification Products ( $\mu$ PD78F05xx and 78F05xxD)) (2/4)

#### (2) When internal high-speed oscillation clock is used and entry RAM is located in short direct addressing range

| Librar                   | y Name                             | Processing Time (µs) |                 |                     |                    |  |  |  |

|--------------------------|------------------------------------|----------------------|-----------------|---------------------|--------------------|--|--|--|

|                          |                                    | Normal Mode          | I of C Compiler | Static Model of C C | compiler/Assembler |  |  |  |

|                          |                                    | Min.                 | Max.            | Min.                | Max.               |  |  |  |

| Self programming start I | ibrary                             |                      | 4               | 25                  |                    |  |  |  |

| Initialize library       |                                    |                      | 44              | 3.5                 |                    |  |  |  |

| Mode check library       |                                    | 219                  | 0.625           | 218                 | .875               |  |  |  |

| Block blank check librar | y                                  | 1223                 | 6.625           | 1223                | 1.625              |  |  |  |

| Block erase library      |                                    | 36363.25             | 355771.75       | 36358.25            | 355750             |  |  |  |

| Word write library       |                                    | 679.75               | 1874.75         | 672.75              | 1867.75            |  |  |  |

|                          |                                    | (680.125)            | (1875.125)      | (673.125)           | (1868.125)         |  |  |  |

| Block verify library     |                                    | 2507                 | 2.625           | 2506                | 7.625              |  |  |  |

| Self programming end li  | brary                              |                      | 4               | 25                  |                    |  |  |  |

| Get information library  | Option value: 03H                  | 337 (3               | 337 (337.125)   |                     | 331.875)           |  |  |  |

|                          | Option value: 04H                  | 329.125              | (239.25)        | 323.87              | 5 (324)            |  |  |  |

|                          | Option value: 05H 502.25 (503.125) |                      | 497 (49         | 97.875)             |                    |  |  |  |

| Set information library  |                                    | 104978.5             | 541143.125      | 104977.5            | 541142.125         |  |  |  |

| EEPROM write library     |                                    | 962.25               | 2157.25         | 955.25              | 2150.25            |  |  |  |

|                          |                                    | (962.625)            | (2157.625)      | (955.625)           | (2150.625)         |  |  |  |

**Remarks 1.** Values in parentheses indicate values when a write start address structure is located other than in the internal high-speed RAM.

- 2. The above processing times are those during stabilized operation of the internal high-speed oscillator (RSTS = 1).

- 3. RSTS: Bit 7 of the internal oscillation mode register (RCM)

### Caution The pins mounted depend on the product. Refer to Caution 2 at the beginning of this chapter.

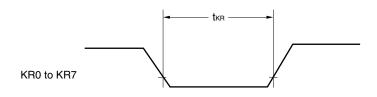

### Key Interrupt Input Timing

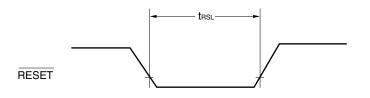

#### **RESET** Input Timing

#### Caution The pins mounted depend on the product. Refer to Caution 2 at the beginning of this chapter.

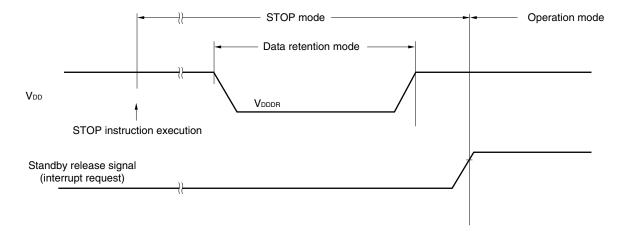

#### Data Memory STOP Mode Low Supply Voltage Data Retention Characteristics (T<sub>A</sub> = -40 to +85°C)

| Parameter                     | Symbol | Conditions | MIN.                 | TYP. | MAX. | Unit |

|-------------------------------|--------|------------|----------------------|------|------|------|

| Data retention supply voltage | VDDDR  |            | 1.44 <sup>Note</sup> |      | 5.5  | V    |

**Note** The value depends on the POC detection voltage. When the voltage drops, the data is retained until a POC reset is effected, but data is not retained when a POC reset is effected.

Caution The pins mounted depend on the product. Refer to Caution at the beginning of this chapter.

#### **X1 Oscillator Characteristics**

$(T_A = -40 \text{ to } +85^{\circ}C, 1.8 \text{ V} \le \text{V}_{DD} = \text{EV}_{DD} \le 5.5 \text{ V}, \text{V}_{SS} = \text{EV}_{SS} = \text{AV}_{SS} = 0 \text{ V})$

| Resonator            | Recommended Circuit | Parameter                                                   |                                           | Conditions                            |                       | TYP. | MAX. | Unit |

|----------------------|---------------------|-------------------------------------------------------------|-------------------------------------------|---------------------------------------|-----------------------|------|------|------|

| Ceramic              |                     | X1 clock<br>oscillation<br>frequency (fx) <sup>Note 1</sup> | specification<br>Products                 | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ | 1.0 <sup>Note 2</sup> |      | 20.0 | MHz  |

| resonator,           | vstal Vss X1 X2     |                                                             |                                           | $2.7~V \leq V_{\text{DD}} < 4.0~V$    | 1.0 <sup>Note 2</sup> |      | 10.0 |      |

| Crystal<br>resonator |                     |                                                             |                                           | $1.8~V \leq V_{\text{DD}} < 2.7~V$    | 1.0                   |      | 5.0  |      |

|                      |                     |                                                             | Expanded-                                 | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$ | 1.0 <sup>Note 2</sup> |      | 20.0 | MHz  |

|                      | 1<br>777            |                                                             | specification<br>Products<br>(µPD78F05xxA | $1.8~V \leq V_{\text{DD}} < 2.7~V$    | 1.0                   |      | 5.0  |      |

|                      |                     |                                                             | (A))                                      |                                       |                       |      |      |      |

Notes 1. Indicates only oscillator characteristics. Refer to AC Characteristics for instruction execution time.

2. It is 2.0 MHz (MIN.) when programming on the board via UART6.

Cautions 1. When using the X1 oscillator, wire as follows in the area enclosed by the broken lines in the above figures to avoid an adverse effect from wiring capacitance.

- Keep the wiring length as short as possible.

- Do not cross the wiring with the other signal lines.

- Do not route the wiring near a signal line through which a high fluctuating current flows.

- Always make the ground point of the oscillator capacitor the same potential as Vss.

- Do not ground the capacitor to a ground pattern through which a high current flows.

- Do not fetch signals from the oscillator.

- 2. Since the CPU is started by the internal high-speed oscillation clock after a reset release, check the X1 clock oscillation stabilization time using the oscillation stabilization time counter status register (OSTC) by the user. Determine the oscillation stabilization time of the OSTC register and oscillation stabilization time select register (OSTS) after sufficiently evaluating the oscillation stabilization time with the resonator to be used.

- **Remark** For the resonator selection and oscillator constant, customers are requested to either evaluate the oscillation themselves or apply to the resonator manufacturer for evaluation.

## CHAPTER 32 ELECTRICAL SPECIFICATIONS ((A2) GRADE PRODUCTS: T<sub>A</sub> = -40 to +110°C)

| Target Products | Conventional-specification Products                                                                | Expanded-specification Products                                                                           |

|-----------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 78K0/KB2        | μθD78F0500(A2), 78F0501(A2), 78F0502(A2),<br>78F0503(A2)                                           | μθD78F0500A(A2), 78F0501A(A2), 78F0502A(A2),<br>78F0503A(A2)                                              |

| 78K0/KC2        | μPD78F0511(A2), 78F0512(A2), 78F0513(A2),<br>78F0514(A2), 78F0515(A2)                              | μPD78F0511A(A2), 78F0512A(A2), 78F0513A(A2),<br>78F0514A(A2), 78F0515A(A2)                                |

| 78K0/KD2        | μPD78F0521(A2), 78F0522(A2), 78F0523(A2),<br>78F0524(A2), 78F0525(A2), 78F0526(A2),<br>78F0527(A2) | μPD78F0521A(A2), 78F0522A(A2), 78F0523A(A2),<br>78F0524A(A2), 78F0525A(A2), 78F0526A(A2),<br>78F0527A(A2) |

| 78K0/KE2        | μPD78F0531(A2), 78F0532(A2), 78F0533(A2),<br>78F0534(A2), 78F0535(A2), 78F0536(A2),<br>78F0537(A2) | μPD78F0531A(A2), 78F0532A(A2), 78F0533A(A2),<br>78F0534A(A2), 78F0535A(A2), 78F0536A(A2),<br>78F0537A(A2) |

| 78K0/KF2        | μPD78F0544(A2), 78F0545(A2), 78F0546(A2),<br>78F0547(A2)                                           | μιPD78F0544A(A2), 78F0545A(A2), 78F0546A(A2),<br>78F0547A(A2)                                             |

The following items are described separately for conventional-specification products ( $\mu$ PD78F05xx(A2)) and expanded-specification products ( $\mu$ PD78F05xxA(A2)).

- X1 clock oscillation frequency (X1 oscillator characteristics)

- Instruction cycle, peripheral hardware clock frequency, external main system clock frequency, external main system clock input high-level width, and external main system clock input low-level width (**(1) Basic operation** in **AC characteristics**)

- A/D conversion time (A/D Converter Characteristics)

- Number of rewrites per chip (Flash Memory Programming Characteristics)

### Caution The pins mounted depend on the product as follows.

#### (1) Port functions

| Port    | 78K0/KB2                  | 78K0/KC2   |            |            | 78K0/KD2   | 78K0/KE2   | 78K0/KF2     |

|---------|---------------------------|------------|------------|------------|------------|------------|--------------|

|         | 30/36 Pins                | 38 Pins    | 44 Pins    | 48 Pins    | 52 Pins    | 64 Pins    | 80 Pins      |

| Port 0  | P00, P01                  |            |            |            | P00 to P03 | P00 to P06 |              |

| Port 1  | P10 to P17                |            |            |            |            |            |              |

| Port 2  | P20 to P23                | P20 to P25 | P20 to P27 |            |            |            |              |

| Port 3  | P30 to P33                |            |            |            |            |            |              |

| Port 4  | -                         | _          | P40, P41   |            |            | P40 to P43 | P40 to P47   |

| Port 5  | -                         |            |            |            |            | P50 to P53 | P50 to P57   |

| Port 6  | P60, P61                  | P60 to P63 |            |            |            |            | P60 to P67   |

| Port 7  | -                         | P70, P71   | P70 to P73 | P70 to P75 | P70 to P77 |            |              |

| Port 12 | P120 to P122 P120 to P124 |            |            |            |            |            |              |

| Port 13 | -                         |            |            | P130       |            |            |              |

| Port 14 | -                         |            |            | P140       |            | P140, P141 | P140 to P145 |

(The remaining table is on the next page.)

| Port mode register 12 (PM12)                   |  |

|------------------------------------------------|--|

| Port mode register 14 (PM14)                   |  |

| Port register 0 (P0)                           |  |

| Port register 1 (P1)                           |  |

| Port register 2 (P2)                           |  |

| Port register 3 (P3)                           |  |

| Port register 4 (P4)                           |  |

| Port register 5 (P5)                           |  |

| Port register 6 (P6)                           |  |

| Port register 7 (P7)                           |  |

| Port register 12 (P12)                         |  |

| Port register 13 (P13)                         |  |

| Port register 14 (P14)                         |  |

| Prescaler mode register 00 (PRM00)             |  |

| Prescaler mode register 01 (PRM01)             |  |

| Priority specification flag register 0H (PR0H) |  |

| Priority specification flag register 0L (PR0L) |  |

| Priority specification flag register 1H (PR1H) |  |

| Priority specification flag register 1L (PR1L) |  |

| Processor clock control register (PCC)         |  |

| Pull-up resistor option register 0 (PU0)       |  |

| Pull-up resistor option register 1 (PU1)       |  |

| Pull-up resistor option register 3 (PU3)       |  |

| Pull-up resistor option register 4 (PU4)       |  |

| Pull-up resistor option register 5 (PU5)       |  |

| Pull-up resistor option register 6 (PU6)       |  |

| Pull-up resistor option register 7 (PU7)       |  |

| Pull-up resistor option register 12 (PU12)     |  |

| Pull-up resistor option register 14 (PU14)     |  |

|                                                |  |

## [R]

| Receive buffer register 0 (RXB0)   | 435 |

|------------------------------------|-----|

| Receive buffer register 6 (RXB6)   | 459 |

| Receive shift register 0 (RXS0)    | 435 |

| Receive shift register 6 (RXS6)    | 459 |

| Remainder data register 0 (SDR0)   | 623 |

| Reset control flag register (RESF) | 691 |

## [S]

| Serial clock selection register 10 (CSIC10)             | 495 |

|---------------------------------------------------------|-----|

| Serial clock selection register 11 (CSIC11)             | 495 |

| Serial I/O shift register 0 (SIOA0)                     | 515 |

| Serial I/O shift register 10 (SIO10)                    | 492 |

| Serial I/O shift register 11 (SIO11)                    | 492 |

| Serial operation mode register 10 (CSIM10)              | 493 |

| Serial operation mode register 11 (CSIM11)              | 493 |

| Serial operation mode specification register 0 (CSIMA0) |     |

| Serial status register 0 (CSIS0)                        |     |

| R01UH0008EJ0401 Rev.4.01                                | 93  |

|           |                |                                                      |                                         |                                                                                                                                                                                                                                                                                                  | (2     | 2/30) |

|-----------|----------------|------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|

| Chapter   | Classification | Function                                             | Details of<br>Function                  | Cautions                                                                                                                                                                                                                                                                                         | Pag    | e     |

| Chapter 4 | Soft           | Memory<br>bank<br>switching<br>function<br>(products | BANK: Memory<br>bank select<br>register | Be sure to change the value of the BANK register in the common area (0000H to 7FFFH).<br>If the value of the BANK register is changed in the bank area (8000H to BFFFH), an inadvertent program loop occurs in the CPU. Therefore, never change the value of the BANK register in the bank area. | p. 150 |       |

|           |                | whose flash                                          | Memory bank                             | Instructions cannot be fetched between different memory banks.                                                                                                                                                                                                                                   | p. 151 |       |

|           |                | memory is<br>at least<br>96 KB only)                 |                                         | Branching and accessing cannot be directly executed between different memory banks. Execute branching or accessing between different memory banks via the common area.                                                                                                                           | p. 151 |       |

|           |                |                                                      |                                         | Allocate interrupt servicing in the common area.                                                                                                                                                                                                                                                 | p. 151 |       |

|           |                |                                                      |                                         | An instruction that extends from 7FFFH to 8000H can only be executed in memory bank 0.                                                                                                                                                                                                           | p. 151 |       |

| Chapter 5 | Soft           | Port<br>function                                     | P02/ <u>SO11,</u><br>P04/SCK11          | To use P02/SO11 and P04/SCK11 as general-purpose ports, set serial operation mode register 11 (CSIM11) and serial clock selection register 11 (CSIC11) to the default status (00H).                                                                                                              | p. 164 |       |

|           |                |                                                      | P10/SCK10/TxD0,<br>P12/SO10             | To use P10/SCK10/TxD0 and P12/SO10 as general-purpose ports, set serial operation mode register 10 (CSIM10) and serial clock selection register 10 (CSIC10) to the default status (00H)                                                                                                          | p. 175 |       |

|           |                |                                                      | P13/TxD6                                | To use P13/TxD6 as general-purpose port, clear bit 0 (TXDLV6) of synchronous serial interface control register 6 (ASICL6) to 0 (normal output of TxD6).                                                                                                                                          | p. 175 |       |

|           | Soft Hard      |                                                      | Port 2                                  | Make the AV_{\text{REF}} pin the same potential as the V_DD pin when port 2 is used as a digital port.                                                                                                                                                                                           | p. 181 |       |

|           |                |                                                      |                                         | For the 38-pin products of 78K0/KC2, be sure to set bits 6 and 7 of PM2 to "1", and bits 6 and 7 of P2 to "0".                                                                                                                                                                                   | p. 182 |       |

|           | Hard           |                                                      | P31/INTP2/<br>OCD1A                     | In the product with an on-chip debug function ( $\mu$ PD78F05xxD and 78F05xxDA), be sure to pull the P31/INTP2/OCD1A pin down before a reset release, to prevent malfunction.                                                                                                                    | p. 183 |       |

|           |                |                                                      |                                         | Process the P31/INTP2/OCD1A pin of the products mounted with the on-chip debug function ( $\mu$ PD78F05xxD and 78F05xxDA) as follows, when it is not used when it is connected to a flash memory programmer or an on-chip debug emulator (see the table on p.183).                               | p. 183 |       |

|           | Soft           |                                                      | Port 4                                  | For the 38-pin products of 78K0/KC2, be sure to set bits 0 and 1 of PM4 and P4 to "0".                                                                                                                                                                                                           | p. 187 |       |

|           | Hard           |                                                      | P60, P61                                | A through current flows through P60 and P61 if an intermediate potential is input to these pins, because the input buffer is also turned on when P60 and P61 are in output mode. Consequently, do not input an intermediate potential when P60 and P61 are in output mode.                       | p. 190 |       |

|           |                |                                                      | P62                                     | A through current flows through P62 if an intermediate potential is input to this pin, because the input buffer is also turned on when P62 is in output mode. Consequently, do not input an intermediate potential when P62 is in output mode.                                                   | p. 191 |       |

|           | Soft           |                                                      | Port 7                                  | For the 38-pin products of 78K0/KC2, be sure to set bits 2 and 3 of PM7 and P7 to "0".                                                                                                                                                                                                           | p. 195 |       |