# E. Kenesas Electronics America Inc - UPD78F0515AGA-GAM-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | 78K/0                                                                                 |

| Core Size                  | 8-Bit                                                                                 |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                                    |

| Number of I/O              | 41                                                                                    |

| Program Memory Size        | 60KB (60K × 8)                                                                        |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 3K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 8x10b                                                                             |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 48-LQFP                                                                               |

| Supplier Device Package    | -                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0515aga-gam-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

• Software example 1 (to branch from all areas)

| RAMD<br>R_BNKA:<br>R_BNKN:<br>RSAVEAX |                                            | SADDR<br>2<br>1<br>2                                              | ; Secures RAM for specifying a memory bank at the branch destination.<br>; Secures RAM for specifying a memory bank number at the branch destination.<br>; Secures RAM for saving the AX register.                                                                                                                   |

|---------------------------------------|--------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ETRC<br>ENTRY:                        | CSEG                                       | UNIT                                                              |                                                                                                                                                                                                                                                                                                                      |

|                                       | MOV<br>MOVW<br>BR<br>:                     | R_BNKN,#BANKNUM TEST<br>R_BNKA,#TEST<br>!BNKBR                    | ; Stores the memory bank number at the branch destination in RAM.<br>; Stores the address at the branch destination in RAM.<br>; Branches to inter-memory bank branch processing.                                                                                                                                    |

| BNKC<br>BNKBR:                        | CSEG                                       | AT 7000H                                                          |                                                                                                                                                                                                                                                                                                                      |

| Dividin.                              | MOVW<br>MOV<br>MOVW<br>PUSH<br>MOVW<br>RET | RSAVEAX,AX<br>A,R_BNKN<br>BANK,A<br>AX,R_BNKA<br>AX<br>RSAVEAX,AX | ; Saves the AX register.<br>; Acquires the memory bank number at the branch destination.<br>; Specifies the memory bank number at the branch destination.<br>; Specifies the address at the branch destination.<br>; Sets the address at the branch destination to stack.<br>; Restores the AX register.<br>; Branch |

| BN3<br>TEST:                          | CSEG                                       | BANK3                                                             |                                                                                                                                                                                                                                                                                                                      |

|                                       | MOV ···<br>:                               |                                                                   |                                                                                                                                                                                                                                                                                                                      |

| END                                   | •                                          |                                                                   |                                                                                                                                                                                                                                                                                                                      |

# Software example 2 (to branch from common area to any bank area)

| ETRC<br>ENTRY: | CSEG      | AT 2000H                      |                                                                                                                             |

|----------------|-----------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

|                | MOV<br>BR | R_BNKN,#BANKNUM TEST<br>!TEST | ; Stores the memory bank number at the branch destination in RAM.<br>; Stores the address at the branch destination in RAM. |

| BN3<br>TEST:   | CSEG      | BANK3                         |                                                                                                                             |

| 1231.          | MOV<br>:  |                               |                                                                                                                             |

| END            | :         |                               |                                                                                                                             |

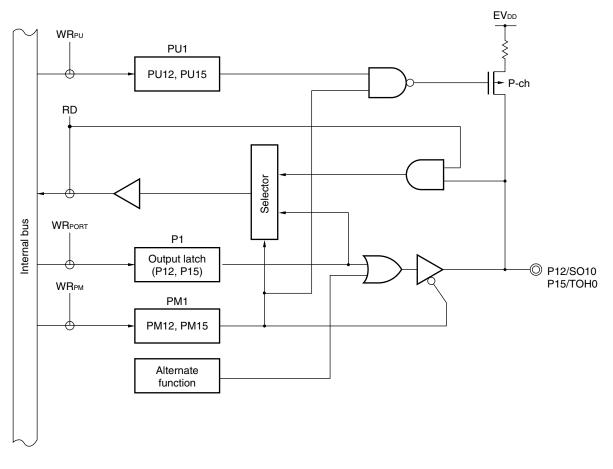

Figure 5-9. Block Diagram of P12 and P15

- P1: Port register 1

- PU1: Pull-up resistor option register 1

- PM1: Port mode register 1

- RD: Read signal

- WR××: Write signal

Remark With products not provided with an EVDD or EVSS pin, replace EVDD with VDD, or replace EVSS with VSS.

# 5.2.4 Port 3

|                                     | 78K0/KB2 | 78K0/KC2 | 78K0/KD2 | 78K0                                                       | /KE2                                                      | 78K0/KF2 |

|-------------------------------------|----------|----------|----------|------------------------------------------------------------|-----------------------------------------------------------|----------|

|                                     |          |          |          | Products<br>whose flash<br>memory is<br>less than<br>32 KB | Products<br>whose flash<br>memory is at<br>least<br>48 KB |          |

| P30/INTP1                           |          |          | •        | V                                                          |                                                           |          |

| P31/INTP2/<br>OCD1A <sup>Note</sup> |          |          | •        | N                                                          |                                                           |          |

| P32/INTP3/<br>OCD1B <sup>Note</sup> |          |          |          | N                                                          |                                                           |          |

| P33/INTP4/TI51/<br>TO51             |          |          |          | V                                                          |                                                           |          |

**Note** OCD1A and OCD1B are provided to the products with an on-chip debug function (µPD78F05xxD and 78F05xxDA) only.

#### **Remark** √: Mounted

Port 3 is an I/O port with an output latch. Port 3 can be set to the input mode or output mode in 1-bit units using port mode register 3 (PM3). When the P30 to P33 pins are used as an input port, use of an on-chip pull-up resistor can be specified in 1-bit units by pull-up resistor option register 3 (PU3).

This port can also be used for external interrupt request input and timer I/O.

Reset signal generation sets port 3 to input mode.

Figures 5-13 and 5-14 show block diagrams of port 3.

- Cautions 1. In the product with an on-chip debug function ( $\mu$ P78F05xxD and D78F05xxDA), be sure to pull the P31/INTP2/OCD1A pin down before a reset release, to prevent malfunction.

- 2. Process the P31/INTP2/OCD1A pin of the products mounted with the on-chip debug function ( $\mu$ PD78F05xxD and 78F05xxDA) as follows, when it is not used when it is connected to a flash memory programmer or an on-chip debug emulator.

|                                                                                         |                       | P31/INTP2/OCD1A                                                                                                                  |  |  |

|-----------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|

| Flash memory program                                                                    | mer connection        | Connect to EVss <sup>Note</sup> via a resistor.                                                                                  |  |  |

| On-chip debug                                                                           | During reset          |                                                                                                                                  |  |  |

| emulator connection<br>(when it is not used<br>as an on-chip debug<br>mode setting pin) | During reset released | Input: Connect to EV <sub>DD</sub> <sup>Note</sup> or EV <sub>SS</sub> <sup>Note</sup><br>via a resistor.<br>Output: Leave open. |  |  |

Note With products without an EVss pin, connect them to Vss. With products without an EVDD pin, connect them to VDD.

R01UH0008EJ0401 Rev.4.01 Jul 15, 2010

RENESAS

# Table 6-6. CPU Clock Transition and SFR Register Setting Examples (3/5)

# (6) CPU clock changing from high-speed system clock (C) to internal high-speed oscillation clock (B)

| (Setting sequence of SFR registers) |       |                         | <u> </u> |

|-------------------------------------|-------|-------------------------|----------|

| Setting Flag of SFR Register        | RSTOP | RSTS                    | MCM0     |

| Status Transition                   |       |                         |          |

| $(C) \to (B)$                       | 0     | Confirm this flag is 1. | 0        |

|                                     |       | )                       |          |

Unnecessary if the CPU is operating with the internal high-speed oscillation clock

# (7) CPU clock changing from high-speed system clock (C) to subsystem clock (D)<sup>Note</sup>

Note The 78K0/KB2 is not provided with a subsystem clock.

| (Setting sequence of SFR registers)              |           |        |         |                                             |     |  |

|--------------------------------------------------|-----------|--------|---------|---------------------------------------------|-----|--|

| Setting Flag of SFR Registe<br>Status Transition | r XTSTART | EXCLKS | OSCSELS | Waiting for<br>Oscillation<br>Stabilization | CSS |  |

| $(C) \rightarrow (D) (XT1 clock)$                | 0         | 0      | 1       | Necessary                                   | 1   |  |

|                                                  | 1         | ×      | ×       |                                             |     |  |

| (C) $\rightarrow$ (D) (external subsystem clock) | 0         | 1      | 1       | Unnecessary                                 | 1   |  |

|                                                  | J         |        |         | 2                                           |     |  |

(Setting sequence of SEB registers)

Unnecessary if the CPU is operating with the subsystem clock

#### (8) CPU clock changing from subsystem clock (D) to internal high-speed oscillation clock (B)

Note The 78K0/KB2 is not provided with a subsystem clock.

| (Set                  | ting sequence of SFR registers) |                    |                    |                | •   |

|-----------------------|---------------------------------|--------------------|--------------------|----------------|-----|

|                       | Setting Flag of SFR Register    | RSTOP              | RSTS               | MCM0           | CSS |

| Status Transition     |                                 |                    |                    |                |     |

| $(D) \rightarrow (B)$ |                                 | 0                  | Confirm this flag  | 0              | 0   |

|                       |                                 |                    | is 1.              |                |     |

|                       |                                 |                    |                    | $\uparrow$     |     |

|                       |                                 | Unnecessary if the | e CPU is operating | Unnecessary if |     |

|                       |                                 | with the interr    | al high-speed      | XSEL is 0      |     |

|                       |                                 | oscillati          | on clock           |                |     |

Remarks 1. (A) to (I) in Table 6-6 correspond to (A) to (I) in Figure 6-17 and 6-18.

| 2. | MCM0:            | Bit 0 of the main clock mode register (MCM)                       |

|----|------------------|-------------------------------------------------------------------|

|    | EXCLKS, OSCSELS: | Bits 5 and 4 of the clock operation mode select register (OSCCTL) |

|    | RSTS, RSTOP:     | Bits 7 and 0 of the internal oscillation mode register (RCM)      |

|    | XTSTART, CSS:    | Bits 6 and 4 of the processor clock control register (PCC)        |

|    | ×:               | Don't care                                                        |

|    |                  |                                                                   |

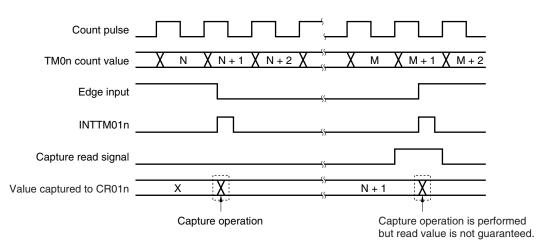

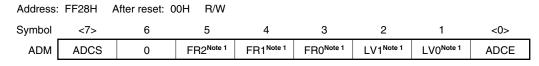

### (4) Timing of holding data by capture register

(a) When the valid edge is input to the TI00n/TI01n pin and the reverse phase of the TI00n pin is detected while CR00n/CR01n is read, CR01n performs a capture operation but the read value of CR00n/CR01n is not guaranteed. At this time, an interrupt signal (INTTM00n/INTTM01n) is generated when the valid edge of the TI00n/TI01n pin is detected (the interrupt signal is not generated when the reverse-phase edge of the TI00n pin is detected).

When the count value is captured because the valid edge of the TI00n/TI01n pin was detected, read the value of CR00n/CR01n after INTTM00n/INTTM01n is generated.

(b) The values of CR00n and CR01n are not guaranteed after 16-bit timer/event counter 0n stops.

#### (5) Setting valid edge

Set the valid edge of the TI00n pin while the timer operation is stopped (TMC0n3 and TMC0n2 = 00). Set the valid edge by using ES0n0 and ES0n1.

#### (6) Re-triggering one-shot pulse

Make sure that the trigger is not generated while an active level is being output in the one-shot pulse output mode. Be sure to input the next trigger after the current active level is output.

- **Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

- n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

| Address: FF   | Address: FF8CH After reset: 00H R/W |   |        |                                         |                           |                 |                      |                          |  |

|---------------|-------------------------------------|---|--------|-----------------------------------------|---------------------------|-----------------|----------------------|--------------------------|--|

| Symbol        | 7                                   | 6 | 5      | 4                                       | 3                         | 2               | 1                    | 0                        |  |

| TCL51         | 0                                   | 0 | 0      | 0                                       | 0                         | TCL512          | TCL511               | TCL510                   |  |

|               |                                     |   |        |                                         |                           |                 |                      |                          |  |

| TCL512 TCL511 |                                     |   | TCL510 |                                         | Coun                      | t clock selecti | ON <sup>Note 1</sup> |                          |  |

|               |                                     |   |        |                                         | fprs =                    | fprs =          | fprs =               | fprs =                   |  |

|               |                                     |   |        |                                         | 2 MHz                     | 5 MHz           | 10 MHz               | 20 MHz                   |  |

|               | 0                                   | 0 | 0      | TI51 pin falling edge <sup>Note 2</sup> |                           |                 |                      |                          |  |

|               | 0                                   | 0 | 1      | TI51 pin risir                          | ng edge <sup>Note 2</sup> |                 |                      |                          |  |

|               | 0                                   | 1 | 0      | fprs <sup>Note 3</sup>                  | 2 MHz                     | 5 MHz           | 10 MHz               | 20 MHz <sup>Note 4</sup> |  |

|               | 0                                   | 1 | 1      | fprs/2                                  | 1 MHz                     | 2.5 MHz         | 5 MHz                | 10 MHz                   |  |

|               | 1                                   | 0 | 0      | fprs/2 <sup>4</sup>                     | 125 kHz                   | 312.5 kHz       | 625 kHz              | 1.25 MHz                 |  |

|               | 1                                   | 0 | 1      | fprs/26                                 | 31.25 kHz                 | 78.13 kHz       | 156.25 kHz           | 312.5 kHz                |  |

|               | 1                                   | 1 | 0      | fprs/2 <sup>8</sup>                     | 7.81 kHz                  | 19.53 kHz       | 39.06 kHz            | 78.13 kHz                |  |

|               | 1                                   | 1 | 1      | fprs/2 <sup>12</sup>                    | 0.49 kHz                  | 1.22 kHz        | 2.44 kHz             | 4.88 kHz                 |  |

# Figure 8-6. Format of Timer Clock Selection Register 51 (TCL51)

**Notes 1.** The frequency that can be used for the peripheral hardware clock (fPRs) differs depending on the power supply voltage and product specifications.

| Supply Voltage                                                                                                           | Conventional-specification Products (µPD78F05xx and 78F05xxD) | Expanded-specification Products (µPD78F05xxA and 78F05xxDA) |

|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------|

| $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                                                                                    | $f_{PRS} \le 20 \text{ MHz}$                                  | $f_{PRS} \le 20 \text{ MHz}$                                |

| $2.7~V \leq V_{\text{DD}} < 4.0~V$                                                                                       | $f_{PRS} \leq 10 \text{ MHz}$                                 |                                                             |

| $\begin{array}{l} 1.8 \ V \leq V_{DD} < 2.7 \ V \\ (Standard products and \\ (A) \ grade \ products \ only) \end{array}$ | fprs ≤ 5 MHz                                                  | fprs ≤ 5 MHz                                                |

(The values shown in the table above are those when fPRS = fXH (XSEL = 1).)

- 2. Do not start timer operation with the external clock from the TI51 pin when the internal high-speed oscillation clock and high-speed system clock are stopped while the CPU operates with the subsystem clock, or when in the STOP mode.

- 3. If the peripheral hardware clock (fPRs) operates on the internal high-speed oscillation clock (fRH) (XSEL = 0), when  $1.8 \text{ V} \le \text{V}_{\text{DD}} < 2.7 \text{ V}$ , the setting of TCL512, TCL511, TCL510 = 0, 1, 0 (count clock: fPRs) is prohibited.

- 4. This is settable only if 4.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V.

# Cautions 1. When rewriting TCL51 to other data, stop the timer operation beforehand.

2. Be sure to clear bits 3 to 7 to "0".

Remark fPRs: Peripheral hardware clock frequency

# CHAPTER 13 A/D CONVERTER

|            | 78K0/KB2 | 78K0/KC2         | 78K0/KD2 | 78K0/KE2 | 78K0/KF2 |

|------------|----------|------------------|----------|----------|----------|

| 10-bit A/D | 4 ch     | 38 pins: 6 ch    |          | 8 ch     |          |

| converter  |          | 44/48 pins: 8 ch |          |          |          |

# **13.1 Function of A/D Converter**

The A/D converter converts an analog input signal into a digital value, and consists of up to eight channels (ANI0 to ANI7) with a resolution of 10 bits.

The A/D converter has the following function.

# • 10-bit resolution A/D conversion

10-bit resolution A/D conversion is carried out repeatedly for one analog input channel selected from ANI0 to ANI7. Each time an A/D conversion operation ends, an interrupt request (INTAD) is generated.

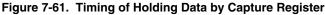

# Figure 13-1. Block Diagram of A/D Converter

Remark ANI0 to ANI3: 78K0/KB2 ANI0 to ANI5: 38-pin products of the 78K0/KC2

ANI0 to ANI7: Products other than above

# 13.3 Registers Used in A/D Converter

The A/D converter uses the following six registers.

- A/D converter mode register (ADM)

- A/D port configuration register (ADPC)

- Analog input channel specification register (ADS)

- Port mode register 2 (PM2)

- 10-bit A/D conversion result register (ADCR)

- 8-bit A/D conversion result register (ADCRH)

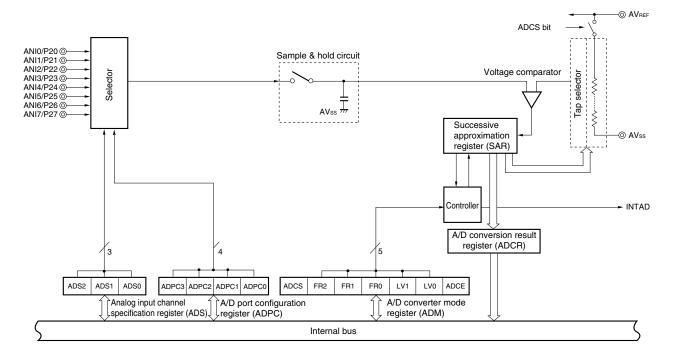

# (1) A/D converter mode register (ADM)

This register sets the conversion time for analog input to be A/D converted, and starts/stops conversion. ADM can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation clears this register to 00H.

#### Figure 13-3. Format of A/D Converter Mode Register (ADM)

| ADCS | A/D conversion operation control |

|------|----------------------------------|

| 0    | Stops conversion operation       |

| 1    | Enables conversion operation     |

| ADCE | Comparator operation control <sup>Note 2</sup> |

|------|------------------------------------------------|

| 0    | Stops comparator operation                     |

| 1    | Enables comparator operation                   |

- Notes 1. For details of FR2 to FR0, LV1, LV0, and A/D conversion, see Table 13-2 A/D Conversion Time Selection (Conventional-specification Products (μPD78F05xx and 78F05xxD)), and Table 13-3 A/D Conversion Time Selection (Expanded-specification Products (μPD78F05xxA and 78F05xxDA)).

- 2. The operation of the comparator is controlled by ADCS and ADCE, and it takes 1  $\mu$ s from operation start to operation stabilization. Therefore, when ADCS is set to 1 after 1  $\mu$ s or more has elapsed from the time ADCE is set to 1, the conversion result at that time has priority over the first conversion result. Otherwise, ignore data of the first conversion.

| Table 13-1. | Settings | of ADCS | and ADCE |

|-------------|----------|---------|----------|

|-------------|----------|---------|----------|

| ADCS | ADCE | A/D Conversion Operation                                                       |

|------|------|--------------------------------------------------------------------------------|

| 0    | 0    | Stop status (DC power consumption path does not exist)                         |

| 0    | 1    | Conversion waiting mode (comparator operation, only comparator consumes power) |

| 1    | 0    | Conversion mode (comparator operation stopped <sup>Note</sup> )                |

| 1    | 1    | Conversion mode (comparator operation)                                         |

**Note** Ignore the first conversion data.

# (1) Receive buffer register 6 (RXB6)

This 8-bit register stores parallel data converted by receive shift register 6 (RXS6).

Each time 1 byte of data has been received, new receive data is transferred to this register from RXS6. If the data length is set to 7 bits, data is transferred as follows.

• In LSB-first reception, the receive data is transferred to bits 0 to 6 of RXB6 and the MSB of RXB6 is always 0.

• In MSB-first reception, the receive data is transferred to bits 1 to 7 of RXB6 and the LSB of RXB6 is always 0. If an overrun error (OVE6) occurs, the receive data is not transferred to RXB6.

RXB6 can be read by an 8-bit memory manipulation instruction. No data can be written to this register. Reset signal generation sets this register to FFH.

# (2) Receive shift register 6 (RXS6)

This register converts the serial data input to the RxD6 pin into parallel data. RXS6 cannot be directly manipulated by a program.

#### (3) Transmit buffer register 6 (TXB6)

This buffer register is used to set transmit data. Transmission is started when data is written to TXB6. This register can be read or written by an 8-bit memory manipulation instruction. Reset signal generation sets this register to FFH.

- Cautions 1. Do not write data to TXB6 when bit 1 (TXBF6) of asynchronous serial interface transmission status register 6 (ASIF6) is 1.

- 2. Do not refresh (write the same value to) TXB6 by software during a communication operation (when bits 7 and 6 (POWER6, TXE6) of asynchronous serial interface operation mode register 6 (ASIM6) are 1 or when bits 7 and 5 (POWER6, RXE6) of ASIM6 are 1).

- 3. Set transmit data to TXB6 at least one base clock (fxcLK6) after setting TXE6 = 1.

#### (4) Transmit shift register 6 (TXS6)

This register transmits the data transferred from TXB6 from the TxD6 pin as serial data. Data is transferred from TXB6 immediately after TXB6 is written for the first transmission, or immediately before INTST6 occurs after one frame was transmitted for continuous transmission. Data is transferred from TXB6 and transmitted from the TxD6 pin at the falling edge of the base clock.

TXS6 cannot be directly manipulated by a program.

# (2) Communication operation

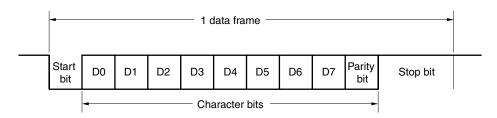

#### (a) Format and waveform example of normal transmit/receive data

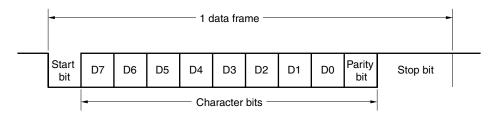

Figures 15-13 and 15-14 show the format and waveform example of the normal transmit/receive data.

#### Figure 15-13. Format of Normal UART Transmit/Receive Data

#### 1. LSB-first transmission/reception

#### 2. MSB-first transmission/reception

One data frame consists of the following bits.

- Start bit ... 1 bit

- Character bits ... 7 or 8 bits

- Parity bit ... Even parity, odd parity, 0 parity, or no parity

- Stop bit ... 1 or 2 bits

The character bit length, parity, and stop bit length in one data frame are specified by asynchronous serial interface operation mode register 6 (ASIM6).

Whether data is communicated with the LSB or MSB first is specified by bit 1 (DIR6) of asynchronous serial interface control register 6 (ASICL6).

Whether the TxD6 pin outputs normal or inverted data is specified by bit 0 (TXDLV6) of ASICL6.

• Serial operation mode register 11 (CSIM11)

Address: FF88H After reset: 00H R/W

| Symbol | <7>    | 6                                           | 5                                                                                                       | 4     | 3 | 2 | 1 | 0      |  |  |  |  |

|--------|--------|---------------------------------------------|---------------------------------------------------------------------------------------------------------|-------|---|---|---|--------|--|--|--|--|

| CSIM11 | CSIE11 | TRMD11                                      | SSE11                                                                                                   | DIR11 | 0 | 0 | 0 | CSOT11 |  |  |  |  |

|        |        |                                             |                                                                                                         |       |   |   |   |        |  |  |  |  |

|        | CSIE11 | Operation control in 3-wire serial I/O mode |                                                                                                         |       |   |   |   |        |  |  |  |  |

|        | 0      | Disables oper                               | Disables operation <sup>Note 1</sup> and asynchronously resets the internal circuit <sup>Note 2</sup> . |       |   |   |   |        |  |  |  |  |

|        |        |                                             |                                                                                                         |       |   |   |   |        |  |  |  |  |

- **Notes 1.** To use P02/SO11, P04/SCK11, and P05/SSI11/TI001 as general-purpose ports, set CSIM11 in the default status (00H).

- 2. Bit 0 (CSOT11) of CSIM11 and serial I/O shift register 11 (SIO11) are reset.

#### 16.4.2 3-wire serial I/O mode

The 3-wire serial I/O mode is used for connecting peripheral ICs and display controllers with a clocked serial interface.

In this mode, communication is executed by using three lines: the serial clock (SCK1n), serial output (SO1n), and serial input (SI1n) lines.

# (1) Registers used

- Serial operation mode register 1n (CSIM1n)

- Serial clock selection register 1n (CSIC1n)

- Port mode register 0 (PM0) or port mode register 1 (PM1)

- Port register 0 (P0) or port register 1 (P1)

The basic procedure of setting an operation in the 3-wire serial I/O mode is as follows.

- <1> Set the CSIC1n register (see Figures 16-5 and 16-6).

- <2> Set bits 4 to 6 (DIR1n, SSE11 (serial interface CSI11 only), and TRMD1n) of the CSIM1n register (see Figures 16-3 and 16-4).

- <3> Set bit 7 (CSIE1n) of the CSIM1n register to 1.  $\rightarrow$  Transmission/reception is enabled.

- <4> Write data to transmit buffer register 1n (SOTB1n). → Data transmission/reception is started.

Read data from serial I/O shift register 1n (SIO1n). → Data reception is started.

- Caution Take relationship with the other party of communication when setting the port mode register and port register.

- **Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

- n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

The relationship between the register settings and pins is shown below.

| CSIAE0 | ATE0 | MASTER0 | PM143               | P143                | PM144               | P144                | PM142               | P142                | Serial I/O                       | Serial Clock                    |                        | Pin Function           |                   |

|--------|------|---------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|----------------------------------|---------------------------------|------------------------|------------------------|-------------------|

|        |      |         |                     |                     |                     |                     |                     |                     | Shift<br>Register 0<br>Operation | Counter<br>Operation<br>Control | SIA0/<br>P143          | SOA0/<br>P144          | SCKA0/<br>P142    |

| 0      | ×    | ×       | × <sup>Note 1</sup> | X <sup>Note 1</sup> | × <sup>Note 1</sup> | × <sup>Note 1</sup> | × <sup>Note 1</sup> | × <sup>Note 1</sup> | Operation stopped                | Clear                           | P143                   | P144                   | P142              |

| 1      | 0    | 0       | 1 <sup>Note 2</sup> | × <sup>Note 2</sup> | 0 <sup>Note 3</sup> | 0 <sup>Note 3</sup> | 1                   | ×                   | Operation<br>enabled             | Count operation                 | SIA0 <sup>Note 2</sup> | SOA0 <sup>Note 3</sup> | SCKA0<br>(input)  |

|        |      | 1       |                     |                     |                     |                     | 0                   | 1                   |                                  |                                 |                        |                        | SCKA0<br>(output) |

Table 17-3. Relationship Between Register Settings and Pins

Notes 1. Can be set as port function.

- 2. Can be used as P143 when only transmission is performed. Clear bit 2 (RXEA0) of CSIMA0 to 0.

- 3. Can be used as P144 when only reception is performed. Clear bit 3 (TXEA0) of CSIMA0 to 0.

Remark×:don't careCSIAE0:Bit 7 of serial operation mode specification register 0 (CSIMA0)ATE0:Bit 6 of CSIMA0MASTER0:Bit 4 of CSIMA0PM14×:Port mode registerP14×:Port output latch

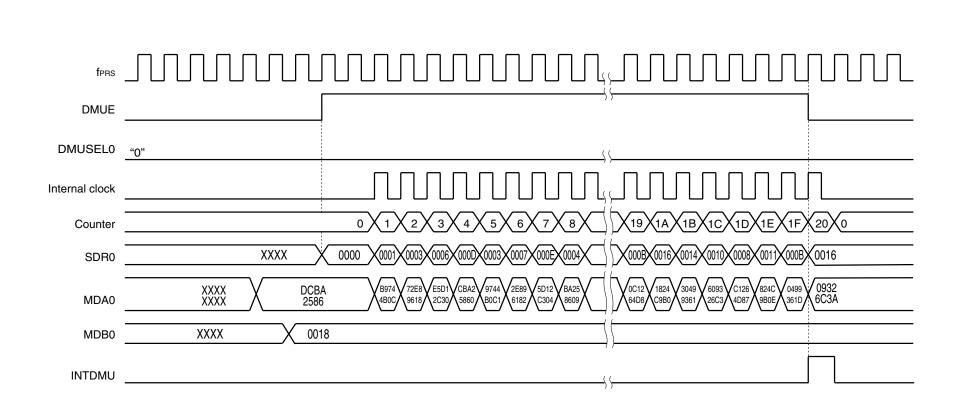

#### Figure 19-7. Timing Chart of Division Operation (DCBA2586H ÷ 0018H)

78K0/Kx2

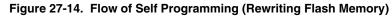

The following figure illustrates a flow of rewriting the flash memory by using a self-programming library.

Remark For details of the self-programming library, refer to 78K0 Microcontrollers Self Programming Library Type01 User's Manual (U18274E).

RENESAS

# CHAPTER 28 ON-CHIP DEBUG FUNCTION (µPD78F05xxD and 78F05xxDA ONLY)

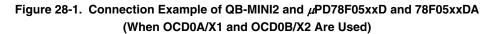

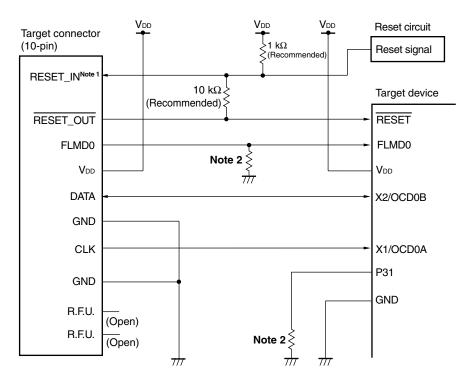

# 28.1 Connecting QB-MINI2 to $\mu$ PD78F05xxD and 78F05xxDA

The  $\mu$ PD78F05xxD and 78F05xxDA use the V<sub>DD</sub>, FLMD0, RESET, OCD0A/X1 (or OCD1A/P31), OCD0B/X2 (or OCD1B/P32), and Vss pins to communicate with the host machine via an on-chip debug emulator (QB-MINI2). Whether OCD0A/X1 and OCD1A/P31, or OCD0B/X2 and OCD1B/P32 are used can be selected.

- Caution The  $\mu$ PD78F05xxD and 78F05xxDA have an on-chip debug function, which is provided for development and evaluation. Do not use the on-chip debug function in products designated for mass production, because the guaranteed number of rewritable times of the flash memory may be exceeded when this function is used, and product reliability therefore cannot be guaranteed. Renesas Electronics is not liable for problems occurring when the on-chip debug function is used.

- RemarkμPD78F05xxD:μPD78F0503D, 78F0513D, 78F0515D, 78F0527D, 78F0537D, 78F0547DμPD78F05xxDA:μPD78F0503DA, 78F0513DA, 78F0515DA, 78F0527DA, 78F0537DA, 78F0547DA

- **Notes 1.** This connection is designed assuming that the reset signal is output from the N-ch open-drain buffer (output resistance: 100  $\Omega$  or less). For details, refer to **QB-MINI2 User's Manual (U18371E)**.

- **2.** Make pull-down resistor 470  $\Omega$  or more (10 k $\Omega$ : recommended).

#### Cautions 1. Input the clock from the OCD0A/X1 pin during on-chip debugging.

2. Control the OCD0A/X1 and OCD0B/X2 pins by externally pulling down the OCD1A/P31 pin or by using an external circuit using the P130 pin (that outputs a low level when the device is reset).

# Caution The pins mounted depend on the product. Refer to Caution 2 at the beginning of this chapter.

| Parameter                     | Symbol | (                           | Conditions                                                                                                               | Ratings     | Unit |

|-------------------------------|--------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------|------|

| Output current, high          | Іон    | Per pin                     | P00 to P06, P10 to P17,<br>P30 to P33, P40 to P47,<br>P50 to P57, P64 to P67,<br>P70 to P77, P120,<br>P130, P140 to P145 | -10         | mA   |

|                               |        | Total of all pins<br>–80 mA | P00 to P04, P40 to P47,<br>P120, P130, P140 to<br>P145                                                                   | -25         | mA   |

|                               |        |                             | P05, P06, P10 to P17,<br>P30 to P33, P50 to P57,<br>P64 to P67, P70 to P77                                               | -55         | mA   |

|                               |        | Per pin                     | P20 to P27                                                                                                               | -0.5        | mA   |

|                               |        | Total of all pins           |                                                                                                                          | -2          | mA   |

|                               |        | Per pin                     | P121 to P124                                                                                                             | -1          | mA   |

|                               |        | Total of all pins           |                                                                                                                          | -4          | mA   |

| Output current, low           | lol    | Per pin                     | P00 to P06, P10 to P17,<br>P30 to P33, P40 to P47,<br>P50 to P57, P60 to P67,<br>P70 to P77, P120, P130,<br>P140 to P145 | 30          | mA   |

|                               |        | Total of all pins<br>200 mA | P00 to P04, P40 to P47,<br>P120, P130, P140 to<br>P145                                                                   | 60          | mA   |

|                               |        |                             | P05, P06, P10 to P17,<br>P30 to P33, P50 to P57,<br>P60 to P67, P70 to P77                                               | 140         | mA   |

|                               |        | Per pin                     | P20 to P27                                                                                                               | 1           | mA   |

|                               |        | Total of all pins           |                                                                                                                          | 5           | mA   |

|                               |        | Per pin                     | P121 to P124                                                                                                             | 4           | mA   |

|                               |        | Total of all pins           |                                                                                                                          | 10          | mA   |

| Operating ambient temperature | Та     |                             |                                                                                                                          | -40 to +85  | °C   |

| Storage temperature           | Tstg   |                             |                                                                                                                          | -65 to +150 | °C   |

#### Absolute Maximum Ratings (T<sub>A</sub> = 25°C) (2/2)

- Cautions 1. Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

- 2. The value of the current that can be run per pin must satisfy the value of the current per pin and the total value of the currents of all pins.

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of port pins.

# Caution The pins mounted depend on the product. Refer to Caution 2 at the beginning of this chapter.

| Parameter                                                 | Symbol        |                                                           | Conditions                            | MIN.                 | TYP.            | MAX.            | Unit |

|-----------------------------------------------------------|---------------|-----------------------------------------------------------|---------------------------------------|----------------------|-----------------|-----------------|------|

| SCKA0 cycle time                                          | tксүз         | $4.0~V \leq V_{\text{DD}} \leq 5.4$                       | 5 V                                   | 600                  |                 |                 | ns   |

|                                                           |               | $2.7~V \leq V_{\text{DD}} < 4.4$                          | 0 V                                   | 1200                 |                 |                 | ns   |

|                                                           |               | $1.8 \text{ V} \leq \text{V}_{\text{DD}} < 2.7$           | 7 V                                   | 1800                 |                 |                 | ns   |

| SCKA0 high-/low-level width                               | tкнз,<br>tк∟з | $4.0~V \le V_{\text{DD}} \le 5.8$                         | 5 V                                   | tксүз/2 –<br>50      |                 |                 | ns   |

|                                                           |               | $2.7 \text{ V} \le \text{V}_{\text{DD}} < 4.0$            | 0 V                                   | tксүз/2 –<br>100     |                 |                 | ns   |

|                                                           |               | $1.8 \text{ V} \le \text{V}_{\text{DD}} < 2.7$            | 7 V                                   | tксүз/2 –<br>200     |                 |                 | ns   |

| SIA0 setup time (to SCKA0↑)                               | tsıкз         | $2.7~V \leq V_{\text{DD}} \leq 5.4$                       | 5 V                                   | 100                  |                 |                 | ns   |

|                                                           |               | $1.8 \text{ V} \leq \text{V}_{\text{DD}} < 2.7 \text{ V}$ |                                       | 200                  |                 |                 | ns   |

| SIA0 hold time (from $\overline{\text{SCKA0}}$ )          | tкsıз         |                                                           |                                       | 300                  |                 |                 | ns   |

| Delay time from $\overline{\text{SCKA0}}\downarrow$ to    | tкsoз         | C = 100 pF <sup>Note</sup>                                | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |                      |                 | 200             | ns   |

| SOA0 output                                               |               |                                                           | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |                      |                 | 300             | ns   |

|                                                           |               |                                                           | $1.8~V \leq V_{\text{DD}} < 2.7~V$    |                      |                 | 400             | ns   |

| Time from SCKA0↑ to STB0↑                                 | tsbd          |                                                           |                                       | tксүз/2 –<br>100     |                 |                 | ns   |

| Strobe signal high-level width                            | tsвw          | $4.0~V \le V_{\text{DD}} \le 5.8$                         | 5 V                                   | tксүз –<br><b>30</b> |                 |                 | ns   |

|                                                           |               | $2.7 \text{ V} \leq \text{V}_{\text{DD}} < 4.0 \text{ V}$ |                                       | tксүз –<br>60        |                 |                 | ns   |

|                                                           |               | $1.8 \text{ V} \leq V_{\text{DD}} < 2.7 \text{ V}$        |                                       | tксүз –<br>120       |                 |                 | ns   |

| Busy signal setup time (to                                | tвys          | $2.7~V \leq V_{\text{DD}} \leq 5.4$                       | 5 V                                   | 100                  |                 |                 | ns   |

| busy signal detection timing)                             |               | $1.8 \text{ V} \leq \text{V}_{\text{DD}} < 2.7$           | 7 V                                   | 200                  |                 |                 | ns   |

| Busy signal hold time (from busy signal detection timing) | tвүн          |                                                           |                                       |                      |                 |                 | ns   |

| Time from busy inactive to<br>SCKA0↓                      | tsps          | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                     |                                       |                      |                 | 2tксүз +<br>100 | ns   |

|                                                           |               | $2.7 \text{ V} \leq \text{V}_{\text{DD}} < 4.4$           | 0 V                                   |                      |                 | 2tксүз +<br>150 | ns   |

|                                                           |               | $1.8 \text{ V} \le \text{V}_{\text{DD}} < 2.7$            |                                       |                      | 2tксүз +<br>200 | ns              |      |

# (f) CSIA0 (master mode, SCKA0...internal clock output)

Note C is the load capacitance of the  $\overline{SCKA0}$  and SOA0 output lines.

# Caution The pins mounted depend on the product. Refer to Caution at the beginning of this chapter.

# DC Characteristics (4/4)

| (TA = -40 to +85°C, 1.8 V $\leq$ Vdd = EVdd $\leq$ 5.5 V, AVREF $\leq$ Vdd, Vss = EVss = AVss = 0 V | /) |

|-----------------------------------------------------------------------------------------------------|----|

|-----------------------------------------------------------------------------------------------------|----|

| Parameter                           | Symbol                 | Conditions                                |                                                                                                                  |                      | MIN. | TYP. | MAX. | Unit |

|-------------------------------------|------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------|------|------|------|------|

| Supply current <sup>Note 1</sup>    | IDD1                   | Operating                                 | fхн = 20 MHz,                                                                                                    | Square wave input    |      | 3.2  | 5.5  | mA   |

|                                     |                        | mode                                      | $V_{\text{DD}} = 5.0 \text{ V}^{\text{Note 2}}$                                                                  | Resonator connection |      | 4.5  | 6.9  | mA   |

|                                     |                        |                                           | fхн = 10 MHz,                                                                                                    | Square wave input    |      | 1.6  | 2.8  | mA   |

|                                     |                        |                                           | $V_{\text{DD}} = 5.0 \text{ V}^{\text{Notes 2, 3}}$                                                              | Resonator connection |      | 2.3  | 3.9  | mA   |

|                                     |                        |                                           | fхн = 10 MHz                                                                                                     | Square wave input    |      | 1.5  | 2.7  | mA   |

|                                     |                        |                                           | $V_{DD} = 3.0 \ V^{Notes  2,  3}$                                                                                | Resonator connection |      | 2.2  | 3.2  | mA   |

|                                     |                        |                                           | fxн = 5 MHz,                                                                                                     | Square wave input    |      | 0.9  | 1.6  | mA   |

|                                     |                        |                                           | $V_{DD} = 3.0 V^{Notes 2, 3}$                                                                                    | Resonator connection |      | 1.3  | 2.0  | mA   |

|                                     |                        |                                           | fxн = 5 MHz,                                                                                                     | Square wave input    |      | 0.7  | 1.4  | mA   |

|                                     |                        |                                           | $V_{DD} = 2.0 \ V^{Notes 2, 3}$                                                                                  | Resonator connection |      | 1.0  | 1.6  | mA   |

|                                     |                        |                                           | fвн = 8 MHz, Vdd = 5.                                                                                            | 0 V Note 4           |      | 1.4  | 2.5  | mA   |

|                                     |                        |                                           | fsuв = 32.768 kHz,                                                                                               | Square wave input    |      | 6    | 30   | μA   |

|                                     |                        |                                           | $V_{\text{DD}} = 5.0 \text{ V}^{\text{Note 5}}$                                                                  | Resonator connection |      | 15   | 35   | μA   |

|                                     | IDD2                   | HALT<br>mode                              | fхн = 20 MHz,                                                                                                    | Square wave input    |      | 0.8  | 2.6  | mA   |

|                                     |                        |                                           | $V_{DD} = 5.0 \text{ V}^{\text{Note 2}}$ $f_{XH} = 10 \text{ MHz},$ $V_{DD} = 5.0 \text{ V}^{\text{Notes 2, 3}}$ | Resonator connection |      | 2.0  | 4.4  | mA   |

|                                     |                        |                                           |                                                                                                                  | Square wave input    |      | 0.4  | 1.3  | mA   |

|                                     |                        |                                           |                                                                                                                  | Resonator connection |      | 1.0  | 2.4  | mA   |

|                                     |                        |                                           | fxн = 5 MHz,                                                                                                     | Square wave input    |      | 0.2  | 0.65 | mA   |

|                                     |                        |                                           | $V_{DD} = 3.0 \ V^{Notes 2, 3}$                                                                                  | Resonator connection |      | 0.5  | 1.1  | mA   |

|                                     |                        |                                           | frн = 8 MHz, Vdd = 5.                                                                                            |                      | 0.4  | 1.2  | mA   |      |

|                                     |                        |                                           | fsuв = 32.768 kHz,                                                                                               | Square wave input    |      | 3.0  | 27   | μA   |

|                                     |                        |                                           | $V_{\text{DD}} = 5.0 \text{ V}^{\text{Note 5}}$                                                                  | Resonator connection |      | 12   | 32   | μA   |

|                                     | DD3 <sup>Note 6</sup>  | STOP mode                                 | 9                                                                                                                |                      |      | 1    | 20   | μA   |

|                                     |                        |                                           | $T_A = -40 \text{ to } +70 ^{\circ}\text{C}$                                                                     |                      |      | 1    | 10   | μA   |

| A/D converter<br>operating current  | IADC <sup>Note 7</sup> | $2.3 \text{ V} \leq \text{AV}_{\text{P}}$ | $ref \leq V_{DD}, ADCS = 1$                                                                                      |                      |      | 0.86 | 1.9  | mA   |

| Watchdog timer<br>operating current | WDT <sup>Note 8</sup>  | During 240 operation                      | kHz internal low-speed                                                                                           |                      | 5    | 10   | μA   |      |

| LVI operating current               | LVI Note 9             |                                           |                                                                                                                  |                      |      | 9    | 18   | μA   |

Remarks 1. fxH: High-speed system clock frequency (X1 clock oscillation frequency or external main system clock frequency)

- 2. free: Internal high-speed oscillation clock frequency

- 3. fsub: Subsystem clock frequency (XT1 clock oscillation frequency or external subsystem clock frequency)

(Notes on next page)

#### SALES OFFICES

**Renesas Electronics Corporation**

http://www.renesas.com

Refer to "http://www.renesas.com/" for the latest and detailed information. Renesas Electronics America Inc. 2880 Scott Boulevard Santa Clara, CA 95050-2554, U.S.A. Tel: +1-408-588-6000, Fax: +1-408-588-6130 Renesas Electronics Canada Limited 1011 Nicholson Read, Newmarket, Onlario L3Y 9C3, Canada Tel: +1-905-898-5441, Fax: +1-905-898-3220 Renesas Electronics Curope Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tel: +44-1625-855-100, Fax: +44-1628-856-900 Renesas Electronics Curope Limited Tel: +49-215-855-100, Fax: +44-211-6503, Tax: +44-1628-856-900 Renesas Electronics (China) Co., Ltd. The Flore, Output Disselford, Germany Tel: +49-211-6503, Fax: +49-211-6503-1327 Renesas Electronics (China) Co., Ltd. The Flore, Output Disselford, Germany Tel: +49-21-155, Fax: +86-10-8235-7679 Renesas Electronics (China) Co., Ltd. Unit 204, 205, AZIA Center, No. 1233 Lujiazui Ring Rd., Pudong District, Shanghai 200120, China Tel: +652-13677-1181, Fax: +86-21-6867-7858 / -7858 Renesas Electronics Taine Kong Limited Unit 1001-1613, 16F, Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: +6562-1666-9316, Fax: +852-2886-9202/9044 Renesas Electronics Inhor Road Tainei, Taiwan Tel: +862-24175-9600, Fax: +865-2415-9670 Renesas Electronics Singapore Ple. Ltd. Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No. 18, Jin Persiaran Barat, 46050 Petalling Jaya, Selangor Darul Ehsan, Malaysia Tel: +656-213-0220, Fax: +636-278-8001 Renesas Electronics Korae Co., Ltd. The Sock B, Menara Amcorp, Amcorp Trade Centre, No. 18, Jin Persiaran Barat, 46050 Petalling Jaya, Selangor Darul Ehsan, Malaysia Tel: +602-35930, Fax: +636-278-59510

> © 2010 Renesas Electronics Corporation. All rights reserved. Colophon 1.0