## E·XF kenesas Electronics America Inc - UPD78F0523AGB-GAG-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                   |

|----------------------------|---------------------------------------------------------------------------------------|

| Core Processor             | 78K/0                                                                                 |

| Core Size                  | 8-Bit                                                                                 |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                                    |

| Number of I/O              | 45                                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 1K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 8x10b                                                                             |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 52-LQFP                                                                               |

| Supplier Device Package    | <u> </u>                                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0523agb-gag-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| CHAPTER 15 SERIAL INTERFACE UART6                                      |     |

|------------------------------------------------------------------------|-----|

| 15.1 Functions of Serial Interface UART6                               |     |

| 15.2 Configuration of Serial Interface UART6                           |     |

| 15.3 Registers Controlling Serial Interface UART6                      |     |

| 15.4 Operation of Serial Interface UART6                               |     |

| 15.4.1 Operation stop mode                                             | 469 |

| 15.4.2 Asynchronous serial interface (UART) mode                       | 470 |

| 15.4.3 Dedicated baud rate generator                                   | 483 |

| 15.4.4 Calculation of baud rate                                        |     |

| CHAPTER 16 SERIAL INTERFACES CSI10 AND CSI11                           | 490 |

| 16.1 Functions of Serial Interfaces CSI10 and CSI11                    |     |

| 16.2 Configuration of Serial Interfaces CSI10 and CSI11                |     |

| 16.3 Registers Controlling Serial Interfaces CSI10 and CSI11           |     |

| 16.4 Operation of Serial Interfaces CSI10 and CSI11                    |     |

| 16.4.1 Operation stop mode                                             |     |

| 16.4.2 3-wire serial I/O mode                                          |     |

|                                                                        |     |

| CHAPTER 17 SERIAL INTERFACE CSIA0                                      | 512 |

| 17.1 Functions of Serial Interface CSIA0                               |     |

| 17.2 Configuration of Serial Interface CSIA0                           |     |

| 17.3 Registers Controlling Serial Interface CSIA0                      |     |

| 17.4 Operation of Serial Interface CSIA0                               |     |

| 17.4.1 Operation stop mode                                             |     |

| 17.4.2 3-wire serial I/O mode                                          | 525 |

| 17.4.3 3-wire serial I/O mode with automatic transmit/receive function | 530 |

| CHAPTER 18 SERIAL INTERFACE IIC0                                       | 550 |

| 18.1 Functions of Serial Interface IIC0                                | 550 |

| 18.2 Configuration of Serial Interface IIC0                            |     |

| 18.3 Registers to Control Serial Interface IIC0                        |     |

| 18.4 I <sup>2</sup> C Bus Mode Functions                               |     |

| 18.4.1 Pin configuration                                               |     |

| 18.5 I <sup>2</sup> C Bus Definitions and Control Methods              |     |

| 18.5.1 Start conditions                                                |     |

| 18.5.2 Addresses                                                       |     |

| 18.5.3 Transfer direction specification                                |     |

| 18.5.4 Acknowledge (ACK)                                               |     |

| 18.5.5 Stop condition                                                  |     |

| 18.5.6 Wait                                                            |     |

| 18.5.7 Canceling wait                                                  |     |

| 18.5.8 Interrupt request (INTIIC0) generation timing and wait control  |     |

| 18.5.9 Address match detection method                                  |     |

| 18.5.10 Error detection                                                |     |

| 18.5.11 Extension code                                                 |     |

| 18.5.12 Arbitration                                                    |     |

| 18.5.13 Wakeup function                                                |     |

| 18.5.14 Communication reservation                                      |     |

|                                                                        |     |

#### 1.1.6 Interrupt response time for self programming library

#### (1) Conventional-specification products (µPD78F05xx and 78F05xxD) (1/2)

#### <1> When internal high-speed oscillation clock is used

| Library Name              | Interrupt Response Time (µs (Max.))    |                                          |                                        |                                          |  |  |

|---------------------------|----------------------------------------|------------------------------------------|----------------------------------------|------------------------------------------|--|--|

|                           | Normal Model                           | of C Compiler                            | Static Model of C Compiler/Assembler   |                                          |  |  |

|                           | Entry RAM location<br>is outside short | Entry RAM location<br>is in short direct | Entry RAM location<br>is outside short | Entry RAM location<br>is in short direct |  |  |

|                           | direct addressing                      | addressing range                         | direct addressing                      | addressing range                         |  |  |

|                           | range                                  |                                          | range                                  |                                          |  |  |

| Block blank check library | 933.6                                  | 668.6                                    | 927.9                                  | 662.9                                    |  |  |

| Block erase library       | 1026.6                                 | 763.6                                    | 1020.9                                 | 757.9                                    |  |  |

| Word write library        | 2505.8                                 | 1942.8                                   | 2497.8                                 | 1934.8                                   |  |  |

| Block verify library      | 958.6                                  | 693.6                                    | 952.9                                  | 687.9                                    |  |  |

| Set information library   | 476.5                                  | 211.5                                    | 475.5                                  | 210.5                                    |  |  |

| EEPROM write library      | 2760.8                                 | 2168.8                                   | 2759.5                                 | 2167.5                                   |  |  |

- **Remarks 1.** The above interrupt response times are those during stabilized operation of the internal high-speed oscillator (RSTS = 1).

- 2. RSTS: Bit 7 of the internal oscillation mode register (RCM)

| <2> When high-speed system clock is used | (normal model of C compiler) |

|------------------------------------------|------------------------------|

|------------------------------------------|------------------------------|

| Library Name                         | Interrupt Response Time (µs (Max.))    |                                          |                                        |                                          |  |  |  |  |

|--------------------------------------|----------------------------------------|------------------------------------------|----------------------------------------|------------------------------------------|--|--|--|--|

|                                      | RSTOP = 0                              | ), RSTS = 1                              | RSTOP = 1                              |                                          |  |  |  |  |

|                                      | Entry RAM location<br>is outside short | Entry RAM location<br>is in short direct | Entry RAM location<br>is outside short | Entry RAM location<br>is in short direct |  |  |  |  |

|                                      | direct addressing                      | addressing range                         | direct addressing                      | addressing range                         |  |  |  |  |

|                                      | range                                  |                                          | range                                  |                                          |  |  |  |  |

| Block blank check library            | 179/fcpu + 507                         | 179/fcpu + 407                           | 179/fcpu + 1650                        | 179/fcpu + 714                           |  |  |  |  |

| Block erase library                  | 179/fcpu + 559                         | 179/fcpu + 460                           | 179/fcpu + 1702                        | 179/fcpu + 767                           |  |  |  |  |

| Word write library                   | 333/fcpu + 1589                        | 333/fcpu + 1298                          | 333/fcpu + 2732                        | 333/fcpu + 1605                          |  |  |  |  |

| Block verify library                 | 179/fcpu + 518                         | 179/fcpu + 418                           | 179/fcpu + 1661                        | 179/fcpu + 725                           |  |  |  |  |

| Set information library              | 80/fcpu + 370                          | 80/fcpu + 165                            | 80/fcpu + 1513                         | 80/fcpu + 472                            |  |  |  |  |

| EEPROM write library <sup>Note</sup> | 29/fcpu + 1759                         | 29/fcpu + 1468                           | 29/fcpu + 1759                         | 29/fcpu + 1468                           |  |  |  |  |

|                                      | 333/fcpu + 834                         | 333/fcpu + 512                           | 333/fcpu + 2061                        | 333/fcpu + 873                           |  |  |  |  |

- **Note** The longer value of the EEPROM write library interrupt response time becomes the Max. value, depending on the value of fcPu.

- Remarks 1. fCPU: CPU operation clock frequency

- 2. RSTOP: Bit 0 of the internal oscillation mode register (RCM)

- 3. RSTS: Bit 7 of the internal oscillation mode register (RCM)

|                              |                                              |                                            |                        | (5/6                                                                                                                                                                               |

|------------------------------|----------------------------------------------|--------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 78K0/Kx2<br>Microcontrollers | Package                                      | Product<br>type                            | Quality<br>grace       | Part Number                                                                                                                                                                        |

| 78K0/KE2                     | 64-pin plastic<br>LQFP (12x12)               | Conventional-<br>specification<br>products | Standard<br>products   | μPD78F0531GK-UET-A, 78F0532GK-UET-A,<br>78F0533GK-UET-A, 78F0534GK-UET-A,<br>78F0535GK-UET-A, 78F0536GK-UET-A,<br>78F0537GK-UET-A, 78F0537DGK-UET-A <sup>Note</sup>                |

|                              |                                              |                                            | (A) grade<br>products  | μPD78F0531GK(A)-GAJ-AX, 78F0532GK(A)-GAJ-AX,<br>78F0533GK(A)-GAJ-AX, 78F0534GK(A)-GAJ-AX,<br>78F0535GK(A)-GAJ-AX, 78F0536GK(A)-GAJ-AX,<br>78F0537GK(A)-GAJ-AX                      |

|                              |                                              |                                            | (A2) grade<br>products | μPD78F0531GK(A2)-GAJ-AX, 78F0532GK(A2)-GAJ-AX,<br>78F0533GK(A2)-GAJ-AX, 78F0534GK(A2)-GAJ-AX,<br>78F0535GK(A2)-GAJ-AX, 78F0536GK(A2)-GAJ-AX,<br>78F0537GK(A2)-GAJ-AX               |

|                              |                                              | Expanded-<br>specification<br>products     | Standard<br>products   | µPD78F0531AGK-GAJ-AX, 78F0532AGK-GAJ-AX,<br>78F0533AGK-GAJ-AX, 78F0534AGK-GAJ-AX,<br>78F0535AGK-GAJ-AX, 78F0536AGK-GAJ-AX,<br>78F0537AGK-GAJ-AX, 78F0537DAGK-GAJ-AX <sup>№0®</sup> |

|                              |                                              |                                            | (A) grade<br>products  | µPD78F0531AGKA-GAJ-G, 78F0532AGKA-GAJ-G,<br>78F0533AGKA-GAJ-G, 78F0534AGKA-GAJ-G,<br>78F0535AGKA-GAJ-G, 78F0536AGKA-GAJ-G,<br>78F0537AGKA-GAJ-G                                    |

|                              |                                              |                                            | (A2) grade<br>products | μPD78F0531AGKA2-GAJ-G, 78F0532AGKA2-GAJ-G,<br>78F0533AGKA2-GAJ-G, 78F0534AGKA2-GAJ-G,<br>78F0535AGKA2-GAJ-G, 78F0536AGKA2-GAJ-G,<br>78F0537AGKA2-GAJ-G                             |

|                              | 64-pin plastic<br>TQFP (fine pitch)<br>(7x7) | Conventional-<br>specification<br>products | Standard<br>products   | µPD78F0531GA-9EV-A, 78F0532GA-9EV-A,<br>78F0533GA-9EV-A, 78F0534GA-9EV-A, 78F0535GA-9EV-A,<br>78F0536GA-9EV-A, 78F0537GA-9EV-A,<br>78F0537DGA-9EV-A <sup>№0®</sup>                 |

|                              |                                              | Expanded-<br>specification<br>products     | Standard products      | μPD78F0531AGA-HAB-AX, 78F0532AGA-HAB-AX,<br>78F0533AGA-HAB-AX, 78F0534AGA-HAB-AX,<br>78F0535AGA-HAB-AX, 78F0536AGA-HAB-AX,<br>78F0537AGA-HAB-AX, 78F0537DAGA-HAB-AX <sup>№0®</sup> |

**Note** The μPD78F0537D and 78F0537DA have an on-chip debug function, which is provided for development and evaluation. Do not use the on-chip debug function in products designated for mass production, because the guaranteed number of rewritable times of the flash memory may be exceeded when this function is used, and product reliability therefore cannot be guaranteed. Renesas Electronics is not liable for problems occurring when the on-chip debug function is used.

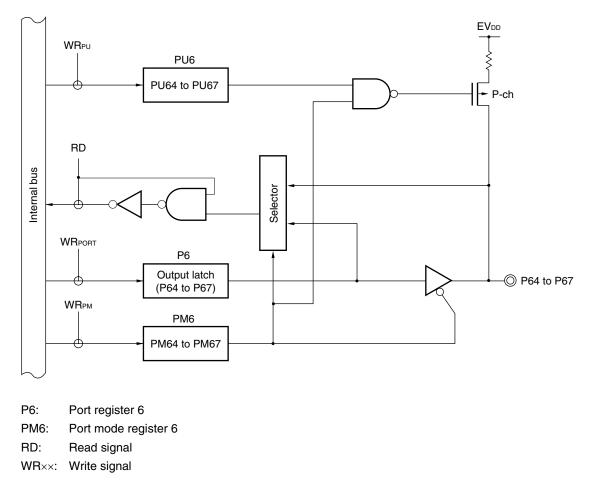

Figure 5-20. Block Diagram of P64 to P67

Remark With products not provided with an EVDD or EVSS pin, replace EVDD with VDD, or replace EVSS with VSS.

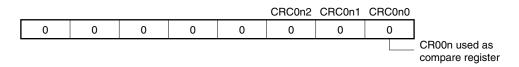

#### Figure 7-4. Format of 16-Bit Timer Capture/Compare Register 00n (CR00n)

Address: FF12H, FF13H (CR000), FFB2H, FFB3H (CR001)

FF13H (CR000), FFB3H (CR001)

After reset: 0000H R/W

|            |    |    |    |    |    |    |   |   | 11 1211 (011000), 11 D211 (011001) |   |   |   |   |   |   |   |

|------------|----|----|----|----|----|----|---|---|------------------------------------|---|---|---|---|---|---|---|

|            |    |    |    |    |    |    |   |   |                                    |   |   |   |   |   |   |   |

|            | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7                                  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| CR00n      |    |    |    |    |    |    |   |   |                                    |   |   |   |   |   |   |   |

| (n = 0, 1) |    |    |    |    |    |    |   |   |                                    |   |   |   |   |   |   |   |

#### (i) When CR00n is used as a compare register

The value set in CR00n is constantly compared with the TM0n count value, and an interrupt request signal (INTTM00n) is generated if they match. The value is held until CR00n is rewritten.

## Caution CR00n does not perform the capture operation when it is set in the comparison mode, even if a capture trigger is input to it.

#### (ii) When CR00n is used as a capture register

The count value of TM0n is captured to CR00n when a capture trigger is input.

As the capture trigger, an edge of a phase reverse to that of the TI00n pin or the valid edge of the TI01n pin can be selected by using CRC0n or PRM0n.

#### Figure 7-5. Format of 16-Bit Timer Capture/Compare Register 01n (CR01n)

| Address:                     | Address: FF14H, FF15H (CR010), FFB4H, FFB5H (CR011) |    |    |    |    |    |   |   |      | After  | r reset | : 000 | он    | R/W   | , |   |

|------------------------------|-----------------------------------------------------|----|----|----|----|----|---|---|------|--------|---------|-------|-------|-------|---|---|

| FF15H (CR010), FFB5H (CR011) |                                                     |    |    |    |    |    |   |   | FF14 | IH (CF | R010),  | FFB4  | H (CF | RO11) |   |   |

|                              |                                                     |    |    |    |    |    |   |   |      |        |         |       |       |       |   |   |

|                              | 15                                                  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7    | 6      | 5       | 4     | 3     | 2     | 1 | 0 |

| CR01n<br>(n = 0, 1)          |                                                     |    |    |    |    |    |   |   |      |        |         |       |       |       |   |   |

#### (i) When CR01n is used as a compare register

The value set in CR01n is constantly compared with the TM0n count value, and an interrupt request signal (INTTM01n) is generated if they match.

## Caution CR01n does not perform the capture operation when it is set in the comparison mode, even if a capture trigger is input to it.

#### (ii) When CR01n is used as a capture register

The count value of TM0n is captured to CR01n when a capture trigger is input.

It is possible to select the valid edge of the TI00n pin as the capture trigger. The TI00n pin valid edge is set by PRM0n.

#### **Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2,

78K0/KD2 products

n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

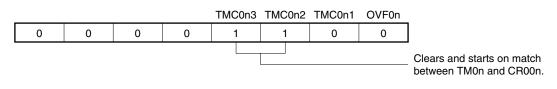

#### Figure 7-18. Example of Register Settings for Interval Timer Operation

#### (a) 16-bit timer mode control register 0n (TMC0n)

#### (b) Capture/compare control register 0n (CRC0n)

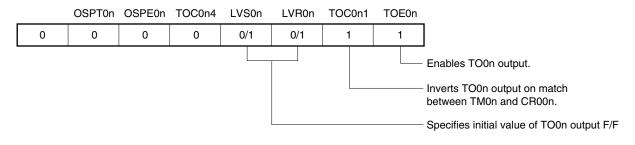

#### (c) 16-bit timer output control register 0n (TOC0n)

|   | OSPT0n | OSPE0n | TOC0n4 | LVS0n | LVR0n | TOC0n1 | TOE0n |

|---|--------|--------|--------|-------|-------|--------|-------|

| 0 | 0      | 0      | 0      | 0     | 0     | 0      | 0     |

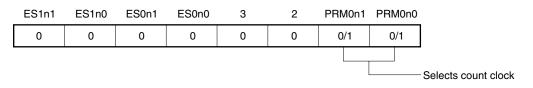

#### (d) Prescaler mode register 0n (PRM0n)

| ES1n1 | ES1n0 | ES0n1 | ES0n0 | 3 | 2 | PRM0n1 | PRM0n0 |                     |

|-------|-------|-------|-------|---|---|--------|--------|---------------------|

| 0     | 0     | 0     | 0     | 0 | 0 | 0/1    | 0/1    |                     |

|       |       |       |       |   |   |        |        |                     |

|       |       |       |       |   |   | l      |        | Selects count clock |

#### (e) 16-bit timer counter 0n (TM0n)

By reading TM0n, the count value can be read.

#### (f) 16-bit capture/compare register 00n (CR00n)

If M is set to CR00n, the interval time is as follows.

• Interval time = (M + 1) × Count clock cycle

Setting CR00n to 0000H is prohibited.

#### (g) 16-bit capture/compare register 01n (CR01n)

Usually, CR01n is not used for the interval timer function. However, a compare match interrupt (INTTM01n) is generated when the set value of CR01n matches the value of TM0n. Therefore, mask the interrupt request by using the interrupt mask flag (TMMK01n).

**Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

#### 78K0/Kx2

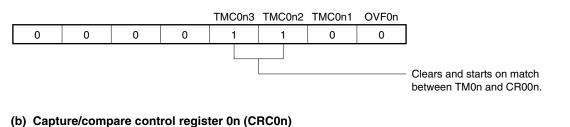

#### Figure 7-22. Example of Register Settings for Square-Wave Output Operation

#### (a) 16-bit timer mode control register 0n (TMC0n)

# CRC0n2 CRC0n1 CRC0n0 0 0 0 0 0 0 CR00n 0 0 0 0 0 0

#### (c) 16-bit timer output control register 0n (TOC0n)

#### (d) Prescaler mode register 0n (PRM0n)

#### (e) 16-bit timer counter 0n (TM0n)

By reading TM0n, the count value can be read.

#### (f) 16-bit capture/compare register 00n (CR00n)

If M is set to CR00n, the interval time is as follows.

• Square wave frequency =  $1 / [2 \times (M + 1) \times Count clock cycle]$

Setting CR00n to 0000H is prohibited.

#### (g) 16-bit capture/compare register 01n (CR01n)

Usually, CR01n is not used for the square-wave output function. However, a compare match interrupt (INTTM01n) is generated when the set value of CR01n matches the value of TM0n.

Therefore, mask the interrupt request by using the interrupt mask flag (TMMK01n).

**Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

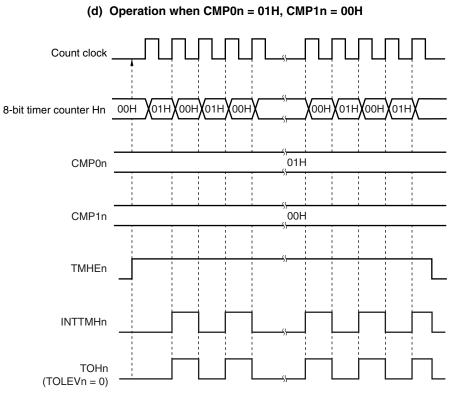

Figure 9-12. Operation Timing in PWM Output Mode (3/4)

**Remark** n = 0, 1

## Caution Do not change the count clock and interval time (by setting bits 4 to 7 (WTM4 to WTM7) of WTM) during watch timer operation.

**Remarks 1.** fw: Watch timer clock frequency (fPRs/2<sup>7</sup> or fsub)

- 2. fprs: Peripheral hardware clock frequency

- 3. fsub: Subsystem clock frequency

The setting methods are described below.

- <1> Set bit 0 (ADCE) of the A/D converter mode register (ADM) to 1.

- <2> Set the channel to be used in the analog input mode by using bits 3 to 0 (ADPC3 to ADPC0) of the A/D port configuration register (ADPC) and bits 7 to 0 (PM27 to PM20) of port mode register 2 (PM2).

- <3> Select conversion time by using bits 5 to 1 (FR2 to FR0, LV1, and LV0) of ADM.

- <4> Select a channel to be used by using bits 2 to 0 (ADS2 to ADS0) of the analog input channel specification register (ADS).

- <5> Set bit 7 (ADCS) of ADM to 1 to start A/D conversion.

- <6> When one A/D conversion has been completed, an interrupt request signal (INTAD) is generated.

- <7> Transfer the A/D conversion data to the A/D conversion result register (ADCR, ADCRH).

<Change the channel>

- <8> Change the channel using bits 2 to 0 (ADS2 to ADS0) of ADS to start A/D conversion.

- <9> When one A/D conversion has been completed, an interrupt request signal (INTAD) is generated.

- <10> Transfer the A/D conversion data to the A/D conversion result register (ADCR, ADCRH).

<Complete A/D conversion>

<11> Clear ADCS to 0.

<12> Clear ADCE to 0.

Cautions 1. Make sure the period of <1> to <5> is 1  $\mu$ s or more.

- 2. <1> may be done between <2> and <4>.

- 3. <1> can be omitted. However, ignore data of the first conversion after <5> in this case.

- The period from <6> to <9> differs from the conversion time set using bits 5 to 1 (FR2 to FR0, LV1, LV0) of ADM. The period from <8> to <9> is the conversion time set using FR2 to FR0, LV1, and LV0.

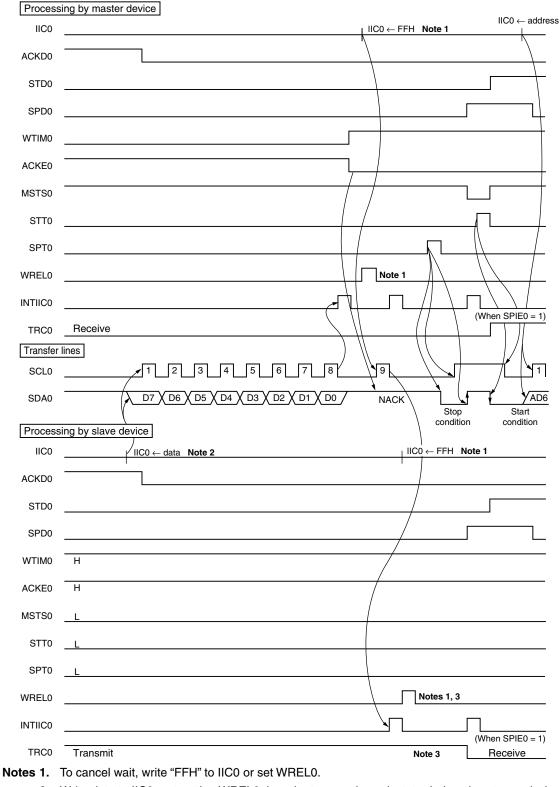

Figure 18-28. Example of Slave to Master Communication (When 8-Clock and 9-Clock Wait Is Selected for Master, 9-Clock Wait Is Selected for Slave) (3/3)

#### (3) Stop condition

- 2. Write data to IIC0, not setting WREL0, in order to cancel a wait state during slave transmission.

- **3.** If a wait state during slave transmission is canceled by setting WREL0, TRC0 will be cleared.

| Address: FF                         | E4H After r                                                                                                                                                              | eset: FFH     | R/W            |        |                         |                             |                         |                                 |  |  |  |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|--------|-------------------------|-----------------------------|-------------------------|---------------------------------|--|--|--|

| Symbol                              | <7>                                                                                                                                                                      | <6>           | <5>            | <4>    | <3>                     | <2>                         | <1>                     | <0>                             |  |  |  |

| MK0L                                | SREMK6                                                                                                                                                                   | PMK5          | PMK4           | PMK3   | PMK2                    | PMK1                        | PMK0                    | LVIMK                           |  |  |  |

| Address: FFE5H After reset: FFH R/W |                                                                                                                                                                          |               |                |        |                         |                             |                         |                                 |  |  |  |

| Symbol                              | <7>                                                                                                                                                                      | <6>           | <5>            | <4>    | <3>                     | <2>                         | <1>                     | <0>                             |  |  |  |

| МКОН                                | TMMK010                                                                                                                                                                  | ТММК000       | TMMK50         | ТММКНО | TMMKH1                  | DUALMK0<br>CSIMK10<br>STMK0 | STMK6                   | SRMK6                           |  |  |  |

| Address: FF                         | Address:         FFE6H         After reset:         FFH         R/W           Symbol         <7>         <6>         <4>         <3>         <2>         <1>         <0> |               |                |        |                         |                             |                         |                                 |  |  |  |

| MK1L                                | PMK7                                                                                                                                                                     | PMK6          | WTMK           | KRMK   | TMMK51                  | WTIMK                       | SRMK0                   | ADMK                            |  |  |  |

|                                     |                                                                                                                                                                          | 1             |                |        |                         |                             |                         |                                 |  |  |  |

| Address: FF                         | E7H After r                                                                                                                                                              | eset: FFH     | R/W            |        |                         |                             |                         |                                 |  |  |  |

| Symbol                              | 7                                                                                                                                                                        | 6             | 5              | 4      | <3>                     | <2>                         | <1>                     | <0>                             |  |  |  |

| MK1H                                | 1                                                                                                                                                                        | 1             | 1              | 1      | TMMK011 <sup>Note</sup> | TMMK001 <sup>Note</sup>     | CSIMK11 <sup>Note</sup> | IICMK0<br>DMUMK <sup>Note</sup> |  |  |  |

|                                     |                                                                                                                                                                          |               |                |        |                         |                             |                         |                                 |  |  |  |

|                                     | ХХМКХ                                                                                                                                                                    |               |                | Interr | upt servicing o         | control                     |                         |                                 |  |  |  |

|                                     | 0                                                                                                                                                                        | Interrupt ser | vicing enabled | d      |                         |                             |                         |                                 |  |  |  |

|                                     | 1                                                                                                                                                                        | Interrupt ser | vicing disable | d      |                         |                             |                         |                                 |  |  |  |

#### Figure 20-10. Format of Interrupt Mask Flag Registers (MK0L, MK0H, MK1L, MK1H) (78K0/KE2)

Note Products whose flash memory is at least 48 KB only.

Caution Be sure to set bits 1 to 7 of MK1H to 1 for the products whose flash memory is less than 32 KB. Be sure to set bits 4 to 7 of MK1H to 1 for the products whose flash memory is at least 48 KB.

| STOP Mode Setting  |                         | g When STOP Instruction Is                                                                                                            | s Executed While CPU Is Operat                                    | ing on Main System Clock                                           |  |  |  |  |  |  |  |

|--------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------|--|--|--|--|--|--|--|

| Item               |                         | When CPU Is Operating on<br>Internal High-Speed<br>Oscillation Clock (fRH)                                                            | When CPU Is Operating on<br>X1 Clock (fx)                         | When CPU Is Operating on<br>External Main System Clock<br>(fexclk) |  |  |  |  |  |  |  |

| System clock       |                         | Clock supply to the CPU is stop                                                                                                       | Clock supply to the CPU is stopped                                |                                                                    |  |  |  |  |  |  |  |

| Main system o      | lock free               | Stopped                                                                                                                               | Stopped                                                           |                                                                    |  |  |  |  |  |  |  |

|                    | fx                      |                                                                                                                                       |                                                                   |                                                                    |  |  |  |  |  |  |  |

|                    | <b>f</b> exclk          | Input invalid                                                                                                                         | Input invalid                                                     |                                                                    |  |  |  |  |  |  |  |

| Subsystem clo      | ock fxt                 | Status before STOP mode was                                                                                                           | set is retained                                                   |                                                                    |  |  |  |  |  |  |  |

|                    | fexclk                  | s Operates or stops by external c                                                                                                     | lock input                                                        |                                                                    |  |  |  |  |  |  |  |

| fRL                |                         | Status before STOP mode was                                                                                                           | set is retained                                                   |                                                                    |  |  |  |  |  |  |  |

| CPU                |                         | Operation stopped                                                                                                                     |                                                                   |                                                                    |  |  |  |  |  |  |  |

| Flash memory       |                         |                                                                                                                                       |                                                                   |                                                                    |  |  |  |  |  |  |  |

| RAM                |                         | Status before STOP mode was                                                                                                           | set is retained                                                   |                                                                    |  |  |  |  |  |  |  |

| Port (latch)       |                         |                                                                                                                                       |                                                                   |                                                                    |  |  |  |  |  |  |  |

| 16-bit timer/event | 00 <sup>Note</sup>      | Operation stopped                                                                                                                     |                                                                   |                                                                    |  |  |  |  |  |  |  |

| counter            | 01 <sup>Note</sup>      | 1                                                                                                                                     |                                                                   |                                                                    |  |  |  |  |  |  |  |

| 8-bit timer/event  | 50 <sup>Note</sup>      | <sup>1</sup> Operable only when TI50 is sel                                                                                           | ected as the count clock                                          |                                                                    |  |  |  |  |  |  |  |

| counter            | 51 <sup>Note</sup>      | <sup>1</sup> Operable only when TI51 is sel                                                                                           | Operable only when TI51 is selected as the count clock            |                                                                    |  |  |  |  |  |  |  |

| 8-bit timer        | H0                      | Operable only when TM50 outp<br>50 operation                                                                                          | ut is selected as the count clock                                 | during 8-bit timer/event counter                                   |  |  |  |  |  |  |  |

|                    | H1                      | Operable only when $f_{RL}$ , $f_{RL}/2^7$ , $f_{RL}/2^9$ is selected as the count clock                                              |                                                                   |                                                                    |  |  |  |  |  |  |  |

| Watch timer        |                         | Operable only when subsystem clock is selected as the count clock                                                                     |                                                                   |                                                                    |  |  |  |  |  |  |  |

| Watchdog timer     |                         | Operable. Clock supply to watchdog timer stops when "internal low-speed oscillator can be stopped by software" is set by option byte. |                                                                   |                                                                    |  |  |  |  |  |  |  |

| Clock output       |                         | Operable only when subsystem                                                                                                          | Operable only when subsystem clock is selected as the count clock |                                                                    |  |  |  |  |  |  |  |

| Buzzer output      |                         | Operation stopped                                                                                                                     |                                                                   |                                                                    |  |  |  |  |  |  |  |

| A/D converter      |                         |                                                                                                                                       |                                                                   |                                                                    |  |  |  |  |  |  |  |

| Serial interface   | UART0                   | Operable only when TM50 outp                                                                                                          | ut is selected as the serial clock                                | during 8-bit timer/event counter                                   |  |  |  |  |  |  |  |

|                    | UART6                   | 50 operation                                                                                                                          |                                                                   |                                                                    |  |  |  |  |  |  |  |

|                    | CSI10 <sup>Note 1</sup> | Operable only when external cl                                                                                                        | ock is selected as the serial clock                               | κ                                                                  |  |  |  |  |  |  |  |

|                    | CSI11 <sup>Note 1</sup> |                                                                                                                                       |                                                                   |                                                                    |  |  |  |  |  |  |  |

|                    | CSIA0 <sup>Note 1</sup> | Operation stopped                                                                                                                     |                                                                   |                                                                    |  |  |  |  |  |  |  |

|                    | IIC0 <sup>Note 1</sup>  | Operable only when the externa                                                                                                        | al clock from EXSCL0/P62 pin is                                   | selected as the serial clockNote 2                                 |  |  |  |  |  |  |  |

| Multiplier/divider |                         | Operation stopped                                                                                                                     |                                                                   |                                                                    |  |  |  |  |  |  |  |

| Power-on-clear fu  | nction                  | Operable                                                                                                                              |                                                                   |                                                                    |  |  |  |  |  |  |  |

| Low-voltage detec  | tion function           |                                                                                                                                       |                                                                   |                                                                    |  |  |  |  |  |  |  |

| External interrupt |                         |                                                                                                                                       |                                                                   |                                                                    |  |  |  |  |  |  |  |

| Table 22-3. | Operating | Statuses | in | STOP I | Mode |

|-------------|-----------|----------|----|--------|------|

|-------------|-----------|----------|----|--------|------|

**Notes 1.** Do not start operation of these functions on the external clock input from peripheral hardware pins in the stop mode.

2. The operation of 78K0/KB2 products is stopped (The external clock from the EXSCL0/P62 pin cannot be selected, because the EXSCL0/P62 pin is not mounted.).

| Remarks 1. | fвн:     | Internal high-speed oscillation clock, | fx:  | X1 clock                             |

|------------|----------|----------------------------------------|------|--------------------------------------|

|            | fexclk:  | External main system clock,            | fx⊤: | XT1 clock                            |

|            | fexclks: | External subsystem clock,              | frl: | Internal low-speed oscillation clock |

2. The functions mounted depend on the product. See 1.7 Block Diagram and 1.8 Outline of Functions.

#### 27.9 Processing Time for Each Command When PG-FP4 or PG-FP5 Is Used (Reference)

The following table shows the processing time for each command (reference) when the PG-FP4 or PG-FP5 is used as a dedicated flash memory programmer.

#### Table 27-12. Processing Time for Each Command When PG-FP4 or PG-FP5 Is Used (Reference) (1/2)

| Command of<br>PG-FP4 | Port: CSI-Internal-OSC<br>(Internal high-speed oscillation | Port: UART-Ext-FP4CK (External main system clock (fexclk)),<br>Speed: 115,200 bps |                   |  |  |

|----------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------|--|--|

|                      | clock (fвн)),<br>Speed: 2.5 MHz                            | Frequency: 2.0 MHz                                                                | Frequency: 20 MHz |  |  |

| Signature            | 0.5 s (TYP.)                                               | 0.5 s (TYP.)                                                                      | 0.5 s (TYP.)      |  |  |

| Blankcheck           | 0.5 s (TYP.)                                               | 0.5 s (TYP.)                                                                      | 0.5 s (TYP.)      |  |  |

| Erase                | 0.5 s (TYP.)                                               | 0.5 s (TYP.)                                                                      | 0.5 s (TYP.)      |  |  |

| Program              | 2.5 s (TYP.)                                               | 5 s (TYP.)                                                                        | 5 s (TYP.)        |  |  |

| Verify               | 1.5 s (TYP.)                                               | 4 s (TYP.)                                                                        | 3.5 s (TYP.)      |  |  |

| E.P.V                | 3.5 s (TYP.)                                               | 6 s (TYP.)                                                                        | 6 s (TYP.)        |  |  |

| Checksum             | 0.5 s (TYP.)                                               | 0.5 s (TYP.)                                                                      | 0.5 s (TYP.)      |  |  |

| Security             | 0.5 s (TYP.)                                               | 0.5 s (TYP.)                                                                      | 0.5 s (TYP.)      |  |  |

(1) Products with internal ROMs of the 32 KB

(2) Products with internal ROMs of the 60 KB

| Command of<br>PG-FP4 | Port: CSI-Internal-OSC<br>(Internal high-speed oscillation | Port: UART-Ext-FP4CK (External main system clock (fexclk)),<br>Speed: 115,200 bps |                   |  |  |

|----------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------|--|--|

|                      | clock (fвн)),<br>Speed: 2.5 MHz                            | Frequency: 2.0 MHz                                                                | Frequency: 20 MHz |  |  |

| Signature            | 0.5 s (TYP.)                                               | 0.5 s (TYP.)                                                                      | 0.5 s (TYP.)      |  |  |

| Blankcheck           | 1 s (TYP.)                                                 | 1 s (TYP.)                                                                        | 1 s (TYP.)        |  |  |

| Erase                | 1 s (TYP.)                                                 | 1 s (TYP.)                                                                        | 1 s (TYP.)        |  |  |

| Program              | 5 s (TYP.)                                                 | 9 s (TYP.)                                                                        | 9 s (TYP.)        |  |  |

| Verify               | 2 s (TYP.)                                                 | 6.5 s (TYP.)                                                                      | 6.5 s (TYP.)      |  |  |

| E.P.V                | 6 s (TYP.)                                                 | 10.5 s (TYP.)                                                                     | 10.5 s (TYP.)     |  |  |

| Checksum             | 0.5 s (TYP.)                                               | 1 s (TYP.)                                                                        | 1 s (TYP.)        |  |  |

| Security             | 0.5 s (TYP.)                                               | 0.5 s (TYP.)                                                                      | 0.5 s (TYP.)      |  |  |

## Caution When executing boot swapping, do not use the E.P.V. command with the dedicated flash memory programmer.

## Table 27-16. Interrupt Response Time for Self Programming Library (Expanded-specification Products ( $\mu$ PD78F05xxA and 78F05xxDA)) (1/2)

#### (1) When internal high-speed oscillation clock is used

| Library Name              | Interrupt Response Time (µs (Max.))                                                                                                                                      |                    |                                                             |                                                              |  |  |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------|--------------------------------------------------------------|--|--|

|                           | Normal Model of C Compiler         Si           Entry RAM location         Entry RAM location         En           is outside short         is in short direct         i |                    | Static Model of C Compiler/Assembler                        |                                                              |  |  |

|                           | is outside short                                                                                                                                                         | is in short direct | Entry RAM location<br>is outside short<br>direct addressing | Entry RAM location<br>is in short direct<br>addressing range |  |  |

|                           | range                                                                                                                                                                    |                    | range                                                       |                                                              |  |  |

| Block blank check library | 1100.9                                                                                                                                                                   | 431.9              | 1095.3                                                      | 426.3                                                        |  |  |

| Block erase library       | 1452.9                                                                                                                                                                   | 783.9              | 1447.3                                                      | 778.3                                                        |  |  |

| Word write library        | 1247.2                                                                                                                                                                   | 579.2              | 1239.2                                                      | 571.2                                                        |  |  |

| Block verify library      | 1125.9                                                                                                                                                                   | 455.9              | 1120.3                                                      | 450.3                                                        |  |  |

| Set information library   | 906.9                                                                                                                                                                    | 312.0              | 905.8                                                       | 311.0                                                        |  |  |

| EEPROM write library      | 1215.2                                                                                                                                                                   | 547.2              | 1213.9                                                      | 545.9                                                        |  |  |

**Remarks 1.** The above interrupt response times are those during stabilized operation of the internal high-speed oscillator (RSTS = 1).

2. RSTS: Bit 7 of the internal oscillation mode register (RCM)

#### (2) When high-speed system clock is used (normal model of C compiler)

| Library Name                         |                                                                                                                                                                                                                                                                                                   | Interrupt Response Time (µs (Max.)) |                                        |                                          |  |  |  |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------|------------------------------------------|--|--|--|

|                                      | RSTOP = 0, RSTS = 1         Entry RAM location         is outside short         direct addressing         range         179/fcpu + 567                                                                                                                                                            |                                     | RSTOP = 1                              |                                          |  |  |  |

|                                      | is outside short                                                                                                                                                                                                                                                                                  | is in short direct                  | Entry RAM location<br>is outside short | Entry RAM location<br>is in short direct |  |  |  |

|                                      | 5                                                                                                                                                                                                                                                                                                 | addressing range                    | direct addressing<br>range             | addressing range                         |  |  |  |

| Block blank check library            | 179/fcpu + 567                                                                                                                                                                                                                                                                                    | 179/fcpu + 246                      | 179/fcpu + 1708                        | 179/fсри + 569                           |  |  |  |

| Block erase library                  | 179/fcpu + 780                                                                                                                                                                                                                                                                                    | 179/fcpu + 459                      | 179/fcpu + 1921                        | 179/fcpu + 782                           |  |  |  |

| Word write library                   | 333/fcpu + 763                                                                                                                                                                                                                                                                                    | 333/fcpu + 443                      | 333/fcpu + 1871                        | 333/fcpu + 767                           |  |  |  |

| Block verify library                 | 179/fcpu + 580                                                                                                                                                                                                                                                                                    | 179/fcpu + 259                      | 179/fcpu + 1721                        | 179/fcpu + 582                           |  |  |  |

| Set information library              | 80/fcpu + 456                                                                                                                                                                                                                                                                                     | 80/fcpu + 200                       | 80/fcpu + 1598                         | 80/fcpu + 459                            |  |  |  |

| EEPROM write library <sup>Note</sup> | 29/fcpu + 767                                                                                                                                                                                                                                                                                     | 29/fcpu + 447                       | 29/fcpu + 767                          | 29/fcpu + 447                            |  |  |  |

|                                      | direct addressing<br>range         addressing range           179/fcpu + 567         179/fcpu + 246           179/fcpu + 780         179/fcpu + 459           333/fcpu + 763         333/fcpu + 443           179/fcpu + 580         179/fcpu + 259           80/fcpu + 456         80/fcpu + 200 | 333/fcpu + 1838                     | 333/fcpu + 700                         |                                          |  |  |  |

**Note** The longer value of the EEPROM write library interrupt response time becomes the Max. value, depending on the value of fcPu.

#### Remarks 1. fcpu: CPU operation clock frequency

- 2. RSTOP: Bit 0 of the internal oscillation mode register (RCM)

- 3. RSTS: Bit 7 of the internal oscillation mode register (RCM)

Caution The pins mounted depend on the product. Refer to Caution at the beginning of this chapter.

#### **Flash Memory Programming Characteristics**

$(T_{A} = -40 \text{ to } +125^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{DD} = \text{EV}_{DD} \le 5.5 \text{ V}, \text{AV}_{REF} \le \text{V}_{DD}, \text{V}_{SS} = \text{EV}_{SS} = \text{AV}_{SS} = 0 \text{ V})$

#### Basic characteristics

| Parar                                  | neter      | Symbol |                                                                 | (                                                                  | Conditions                                                                                                                                                                                        |                        | MIN.  | TYP. | MAX. | Unit  |

|----------------------------------------|------------|--------|-----------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------|------|------|-------|

| VDD supply current                     |            | Idd    | fxp = 10 MHz (TYP.), 20 MHz (MAX.)                              |                                                                    |                                                                                                                                                                                                   |                        | 4.5   | 16.0 | mA   |       |

| Erase time                             | All block  | Teraca |                                                                 |                                                                    |                                                                                                                                                                                                   |                        |       | 20   | 200  | ms    |

| Notes 1, 2                             | Block unit | Terasa |                                                                 |                                                                    |                                                                                                                                                                                                   |                        |       | 20   | 200  | ms    |

| Write time<br>units) <sup>Note 1</sup> | (in 8-bit  | Twrwa  |                                                                 |                                                                    |                                                                                                                                                                                                   |                        |       | 10   | 100  | μS    |

| Number of rewrites<br>per chip         |            | Cerwr  | 1 erase +<br>1 write<br>after<br>erase =<br>1 rewrite<br>Note 3 | Expanded-<br>specification<br>Products<br>(µPD78F05xxA<br>(A2))    | <ul> <li>When a flash memory<br/>programmer is used,<br/>and the libraries<sup>Note 4</sup><br/>provided by Renesas<br/>Electronics are used</li> <li>For program update</li> </ul>               | Retention:<br>15 years | 1000  |      |      | Times |

|                                        |            |        |                                                                 |                                                                    | <ul> <li>When the EEPROM<br/>emulation libraries<sup>Note 5</sup><br/>provided by Renesas<br/>Electronics are used</li> <li>The rewritable ROM<br/>size: 4 KB</li> <li>For data update</li> </ul> | Retention:<br>5 years  | 10000 |      |      | Times |

|                                        |            |        |                                                                 | Expanded-<br>specification<br>Products<br>(µPD78F05xxA<br>(A2))    | Conditions other than<br>the above <sup>Note 6</sup>                                                                                                                                              | Retention:<br>10 years | 100   |      |      | Times |

|                                        |            |        |                                                                 | Conventional-<br>specification<br>Products<br>(µPD78F05xx<br>(A2)) |                                                                                                                                                                                                   |                        |       |      |      |       |

**Notes 1.** Characteristic of the flash memory. For the characteristic when a dedicated flash programmer, PG-FP4 or PG-FP5, is used and the rewrite time during self programming, see **Tables 27-12** to **27-14**.

- 2. The prewrite time before erasure and the erase verify time (writeback time) are not included.

- **3.** When a product is first written after shipment, "erase  $\rightarrow$  write" and "write only" are both taken as one rewrite.

- The sample library specified by the 78K0/Kx2 Flash Memory Self Programming User's Manual (Document No.: U17516E) is excluded.

- The sample program specified by the 78K0/Kx2 EEPROM Emulation Application Note (Document No.: U17517E) is excluded.

- 6. These include when the sample library specified by the 78K0/Kx2 Flash Memory Self Programming User's Manual (Document No.: U17516E) and the sample program specified by the 78K0/Kx2 EEPROM Emulation Application Note (Document No.: U17517E) are used.

Remarks 1. fxp: Main system clock oscillation frequency

2. For serial write operation characteristics, refer to 78K0/Kx2 Flash Memory Programming (Programmer) Application Note (Document No.: U17739E).

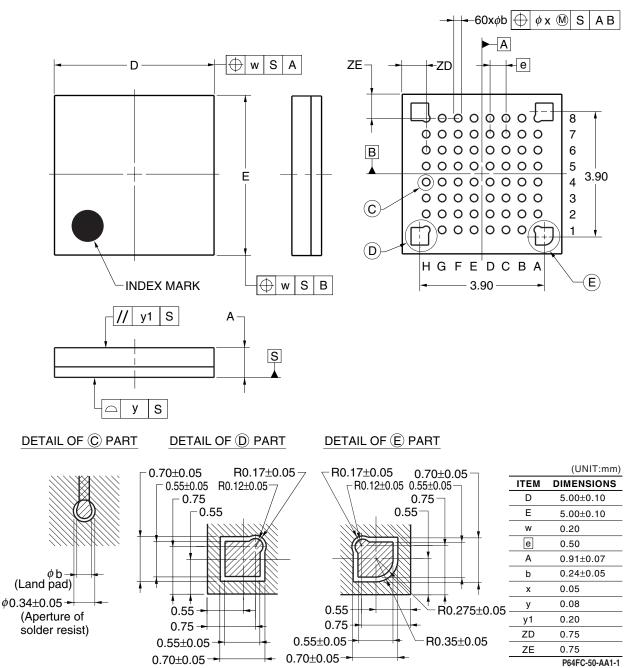

- μPD78F0531FC-AA1-A, 78F0532FC-AA1-A, 78F0533FC-AA1-A, 78F0534FC-AA1-A, 78F0535FC-AA1-A, 78F0536FC-AA1-A, 78F0537DFC-AA1-A

- μPD78F0531AFC-AA1-A, 78F0532AFC-AA1-A, 78F0533AFC-AA1-A, 78F0534AFC-AA1-A, 78F0535AFC-AA1-A, 78F0535AFC-AA1-A, 78F0537DAFC-AA1-A

#### 64-PIN PLASTIC FLGA(5x5)

| Serial trigger register 0 (CSIT0)                 | 519 |

|---------------------------------------------------|-----|

| Slave address register 0 (SVA0)                   | 553 |

| 16-bit timer capture/compare register 000 (CR000) | 273 |

| 16-bit timer capture/compare register 001 (CR001) | 273 |

| 16-bit timer capture/compare register 010 (CR010) | 273 |

| 16-bit timer capture/compare register 011 (CR011) | 273 |

| 16-bit timer counter 00 (TM00)                    | 272 |

| 16-bit timer counter 01 (TM00)                    | 272 |

| 16-bit timer mode control register 00 (TMC00)     | 277 |

| 16-bit timer mode control register 01 (TMC01)     | 277 |

| 16-bit timer output control register 00 (TOC00)   | 282 |

| 16-bit timer output control register 01 (TOC01)   | 282 |

#### [T]

| Timer clock selection register 50 (TCL50)    | . 348 |

|----------------------------------------------|-------|

| Timer clock selection register 51 (TCL51)    | . 348 |

| 10-bit A/D conversion result register (ADCR) | . 416 |

| Transmit buffer register 10 (SOTB10)         | . 492 |

| Transmit buffer register 11 (SOTB11)         | . 492 |

| Transmit buffer register 6 (TXB6)            | . 459 |

| Transmit shift register 0 (TXS0)             | . 435 |

| Transmit shift register 6 (TXS6)             | . 459 |

| [W]                                          |       |

| Watch timer operation mode register (WTM) | 391 |

|-------------------------------------------|-----|

| Watchdog timer enable register (WDTE)     | 398 |

|            |                                  |                                                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     | 6/30)                                                                                                                                 |    |     |  |

|------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------|----|-----|--|

| Chapter    | Classification                   | Function                                                                                                        | Details of<br>Function                                                                                                                                                                                                                                                                                                                                                                                      | Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | Pag | е                                                                                                                                     |    |     |  |

| Chapter 14 | t t Serial<br>interface<br>UART0 | POWER0, TXE0,<br>RXE0: Bits 7, 6,<br>5 of ASIM0                                                                 | Clear POWER0 to 0 after clearing TXE0 and RXE0 to 0 to set the operation stop<br>mode.<br>To start the communication, set POWER0 to 1, and then set TXE0 or RXE0 to 1.                                                                                                                                                                                                                                      | p.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 441 |     |                                                                                                                                       |    |     |  |

| Cha        |                                  | UART mode                                                                                                       | Take relationship with the other party of communication when setting the port mode register and port register.                                                                                                                                                                                                                                                                                              | p.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 442 |     |                                                                                                                                       |    |     |  |

|            |                                  |                                                                                                                 | UART<br>transmission                                                                                                                                                                                                                                                                                                                                                                                        | After transmit data is written to TXS0, do not write the next transmit data before the transmission completion interrupt signal (INTST0) is generated.                                                                                                                                                                                                                                                                                                                                                                                                         | p.  | 445 |                                                                                                                                       |    |     |  |