# E·XF kenesas Electronics America Inc - UPD78F0524AGB-GAG-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | 78K/0                                                                                 |

| Core Size                  | 8-Bit                                                                                 |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                                    |

| Number of I/O              | 45                                                                                    |

| Program Memory Size        | 48KB (48K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 2K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 8x10b                                                                             |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 52-LQFP                                                                               |

| Supplier Device Package    | -                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0524agb-gag-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| CHAPTER 29 INSTRUCTION SET                                                        | 759 |

|-----------------------------------------------------------------------------------|-----|

| 29.1 Conventions Used in Operation List                                           | 759 |

| 29.1.1 Operand identifiers and specification methods                              | 759 |

| 29.1.2 Description of operation column                                            | 760 |

| 29.1.3 Description of flag operation column                                       | 760 |

| 29.2 Operation List                                                               | 761 |

| 29.3 Instructions Listed by Addressing Type                                       | 769 |

| CHAPTER 30 ELECTRICAL SPECIFICATIONS (STANDARD PRODUCTS)                          | 772 |

| CHAPTER 31 ELECTRICAL SPECIFICATIONS ((A) GRADE PRODUCTS)                         | 802 |

| CHAPTER 32 ELECTRICAL SPECIFICATIONS ((A2) GRADE PRODUCTS: $T_A = -40$ to +110°C) | 830 |

| CHAPTER 33 ELECTRICAL SPECIFICATIONS ((A2) GRADE PRODUCTS: $T_A = -40$ to +125°C) | 859 |

| CHAPTER 34 PACKAGE DRAWINGS                                                       | 888 |

| 34.1 78K0/KB2                                                                     | 888 |

| 34.2 78K0/KC2                                                                     |     |

| 34.3 78K0/KD2                                                                     |     |

| 34.4 78K0/KE2                                                                     | 898 |

| 34.5 78K0/KF2                                                                     | 908 |

| CHAPTER 35 RECOMMENDED SOLDERING CONDITIONS                                       | 912 |

| CHAPTER 36 CAUTIONS FOR WAIT                                                      | 917 |

| 36.1 Cautions for Wait                                                            | 917 |

| 36.2 Peripheral Hardware That Generates Wait                                      | 918 |

| APPENDIX A DEVELOPMENT TOOLS                                                      | 920 |

| A.1 Software Package                                                              | 923 |

| A.2 Language Processing Software                                                  | 923 |

| A.3 Flash Memory Programming Tools                                                |     |

| A.3.1 When using flash memory programmer FG-FP5, FL-PR5, FG-FP4, and FL-PR4       | 924 |

| A.3.2 When using on-chip debug emulator with programming function QB-MINI2        |     |

| A.4 Debugging Tools (Hardware)                                                    |     |

| A.4.1 When using in-circuit emulator QB-78K0KX2                                   |     |

| A.4.2 When using on-chip debug emulator with programming function QB-MINI2        |     |

| A.5 Debugging Tools (Software)                                                    | 928 |

#### 1.1.6 Interrupt response time for self programming library

#### (1) Conventional-specification products (µPD78F05xx and 78F05xxD) (1/2)

#### <1> When internal high-speed oscillation clock is used

| Library Name              | Interrupt Response Time ( $\mu$ s (Max.))                              |                  |                                        |                                          |  |

|---------------------------|------------------------------------------------------------------------|------------------|----------------------------------------|------------------------------------------|--|

|                           | Normal Model                                                           | of C Compiler    | Static Model of C Cor                  | mpiler/Assembler                         |  |

|                           | Entry RAM locationEntry RAM locationis outside shortis in short direct |                  | Entry RAM location<br>is outside short | Entry RAM location<br>is in short direct |  |

|                           | direct addressing                                                      | addressing range | direct addressing                      | addressing range                         |  |

|                           | range                                                                  |                  | range                                  |                                          |  |

| Block blank check library | 933.6                                                                  | 668.6            | 927.9                                  | 662.9                                    |  |

| Block erase library       | 1026.6                                                                 | 763.6            | 1020.9                                 | 757.9                                    |  |

| Word write library        | 2505.8                                                                 | 1942.8           | 2497.8                                 | 1934.8                                   |  |

| Block verify library      | 958.6                                                                  | 693.6            | 952.9                                  | 687.9                                    |  |

| Set information library   | 476.5                                                                  | 211.5            | 475.5                                  | 210.5                                    |  |

| EEPROM write library      | 2760.8                                                                 | 2168.8           | 2759.5                                 | 2167.5                                   |  |

- **Remarks 1.** The above interrupt response times are those during stabilized operation of the internal high-speed oscillator (RSTS = 1).

- 2. RSTS: Bit 7 of the internal oscillation mode register (RCM)

| <2> When high-speed system clock is used | (normal model of C compiler) |

|------------------------------------------|------------------------------|

|------------------------------------------|------------------------------|

| Library Name                         | Interrupt Response Time ( $\mu$ s (Max.)) |                                          |                                        |                                          |

|--------------------------------------|-------------------------------------------|------------------------------------------|----------------------------------------|------------------------------------------|

|                                      | RSTOP = 0                                 | ), RSTS = 1                              | RSTOP = 1                              |                                          |

|                                      | Entry RAM location<br>is outside short    | Entry RAM location<br>is in short direct | Entry RAM location<br>is outside short | Entry RAM location<br>is in short direct |

|                                      | direct addressing                         | addressing range                         | direct addressing                      | addressing range                         |

|                                      | range                                     |                                          | range                                  |                                          |

| Block blank check library            | 179/fcpu + 507                            | 179/fcpu + 407                           | 179/fcpu + 1650                        | 179/fcpu + 714                           |

| Block erase library                  | 179/fcpu + 559                            | 179/fcpu + 460                           | 179/fcpu + 1702                        | 179/fcpu + 767                           |

| Word write library                   | 333/fcpu + 1589                           | 333/fcpu + 1298                          | 333/fcpu + 2732                        | 333/fcpu + 1605                          |

| Block verify library                 | 179/fcpu + 518                            | 179/fcpu + 418                           | 179/fcpu + 1661                        | 179/fcpu + 725                           |

| Set information library              | 80/fcpu + 370                             | 80/fcpu + 165                            | 80/fcpu + 1513                         | 80/fcpu + 472                            |

| EEPROM write library <sup>Note</sup> | 29/fcpu + 1759                            | 29/fcpu + 1468                           | 29/fcpu + 1759                         | 29/fcpu + 1468                           |

|                                      | 333/fcpu + 834                            | 333/fcpu + 512                           | 333/fcpu + 2061                        | 333/fcpu + 873                           |

- **Note** The longer value of the EEPROM write library interrupt response time becomes the Max. value, depending on the value of fcPu.

- Remarks 1. fCPU: CPU operation clock frequency

- 2. RSTOP: Bit 0 of the internal oscillation mode register (RCM)

- 3. RSTS: Bit 7 of the internal oscillation mode register (RCM)

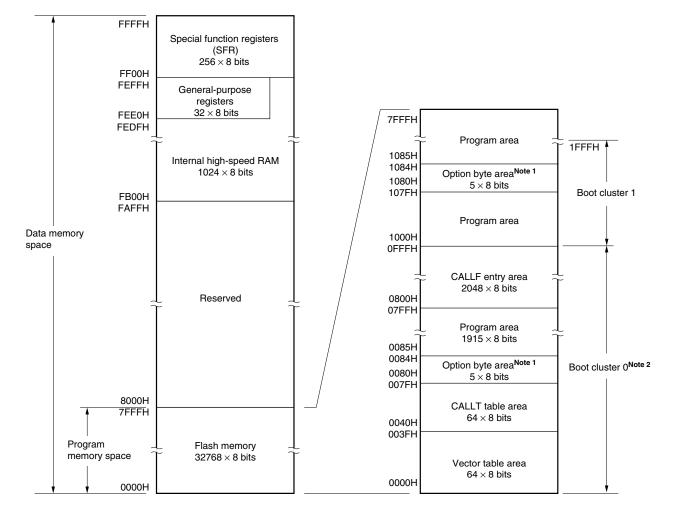

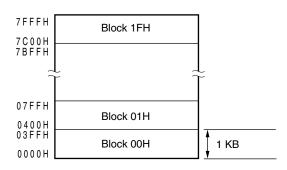

#### Figure 3-4. Memory Map (µPD78F0503, 78F0503A, 78F0513, 78F0513A, 78F0523, 78F0523A, 78F0533 and 78F0533A)

Notes 1. When boot swap is not used: Set the option bytes to 0080H to 0084H.

When boot swap is used: Set the option bytes to 0080H to 0084H and 1080H to 1084H.

- 2. Writing boot cluster 0 can be prohibited depending on the setting of security (see 27.8 Security Settings).

- RemarkThe flash memory is divided into blocks (one block = 1 KB). For the address values and block numbers, seeTable 3-3Correspondence Between Address Values and Block Numbers in Flash Memory.

#### 5.2.4 Port 3

|                                     | 78K0/KB2     | 78K0/KC2 | 78K0/KD2 | 78K0                                                       | /KE2                                                      | 78K0/KF2 |  |

|-------------------------------------|--------------|----------|----------|------------------------------------------------------------|-----------------------------------------------------------|----------|--|

|                                     |              |          |          | Products<br>whose flash<br>memory is<br>less than<br>32 KB | Products<br>whose flash<br>memory is at<br>least<br>48 KB |          |  |

| P30/INTP1                           |              | $\sim$   |          |                                                            |                                                           |          |  |

| P31/INTP2/<br>OCD1A <sup>Note</sup> | $\checkmark$ |          |          |                                                            |                                                           |          |  |

| P32/INTP3/<br>OCD1B <sup>Note</sup> | $\checkmark$ |          |          |                                                            |                                                           |          |  |

| P33/INTP4/TI51/<br>TO51             |              |          |          | V                                                          |                                                           |          |  |

**Note** OCD1A and OCD1B are provided to the products with an on-chip debug function (µPD78F05xxD and 78F05xxDA) only.

#### **Remark** √: Mounted

Port 3 is an I/O port with an output latch. Port 3 can be set to the input mode or output mode in 1-bit units using port mode register 3 (PM3). When the P30 to P33 pins are used as an input port, use of an on-chip pull-up resistor can be specified in 1-bit units by pull-up resistor option register 3 (PU3).

This port can also be used for external interrupt request input and timer I/O.

Reset signal generation sets port 3 to input mode.

Figures 5-13 and 5-14 show block diagrams of port 3.

- Cautions 1. In the product with an on-chip debug function ( $\mu$ P78F05xxD and D78F05xxDA), be sure to pull the P31/INTP2/OCD1A pin down before a reset release, to prevent malfunction.

- 2. Process the P31/INTP2/OCD1A pin of the products mounted with the on-chip debug function ( $\mu$ PD78F05xxD and 78F05xxDA) as follows, when it is not used when it is connected to a flash memory programmer or an on-chip debug emulator.

|                                                                                         |                       | P31/INTP2/OCD1A                                                                                                                  |

|-----------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Flash memory program                                                                    | mer connection        | Connect to EVss <sup>Note</sup> via a resistor.                                                                                  |

| On-chip debug                                                                           | During reset          |                                                                                                                                  |

| emulator connection<br>(when it is not used<br>as an on-chip debug<br>mode setting pin) | During reset released | Input: Connect to EV <sub>DD</sub> <sup>Note</sup> or EV <sub>SS</sub> <sup>Note</sup><br>via a resistor.<br>Output: Leave open. |

Note With products without an EVss pin, connect them to Vss. With products without an EVDD pin, connect them to VDD.

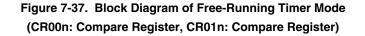

#### 7.4.5 Free-running timer operation

When bits 3 and 2 (TMC0n3 and TMC0n2) of 16-bit timer mode control register 0n (TMC0n) are set to 01 (free-running timer mode), 16-bit timer/event counter 0n continues counting up in synchronization with the count clock. When it has counted up to FFFFH, the overflow flag (OVF0n) is set to 1 at the next clock, and TM0n is cleared (to 0000H) and continues counting. Clear OVF0n to 0 by executing the CLR instruction via software.

The following three types of free-running timer operations are available.

- Both CR00n and CR01n are used as compare registers.

- One of CR00n or CR01n is used as a compare register and the other is used as a capture register.

- Both CR00n and CR01n are used as capture registers.

Remarks 1. For the setting of the I/O pins, see 7.3 (5) Port mode register 0 (PM0).

2. For how to enable the INTTM00n signal interrupt, see CHAPTER 20 INTERRUPT FUNCTIONS.

#### (1) Free-running timer mode operation

(CR00n: compare register, CR01n: compare register)

- **Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

- n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

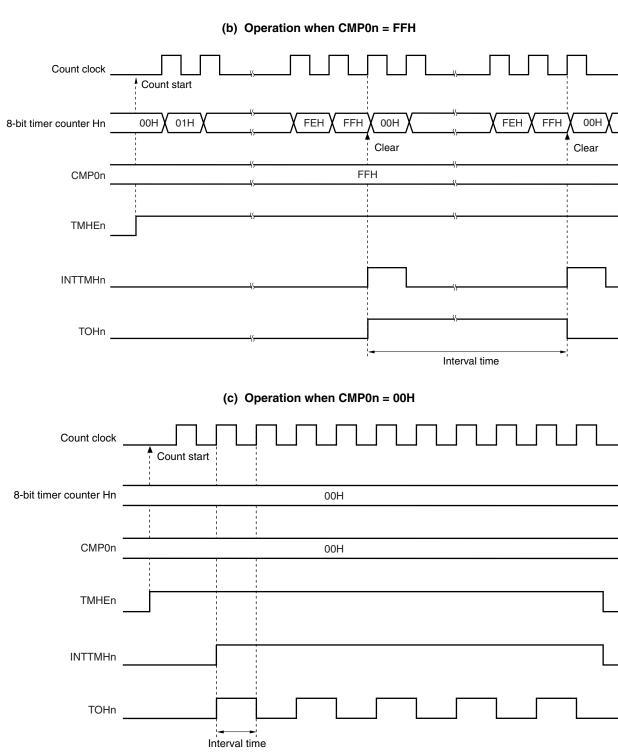

#### Figure 9-10. Timing of Interval Timer/Square-Wave Output Operation (2/2)

#### **11.4 Operation of Watchdog Timer**

#### **11.4.1 Controlling operation of watchdog timer**

- 1. When the watchdog timer is used, its operation is specified by the option byte (0080H).

- Enable counting operation of the watchdog timer by setting bit 4 (WDTON) of the option byte (0080H) to 1 (the counter starts operating after a reset release) (for details, see CHAPTER 26).

| WDTON | Operation Control of Watchdog Timer Counter/Illegal Access Detection                                   |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------|--|--|--|

| 0     | Counter operation disabled (counting stopped after reset), illegal access detection operation disabled |  |  |  |

| 1     | Counter operation enabled (counting started after reset), illegal access detection operation enabled   |  |  |  |

- Set an overflow time by using bits 3 to 1 (WDCS2 to WDCS0) of the option byte (0080H) (for details, see **11.4.2** and **CHAPTER 26**).

- Set a window open period by using bits 6 and 5 (WINDOW1 and WINDOW0) of the option byte (0080H) (for details, see **11.4.3** and **CHAPTER 26**).

- 2. After a reset release, the watchdog timer starts counting.

- 3. By writing "ACH" to WDTE after the watchdog timer starts counting and before the overflow time set by the option byte, the watchdog timer is cleared and starts counting again.

- 4. After that, write WDTE the second time or later after a reset release during the window open period. If WDTE is written during a window close period, an internal reset signal is generated.

- 5. If the overflow time expires without "ACH" written to WDTE, an internal reset signal is generated. A internal reset signal is generated in the following cases.

- If a 1-bit manipulation instruction is executed on the watchdog timer enable register (WDTE)

- If data other than "ACH" is written to WDTE

- If the instruction is fetched from an area not set by the IMS and IXS registers (detection of an invalid check during a CPU program loop)

- If the CPU accesses an area not set by the IMS and IXS registers (excluding FB00H to FFCFH and FFE0H to FFFFH) by executing a read/write instruction (detection of an abnormal access during a CPU program loop)

- Cautions 1. The first writing to WDTE after a reset release clears the watchdog timer, if it is made before the overflow time regardless of the timing of the writing, and the watchdog timer starts counting again.

- 2. If the watchdog timer is cleared by writing "ACH" to WDTE, the actual overflow time may be different from the overflow time set by the option byte by up to 2/f<sub>RL</sub> seconds.

- 3. The watchdog timer can be cleared immediately before the count value overflows (FFFFH).

#### Notes 2. Set the serial clock to satisfy the following conditions.

| Supply Voltage                        | Conventional-specification Products (μPD78F05xx and 78F05xxD) and<br>Expanded-specification Products (μPD78F05xxA and 78F05xxDA) |                              |                             |  |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------|--|

| 11 3                                  | Standard Products                                                                                                                | (A) Grade Products           | (A2) Grade Products         |  |

| $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ | Serial clock $\leq$ 6.25 MHz                                                                                                     | Serial clock $\leq$ 5 MHz    | Serial clock $\leq$ 5 MHz   |  |

| $2.7~V \leq V_{\text{DD}} < 4.0~V$    | Serial clock $\leq$ 4 MHz                                                                                                        | Serial clock $\leq$ 2.5 MHz  | Serial clock $\leq$ 2.5 MHz |  |

| $1.8~V \leq V_{\text{DD}} < 2.7~V$    | Serial clock $\leq$ 2 MHz                                                                                                        | Serial clock $\leq$ 1.66 MHz | -                           |  |

**3.** Do not start communication with the external clock from the SCK11 pin when the internal high-speed oscillation clock and high-speed system clock are stopped while the CPU operates with the subsystem clock, or when in the STOP mode.

#### Cautions 1. Do not write to CSIC11 while CSIE11 = 1 (operation enabled).

- 2. To use P02/SO11 and P04/SCK11 as general-purpose ports, set CSIC11 in the default status (00H).

- 3. The phase type of the data clock is type 1 after reset.

**Remark** fprs: Peripheral hardware clock frequency

#### (3) Port mode registers 0 and 1 (PM0, PM1)

These registers set port 0 and 1 input/output in 1-bit units.

When using P10/SCK10 and P04/SCK11 as the clock output pins of the serial interface, clear PM10 and PM04 to 0, and set the output latches of P10 and P04 to 1.

When using P12/SO10 and P02/SO11 as the data output pins of the serial interface, clear PM12, PM02, and the output latches of P12 and P02 to 0.

When using P10/SCK10 and P04/SCK11 as the clock input pins of the serial interface, P11/SI10/RxD0 and P03/SI11 as the data input pins, and P05/SSI11/TI001 as the chip select input pin, set PM10, PM04, PM11, PM03, and PM05 to 1. At this time, the output latches of P10, P04, P11, P03, and P05 may be 0 or 1.

PM0 and PM1 can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets these registers to FFH.

| Figure 16-7. Format of Port Mode Register 0 (PM0) |

|---------------------------------------------------|

|---------------------------------------------------|

| Address | : FF20 | H Af                           | ter rese                                | t: FFH  | R/W    |      |      |      |

|---------|--------|--------------------------------|-----------------------------------------|---------|--------|------|------|------|

| Symbol  | 7      | 6                              | 5                                       | 4       | 3      | 2    | 1    | 0    |

| PM0     | 1      | PM06                           | PM05                                    | PM04    | PM03   | PM02 | PM01 | PM00 |

|         |        |                                |                                         |         |        |      |      |      |

|         | PM0n   | F                              | P0n pin I/O mode selection (n = 0 to 6) |         |        |      | 6)   |      |

|         | 0      | Output mode (output buffer on) |                                         |         |        |      |      |      |

|         | 1      | Input                          | t mode                                  | (output | buffer | off) |      |      |

Remark The figure shown above presents the format of port mode register 0 of 78K0/KF2 products. For the format of port mode register 0 of other products, see (1) Port mode registers (PMxx) in 5.3 Registers Controlling Port Function.

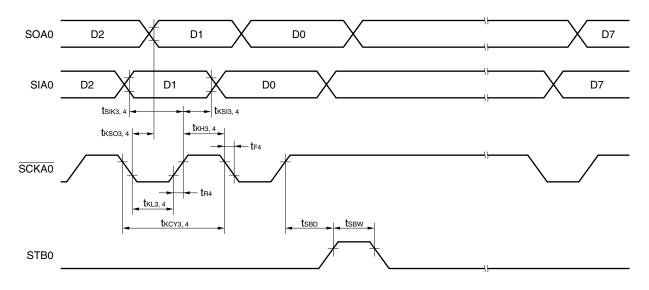

#### 17.4.2 3-wire serial I/O mode

The one-byte data transmission/reception is executed in the mode in which bit 6 (ATE0) of serial operation mode specification register 0 (CSIMA0) is cleared to 0.

The 3-wire serial I/O mode is useful for connecting peripheral ICs and display controllers with a clocked serial interface.

In this mode, communication is executed by using three lines: serial clock (SCKA0), serial output (SOA0), and serial input (SIA0) lines.

#### (1) Registers used

- Serial operation mode specification register 0 (CSIMA0)<sup>Note 1</sup>

- Serial status register 0 (CSIS0)Note 2

- Divisor selection register 0 (BRGCA0)

- Port mode register 14 (PM14)

- Port register 14 (P14)

- Notes 1. Bits 7, 6, and 4 to 1 (CSIAE0, ATE0, MASTER0, TXEA0, RXEA0, and DIR0) are used. Setting of bit 5 (ATM0) is invalid.

- 2. Only bit 0 (TSF0) and bit 6 (CKS00) are used.

The basic procedure of setting an operation in the 3-wire serial I/O mode is as follows.

- <1> Set bit 6 (CKS00) of the CSIS0 register (see Figure 17-3)<sup>Note 1</sup>.

- <2> Set the BRGCA0 register (see Figure 17-5)<sup>Note 1</sup>.

- <3> Set bits 4 to 1 (MASTER0, TXEA0, RXEA0, and DIR0) of the CSIMA0 register (see Figure 17-2).

- <4> Set bit 7 (CSIAE0) of the CSIMA0 register to 1 and clear bit 6 (ATE0) to 0.

- <5> Write data to serial I/O shift register 0 (SIOA0).  $\rightarrow$  Data transmission/reception is started<sup>Note 2</sup>.

- Notes 1. This register does not have to be set when the slave mode is specified (MASTER0 = 0).

- 2. Write dummy data to SIOA0 only for reception.

- Caution Take relationship with the other party of communication when setting the port mode register and port register.

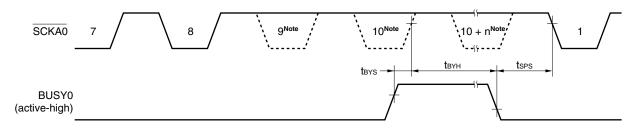

#### 17.4.3 3-wire serial I/O mode with automatic transmit/receive function

Up to 32 bytes of data can be transmitted/received without using software in the mode in which bit 6 (ATE0) of serial operation mode specification register 0 (CSIMA0) is set to 1. After communication is started, only data of the set number of bytes stored in RAM in advance can be transmitted, and only data of the set number of bytes can be received and stored in RAM.

In addition, to transmit/receive data continuously when used as the master, handshake signals (STB0 and BUSY0) generated by hardware are supported. Therefore, connection to peripheral ICs such as OSD (On Screen Display) ICs and LCD controller/drivers can be easily realized.

#### (1) Registers used

- Serial operation mode specification register 0 (CSIMA0)

- Serial status register 0 (CSIS0)

- Serial trigger register 0 (CSIT0)

- Divisor selection register 0 (BRGCA0)

- Automatic data transfer address point specification register 0 (ADTP0)

- Automatic data transfer interval specification register 0 (ADTI0)

- Port mode register 14 (PM14)

- Port register 14 (P14)

The relationship between the register settings and pins is shown below.

## Caution A wait state may be generated when data is written to the buffer RAM. For details, see CHAPTER 36 CAUTIONS FOR WAIT.

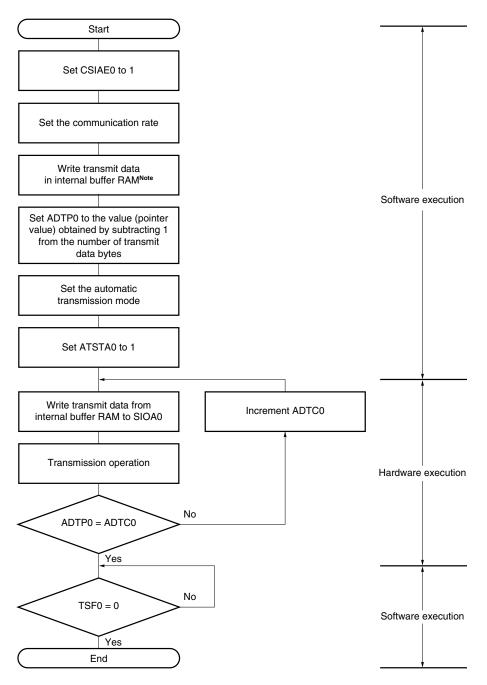

#### Figure 17-18. Automatic Transmission Mode Flowchart

- CSIAE0: Bit 7 of serial operation mode specification register 0 (CSIMA0)

- ADTP0: Automatic data transfer address point specification register 0

- ADTI0: Automatic data transfer interval specification register 0

- ATSTA0: Bit 0 of serial trigger register 0 (CSIT0)

- SIOA0: Serial I/O shift register 0

- ADTCO: Automatic data transfer address count register 0

- TSF0: Bit 0 of serial status register 0 (CSIS0)

- Note A wait state may be generated when data is written to the buffer RAM. For details, see CHAPTER 36 CAUTIONS FOR WAIT.

| CL01 | CL00 | Wait Period |

|------|------|-------------|

| 0    | 0    | 6 clocks    |

| 0    | 1    | 6 clocks    |

| 1    | 0    | 12 clocks   |

| 1    | 1    | 3 clocks    |

Table 18-7. Wait Periods

#### 18.5.15 Cautions

(1) When STCEN (bit 1 of IIC flag register 0 (IICF0)) = 0

Immediately after  $I^2C$  operation is enabled (IICE0 = 1), the bus communication status (IICBSY flag (bit 6 of IICF0) = 1) is recognized regardless of the actual bus status. When changing from a mode in which no stop condition has been detected to a master device communication mode, first generate a stop condition to release the bus, then perform master device communication.

When using multiple masters, it is not possible to perform master device communication when the bus has not been released (when a stop condition has not been detected).

Use the following sequence for generating a stop condition.

- <1> Set IIC clock selection register 0 (IICCL0).

- <2> Set bit 7 (IICE0) of IIC control register 0 (IICC0) to 1.

- <3> Set bit 0 (SPT0) of IICC0 to 1.

- (2) When STCEN = 1

Immediately after  $l^2C$  operation is enabled (IICE0 = 1), the bus released status (IICBSY = 0) is recognized regardless of the actual bus status. To generate the first start condition (STT0 (bit 1 of IIC control register 0 (IICC0)) = 1), it is necessary to confirm that the bus has been released, so as to not disturb other communications.

(3) If other I<sup>2</sup>C communications are already in progress

If  $l^2C$  operation is enabled and the device participates in communication already in progress when the SDA0 pin is low and the SCL0 pin is high, the macro of  $l^2C$  recognizes that the SDA0 pin has gone low (detects a start condition). If the value on the bus at this time can be recognized as an extension code,  $\overline{ACK}$  is returned, but this interferes with other  $l^2C$  communications. To avoid this, start  $l^2C$  in the following sequence.

- <1> Clear bit 4 (SPIE0) of IICC0 register to 0 to disable generation of an interrupt request signal (INTIIC0) when the stop condition is detected.

- <2> Set bit 7 (IICE0) of IICC0 register to 1 to enable the operation of  $l^2C$ .

- <3> Wait for detection of the start condition.

- <4> Set bit 6 (LREL0) of IICC0 register to 1 before ACK is returned (4 to 80 clocks after setting IICE0 bit to 1), to forcibly disable detection.

- (4) Determine the transfer clock frequency by using SMC0, CL01, CL00 bits (bits 3, 1, and 0 of IICL0 register), and CLX0 bit (bit 0 of IICX0 register) before enabling the operation (IICE0 = 1). To change the transfer clock frequency, clear IICE0 bit to 0 once.

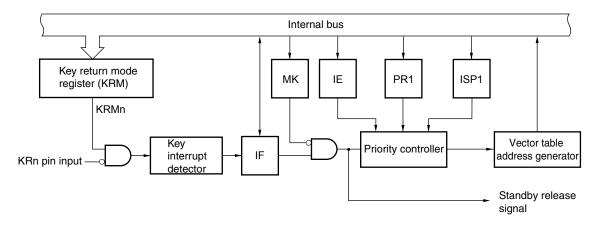

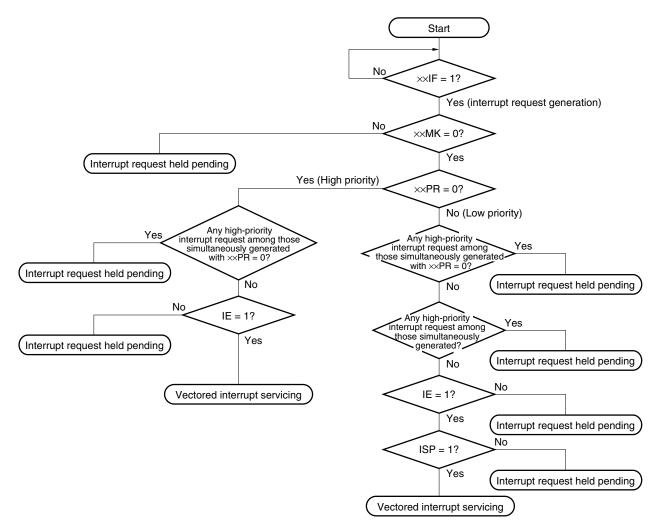

#### Figure 20-1. Basic Configuration of Interrupt Function (2/2)

#### <R> (C) External maskable interrupt (INTKR)

#### (D) Software interrupt

- IF: Interrupt request flag

- IE: Interrupt enable flag

- ISP: In-service priority flag

- MK: Interrupt mask flag

- PR: Priority specification flag

- KRM: Key return mode register

| Address: FF                         | E0H After res                                              | et: 00H R/W            | ,      |        |        |         |       |        |  |

|-------------------------------------|------------------------------------------------------------|------------------------|--------|--------|--------|---------|-------|--------|--|

| Symbol                              | <7>                                                        | <6>                    | <5>    | <4>    | <3>    | <2>     | <1>   | <0>    |  |

| IF0L                                | SREIF6                                                     | PIF5                   | PIF4   | PIF3   | PIF2   | PIF1    | PIF0  | LVIIF  |  |

|                                     |                                                            |                        |        |        |        |         |       |        |  |

| Address: FFE1H After reset: 00H R/W |                                                            |                        |        |        |        |         |       |        |  |

| Symbol                              | <7>                                                        | <6>                    | <5>    | <4>    | <3>    | <2>     | <1>   | <0>    |  |

| IF0H                                | TMIF010                                                    | TMIF000                | TMIF50 | TMIFH0 | TMIFH1 | DUALIF0 | STIF6 | SRIF6  |  |

|                                     |                                                            |                        |        |        |        | CSIIF10 |       |        |  |

|                                     |                                                            |                        |        |        |        | STIF0   |       |        |  |

|                                     |                                                            |                        |        |        |        |         |       |        |  |

| Address: FFE2H After reset: 00H R/W |                                                            |                        |        |        |        |         |       |        |  |

| Symbol                              | 7                                                          | 6                      | 5      | 4      | <3>    | 2       | <1>   | <0>    |  |

| IF1L                                | 0                                                          | 0                      | 0      | 0      | TMIF51 | 0       | SRIF0 | ADIF   |  |

|                                     |                                                            |                        |        |        |        |         |       |        |  |

| Address: FFE3H After reset: 00H R/W |                                                            |                        |        |        |        |         |       |        |  |

| Symbol                              | 7                                                          | 6                      | 5      | 4      | 3      | 2       | 1     | <0>    |  |

| IF1H                                | 0                                                          | 0                      | 0      | 0      | 0      | 0       | 0     | IICIF0 |  |

|                                     |                                                            |                        |        |        |        |         |       |        |  |

|                                     | XXIFX                                                      | Interrupt request flag |        |        |        |         |       |        |  |

|                                     | 0 No interrupt request signal is generated                 |                        |        |        |        |         |       |        |  |

|                                     | 1 Interrupt request is generated, interrupt request status |                        |        |        |        |         |       |        |  |

#### Figure 20-2. Format of Interrupt Request Flag Registers (IF0L, IF0H, IF1L, IF1H) (78K0/KB2)

Caution Be sure to clear bits 2, 4 to 7 of IF1L and bits 1 to 7 of IF1H to 0.

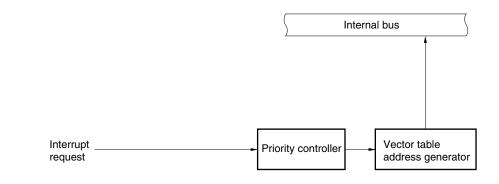

#### Figure 20-19. Interrupt Request Acknowledgment Processing Algorithm

××IF: Interrupt request flag

××MK: Interrupt mask flag

××PR: Priority specification flag

IE: Flag that controls acknowledgment of maskable interrupt request (1 = Enable, 0 = Disable)

ISP: Flag that indicates the priority level of the interrupt currently being serviced (0 = high-priority interrupt servicing, 1 = No interrupt request acknowledged, or low-priority interrupt servicing)

- Cautions 3. When using LVI as an interrupt, if LVION is cleared (0) in a state below the LVI detection voltage, an INTLVI signal is generated and LVIIF becomes 1.

- 4. With the conventional-specification products ( $\mu$ PD78F05xx and 78F05xxD), after an LVI reset has been generated, do not write values to LVIS and LVIM when LVION = 1.

#### (2) Low-voltage detection level selection register (LVIS)

This register selects the low-voltage detection level.

This register can be set by a 1-bit or 8-bit memory manipulation instruction.

The generation of a reset signal other than an LVI reset clears this register to 00H.

#### Figure 25-3. Format of Low-Voltage Detection Level Selection Register (LVIS)

Address: FFBFH After reset: 00HNote 1 R/W Symbol 7 6 5 4 3 2 1 0 0 0 LVIS3 LVIS2 LVIS1 LVIS0 LVIS 0 0

| LVIS3 | LVIS2 | LVIS1 | LVIS0 | Detection level                   |

|-------|-------|-------|-------|-----------------------------------|

| 0     | 0     | 0     | 0     | VLVI0 (4.24 V ±0.1 V)             |

| 0     | 0     | 0     | 1     | V <sub>LVI1</sub> (4.09 V ±0.1 V) |

| 0     | 0     | 1     | 0     | VLVI2 (3.93 V ±0.1 V)             |

| 0     | 0     | 1     | 1     | VLVI3 (3.78 V ±0.1 V)             |

| 0     | 1     | 0     | 0     | VLVI4 (3.62 V ±0.1 V)             |

| 0     | 1     | 0     | 1     | VLVI5 (3.47 V ±0.1 V)             |

| 0     | 1     | 1     | 0     | VLVI6 (3.32 V ±0.1 V)             |

| 0     | 1     | 1     | 1     | VLVI7 (3.16 V ±0.1 V)             |

| 1     | 0     | 0     | 0     | VLVI8 (3.01 V ±0.1 V)             |

| 1     | 0     | 0     | 1     | VLVI9 (2.85 V ±0.1 V)             |

| 1     | 0     | 1     | 0     | VLVI10 (2.70 V ±0.1 V) Note 2     |

| 1     | 0     | 1     | 1     | VLVI11 (2.55 V ±0.1 V) Note 2     |

| 1     | 1     | 0     | 0     | VLVI12 (2.39 V ±0.1 V) Note 2     |

| 1     | 1     | 0     | 1     | VLVI13 (2.24 V ±0.1 V) Note 2     |

| 1     | 1     | 1     | 0     | VLVI14 (2.08 V ±0.1 V) Note 2     |

| 1     | 1     | 1     | 1     | VLVI15 (1.93 V ±0.1 V) Note 2     |

- **Notes 1.** The value of LVIS is not reset but retained as is, upon a reset by LVI. It is cleared to 00H upon other resets.

- 2. Do not set VLVI10 to VLVI15 for (A2) grade products.

Cautions 1. Be sure to clear bits 4 to 7 to "0".

- 2. Do not change the value of LVIS during LVI operation.

- 3. When an input voltage from the external input pin (EXLVI) is detected, the detection voltage (VEXLVI = 1.21 V (TYP.)) is fixed. Therefore, setting of LVIS is not necessary.

- 4. With the conventional-specification products ( $\mu$ PD78F05xx and 78F05xxD), after an LVI reset has been generated, do not write values to LVIS and LVIM when LVION = 1.

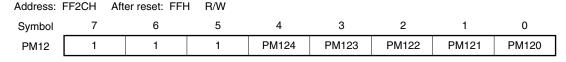

#### (3) Port mode register 12 (PM12)

When using the P120/EXLVI/INTP0 pin for external low-voltage detection potential input, set PM120 to 1. At this time, the output latch of P120 may be 0 or 1.

PM12 can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets PM12 to FFH.

### Figure 25-4. Format of Port Mode Register 12 (PM12)

| PM12n | P12n pin I/O mode selection (n = 0 to 4) |  |

|-------|------------------------------------------|--|

| 0     | Output mode (output buffer on)           |  |

| 1     | Input mode (output buffer off)           |  |

Remark The format of port mode register 12 of 78K0/KB2 products is different from the above format. See 5.3 Registers Controlling Port Function (1) Port mode registers (PMxx).

#### 25.4 Operation of Low-Voltage Detector

The low-voltage detector can be used in the following two modes.

#### (1) Used as reset (LVIMD = 1)

- If LVISEL = 0, compares the supply voltage (V<sub>DD</sub>) and detection voltage (V<sub>LVI</sub>), generates an internal reset signal when V<sub>DD</sub> < V<sub>LVI</sub>, and releases internal reset when V<sub>DD</sub> ≥ V<sub>LVI</sub>.

- If LVISEL = 1, compares the input voltage from external input pin (EXLVI) and detection voltage (VEXLVI = 1.21 V (TYP.)), generates an internal reset signal when EXLVI < VEXLVI, and releases internal reset when EXLVI ≥ VEXLVI.</li>

#### (2) Used as interrupt (LVIMD = 0)

- If LVISEL = 0, compares the supply voltage (V<sub>DD</sub>) and detection voltage (V<sub>LVI</sub>). When V<sub>DD</sub> drops lower than V<sub>LVI</sub> (V<sub>DD</sub> < V<sub>LVI</sub>) or when V<sub>DD</sub> becomes V<sub>LVI</sub> or higher (V<sub>DD</sub> ≥ V<sub>LVI</sub>), generates an interrupt signal (INTLVI).

- If LVISEL = 1, compares the input voltage from external input pin (EXLVI) and detection voltage (V<sub>EXLVI</sub> = 1.21 V (TYP.)). When EXLVI drops lower than V<sub>EXLVI</sub> (EXLVI < V<sub>EXLVI</sub>) or when EXLVI becomes V<sub>EXLVI</sub> or higher (EXLVI ≥ V<sub>EXLVI</sub>), generates an interrupt signal (INTLVI).

While the low-voltage detector is operating, whether the supply voltage or the input voltage from an external input pin is more than or less than the detection level can be checked by reading the low-voltage detection flag (LVIF: bit 0 of LVIM).

Remark LVIMD: Bit 1 of low-voltage detection register (LVIM) LVISEL: Bit 2 of LVIM

#### Caution The pins mounted depend on the product. Refer to Caution 2 at the beginning of this chapter.

#### Serial Transfer Timing (2/2)

#### CSIA0:

#### CSIA0 (busy processing):

**Note** SCKA0 does not become low level here, but the timing is illustrated so that the timing specifications can be shown.

- μPD78F0511GB(A)-GAF-AX, 78F0512GB(A)-GAF-AX, 78F0513GB(A)-GAF-AX

- *µ*PD78F0511GB(A2)-GAF-AX, 78F0512GB(A2)-GAF-AX, 78F0513GB(A2)-GAF-AX

- μPD78F0511AGB-GAF-AX, 78F0512AGB-GAF-AX, 78F0513AGB-GAF-AX, 78F0513DAGB-GAF-AX

- *µ*PD78F0511AGBA-GAF-G, 78F0512AGBA-GAF-G, 78F0513AGBA-GAF-G

- μPD78F0511AGBA2-GAF-G, 78F0512AGBA2-GAF-G, 78F0513AGBA2-GAF-G

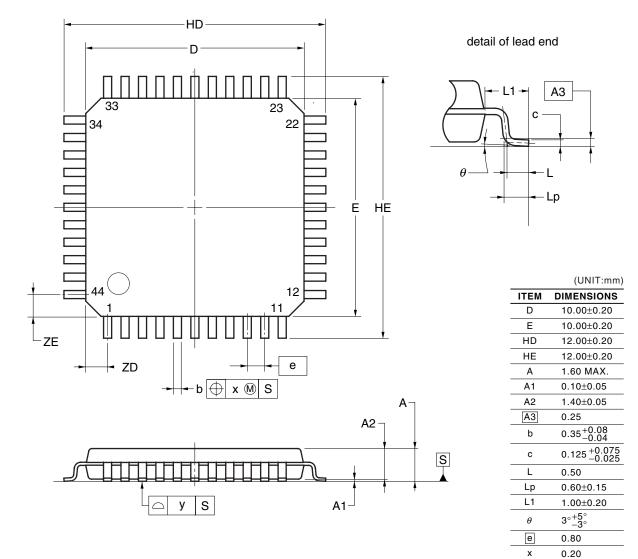

### 44-PIN PLASTIC LQFP (10x10)

#### NOTE

Each lead centerline is located within 0.20 mm of its true position at maximum material condition.

0.10

1.00

1.00 P44GB-80-GAF

у

ZD

ΖE

[MEMO]