# E·XF kenesas Electronics America Inc - UPD78F0525AGB-GAG-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | 78K/0                                                                                 |

| Core Size                  | 8-Bit                                                                                 |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                                    |

| Number of I/O              | 45                                                                                    |

| Program Memory Size        | 60KB (60K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 3K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 8x10b                                                                             |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 52-LQFP                                                                               |

| Supplier Device Package    | -                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0525agb-gag-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- O On-chip 10-bit resolution A/D converter (AV<sub>REF</sub> = 2.3 to 5.5 V)

- O On-chip multiplier/divider (16 bits × 16 bits, 32 bits/16 bits), key interrupt function, clock output/buzzer output controller, I/O ports, timer, and serial interface

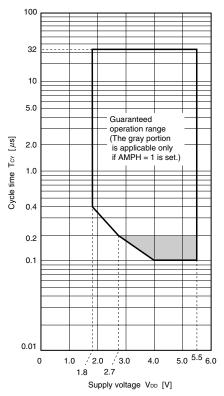

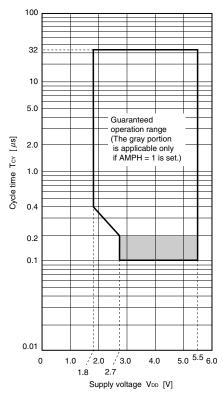

- O Power supply voltage

- Standard products, (A) grade products:  $V_{DD} = 1.8$  to 5.5 V

- (A2) grade products:  $V_{DD} = 2.7 \text{ to } 5.5 \text{ V}$

- O Operating ambient temperature

- Standard products, (A) grade products:  $T_A = -40$  to  $+85^{\circ}C$

- (A2) grade products:  $T_A = -40 \text{ to } +125^{\circ}\text{C}$

Remark The functions mounted depend on the product. See 1.7 Block Diagram and 1.8 Outline of Functions.

#### **1.3 Applications**

- O Automotive equipment (compatible with (A) and (A2) grade products)

- System control for body electricals (power windows, keyless entry reception, etc.)

- Sub-microcontrollers for control

- O Car audio

- O AV equipment, home audio

- O PC peripheral equipment (keyboards, etc.)

- O Household electrical appliances

- Air conditioners

- Microwave ovens, electric rice cookers

- O Industrial equipment

- Pumps

- Vending machines

- FA (Factory Automation)

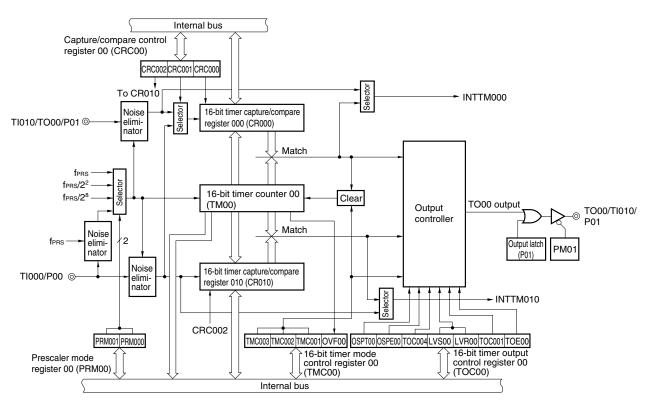

#### 7.2 Configuration of 16-Bit Timer/Event Counters 00 and 01

16-bit timer/event counters 00 and 01 include the following hardware.

#### Table 7-1. Configuration of 16-Bit Timer/Event Counters 00 and 01

| Item              | Configuration                                                                                                                                                                                                                                                                                              |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Time/counter      | 16-bit timer counter 0n (TM0n)                                                                                                                                                                                                                                                                             |  |  |  |

| Register          | 16-bit timer capture/compare registers 00n, 01n (CR00n, CR01n)                                                                                                                                                                                                                                             |  |  |  |

| Timer input       | TI00n, TI01n pins                                                                                                                                                                                                                                                                                          |  |  |  |

| Timer output      | TO0n pin, output controller                                                                                                                                                                                                                                                                                |  |  |  |

| Control registers | <ul> <li>16-bit timer mode control register 0n (TMC0n)</li> <li>16-bit timer capture/compare control register 0n (CRC0n)</li> <li>16-bit timer output control register 0n (TOC0n)</li> <li>Prescaler mode register 0n (PRM0n)</li> <li>Port mode register 0 (PM0)</li> <li>Port register 0 (P0)</li> </ul> |  |  |  |

**Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

Figures 7-1 and 7-2 show the block diagrams.

(Cautions 1 to 3 are listed on the next page.)

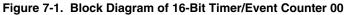

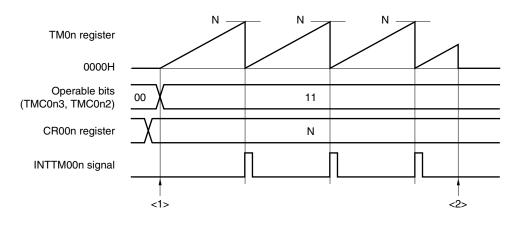

#### Figure 7-19. Example of Software Processing for Interval Timer Function

<1> Count operation start flow

STOP

- **Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

- n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

#### Figure 7-56. Example of Register Settings for Pulse Width Measurement (1/2)

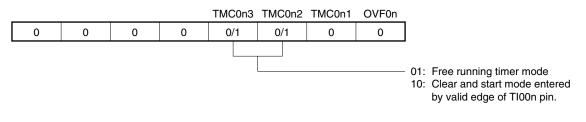

#### (a) 16-bit timer mode control register 0n (TMC0n)

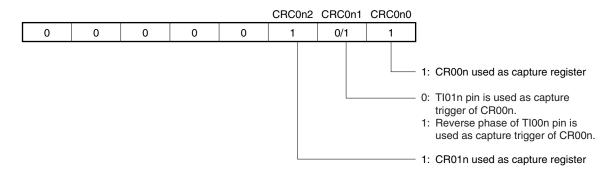

#### (b) Capture/compare control register 0n (CRC0n)

#### (c) 16-bit timer output control register 0n (TOC0n)

| _ |   | OSPT0n | OSPE0n | TOC0n4 | LVS0n | LVR0n | TOC0n1 | TOE0n |

|---|---|--------|--------|--------|-------|-------|--------|-------|

| ſ | 0 | 0      | 0      | 0      | 0     | 0     | 0      | 0     |

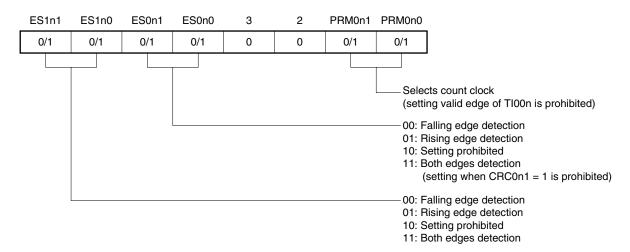

#### (d) Prescaler mode register 0n (PRM0n)

## **Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

| Address: FF8CH After reset: 00H R/W |        |        |        |                        |                           |                 |                      |                          |  |  |  |

|-------------------------------------|--------|--------|--------|------------------------|---------------------------|-----------------|----------------------|--------------------------|--|--|--|

| Symbol                              | 7      | 6      | 5      | 4                      | 3                         | 2               | 1                    | 0                        |  |  |  |

| TCL51                               | 0      | 0      | 0      | 0                      | 0                         | TCL512          | TCL511               | TCL510                   |  |  |  |

|                                     |        |        |        |                        |                           |                 |                      |                          |  |  |  |

|                                     | TCL512 | TCL511 | TCL510 |                        | Coun                      | t clock selecti | ON <sup>Note 1</sup> |                          |  |  |  |

|                                     |        |        |        |                        | fprs =                    | fprs =          | fprs =               | fprs =                   |  |  |  |

|                                     |        |        |        |                        | 2 MHz                     | 5 MHz           | 10 MHz               | 20 MHz                   |  |  |  |

|                                     | 0      | 0      | 0      | TI51 pin falli         | ng edge <sup>Note 2</sup> |                 |                      |                          |  |  |  |

|                                     | 0      | 0      | 1      | TI51 pin risir         | ng edge <sup>Note 2</sup> |                 |                      |                          |  |  |  |

|                                     | 0      | 1      | 0      | fprs <sup>Note 3</sup> | 2 MHz                     | 5 MHz           | 10 MHz               | 20 MHz <sup>Note 4</sup> |  |  |  |

|                                     | 0      | 1      | 1      | fprs/2                 | 1 MHz                     | 2.5 MHz         | 5 MHz                | 10 MHz                   |  |  |  |

|                                     | 1      | 0      | 0      | fprs/2⁴                | 125 kHz                   | 312.5 kHz       | 625 kHz              | 1.25 MHz                 |  |  |  |

|                                     | 1      | 0      | 1      | fprs/26                | 31.25 kHz                 | 78.13 kHz       | 156.25 kHz           | 312.5 kHz                |  |  |  |

|                                     | 1      | 1      | 0      | fprs/2 <sup>8</sup>    | 7.81 kHz                  | 19.53 kHz       | 39.06 kHz            | 78.13 kHz                |  |  |  |

|                                     | 1      | 1      | 1      | fprs/2 <sup>12</sup>   | 0.49 kHz                  | 1.22 kHz        | 2.44 kHz             | 4.88 kHz                 |  |  |  |

#### Figure 8-6. Format of Timer Clock Selection Register 51 (TCL51)

**Notes 1.** The frequency that can be used for the peripheral hardware clock (fPRs) differs depending on the power supply voltage and product specifications.

| Supply Voltage                                                                                                           | Conventional-specification Products (µPD78F05xx and 78F05xxD) | Expanded-specification Products (µPD78F05xxA and 78F05xxDA) |

|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------|

| $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                                                                                    | $f_{\text{PRS}} \leq 20 \text{ MHz}$                          | $f_{PRS} \le 20 \text{ MHz}$                                |

| $2.7~V \leq V_{\text{DD}} < 4.0~V$                                                                                       | $f_{PRS} \leq 10 \text{ MHz}$                                 |                                                             |

| $\begin{array}{l} 1.8 \ V \leq V_{DD} < 2.7 \ V \\ (Standard products and \\ (A) \ grade \ products \ only) \end{array}$ | fprs ≤ 5 MHz                                                  | fprs ≤ 5 MHz                                                |

(The values shown in the table above are those when fPRS = fXH (XSEL = 1).)

- 2. Do not start timer operation with the external clock from the TI51 pin when the internal high-speed oscillation clock and high-speed system clock are stopped while the CPU operates with the subsystem clock, or when in the STOP mode.

- 3. If the peripheral hardware clock (fPRs) operates on the internal high-speed oscillation clock (fRH) (XSEL = 0), when  $1.8 \text{ V} \le \text{V}_{\text{DD}} < 2.7 \text{ V}$ , the setting of TCL512, TCL511, TCL510 = 0, 1, 0 (count clock: fPRs) is prohibited.

- 4. This is settable only if 4.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V.

### Cautions 1. When rewriting TCL51 to other data, stop the timer operation beforehand.

2. Be sure to clear bits 3 to 7 to "0".

Remark fPRs: Peripheral hardware clock frequency

78K0/Kx2

434

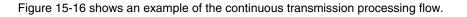

Remark

TXB6:

Transmit buffer register 6

ASIF6:

Asynchronous serial interface transmission status register 6

TXBF6:

Bit 1 of ASIF6 (transmit buffer data flag)

TXSF6:

Bit 0 of ASIF6 (transmit shift register data flag)

#### (4) IIC clock selection register 0 (IICCL0)

This register is used to set the transfer clock for the I<sup>2</sup>C bus.

IICCL0 is set by a 1-bit or 8-bit memory manipulation instruction. However, the CLD0 and DAD0 bits are read-only. The SMC0, CL01, and CL00 bits are set in combination with bit 0 (CLX0) of IIC function expansion register 0 (IICX0) (see **18.3 (6)**  $I^2C$  transfer clock setting method).

Set IICCL0 while bit 7 (IICE0) of IIC control register 0 (IICC0) is 0.

Reset signal generation clears IICCL0 to 00H.

#### Figure 18-8. Format of IIC Clock Selection Register 0 (IICCL0)

| Address: FF | A8H | After reset: 0 | 0H R/W | Note |      |      |      |      |

|-------------|-----|----------------|--------|------|------|------|------|------|

| Symbol      | 7   | 6              | <5>    | <4>  | <3>  | <2>  | 1    | 0    |

| IICCL0      | 0   | 0              | CLD0   | DAD0 | SMC0 | DFC0 | CL01 | CL00 |

| CLD0        | D0 Detection of SCL0 pin level (valid only when IICE0 = 1) |                                    |  |  |  |  |  |

|-------------|------------------------------------------------------------|------------------------------------|--|--|--|--|--|

| 0           | The SCL0 pin was detected at low level.                    |                                    |  |  |  |  |  |

| 1           | The SCL0 pin was detected at high level.                   |                                    |  |  |  |  |  |

| Condition f | or clearing (CLD0 = 0)                                     | Condition for setting (CLD0 = 1)   |  |  |  |  |  |

|             | e SCL0 pin is at low level<br>E0 = 0 (operation stop)      | When the SCL0 pin is at high level |  |  |  |  |  |

| DAD0        | Detection of SDA0 pin level (valid only when IICE0 = 1) |                                    |  |  |  |  |  |

|-------------|---------------------------------------------------------|------------------------------------|--|--|--|--|--|

| 0           | The SDA0 pin was detected at low level.                 |                                    |  |  |  |  |  |

| 1           | The SDA0 pin was detected at high level.                |                                    |  |  |  |  |  |

| Condition f | or clearing (DAD0 = 0)                                  | Condition for setting (DAD0 = 1)   |  |  |  |  |  |

|             | e SDA0 pin is at low level<br>E0 = 0 (operation stop)   | When the SDA0 pin is at high level |  |  |  |  |  |

| SMC0 | Operation mode switching     |

|------|------------------------------|

| 0    | Operates in standard mode.   |

| 1    | Operates in high-speed mode. |

| DFC0           | Digital filter operation control                                                               |  |  |  |  |  |  |

|----------------|------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 0              | Digital filter off.                                                                            |  |  |  |  |  |  |

| 1              | Digital filter on.                                                                             |  |  |  |  |  |  |

| Digital filter | Digital filter can be used only in high-speed mode.                                            |  |  |  |  |  |  |

| In high-spe    | In high-speed mode, the transfer clock does not vary regardless of DFC0 bit set (1)/clear (0). |  |  |  |  |  |  |

The digital filter is used for noise elimination in high-speed mode.

**Note** Bits 4 and 5 are read-only.

Remark IICE0: Bit 7 of IIC control register 0 (IICC0)

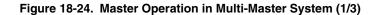

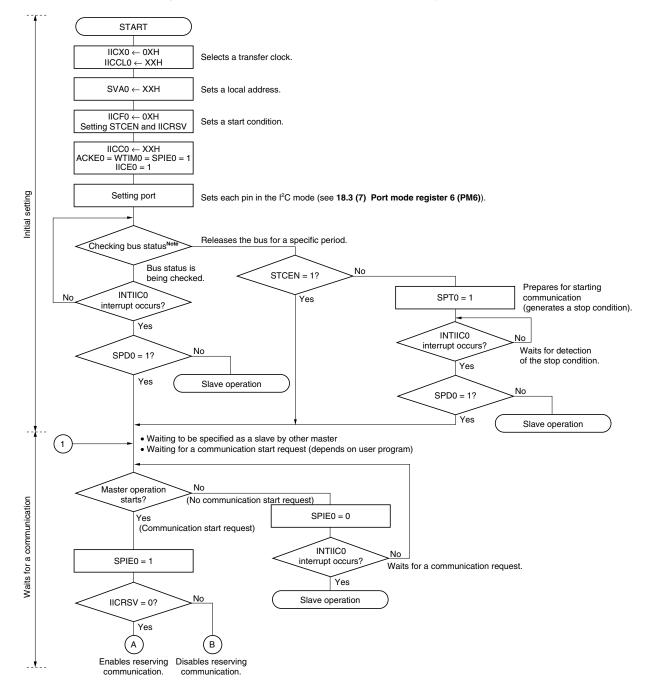

#### (2) Master operation in multi-master system

**Note** Confirm that the bus is released (CLD0 bit = 1, DAD0 bit = 1) for a specific period (for example, for a period of one frame). If the SDA0 pin is constantly at low level, decide whether to release the I<sup>2</sup>C bus (SCL0 and SDA0 pins = high level) in conformance with the specifications of the product that is communicating.

#### 20.3 Registers Controlling Interrupt Functions

The following 6 types of registers are used to control the interrupt functions.

- Interrupt request flag register (IF0L, IF0H, IF1L, IF1H)

- Interrupt mask flag register (MK0L, MK0H, MK1L, MK1H)

- Priority specification flag register (PR0L, PR0H, PR1L, PR1H)

- External interrupt rising edge enable register (EGP)

- External interrupt falling edge enable register (EGN)

- Program status word (PSW)

Table 20-2 shows a list of interrupt request flags, interrupt mask flags, and priority specification flags corresponding to interrupt request sources.

| к            | к            | к            | к            | к            | Interrupt | Interr            | upt Request       | Flag     | Inte              | rrupt Mask F      | lag      | Priority Specification Fla |                   | n Flag   |

|--------------|--------------|--------------|--------------|--------------|-----------|-------------------|-------------------|----------|-------------------|-------------------|----------|----------------------------|-------------------|----------|

| в            | С            | D            | Е            | F            | Source    | Γ                 |                   | Register |                   |                   |          |                            |                   | Register |

| 2            | 2            | 2            | 2            | 2            |           |                   |                   |          |                   |                   | Register |                            |                   | Ů        |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | INTLVI    | LVIIF             |                   | IFOL     | LVIMK             |                   | MKOL     | LVIPR                      |                   | PROL     |

| $\checkmark$ | $\checkmark$ | $\checkmark$ |              | $\checkmark$ | INTP0     | PIF0              |                   |          | PMK0              |                   |          | PPR0                       |                   |          |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | INTP1     | PIF1              |                   |          | PMK1              |                   |          | PPR1                       |                   |          |

| $\checkmark$ | $\checkmark$ | $\checkmark$ |              | $\checkmark$ | INTP2     | PIF2              |                   |          | PMK2              |                   |          | PPR2                       |                   |          |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | INTP3     | PIF3              |                   |          | РМКЗ              |                   |          | PPR3                       |                   |          |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | INTP4     | PIF4              | PIF4              |          | PMK4              |                   |          | PPR4                       |                   |          |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | INTP5     | PIF5              |                   |          | PMK5              |                   |          | PPR5                       |                   |          |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | INTSRE6   | SREIF6            |                   |          | SREMK6            |                   |          | SREPR6                     |                   |          |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | INTSR6    | SRIF6             |                   | IF0H     | SRMK6             |                   | МК0Н     | SRPR6                      |                   | PR0H     |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | INTST6    | STIF6             |                   |          | STMK6             |                   |          | STPR6                      |                   |          |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | INTCSI10  | CSIIF10<br>Note 1 | DUALIF0<br>Note 1 |          | CSIMK10<br>Note 2 | DUALMK0<br>Note 2 |          | CSIPR10<br>Note 3          | DUALPR0<br>Note 3 |          |

| V            | $\checkmark$ | $\checkmark$ | V            | $\checkmark$ | INTST0    | STIF0<br>Note 1   |                   |          | STMK0<br>Note 2   |                   |          | STPR0<br>Note 3            |                   |          |

| $\checkmark$ | $\checkmark$ |              | $\checkmark$ | $\checkmark$ | INTTMH1   | TMIFH1            |                   |          | TMMKH1            |                   |          | TMPRH1                     |                   |          |

| $\checkmark$ | $\checkmark$ | $\checkmark$ |              | $\checkmark$ | INTTMH0   | TMIFHO            |                   |          | ТММКНО            |                   |          | TMPRH0                     |                   |          |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | INTTM50   | TMIF50            |                   |          | TMMK50            |                   |          | TMPR50                     |                   |          |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | INTTM000  | TMIF000           |                   |          | ТММК000           |                   |          | TMPR000                    |                   |          |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | INTTM010  | TMIF010           |                   |          | TMMK010           | 1                 |          | TMPR010                    |                   |          |

#### Table 20-2. Flags Corresponding to Interrupt Request Sources (1/2)

Notes 1. If either interrupt source INTCSI10 or INTST0 is generated, bit 2 of IF0H is set (1).

- 2. Bit 2 of MK0H supports both interrupt sources INTCSI10 and INTST0.

- 3. Bit 2 of PR0H supports both interrupt sources INTCSI10 and INTST0.

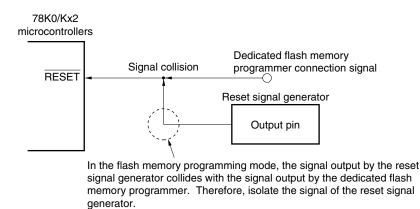

#### 27.6.3 RESET pin

If the reset signal of the dedicated flash memory programmer is connected to the RESET pin that is connected to the reset signal generator on the board, signal collision takes place. To prevent this collision, isolate the connection with the reset signal generator.

If the reset signal is input from the user system while the flash memory programming mode is set, the flash memory will not be correctly programmed. Do not input any signal other than the reset signal of the dedicated flash memory programmer.

Figure 27-9. Signal Collision (RESET Pin)

#### 27.6.4 Port pins

When the flash memory programming mode is set, all the pins not used for flash memory programming enter the same status as that immediately after reset. If external devices connected to the ports do not recognize the port status immediately after reset, the port pin must be connected to EV<sub>DD</sub><sup>Note</sup> or EV<sub>SS</sub><sup>Note</sup> via a resistor.

Note With products without an EVss pin, connect them to Vss. With products without an EVDD pin, connect them to VDD.

#### <R> 27.6.5 REGC pin

Connect the REGC pin to Vss via a capacitor (0.47 to 1  $\mu$ F) in the same manner as during normal operation.

TCY vs. VDD (Main System Clock Operation)

<2> Expanded-specification Products (µPD78F05xxA(A))

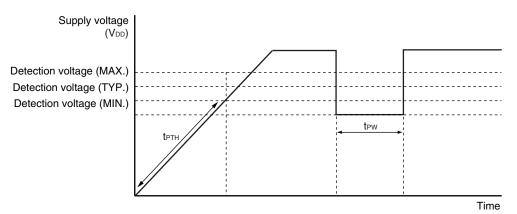

| Parameter                             | Symbol | Conditions                                                                       | MIN. | TYP. | MAX. | Unit |

|---------------------------------------|--------|----------------------------------------------------------------------------------|------|------|------|------|

| Detection voltage                     | VPOC   |                                                                                  | 1.44 | 1.59 | 1.74 | V    |

| Power supply voltage rise inclination | tртн   | $V_{\text{DD}}\text{: }0$ V $\rightarrow$ change inclination of $V_{\text{POC}}$ | 0.5  |      |      | V/ms |

| Minimum pulse width                   | tpw    |                                                                                  | 200  |      |      | μS   |

#### 1.59 V POC Circuit Characteristics (TA = -40 to +85°C, Vss = EVss = 0 V)

#### 1.59 V POC Circuit Timing

| Parameter                     | Symbol | (                           | Conditions                                                                                                               | Ratings     | Unit |

|-------------------------------|--------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------|------|

| Output current, high          | Іон    | Per pin                     | P00 to P06, P10 to P17,<br>P30 to P33, P40 to P47,<br>P50 to P57, P64 to P67,<br>P70 to P77, P120,<br>P130, P140 to P145 | -10         | mA   |

|                               |        | Total of all pins<br>-80 mA | P00 to P04, P40 to P47,<br>P120, P130, P140 to<br>P145                                                                   | -25         | mA   |

|                               |        |                             | P05, P06, P10 to P17,<br>P30 to P33, P50 to P57,<br>P64 to P67, P70 to P77                                               | -55         | mA   |

|                               |        | Per pin                     | P20 to P27                                                                                                               | -0.5        | mA   |

|                               |        | Total of all pins           |                                                                                                                          | -2          | mA   |

|                               |        | Per pin                     | P121 to P124                                                                                                             | –1          | mA   |

|                               |        | Total of all pins           |                                                                                                                          | -4          | mA   |

| Output current, low           | Ιοι    | Per pin                     | P00 to P06, P10 to P17,<br>P30 to P33, P40 to P47,<br>P50 to P57, P60 to P67,<br>P70 to P77, P120, P130,<br>P140 to P145 | 30          | mA   |

|                               |        | Total of all pins<br>200 mA | P00 to P04, P40 to P47,<br>P120, P130, P140 to<br>P145                                                                   | 60          | mA   |

|                               |        |                             | P05, P06, P10 to P17,<br>P30 to P33, P50 to P57,<br>P60 to P67, P70 to P77                                               | 140         | mA   |

|                               |        | Per pin                     | P20 to P27                                                                                                               | 1           | mA   |

|                               |        | Total of all pins           |                                                                                                                          | 5           | mA   |

|                               |        | Per pin                     | P121 to P124                                                                                                             | 4           | mA   |

|                               |        | Total of all pins           |                                                                                                                          | 10          | mA   |

| Operating ambient temperature | TA     |                             |                                                                                                                          | -40 to +110 | °C   |

| Storage temperature           | Tstg   |                             |                                                                                                                          | -65 to +150 | °C   |

#### Absolute Maximum Ratings (T<sub>A</sub> = 25°C) (2/2)

- Cautions 1. Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

- 2. The value of the current that can be run per pin must satisfy the value of the current per pin and the total value of the currents of all pins.

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of port pins.

| Parameter                                                                  | Symbol                                                        |                                                                                                            | Conditions                            | MIN.                 | TYP. | MAX.            | Unit |

|----------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------|------|-----------------|------|

| SCKA0 cycle time                                                           | tксүз                                                         | $\begin{array}{c} 4.0 \ V \leq V_{DD} \leq 5.5 \ V \\ \\ \hline 2.7 \ V \leq V_{DD} < 4.0 \ V \end{array}$ |                                       | 600                  |      |                 | ns   |

|                                                                            |                                                               |                                                                                                            |                                       | 1200                 |      |                 | ns   |

| SCKA0 high-/low-level width                                                | tkh3, $4.0 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5$ tkl3 |                                                                                                            | 5 V                                   | tксүз/2 –<br>50      |      |                 | ns   |

|                                                                            |                                                               | $2.7 \text{ V} \leq \text{V}_{\text{DD}} < 4.$                                                             | 0 V                                   | tксүз/2 –<br>100     |      |                 | ns   |

| SIA0 setup time (to $\overline{\text{SCKA0}}$ )                            | tsik3                                                         |                                                                                                            |                                       | 100                  |      |                 | ns   |

| SIA0 hold time (from $\overline{\text{SCKA0}}\uparrow$ )                   | tหรเง                                                         |                                                                                                            |                                       | 300                  |      |                 | ns   |

| Delay time from $\overline{SCKA0}\downarrow$ to                            | tĸso3                                                         | $C = 100 \text{ pF}^{\text{Note}}$                                                                         | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |                      |      | 200             | ns   |

| SOA0 output                                                                |                                                               |                                                                                                            | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |                      |      | 300             | ns   |

| Time from $\overline{\text{SCKA0}}^{\uparrow}$ to $\text{STB0}^{\uparrow}$ | tsbd                                                          |                                                                                                            |                                       | tксүз/2 –<br>100     |      |                 | ns   |

| Strobe signal high-level width                                             | tsвw                                                          | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                                                                      |                                       | tксүз –<br><b>30</b> |      |                 | ns   |

|                                                                            |                                                               | $2.7 \text{ V} \leq \text{V}_{\text{DD}} < 4.$                                                             | 0 V                                   | tксүз –<br>60        |      |                 | ns   |

| Busy signal setup time (to busy signal detection timing)                   | tвys                                                          |                                                                                                            |                                       |                      |      |                 | ns   |

| Busy signal hold time (from busy signal detection timing)                  | tвүн                                                          |                                                                                                            |                                       | 100                  |      |                 | ns   |

| Time from busy inactive to $\overline{\text{SCKA0}}\downarrow$             | tsps $4.0 \text{ V} \le \text{V}_{\text{DD}} \le 5$           |                                                                                                            | 5 V                                   |                      |      | 2tксүз +<br>100 | ns   |

|                                                                            |                                                               | $2.7 \text{ V} \leq V_{\text{DD}} < 4.$                                                                    | 0 V                                   |                      |      | 2tксүз –<br>150 | ns   |

#### (f) CSIA0 (master mode, SCKA0...internal clock output)

Note C is the load capacitance of the  $\overline{SCKA0}$  and SOA0 output lines.

#### 2.7 V POC Circuit Characteristics (T<sub>A</sub> = -40 to +125°C, Vss = EVss = 0 V)

| Parameter                                  | Symbol | Conditions               | MIN. | TYP. | MAX. | Unit |

|--------------------------------------------|--------|--------------------------|------|------|------|------|

| Detection voltage on application of supply | VDDPOC | POCMODE (option bye) = 1 | 2.50 | 2.70 | 2.90 | V    |

| voltage                                    |        |                          |      |      |      |      |

#### **Remark** The operations of the POC circuit are as described below, depending on the POCMODE (option byte) setting.

| Option Byte Setting | POC Mode                    | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POCMODE = 0         | 1.59 V mode operation       | A reset state is retained until V <sub>POC</sub> = 1.59 V (TYP.) is reached<br>after the power is turned on, and the reset is released when<br>V <sub>POC</sub> is exceeded. After that, POC detection is performed at<br>V <sub>POC</sub> , similarly as when the power was turned on.<br>The power supply voltage must be raised at a time of t <sub>PUP1</sub> or<br>t <sub>PUP2</sub> when POCMODE is 0.                                                                          |

| POCMODE = 1         | 2.7 V/1.59 V mode operation | A reset state is retained until VDDPOC = $2.7 \text{ V}$ (TYP.) is<br>reached after the power is turned on, and the reset is<br>released when VDDPOC is exceeded. After that, POC detection<br>is performed at VPOC = $1.59 \text{ V}$ (TYP.) and not at VDDPOC.<br>The use of the $2.7 \text{ V}/1.59 \text{ V}$ POC mode is recommended<br>when the rise of the voltage, after the power is turned on and<br>until the voltage reaches $1.8 \text{ V}$ , is more relaxed than tPTH. |

- µPD78F0544GK(A)-GAK-AX, 78F0545GK(A)-GAK-AX, 78F0546GK(A)-GAK-AX, 78F0547GK(A)-GAK-AX

- µPD78F0544GK(A2)-GAK-AX, 78F0545GK(A2)-GAK-AX, 78F0546GK(A2)-GAK-AX, 78F0547GK(A2)-GAK-AX

- μPD78F0544AGK-GAK-AX, 78F0545AGK-GAK-AX, 78F0546AGK-GAK-AX, 78F0547AGK-GAK-AX, 78F0547DAGK-GAK-AX

- µPD78F0544AGKA-GAK-G, 78F0545AGKA-GAK-G, 78F0546AGKA-GAK-G, 78F0547AGKA-GAK-G

- µPD78F0544AGKA2-GAK-G, 78F0545AGKA2-GAK-G, 78F0546AGKA2-GAK-G, 78F0547AGKA2-GAK-G

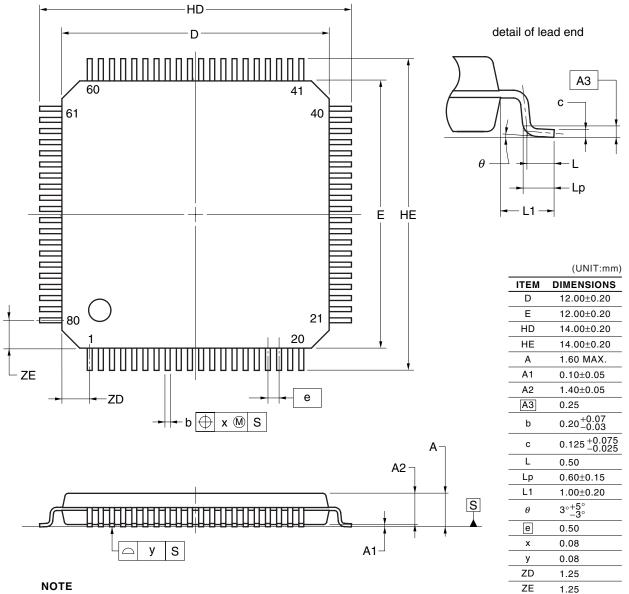

### 80-PIN PLASTIC LQFP(FINE PITCH)(12x12)

Each lead centerline is located within 0.08 mm of its true position at maximum material condition.

P80GK-50-GAK

#### 36.2 Peripheral Hardware That Generates Wait

Table 36-1 lists the registers that issue a wait request when accessed by the CPU, and the number of CPU wait clocks and Table 36-2 lists the RAM accesses that issue a wait request and the number of CPU wait clocks.

| Peripheral<br>Hardware    | Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Access | Number of Wait Clocks                                                                                                                                                       |  |  |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

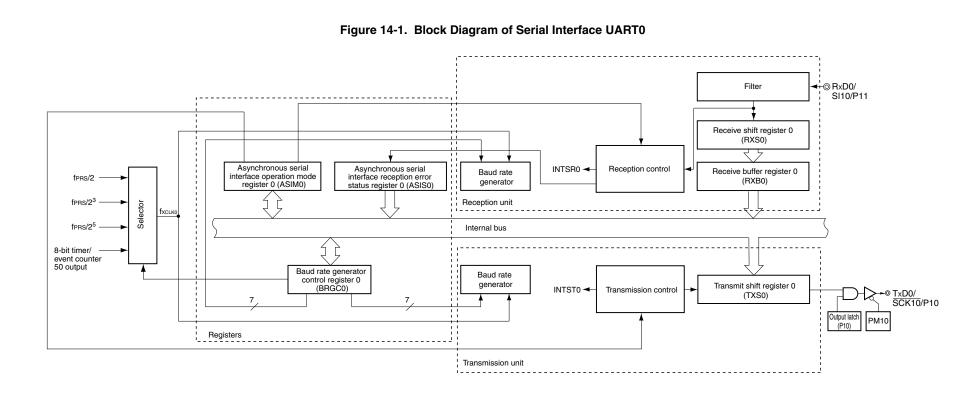

| Serial interface<br>UART0 | ASIS0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Read   | 1 clock (fixed)                                                                                                                                                             |  |  |  |

| Serial interface<br>UART6 | ASIS6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Read   | 1 clock (fixed)                                                                                                                                                             |  |  |  |

| Serial interface<br>IIC0  | IICS0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Read   | 1 clock (fixed)                                                                                                                                                             |  |  |  |

| A/D converter             | ADM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Write  | 1 to 5 clocks (when fad = fprs/2 is selected)                                                                                                                               |  |  |  |

|                           | ADS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Write  | 1 to 7 clocks (when fad = fprs/3 is selected)                                                                                                                               |  |  |  |

|                           | ADPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Write  | 1 to 9 clocks (when $f_{AD} = f_{PRS}/4$ is selected)<br>2 to 13 clocks (when $f_{AD} = f_{PRS}/6$ is selected)                                                             |  |  |  |

|                           | ADCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Read   | 2 to 17 clocks (when $f_{AD} = f_{PRS}/6$ is selected)<br>2 to 17 clocks (when $f_{AD} = f_{PRS}/8$ is selected)<br>2 to 25 clocks (when $f_{AD} = f_{PRS}/12$ is selected) |  |  |  |

|                           | The above number of clocks is when the same source clock is selected for fcPu and fPBS. The number of wait clocks can be calculated by the following expression and under the following conditions. <calculating clocks="" number="" of="" wait="">         • Number of wait clocks = <math>\frac{2 \text{ fcPU}}{f_{AD}}</math> + 1         * Fraction is truncated if the number of wait clocks ≤ 0.5 and rounded up if the number of wait clocks &gt; 0.5         f_AD:       A/D conversion clock frequency (fPBS/2 to fPBS/12)         f_CPU:       CPU clock frequency         f_PBS:       Peripheral hardware clock frequency         f_xP:       Main system clock frequency          Conditions for maximum/minimum number of wait clocks&gt;         • Maximum number of times: Maximum speed of CPU (fxP), lowest speed of A/D conversion clock (fPBS/12)</calculating> |        |                                                                                                                                                                             |  |  |  |

| Table 36-1. | Registers That Generate Wait and Number of CPU Wait Clocks |

|-------------|------------------------------------------------------------|

|-------------|------------------------------------------------------------|

# Caution When the peripheral hardware clock (fPRs) is stopped, do not access the registers listed above using an access method in which a wait request is issued.

**Remark** The clock is the CPU clock (fcPu).

|          | Package                                              | Exchange<br>Adapter | Space Adapter      | YQ Connector       | Mount Adapter      | Target<br>Connector |

|----------|------------------------------------------------------|---------------------|--------------------|--------------------|--------------------|---------------------|

| 78K0/KB2 | 30-pin plastic SSOP<br>(MC-5A4 and<br>MC-CAB types)  | QB-30MC-<br>EA-02T  | QB-30MC-<br>YS-01T | QB-30MC-<br>YQ-01T | QB-30MC-<br>HQ-01T | QB-30MC-<br>NQ-01T  |

|          | 36-pin plastic FLGA<br>(FC-AA3 type)                 | QB-36FC-<br>EA-01T  | None               | None               | None               | QB-36FC-<br>NQ-01T  |

| 78K0/KC2 | 38-pin plastic SSOP<br>(MC-GAA type)                 | QB-38MC-<br>EA-01T  | QB-38MC-<br>YQ-01T | QB-38MC-<br>YQ-01T | QB-38MC-<br>HQ-01T | QB-38MC-<br>NQ-01T  |

|          | 44-pin plastic LQFP<br>(GB-UES and GB-<br>GAF types) | QB-44GB-<br>EA-03T  | QB-44GB-<br>YS-01T | QB-44GB-<br>YQ-01T | QB-44GB-<br>HQ-01T | QB-44GB-<br>NQ-01T  |

|          | 48-pin plastic LQFP<br>(GA-8EU and GA-<br>GAM types) | QB-48GA-<br>EA-02T  | QB-48GA-<br>YS-01T | QB-48GA-<br>YQ-01T | QB-48GA-<br>HQ-01T | QB-48GA-<br>NQ-01T  |

| 78K0/KD2 | 52-pin plastic LQFP<br>(GB-UET and GB-<br>GAG types) | QB-52GB-<br>EA-02T  | QB-52GB-<br>YS-01T | QB-52GB-<br>YQ-01T | QB-52GB-<br>HQ-01T | QB-52GB-<br>NQ-01T  |

| 78K0/KE2 | 64-pin plastic LQFP<br>(GB-UEU and GB-<br>GAH types) | QB-64GB-<br>EA-04T  | QB-64GB-<br>YS-01T | QB-64GB-<br>YQ-01T | QB-64GB-<br>HQ-01T | QB-64GB-<br>NQ-01T  |

|          | 64-pin plastic LQFP<br>(GC-UBS and GC-<br>GAL types) | QB-64GC-<br>EA-03T  | QB-64GC-<br>YS-01T | QB-64GC-<br>YQ-01T | QB-64GC-<br>HQ-01T | QB-64GC-<br>NQ-01T  |

|          | 64-pin plastic LQFP<br>(GK-UET and GK-<br>GAJ types) | QB-64GK-<br>EA-04T  | QB-64GK-<br>YS-01T | QB-64GK-<br>YQ-01T | QB-64GK-<br>HQ-01T | QB-64GK-<br>NQ-01T  |

|          | 64-pin plastic TQFP<br>(GA-9EV and GA-<br>HAB types) | QB-64GA-<br>EA-01T  | QB-64GA-<br>YS-01T | QB-64GA-<br>YQ-01T | QB-64GA-<br>HQ-01T | QB-64GA-<br>NQ-01T  |

|          | 64-pin plastic FLGA<br>(FC-AA1 type)                 | QB-64FC-<br>EA-01T  | None               | None               | None               | QB-64FC-<br>NQ-01T  |

| 78K0/KF2 | 80-pin plastic LQFP<br>(GC-UBT and GC-<br>GAD types) | QB-80GC-<br>EA-01T  | QB-80GC-<br>YS-01T | QB-80GC-<br>YQ-01T | QB-80GC-<br>HQ-01T | QB-80GC-<br>NQ-01T  |

|          | 80-pin plastic LQFP<br>(GK-8EU and GK-<br>GAK type)  | QB-80GK-<br>EA-01T  | QB-80GK-<br>YS-01T | QB-80GK-<br>YQ-01T | QB-80GK-<br>HQ-01T | QB-80GK-<br>NQ-01T  |

**Note** The part numbers of the exchange adapter, space adapter, YQ connector, mount adapter, and target connector and the packages of the target device are described below.

|           |      |                                                               |                                                    |                                                                                                                                                                                                                                                                                                                                           |                    | (6/30 |

|-----------|------|---------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------|

| Chapter   | 0    |                                                               | nction Details of Cautions<br>Function             |                                                                                                                                                                                                                                                                                                                                           | Pa                 | ige   |

| Chapter 6 | Hard | Clock<br>generator                                            | _                                                  | It is not necessary to wait for the oscillation stabilization time when an external clock input from the EXCLK and EXCLKS pins is used.                                                                                                                                                                                                   | pp. 24<br>247      | 16, 🗌 |

| Chal      |      | operation<br>when power<br>supply<br>voltage is<br>turned on  |                                                    | A voltage oscillation stabilization time of 1.93 to 5.39 ms is required after the power<br>supply voltage reaches 1.59 V (TYP.). If the supply voltage rises from<br>1.59 V (TYP.) to 2.7 V (TYP.) within 1.93 ms, the power supply oscillation<br>stabilization time of 0 to 5.39 ms is automatically generated before reset processing. | p. 24              | 7     |

|           | Soft | Controlling<br>high-speed                                     |                                                    | The X1/P121 and X2/EXCLK/P122 pins are in the I/O port mode after a reset release.                                                                                                                                                                                                                                                        | p. 248             | 3     |

|           |      | system clock                                                  | X1 clock                                           | Do not change the value of EXCLK and OSCSEL while the X1 clock is operating.                                                                                                                                                                                                                                                              | p. 249             | )     |

|           |      |                                                               |                                                    | Set the X1 clock after the supply voltage has reached the operable voltage of the clock to be used (see CHAPTER 30 ELECTRICAL SPECIFICATIONS (STANDARD PRODUCTS) to CHAPTER 33 ELECTRICAL SPECIFICATIONS ((A2) GRADE PRODUCTS : $T_A = \bullet 40$ to $+125^{\circ}$ C)).                                                                 | p. 249             | 9     |

|           |      |                                                               | External main<br>system clock                      | Do not change the value of EXCLK and OSCSEL while the external main systerm<br>clock is operating.                                                                                                                                                                                                                                        | p. 249             | €     |

|           |      |                                                               |                                                    | Set the external main system clock after the supply voltage has reached the operable voltage of the clock to be used (see CHAPTER 30 ELECTRICAL SPECIFICATIONS (STANDARD PRODUCTS) to CHAPTER 33 ELECTRICAL SPECIFICATIONS ((A2) GRADE PRODUCTS : $T_A = \bullet 40$ to $+125^\circ$ C)).                                                 | p. 249             | € □   |

|           |      |                                                               | Main system<br>clock                               | If the high-speed system clock is selected as the main system clock, a clock other than the high-speed system clock cannot be set as the peripheral hardware clock.                                                                                                                                                                       | p. 250             |       |

|           |      |                                                               | High-speed<br>system clock                         | Be sure to confirm that MCS = 0 or CLS = 1 when setting MSTOP to 1. In addition, stop peripheral hardware that is operating on the high-speed system clock.                                                                                                                                                                               | p. 25 <sup>.</sup> |       |

|           |      |                                                               | Internal high-<br>speed oscillation<br>clock       | Be sure to confirm that MCS = 1 or CLS = 1 when setting RSTOP to 1. In addition, stop peripheral hardware that is operating on the internal high-speed oscillation clock.                                                                                                                                                                 | p. 25              | 3     |

|           |      |                                                               | XT1/P123,<br>XT2/EXCLKS/<br>P124                   | The XT1/P123 and XT2/EXCLKS/P124 pins are in the I/O port mode after a reset release.                                                                                                                                                                                                                                                     | p. 254             | 1     |

|           |      |                                                               | External clock<br>from peripheral<br>hardware pins | Do not start the peripheral hardware operation with the external clock from peripheral hardware pins when the internal high-speed oscillation clock and high-speed system clock are stopped while the CPU operates with the subsystem clock, or when in the STOP mode.                                                                    | p. 254             | 1     |

|           |      |                                                               | XT1 clock,<br>external<br>subsystem clock          | Do not change the value of XTSTART, EXCLKS, and OSCSELS while the<br>subsystem clock is operating.                                                                                                                                                                                                                                        | p. 254             | 1     |

|           |      |                                                               |                                                    | Be sure to confirm that CLS = 0 when clearing OSCSELS to 0. In addition, stop the watch timer if it is operating on the subsystem clock.                                                                                                                                                                                                  | p. 25              | 5     |

|           |      |                                                               |                                                    | The subsystem clock oscillation cannot be stopped using the STOP instruction.                                                                                                                                                                                                                                                             | p. 25              | 5     |

|           |      | Controlling<br>internal low-<br>speed<br>oscillation<br>clock | Internal low-<br>speed oscillation<br>clock        | If "Internal low-speed oscillator cannot be stopped" is selected by the option byte,<br>oscillation of the internal low-speed oscillation clock cannot be controlled.                                                                                                                                                                     | p. 256             | 6     |