#

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detalls                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | 78K/0                                                                                 |

| Core Size                  | 8-Bit                                                                                 |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                                    |

| Number of I/O              | 55                                                                                    |

| Program Memory Size        | 16KB (16K × 8)                                                                        |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 768 x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 8x10b                                                                             |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 64-LQFP                                                                               |

| Supplier Device Package    | -                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0531agb-gah-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## (1) Conventional-specification products (µPD78F05xx and 78F05xxD) (3/3)

## <4> When high-speed system clock (X1 oscillation or external clock input) is used and entry RAM is located in short direct addressing range

| Library                   | / Name            |                                             | Processing Time ( $\mu$ s)                        |                                      |                            |  |  |

|---------------------------|-------------------|---------------------------------------------|---------------------------------------------------|--------------------------------------|----------------------------|--|--|

|                           |                   | Normal Model                                | of C Compiler                                     | Static Model of C Compiler/Assembler |                            |  |  |

|                           |                   | Min. Max. Min.                              |                                                   | Min.                                 | Max.                       |  |  |

| Self programming start l  | ibrary            |                                             | 34/                                               | fcpu                                 |                            |  |  |

| Initialize library        |                   |                                             | 49/fcpu +                                         | 224.6875                             |                            |  |  |

| Mode check library        |                   | <b>35/f</b> сри +                           | 113.625                                           | <b>29/f</b> сри +                    | 113.625                    |  |  |

| Block blank check library | /                 | 174/fcpu +                                  | 6120.9375                                         | 134/fcpu +                           | 6120.9375                  |  |  |

| Block erase library       |                   | 174/fcpu +<br>30820.75                      | 174/fсец +<br>298675                              | 134/fcpu +<br>30820.75               | 134/fcpu +<br>298675       |  |  |

| Word write library        |                   | 318 (321)/fcpu +<br>383                     | 318 (321)/fcpu + 262 (265)/fcpu + 2<br>1230.5 383 |                                      | 262 (265)/fcpu +<br>1230.5 |  |  |

| Block verify library      |                   | 174/fcpu + 13175.4375 134/fcpu + 13175.4375 |                                                   |                                      |                            |  |  |

| Self programming end li   | brary             | 34/fcpu                                     |                                                   |                                      |                            |  |  |

| Get information library   | Option value: 03H | 171 (172)/fcp                               | u + 171.3125                                      | 129 (130)/fcpu + 171.3125            |                            |  |  |

|                           | Option value: 04H | 181 (182)/fo                                | сец <b>+ 166.75</b>                               | 139 (140)/fcpu + 166.75              |                            |  |  |

| Option value: 05H         |                   | <b>404 (411)/f</b> c                        | ри <b>+ 231.875</b>                               | 362 (369)/fcpu + 231.875             |                            |  |  |

| Set information library   |                   | 75/fcpu +                                   | 75/fcpu +                                         | 67/fcpu +                            | 67/fcpu +                  |  |  |

|                           |                   | 78884.5625                                  | 527566.875                                        | 78884.5625                           | 527566.875                 |  |  |

| EEPROM write library      |                   | 318 (321)/fcpu +                            | 318 (321)/fcpu +                                  | 262 (265)/fcpu +                     | 262 (265)/fcpu +           |  |  |

|                           |                   | 538.75                                      | 1386.25                                           | 538.75                               | 1386.25                    |  |  |

- **Remarks 1.** Values in parentheses indicate values when a write start address structure is located other than in the internal high-speed RAM.

- 2. The above processing times are those during stabilized operation of the internal high-speed oscillator (RSTS = 1).

- 3. fcpu: CPU operation clock frequency

- 4. RSTS: Bit 7 of the internal oscillation mode register (RCM)

## 1.2 Features

- O Minimum instruction execution time can be changed from high speed (0.1  $\mu$ s: @ 20 MHz operation with high-speed system clock) to ultra low-speed (122  $\mu$ s: @ 32.768 kHz operation with subsystem clock)

- O General-purpose register: 8 bits × 32 registers (8 bits × 8 registers × 4 banks)

- $\, \odot \,$  ROM (flash memory), RAM capacities

| ROM <sup>Note</sup> | High-                        | Expansion           | 78K0/KB2                  | 78K0                      | )/KC2                             | 78K0/KD2                          | 78K0/KE2                          | 78K0/KF2                        |

|---------------------|------------------------------|---------------------|---------------------------|---------------------------|-----------------------------------|-----------------------------------|-----------------------------------|---------------------------------|

|                     | Speed<br>RAM <sup>Note</sup> | RAM <sup>Note</sup> | 30/36 pins                | 38/44 pins                | 48 pins                           | 52 pins                           | 64 pins                           | 80 pins                         |

| 128 KB              | 1 KB                         | 6 KB                | _                         | _                         | _                                 | <i>µ</i> PD78F0527D,<br>78F0527DA | <i>µ</i> PD78F0537D,<br>78F0537DA | μPD78F0547D,<br>78F0547DA       |

|                     |                              |                     |                           |                           |                                   | <i>µ</i> PD78F0527,<br>78F0527A   | μPD78F0537,<br>78F0537A           | μPD78F0547<br>78F0547A          |

| 96 KB               | 1 KB                         | 4 KB                | _                         | _                         | _                                 | μPD78F0526,<br>78F0526A           | μPD78F0536,<br>78F0536A           | μPD78F0546,<br>78F0546A         |

| 60 KB               | 1 KB                         | 2 KB                | -                         | _                         | <i>µ</i> PD78F0515D,<br>78F0515DA | <i>µ</i> PD78F0525,<br>78F0525A   | <i>µ</i> PD78F0535,<br>78F0535A   | <i>µ</i> PD78F0545,<br>78F0545A |

|                     |                              |                     |                           |                           | <i>µ</i> PD78F0515,<br>78F0515A   |                                   |                                   |                                 |

| 48 KB               | 1 KB                         | 1 KB                | -                         | -                         | <i>µ</i> PD78F0514,<br>78F0514A   | <i>µ</i> PD78F0524,<br>78F0524A   | <i>µ</i> PD78F0534,<br>78F0534A   | <i>µ</i> PD78F0544,<br>78F0544A |

| 32 KB               | 1 KB                         | -                   | μPD78F0503D,<br>78F0503DA | μPD78F0513D,<br>78F0513DA | <i>µ</i> PD78F0513,<br>78F0513A   | <i>µ</i> PD78F0523,<br>78F0523A   | <i>µ</i> PD78F0533,<br>78F0533A   | -                               |

|                     |                              |                     | μPD78F0503,<br>78F0503A   | μPD78F0513,<br>78F0513A   |                                   |                                   |                                   |                                 |

| 24 KB               | 1 KB                         | -                   | μPD78F0502,<br>78F0502A   | μPD78F0512,<br>78F0512A   | <i>µ</i> PD78F0512,<br>78F0512A   | <i>µ</i> PD78F0522,<br>78F0522A   | <i>µ</i> PD78F0532,<br>78F0532A   | -                               |

| 16 KB               | 768 B                        | -                   | μPD78F0501,<br>78F0501A   | μPD78F0511,<br>78F0511A   | <i>µ</i> PD78F0511,<br>78F0511A   | μPD78F0521,<br>78F0521A           | <i>µ</i> PD78F0531,<br>78F0531A   | -                               |

| 8 KB                | 512 B                        | _                   | μPD78F0500,<br>78F0500A   | _                         | _                                 | _                                 | _                                 | -                               |

- Note The internal flash memory, internal high-speed RAM capacities, and internal expansion RAM capacities can be changed using the internal memory size switching register (IMS) and the internal expansion RAM size switching register (IXS). For IMS and IXS, see 27.1 Internal Memory Size Switching Register and 27.2 Internal Expansion RAM Size Switching Register.

- O Buffer RAM: 32 bytes (can be used for transfer in CSI with automatic transmit/receive function) (78K0/KF2 only)

- O On-chip single-power-supply flash memory

- O Self-programming (with boot swap function)

- On-chip debug function ( $\mu$ PD78F05xxD and 78F05xxDA only)<sup>Note</sup>

- **Note** The μPD78F05xxD and 78F05xxDA have an on-chip debug function, which is provided for development and evaluation. Do not use the on-chip debug function in products designated for mass production, because the guaranteed number of rewritable times of the flash memory may be exceeded when this function is used, and product reliability therefore cannot be guaranteed. Renesas Electronics is not liable for problems occurring when the on-chip debug function is used.

- O On-chip power-on-clear (POC) circuit and low-voltage detector (LVI)

- O On-chip watchdog timer (operable with the on-chip internal low-speed oscillation clock)

### (c) VDD and EVDD

VDD is the positive power supply pin for P121 to P124 and other than ports<sup>Note</sup>. EVDD is the positive power supply pin for ports other than P20 to P27 and P121 to P124. Always make EVDD the same potential as VDD.

**Note** With products that are not mounted with an EV<sub>DD</sub> pin, use V<sub>DD</sub> as a positive power supply pin other than P20 to P27.

### (d) Vss and EVss

Vss is the ground potential pin for P121 to P124 and other than ports. EVss is the ground potential pin for ports other than P20 to P27 and P121 to P124. Always make EVss the same potential as Vss.

**Note** With products that are not mounted with an EVss pin, use Vss as a ground potential pin other than P20 to P27.

#### 2.2.13 RESET

This is the active-low system reset input pin.

#### 2.2.14 REGC

This is the pin for connecting regulator output (2.5 V) stabilization capacitance for internal operation. Connect this pin to Vss via a capacitor (0.47 to 1  $\mu$ F).

#### Caution Keep the wiring length as short as possible for the broken-line part in the above figure.

#### 2.2.15 FLMD0

This is a pin for setting flash memory programming mode.

Connect FLMD0 to EVss or Vss in the normal operation mode.

In flash memory programming mode, connect this pin to the flash memory programmer.

#### (5) Main OSC control register (MOC)

This register selects the operation mode of the high-speed system clock.

This register is used to stop the X1 oscillator or to disable an external clock input from the EXCLK pin when the CPU operates with a clock other than the high-speed system clock.

MOC can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets this register to 80H.

#### Figure 6-8. Format of Main OSC Control Register (MOC)

Address: FFA2H After reset: 80H R/W

Symbol <7> 6 5 3 2 0 4 1 MOC MSTOP 0 0 0 0 0 0 0

| MSTOP | Control of high-speed   | system clock operation                    |

|-------|-------------------------|-------------------------------------------|

|       | X1 oscillation mode     | External clock input mode                 |

| 0     | X1 oscillator operating | External clock from EXCLK pin is enabled  |

| 1     | X1 oscillator stopped   | External clock from EXCLK pin is disabled |

Cautions 1. When setting MSTOP to 1, be sure to confirm that the CPU operates with a clock other than the high-speed system clock. Specifically, set under either of the following conditions.

- <1> 78K0/KB2

- When MCS = 0 (when CPU operates with the internal high-speed oscillation clock)

- <2> 78K0/KC2, 78K0/KD2, 78K0/KE2, and 78K0/KF2

- When MCS = 0 (when CPU operates with the internal high-speed oscillation clock)

- When CLS = 1 (when CPU operates with the subsystem clock)

In addition, stop peripheral hardware that is operating on the high-speed system clock before setting MSTOP to 1.

- 2. Do not clear MSTOP to 0 while bit 6 (OSCSEL) of the clock operation mode select register (OSCCTL) is 0 (I/O port mode).

- 3. The peripheral hardware cannot operate when the peripheral hardware clock is stopped. To resume the operation of the peripheral hardware after the peripheral hardware clock has been stopped, initialize the peripheral hardware.

#### 6.6.5 Clocks supplied to CPU and peripheral hardware

The following table shows the relation among the clocks supplied to the CPU and peripheral hardware, and setting of registers.

#### Table 6-4. Clocks Supplied to CPU and Peripheral Hardware, and Register Setting (78K0/KB2)

| Sup                                   | XSEL                                                        | MCM0 | EXCLK |   |

|---------------------------------------|-------------------------------------------------------------|------|-------|---|

| Clock Supplied to CPU                 | Clock Supplied to CPU Clock Supplied to Peripheral Hardware |      |       |   |

| Internal high-speed oscillation clock | 0                                                           | ×    | ×     |   |

| Internal high-speed oscillation clock | X1 clock                                                    | 1    | 0     | 0 |

|                                       | External main system clock                                  | 1    | 0     | 1 |

| X1 clock                              | 1                                                           | 1    | 0     |   |

| External main system clock            | 1                                                           | 1    | 1     |   |

**Remarks 1.** The 78K0/KB2 is not provided with a subsystem clock.

- **2.** XSEL: Bit 2 of the main clock mode register (MCM)

- MCM0: Bit 0 of MCM

EXCLK: Bit 7 of the clock operation mode select register (OSCCTL)

×: don't care

## Table 6-5. Clocks Supplied to CPU and Peripheral Hardware, and Register Setting (78K0/KC2, 78K0/KD2, 78K0/KE2, and 78K0/KF2)

| Suppli                                | XSEL                                  | CSS | MCM0 | EXCLK |   |

|---------------------------------------|---------------------------------------|-----|------|-------|---|

| Clock Supplied to CPU                 |                                       |     |      |       |   |

| Internal high-speed oscillation clock |                                       | 0   | 0    | ×     | × |

| Internal high-speed oscillation clock | X1 clock                              | 1   | 0    | 0     | 0 |

|                                       | External main system clock            | 1   | 0    | 0     | 1 |

| X1 clock                              |                                       | 1   | 0    | 1     | 0 |

| External main system clock            |                                       | 1   | 0    | 1     | 1 |

| Subsystem clock                       | Internal high-speed oscillation clock | 0   | 1    | ×     | × |

|                                       | X1 clock                              | 1   | 1    | 0     | 0 |

|                                       |                                       | 1   | 1    | 1     | 0 |

|                                       | External main system clock            | 1   | 1    | 0     | 1 |

|                                       |                                       | 1   | 1    | 1     | 1 |

**Remark** XSEL: Bit 2 of the main clock mode register (MCM)

CSS: Bit 4 of the processor clock control register (PCC)

MCM0: Bit 0 of MCM

EXCLK: Bit 7 of the clock operation mode select register (OSCCTL)

×: don't care

## 78K0/Kx2

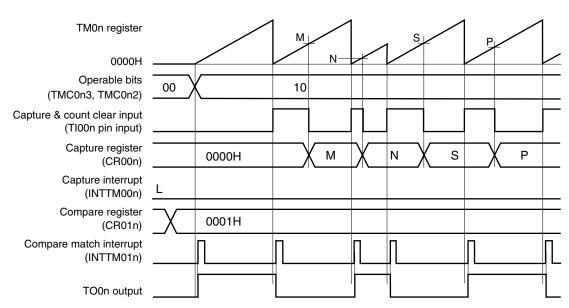

## Figure 7-32. Timing Example of Clear & Start Mode Entered by TI00n Pin Valid Edge Input (CR00n: Capture Register, CR01n: Compare Register) (1/2)

### (a) TOC0n = 13H, PRM0n = 10H, CRC0n, = 03H, TMC0n = 08H, CR01n = 0001H

This is an application example where the TO0n output level is to be inverted when the count value has been captured & cleared.

TMOn is cleared at the rising edge detection of the TI00n pin and it is captured to CR00n at the falling edge detection of the TI00n pin.

When bit 1 (CRC0n1) of capture/compare control register 0n (CRC0n) is set to 1, the count value of TM0n is captured to CR00n in the phase reverse to that of the signal input to the TI00n pin, but the capture interrupt signal (INTTM00n) is not generated. However, the INTTM00n signal is generated when the valid edge of the TI01n pin is detected. Mask the INTTM00n signal when it is not used.

## **Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

| Address: FF | 6AH After | reset: 00H | R/W    |                                               |                           |                 |                      |                          |

|-------------|-----------|------------|--------|-----------------------------------------------|---------------------------|-----------------|----------------------|--------------------------|

| Symbol      | 7         | 6          | 5      | 4                                             | 3                         | 2               | 1                    | 0                        |

| TCL50       | 0         | 0          | 0      | 0                                             | 0                         | TCL502          | TCL501               | TCL500                   |

|             |           |            |        |                                               |                           |                 |                      |                          |

|             | TCL502    | TCL501     | TCL500 |                                               | Coun                      | t clock selecti | on <sup>Note 1</sup> |                          |

|             |           |            |        |                                               | fprs =                    | fprs =          | fprs =               | fprs =                   |

|             |           |            |        |                                               | 2 MHz                     | 5 MHz           | 10 MHz               | 20 MHz                   |

|             | 0         | 0          | 0      | TI50 pin falli                                | ng edge <sup>Note 2</sup> |                 |                      |                          |

|             | 0         | 0          | 1      | TI50 pin risir                                | ng edge <sup>Note 2</sup> |                 |                      |                          |

|             | 0         | 1          | 0      | fprs <sup>Note 3</sup>                        | 2 MHz                     | 5 MHz           | 10 MHz               | 20 MHz <sup>Note 4</sup> |

|             | 0         | 1          | 1      | fprs/2                                        | 1 MHz                     | 2.5 MHz         | 5 MHz                | 10 MHz                   |

|             | 1         | 0          | 0      | fprs/2 <sup>2</sup> 500 kHz 1.25 MHz 2.5 MH   |                           | 2.5 MHz         | 5 MHz                |                          |

|             | 1         | 0          | 1      | fprs/2 <sup>6</sup> 31.25 kHz 78.13 kHz 156.2 |                           | 156.25 kHz      | 312.5 kHz            |                          |

|             | 1         | 1          | 0      | fprs/2 <sup>8</sup>                           | 7.81 kHz                  | 19.53 kHz       | 39.06 kHz            | 78.13 kHz                |

|             | 1         | 1          | 1      | fprs/2 <sup>13</sup>                          | 0.24 kHz                  | 0.61 kHz        | 1.22 kHz             | 2.44 kHz                 |

#### Figure 8-5. Format of Timer Clock Selection Register 50 (TCL50)

**Notes 1.** The frequency that can be used for the peripheral hardware clock (fPRs) differs depending on the power supply voltage and product specifications.

| Supply Voltage                                                                                                                                   | Conventional-specification Products (µPD78F05xx and 78F05xxD) | Expanded-specification Products (µPD78F05xxA and 78F05xxDA) |

|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------|

| $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                                                                                                            | $f_{PRS} \leq 20 \text{ MHz}$                                 | $f_{PRS} \le 20 \text{ MHz}$                                |

| $2.7~V \leq V_{\text{DD}} < 4.0~V$                                                                                                               | $f_{PRS} \leq 10 \text{ MHz}$                                 |                                                             |

| $\begin{array}{l} 1.8 \ V \leq V_{\text{DD}} < 2.7 \ V \\ (\text{Standard products and} \\ (\text{A}) \ \text{grade products only}) \end{array}$ | fprs ≤ 5 MHz                                                  | fprs ≤ 5 MHz                                                |

(The values shown in the table above are those when fPRS = fXH (XSEL = 1).)

- 2. Do not start timer operation with the external clock from the TI50 pin when the internal high-speed oscillation clock and high-speed system clock are stopped while the CPU operates with the subsystem clock, or when in the STOP mode.

- 3. If the peripheral hardware clock (fPRs) operates on the internal high-speed oscillation clock (fRH) (XSEL = 0), when 1.8 V  $\leq$  VDD < 2.7 V, the setting of TCL502, TCL501, TCL500 = 0, 1, 0 (count clock: fPRs) is prohibited.

- 4. This is settable only if 4.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V.

## Cautions 1. When rewriting TCL50 to other data, stop the timer operation beforehand.

2. Be sure to clear bits 3 to 7 to "0".

Remark fPRs: Peripheral hardware clock frequency

## (e) Reception error

Three types of errors may occur during reception: a parity error, framing error, or overrun error. If the error flag of asynchronous serial interface reception error status register 0 (ASIS0) is set as a result of data reception, a reception error interrupt (INTSR0) is generated.

Which error has occurred during reception can be identified by reading the contents of ASIS0 in the reception error interrupt (INTSR0) servicing (see **Figure 14-3**).

The contents of ASIS0 are cleared to 0 when ASIS0 is read.

| Reception Error | Cause                                                                                              |

|-----------------|----------------------------------------------------------------------------------------------------|

| Parity error    | The parity specified for transmission does not match the parity of the receive data.               |

| Framing error   | Stop bit is not detected.                                                                          |

| Overrun error   | Reception of the next data is completed before data is read from receive buffer register 0 (RXB0). |

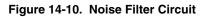

#### (f) Noise filter of receive data

The RxD0 signal is sampled using the base clock output by the prescaler block.

If two sampled values are the same, the output of the match detector changes, and the data is sampled as input data.

Because the circuit is configured as shown in Figure 14-10, the internal processing of the reception operation is delayed by two clocks from the external signal status.

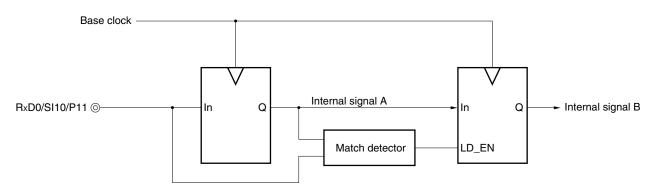

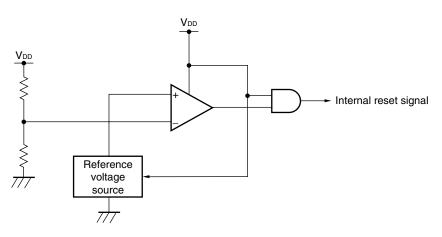

#### (4) Permissible baud rate range during reception

The permissible error from the baud rate at the transmission destination during reception is shown below.

## Caution Make sure that the baud rate error during reception is within the permissible error range, by using the calculation expression shown below.

As shown in Figure 15-25, the latch timing of the receive data is determined by the counter set by baud rate generator control register 6 (BRGC6) after the start bit has been detected. If the last data (stop bit) meets this latch timing, the data can be correctly received.

Assuming that 11-bit data is received, the theoretical values can be calculated as follows.

$FL = (Brate)^{-1}$

Brate:Baud rate of UART6k:Set value of BRGC6FL:1-bit data lengthMargin of latch timing: 2 clocks

#### (2) Communication operation

In the 3-wire serial I/O mode, data is transmitted or received in 8-bit units. Each bit of the data is transmitted or received in synchronization with the serial clock.

Data can be transmitted or received if bit 6 (TRMD1n) of serial operation mode register 1n (CSIM1n) is 1. Transmission/reception is started when a value is written to transmit buffer register 1n (SOTB1n). In addition, data can be received when bit 6 (TRMD1n) of serial operation mode register 1n (CSIM1n) is 0.

Reception is started when data is read from serial I/O shift register 1n (SIO1n).

However, communication is performed as follows if bit 5 (SSE11) of CSIM11 is 1 when serial interface CSI11 is in the slave mode.

- <1> Low level input to the SSI11 pin

- → Transmission/reception is started when SOTB11 is written, or reception is started when SIO11 is read.

- <2> High level input to the  $\overline{SSI11}$  pin

- → Transmission/reception or reception is held, therefore, even if SOTB11 is written or SIO11 is read, transmission/reception or reception will not be started.

- <3> Data is written to SOTB11 or data is read from SIO11 while a high level is input to the SSI11 pin, then a low level is input to the SSI11 pin

- $\rightarrow$  Transmission/reception or reception is started.

- <4> A high level is input to the SSI11 pin during transmission/reception or reception

- $\rightarrow$  Transmission/reception or reception is suspended.

After communication has been started, bit 0 (CSOT1n) of CSIM1n is set to 1. When communication of 8-bit data has been completed, a communication completion interrupt request flag (CSIIF1n) is set, and CSOT1n is cleared to 0. Then the next communication is enabled.

- Cautions 1. Do not access the control register and data register when CSOT1n = 1 (during serial communication).

- 2. When using serial interface CSI11, wait for the duration of at least one clock before the clock operation is started to change the level of the SSI11 pin in the slave mode; otherwise, malfunctioning may occur.

- **Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

- n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

| Addre | ess: Fl | FA6H | I A                                                                                              | fter reset: 00 | )H R/W |       |       |       |      |      |  |

|-------|---------|------|--------------------------------------------------------------------------------------------------|----------------|--------|-------|-------|-------|------|------|--|

| Sy    | mbol    | <    | <7>                                                                                              | <6>            | <5>    | <4>   | <3>   | <2>   | <1>  | <0>  |  |

| 110   | CC0     | 110  | CE0                                                                                              | LREL0          | WREL0  | SPIE0 | WTIM0 | ACKE0 | STT0 | SPT0 |  |

| Г     |         |      |                                                                                                  |                |        |       | 120   |       |      |      |  |

|       | IICE    | )    | I <sup>2</sup> C operation enable                                                                |                |        |       |       |       |      |      |  |

|       | 0       |      | Stop operation. Reset IIC status register 0 (IICS0) <sup>Note 1</sup> . Stop internal operation. |                |        |       |       |       |      |      |  |

#### Figure 18-5. Format of IIC Control Register 0 (IICC0) (1/4)

| 0                      | Stop operation. Reset IIC status register 0 (IICS0) <sup>Note 1</sup> . Stop internal operation. |                                   |  |  |  |  |

|------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------|--|--|--|--|

| 1                      | Enable operation.                                                                                |                                   |  |  |  |  |

| Be sure to se          | Be sure to set this bit (1) while the SCL0 and SDA0 lines are at high level.                     |                                   |  |  |  |  |

| Condition for          | r clearing (IICE0 = 0)                                                                           | Condition for setting (IICE0 = 1) |  |  |  |  |

| Cleared by instruction |                                                                                                  | Set by instruction                |  |  |  |  |

| Reset                  |                                                                                                  |                                   |  |  |  |  |

| LRELO <sup>Note s 2, 3</sup>                                                                                                                                                                                                                                                               | Exit from communications                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 0                                                                                                                                                                                                                                                                                          | Normal operation                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| 1                                                                                                                                                                                                                                                                                          | This exits from the current communications and sets standby mode. This setting is automatically cleared to 0 after being executed.<br>Its uses include cases in which a locally irrelevant extension code has been received.<br>The SCL0 and SDA0 lines are set to high impedance.<br>The following flags of IIC control register 0 (IICC0) and IIC status register 0 (IICS0) are cleared to 0.<br>• STT0 • SPT0 • MSTS0 • EXC0 • COI0 • TRC0 • ACKD0 • STD0 |  |  |  |  |  |  |  |

| The standby mode following exit from communications remains in effect until the following communications entry conditions are met.<br>• After a stop condition is detected, restart is in master mode.<br>• An address match or extension code reception occurs after the start condition. |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Condition for clearing (LREL0 = 0)    | Condition for setting (LREL0 = 1) |  |  |

|---------------------------------------|-----------------------------------|--|--|

| Automatically cleared after execution | Set by instruction                |  |  |

| • Reset                               |                                   |  |  |

| WREL0 <sup>Note s 2, 3</sup>                                          | Wait cancellation                                                                                                                                                                     |                    |  |  |  |  |  |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|--|--|--|

| 0                                                                     | Do not cancel wait                                                                                                                                                                    | Do not cancel wait |  |  |  |  |  |

| 1                                                                     | Cancel wait. This setting is automatically cleared after wait is canceled.                                                                                                            |                    |  |  |  |  |  |

|                                                                       | When WREL0 is set (wait canceled) during the wait period at the ninth clock pulse in the transmission status (TRC0 = 1), the SDA0 line goes into the high impedance state (TRC0 = 0). |                    |  |  |  |  |  |

| Condition for                                                         | Condition for clearing (WREL0 = 0) Condition for setting (WREL0 = 1)                                                                                                                  |                    |  |  |  |  |  |

| <ul><li>Automatically cleared after execution</li><li>Reset</li></ul> |                                                                                                                                                                                       | Set by instruction |  |  |  |  |  |

Notes 1. The IICS0 register, the STCF0 and IICBSY bits of the IICF0 register, and the CLD0 and DAD0 bits of the IICCL0 register are reset.

2. The signals of these bits are invalid while the IICE0 bit is 0.

3. When the LREL0 and WREL0 bits are read, 0 is always read.

<R> Caution If the operation of I<sup>2</sup>C is enabled (IICE0 = 1) when the SCL0 line is high level, the SDA0 line is low level, and the digital filter is turned on (DFC0 of the IICCL0 register = 1), a start condition will be inadvertently detected immediately. In this case, set (1) the LREL0 bit by using a 1-bit memory manipulation instruction immediately after enabling operation of I<sup>2</sup>C (IICE0 = 1).

<R>

| STT0 <sup>Note</sup>                                                                                                                                                                                                                                                                                                              | Start condition trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                         |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|--|--|--|

| 0                                                                                                                                                                                                                                                                                                                                 | Do not generate a start condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                         |  |  |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                                 | <ul> <li>When bus is released (in standby state, when IICBSY = 0):</li> <li>If this bit is set (1), a start condition is generated (startup as the master).</li> <li>When a third party is communicating:</li> <li>When communication reservation function is enabled (IICRSV = 0)</li> <li>Functions as the start condition reservation flag. When set to 1, automatically generates a start condition after the bus is released.</li> </ul>                                                                                                                                                                                  |                                                                                         |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                   | <ul> <li>When communication reservation function is d<br/>Even if this bit is set (1), the STT0 is cleared a<br/>generated.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | isabled (IICRSV = 1)<br>nd the STT0 clear flag (STCF) is set (1). No start condition is |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                   | In the wait state (when master device):<br>Generates a restart condition after releasing the w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | wait.                                                                                   |  |  |  |  |  |

| <ul> <li>For mast</li> <li>For mast</li> <li>Cannot b</li> </ul>                                                                                                                                                                                                                                                                  | <ul> <li>Cautions concerning set timing</li> <li>For master reception: Cannot be set to 1 during transfer. Can be set to 1 only in the waiting period when ACKE0 has been cleared to 0 and slave has been notified of final reception.</li> <li>For master transmission: A start condition cannot be generated normally during the acknowledge period. Set to 1 during the wait period that follows output of the ninth clock.</li> <li>Cannot be set to 1 at the same time as stop condition trigger (SPT0).</li> <li>Setting the STT0 bit to 1 and then setting it again before it is cleared to 0 is prohibited.</li> </ul> |                                                                                         |  |  |  |  |  |

| Condition f                                                                                                                                                                                                                                                                                                                       | for clearing (STT0 = 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Condition for setting (STT0 = 1)                                                        |  |  |  |  |  |

| <ul> <li>Cleared by setting SST0 bit to 1 while communication reservation is prohibited.</li> <li>Cleared by loss in arbitration</li> <li>Cleared after start condition is generated by master device</li> <li>Cleared by LREL0 = 1 (exit from communications)</li> <li>When IICE0 = 0 (operation stop)</li> <li>Reset</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Set by instruction                                                                      |  |  |  |  |  |

## Figure 18-5. Format of IIC Control Register 0 (IICC0) (3/4)

**Note** The signal of this bit is invalid while IICE0 is 0.

Remarks 1. Bit 1 (STT0) becomes 0 when it is read after data setting.

- 2. IICRSV: Bit 0 of IIC flag register (IICF0)

- STCF: Bit 7 of IIC flag register (IICF0)

<R>

## CHAPTER 19 MULTIPLIER/DIVIDER

|                    | 78K0/KB2 | 78K0/KC2                                          | 78K0/KD2                | 78K0/KE2 | 78K0/KF2 |  |  |  |

|--------------------|----------|---------------------------------------------------|-------------------------|----------|----------|--|--|--|

| Multiplier/divider | -        | Products whose flash memory is less than 32 KB: – |                         |          |          |  |  |  |

|                    |          | Products whose flash                              | n memory is at least 48 | кв: √    |          |  |  |  |

**Remark**  $\sqrt{:}$  Mounted, -: Not mounted

Caution Do not use serial interface IIC0 and the multiplier/divider simultaneously, because various flags corresponding to interrupt request sources are shared among serial interface IIC0 and the multiplier/divider.

#### **19.1 Functions of Multiplier/Divider**

The multiplier/divider has the following functions.

- 16 bits × 16 bits = 32 bits (multiplication)

- 32 bits ÷ 16 bits = 32 bits, 16-bit remainder (division)

#### 19.2 Configuration of Multiplier/Divider

The multiplier/divider includes the following hardware.

| Table 19-1. | Configuration of Multiplier/Divider |

|-------------|-------------------------------------|

|             |                                     |

| Item             | Configuration                                                                                                                                    |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Registers        | Remainder data register 0 (SDR0)<br>Multiplication/division data registers A0 (MDA0H, MDA0L)<br>Multiplication/division data registers B0 (MDB0) |

| Control register | Multiplier/divider control register 0 (DMUC0)                                                                                                    |

Figure 19-1 shows the block diagram of the multiplier/divider.

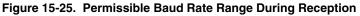

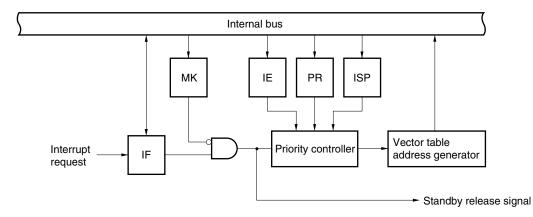

## Figure 20-1. Basic Configuration of Interrupt Function (1/2)

#### (A) Internal maskable interrupt

#### (B) External maskable interrupt (INTPn)

Remark

n = 0 to 5:

78K0/KB2, 38-pin and 44-pin products of 78K0/KC2

n = 0 to 6:

78K0/KD2, 48-pin products of 78K0/KC2

n = 0 to 7:

78K0/KE2, 78K0/KF2

- IF: Interrupt request flag

- IE: Interrupt enable flag

- ISP: In-service priority flag

- MK: Interrupt mask flag

- PR: Priority specification flag

|                          | Hardware                                                                | Status After Reset<br>Acknowledgment <sup>Note</sup> |

|--------------------------|-------------------------------------------------------------------------|------------------------------------------------------|

| Serial interface UART6   | Receive buffer register 6 (RXB6)                                        | FFH                                                  |

|                          | Transmit buffer register 6 (TXB6)                                       | FFH                                                  |

|                          | Asynchronous serial interface operation mode register 6 (ASIM6)         | 01H                                                  |

|                          | Asynchronous serial interface reception error status register 6 (ASIS6) | 00H                                                  |

|                          | Asynchronous serial interface transmission status register 6 (ASIF6)    | 00H                                                  |

|                          | Clock selection register 6 (CKSR6)                                      | 00H                                                  |

|                          | Baud rate generator control register 6 (BRGC6)                          | FFH                                                  |

|                          | Asynchronous serial interface control register 6 (ASICL6)               | 16H                                                  |

|                          | Input switch control register (ISC)                                     | 00H                                                  |

| Serial interfaces CSI10, | Transmit buffer registers 10, 11 (SOTB10, SOTB11)                       | 00H                                                  |

| CSI11                    | Serial I/O shift registers 10, 11 (SIO10, SIO11)                        | 00H                                                  |

|                          | Serial operation mode registers 10, 11 (CSIM10, CSIM11)                 | 00H                                                  |

|                          | Serial clock selection registers 10, 11 (CSIC10, CSIC11)                | 00H                                                  |

| Serial interface CSIA0   | Serial operation mode specification register 0 (CSIMA0)                 | 00H                                                  |

|                          | Serial status register 0 (CSIS0)                                        | 00H                                                  |

|                          | Serial trigger register 0 (CSIT0)                                       | 00H                                                  |

|                          | Divisor value selection register 0 (BRGCA0)                             | 03H                                                  |

|                          | Automatic data transfer address point specification register 0 (ADTP0)  | 00H                                                  |

|                          | Automatic data transfer interval specification register 0 (ADTI0)       | 00H                                                  |

|                          | Serial I/O shift register 0 (SIOA0)                                     | 00H                                                  |

|                          | Automatic data transfer address count register 0 (ADTC0)                | 00H                                                  |

| Serial interface IIC0    | Shift register 0 (IIC0)                                                 | 00H                                                  |

|                          | Control register 0 (IICC0)                                              | 00H                                                  |

|                          | Slave address register 0 (SVA0)                                         | 00H                                                  |

|                          | Clock selection register 0 (IICCL0)                                     | 00H                                                  |

|                          | Function expansion register 0 (IICX0)                                   | 00H                                                  |

|                          | Status register 0 (IICS0)                                               | 00H                                                  |

|                          | Flag register 0 (IICF0)                                                 | 00H                                                  |

| Multiplier/divider       | Remainder data register 0 (SDR0)                                        | 0000H                                                |

|                          | Multiplication/division data register A0 (MDA0H, MDA0L)                 | 0000H                                                |

|                          | Multiplication/division data register B0 (MDB0)                         | 0000H                                                |

|                          | Multiplier/divider control register 0 (DMUC0)                           | 00H                                                  |

| Key interrupt            | Key return mode register (KRM)                                          | 00H                                                  |

| Table 23-2. | Hardware S | Statuses Af | ter Reset | Acknowledgment (3/4) |

|-------------|------------|-------------|-----------|----------------------|

|-------------|------------|-------------|-----------|----------------------|

- **Note** During reset signal generation or oscillation stabilization time wait, only the PC contents among the hardware statuses become undefined. All other hardware statuses remain unchanged after reset.

- Remark The special function register (SFR) mounted depend on the product. See 3.2.3 Special function registers (SFRs).

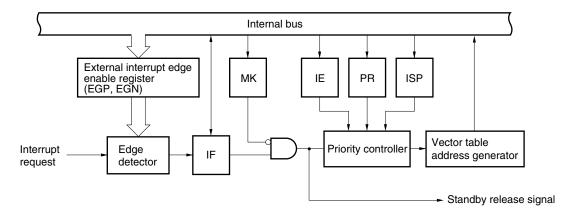

## 24.2 Configuration of Power-on-Clear Circuit

The block diagram of the power-on-clear circuit is shown in Figure 24-1.

## Figure 24-1. Block Diagram of Power-on-Clear Circuit

#### 24.3 Operation of Power-on-Clear Circuit

#### (1) In 1.59 V POC mode (option byte: POCMODE = 0)

- An internal reset signal is generated on power application. When the supply voltage (V<sub>DD</sub>) exceeds the detection voltage (V<sub>POC</sub> = 1.59 V ±0.15 V), the reset status is released.

- The supply voltage (V<sub>DD</sub>) and detection voltage (V<sub>POC</sub> = 1.59 V ±0.15 V) are compared. When V<sub>DD</sub> < V<sub>POC</sub>, the internal reset signal is generated. It is released when V<sub>DD</sub> ≥ V<sub>POC</sub>.

#### (2) In 2.7 V/1.59 V POC mode (option byte: POCMODE = 1)

- An internal reset signal is generated on power application. When the supply voltage (V<sub>DD</sub>) exceeds the detection voltage (V<sub>DDPOC</sub> = 2.7 V ±0.2 V), the reset status is released.

- The supply voltage (V<sub>DD</sub>) and detection voltage (V<sub>POC</sub> = 1.59 V ±0.15 V) are compared. When V<sub>DD</sub> < V<sub>POC</sub>, the internal reset signal is generated. It is released when V<sub>DD</sub> ≥ V<sub>DDPOC</sub>.

The timing of generation of the internal reset signal by the power-on-clear circuit and low-voltage detector is shown below.

### Caution The pins mounted depend on the product. Refer to Caution at the beginning of this chapter.

#### (2) Serial interface

#### $(T_A = -40 \text{ to } +110^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{DD} = \text{EV}_{DD} \le 5.5 \text{ V}, \text{AV}_{REF} \le \text{V}_{DD}, \text{V}_{SS} = \text{EV}_{SS} = \text{AV}_{SS} = 0 \text{ V})$

#### (a) UART6 (dedicated baud rate generator output)

| Parameter     | Symbol | Conditions | MIN. | TYP. | MAX. | Unit |

|---------------|--------|------------|------|------|------|------|

| Transfer rate |        |            |      |      | 625  | kbps |

#### (b) UART0 (dedicated baud rate generator output)

| Parameter     | Symbol | Conditions | MIN. | TYP. | MAX. | Unit |

|---------------|--------|------------|------|------|------|------|

| Transfer rate |        |            |      |      | 625  | kbps |

#### (c) IIC0

| Parameter                                       | Symbol       | Conditions                                                                                                                               | Standard Mode |      | High-Spe | ed Mode                                         | Unit |

|-------------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|----------|-------------------------------------------------|------|

|                                                 |              |                                                                                                                                          | MIN.          | MAX. | MIN.     | MAX.                                            |      |

| SCL0 clock frequency                            | fsc∟         |                                                                                                                                          | 0             | 100  | 0        | 400                                             | kHz  |

| Setup time of restart condition                 | tsu: STA     |                                                                                                                                          | 4.7           | -    | 0.6      | _                                               | μs   |

| Hold time <sup>Note 1</sup>                     | thd: STA     |                                                                                                                                          | 4.0           | -    | 0.6      | _                                               | μS   |

| Hold time when SCL0 = "L"                       | tLOW         | Internal clock operation                                                                                                                 | 4.7           | -    | 1.3      | _                                               | μs   |

|                                                 |              | EXSCL0 clock (6.4 MHz) operation                                                                                                         | 4.7           | -    | 1.25     | -                                               | μS   |

| Hold time when SCL0 = "H"                       | tніgн        |                                                                                                                                          | 4.0           | -    | 0.6      | _                                               | μs   |

| Data setup time (reception)                     | tsu: dat     |                                                                                                                                          | 250           | -    | 100      | _                                               | ns   |

| Data hold time (transmission) <sup>Note 2</sup> | thd: dat     | $\label{eq:weight} \begin{split} f_W &= f_{XH}/2^N  \text{or} \; f_W = f_{\text{EXSCL0}} \\ \text{selected}^{\text{Note 3}} \end{split}$ | 0             | 3.45 | 0        | 0.9 <sup>Note 4</sup><br>1.00 <sup>Note 5</sup> | μs   |

|                                                 |              | $f_W = f_{RH}/2^N selected^{Note 3}$                                                                                                     | 0             | 3.45 | 0        | 1.05                                            | μS   |

| Setup time of stop condition                    | tsu: sto     |                                                                                                                                          | 4.0           | -    | 0.6      | —                                               | μs   |

| Bus free time                                   | <b>t</b> BUF |                                                                                                                                          | 4.7           | _    | 1.3      | -                                               | μS   |

Notes 1. The first clock pulse is generated after this period when the start/restart condition is detected.

- 2. The maximum value (MAX.) of the:DAT is during normal transfer and a wait state is inserted in the ACK (acknowledge) timing.

- 3. fw indicates the IIC0 transfer clock selected by the IICCL and IICX0 registers.

- 4. When fw  $\geq$  4.4 MHz is selected

- 5. When fw < 4.4 MHz is selected

• μPD78F0531AGA-HAB-AX, 78F0532AGA-HAB-AX, 78F0533AGA-HAB-AX, 78F0534AGA-HAB-AX, 78F0535AGA-HAB-AX, 78F0536AGA-HAB-AX, 78F0537AGA-HAB-AX, 78F0537DAGA-HAB-AX

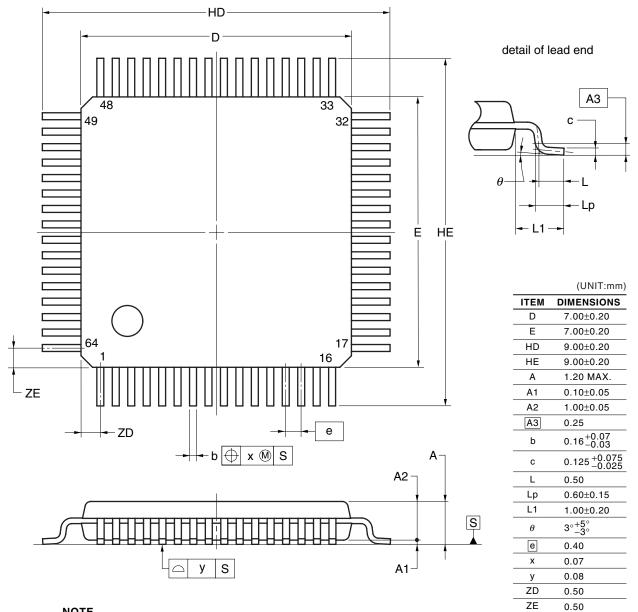

## 64-PIN PLASTIC TQFP (FINE PITCH) (7x7)

NOTE

Each lead centerline is located within 0.07mm of its true position at maximum material condition.

P64GA-40-HAB

|                         |                |                                                                                |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | (28                                                                                                                                                   | /30)                                          |

|-------------------------|----------------|--------------------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Chapter                 | Classification | Function                                                                       | Details of<br>Function                                   | Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Page                                                                                                                                                  |                                               |

| Chapter 27              | Hard           | Flash<br>memory                                                                | E.P.V.<br>command<br>usage                               | When executing boot swapping, do not use the E.P.V. command with the dedicated flash memory programmer.                                                                                                                                                                                                                                                                                                                                                                                           | pp. 737,<br>738, 753                                                                                                                                  |                                               |

|                         | Soft           |                                                                                | self-<br>programming                                     | The self-programming function cannot be used when the CPU operates with the subsystem clock.                                                                                                                                                                                                                                                                                                                                                                                                      | p. 739                                                                                                                                                |                                               |

|                         |                |                                                                                |                                                          | Oscillation of the internal high-speed oscillator is started during self programming, regardless of the setting of the RSTOP flag (bit 0 of the internal oscillation mode register (RCM)). Oscillation of the internal high-speed oscillator cannot be stopped even if the STOP instruction is executed.                                                                                                                                                                                          |                                                                                                                                                       |                                               |

|                         |                |                                                                                |                                                          | Input a high level to the FLMD0 pin during self-programming.                                                                                                                                                                                                                                                                                                                                                                                                                                      | p. 739                                                                                                                                                |                                               |

|                         |                |                                                                                |                                                          | Be sure to execute the DI instruction before starting self-programming.<br>The self-programming function checks the interrupt request flags (IF0L, IF0H, IF1L, and IF1H). If an interrupt request is generated, self-programming is stopped.                                                                                                                                                                                                                                                      | p. 739                                                                                                                                                |                                               |

|                         |                |                                                                                |                                                          | Self-programming is also stopped by an interrupt request that is not masked even in the DI status. To prevent this, mask the interrupt by using the interrupt mask flag registers (MK0L, MK0H, MK1L, and MK1H).                                                                                                                                                                                                                                                                                   | p. 739                                                                                                                                                |                                               |

|                         |                |                                                                                |                                                          | Allocate the entry program for self-programming in the common area of 0000H to 7FFFH.                                                                                                                                                                                                                                                                                                                                                                                                             | p. 740                                                                                                                                                |                                               |

| Chapter 28              | Hard           | On-chip<br>debug<br>function<br>(µPD78F<br>05xxD<br>and<br>78F05xx<br>DA only) | μΡD78F05xxD<br>and 78F05xxDA                             | The $\mu$ PD78F05xxD and 78F05xxDA have an on-chip debug function, which is provided<br>for development and evaluation. Do not use the on-chip debug function in products<br>designated for mass production, because the guaranteed number of rewritable times of<br>the flash memory may be exceeded when this function is used, and product reliability<br>therefore cannot be guaranteed. Renesas Electronics is not liable for problems<br>occurring when the on-chip debug function is used. | p. 756                                                                                                                                                |                                               |

|                         |                |                                                                                |                                                          | Input the clock from the OCD0A/X1 pin during on-chip debugging.                                                                                                                                                                                                                                                                                                                                                                                                                                   | p. 756                                                                                                                                                |                                               |

|                         |                |                                                                                |                                                          | Control the OCD0A/X1 and OCD0B/X2 pins by externally pulling down the OCD1A/P31 pin or by using an external circuit using the P130 pin (that outputs a low level when the device is reset).                                                                                                                                                                                                                                                                                                       | p. 756                                                                                                                                                |                                               |