# E·X Renesas Electronics America Inc - <u>UPD78F0532AGC-GAL-AX Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | 78K/0                                                                                 |

| Core Size                  | 8-Bit                                                                                 |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                                    |

| Number of I/O              | 55                                                                                    |

| Program Memory Size        | 24KB (24K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 1K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 8x10b                                                                             |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 64-LQFP                                                                               |

| Supplier Device Package    | -                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0532agc-gal-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## (2) Expanded-specification products (µPD78F05xxA and 78F05xxDA) (1/2)

## <1> When internal high-speed oscillation clock is used

| Library Name              | Interrupt Response Time (µs (Max.))                         |                                                              |                                                             |                                                              |  |

|---------------------------|-------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------|--|

|                           | Normal Model                                                | of C Compiler                                                | Static Model of C Cor                                       | mpiler/Assembler                                             |  |

|                           | Entry RAM location<br>is outside short<br>direct addressing | Entry RAM location<br>is in short direct<br>addressing range | Entry RAM location<br>is outside short<br>direct addressing | Entry RAM location<br>is in short direct<br>addressing range |  |

|                           | range                                                       |                                                              | range                                                       |                                                              |  |

| Block blank check library | 1100.9                                                      | 431.9                                                        | 1095.3                                                      | 426.3                                                        |  |

| Block erase library       | 1452.9                                                      | 783.9                                                        | 1447.3                                                      | 778.3                                                        |  |

| Word write library        | 1247.2                                                      | 579.2                                                        | 1239.2                                                      | 571.2                                                        |  |

| Block verify library      | 1125.9                                                      | 455.9                                                        | 1120.3                                                      | 450.3                                                        |  |

| Set information library   | 906.9                                                       | 312.0                                                        | 905.8                                                       | 311.0                                                        |  |

| EEPROM write library      | 1215.2                                                      | 547.2                                                        | 1213.9                                                      | 545.9                                                        |  |

**Remarks 1.** The above interrupt response times are those during stabilized operation of the internal high-speed oscillator (RSTS = 1).

2. RSTS: Bit 7 of the internal oscillation mode register (RCM)

#### <2> When high-speed system clock is used (normal model of C compiler)

| Library Name                         | Interrupt Response Time ( $\mu$ s (Max.)) |                                          |                                        |                                          |  |

|--------------------------------------|-------------------------------------------|------------------------------------------|----------------------------------------|------------------------------------------|--|

|                                      | RSTOP = 0                                 | ), RSTS = 1                              | RSTOP = 1                              |                                          |  |

|                                      | Entry RAM location<br>is outside short    | Entry RAM location<br>is in short direct | Entry RAM location<br>is outside short | Entry RAM location<br>is in short direct |  |

|                                      | direct addressing                         | addressing range                         | direct addressing                      | addressing range                         |  |

|                                      | range                                     |                                          | range                                  |                                          |  |

| Block blank check library            | 179/fсри + 567                            | 179/fcpu + 246                           | 179/fcpu + 1708                        | 179/fcpu + 569                           |  |

| Block erase library                  | 179/fcpu + 780                            | 179/fcpu + 459                           | 179/fcpu + 1921                        | 179/fcpu + 782                           |  |

| Word write library                   | 333/fcpu + 763                            | 333/fcpu + 443                           | 333/fcpu + 1871                        | 333/fcpu + 767                           |  |

| Block verify library                 | 179/fcpu + 580                            | 179/fcpu + 259                           | 179/fcpu + 1721                        | 179/fcpu + 582                           |  |

| Set information library              | 80/fcpu + 456                             | 80/fcpu + 200                            | 80/fcpu + 1598                         | 80/fcpu + 459                            |  |

| EEPROM write library <sup>Note</sup> | 29/fcpu + 767                             | 29/fcpu + 447                            | 29/fcpu + 767                          | <u> 29/fcpu + 447</u>                    |  |

|                                      | 333/fcpu + 696                            | 333/fcpu + 376                           | 333/fcpu + 1838                        | 333/fcpu + 700                           |  |

**Note** The longer value of the EEPROM write library interrupt response time becomes the Max. value, depending on the value of fcPu.

#### Remarks 1. fcPU: CPU operation clock frequency

- 2. RSTOP: Bit 0 of the internal oscillation mode register (RCM)

- 3. RSTS: Bit 7 of the internal oscillation mode register (RCM)

| Symbol | 7   | 6   | 5    | 4                    | 3                    | 2                    | 1                    | 0    | Address | After reset        | R/W |

|--------|-----|-----|------|----------------------|----------------------|----------------------|----------------------|------|---------|--------------------|-----|

| P0     | 0   | P06 | P05  | P04                  | P03                  | P02                  | P01                  | P00  | FF00H   | 00H (output latch) | R/W |

|        |     |     |      |                      |                      |                      |                      |      | -       |                    |     |

| P1     | P17 | P16 | P15  | P14                  | P13                  | P12                  | P11                  | P10  | FF01H   | 00H (output latch) | R/W |

|        |     |     |      |                      |                      |                      |                      |      | -       |                    |     |

| P2     | P27 | P26 | P25  | P24                  | P23                  | P22                  | P21                  | P20  | FF02H   | 00H (output latch) | R/W |

|        |     |     |      |                      |                      |                      |                      |      | _       |                    |     |

| P3     | 0   | 0   | 0    | 0                    | P33                  | P32                  | P31                  | P30  | FF03H   | 00H (output latch) | R/W |

|        |     |     |      |                      |                      |                      |                      |      |         |                    |     |

| P4     | P47 | P46 | P45  | P44                  | P43                  | P42                  | P41                  | P40  | FF04H   | 00H (output latch) | R/W |

|        |     |     |      |                      |                      |                      |                      |      |         |                    |     |

| P5     | P57 | P56 | P55  | P54                  | P53                  | P52                  | P51                  | P50  | FF05H   | 00H (output latch) | R/W |

|        |     |     |      |                      |                      |                      |                      |      |         |                    |     |

| P6     | P67 | P66 | P65  | P64                  | P63                  | P62                  | P61                  | P60  | FF06H   | 00H (output latch) | R/W |

|        |     |     |      |                      |                      |                      |                      |      |         |                    |     |

| P7     | P77 | P76 | P75  | P74                  | P73                  | P72                  | P71                  | P70  | FF07H   | 00H (output latch) | R/W |

|        |     |     |      |                      |                      |                      |                      |      |         |                    |     |

| P12    | 0   | 0   | 0    | P124 <sup>Note</sup> | P123 <sup>Note</sup> | P122 <sup>Note</sup> | P121 <sup>Note</sup> | P120 | FF0CH   | 00H (output latch) | R/W |

|        |     |     |      |                      |                      | -                    |                      |      | -       |                    |     |

| P13    | 0   | 0   | 0    | 0                    | 0                    | 0                    | 0                    | P130 | FF0DH   | 00H (output latch) | R/W |

|        |     |     |      |                      |                      |                      |                      |      |         |                    |     |

| P14    | 0   | 0   | P145 | P144                 | P143                 | P142                 | P141                 | P140 | FF0EH   | 00H (output latch) | R/W |

|        |     |     |      |                      |                      |                      |                      |      |         |                    |     |

## Figure 5-38. Format of Port Register (78K0/KF2)

| Pmn | m = 0 to 7, 12 to 14; n = 0 to 7     |                                 |  |  |  |  |

|-----|--------------------------------------|---------------------------------|--|--|--|--|

|     | Output data control (in output mode) | Input data read (in input mode) |  |  |  |  |

| 0   | Output 0                             | Input low level                 |  |  |  |  |

| 1   | Output 1                             | Input high level                |  |  |  |  |

Note "0" is always read from the output latch of P121 to P124 if the pin is in the external clock input mode.

| Remark | fx:      | X1 clock oscillation frequency                  |

|--------|----------|-------------------------------------------------|

|        | fвн:     | Internal high-speed oscillation clock frequency |

|        | fexclk:  | External main system clock frequency            |

|        | fхн:     | High-speed system clock frequency               |

|        | fxp:     | Main system clock frequency                     |

|        | fprs:    | Peripheral hardware clock frequency             |

|        | fcpu:    | CPU clock frequency                             |

|        | fхт:     | XT1 clock oscillation frequency                 |

|        | fexclks: | External subsystem clock frequency              |

|        | fsuв:    | Subsystem clock frequency                       |

|        | frL:     | Internal low-speed oscillation clock frequency  |

## 6.3 Registers Controlling Clock Generator

The following seven registers are used to control the clock generator.

- Clock operation mode select register (OSCCTL)

- Processor clock control register (PCC)

- Internal oscillation mode register (RCM)

- Main OSC control register (MOC)

- Main clock mode register (MCM)

- Oscillation stabilization time counter status register (OSTC)

- Oscillation stabilization time select register (OSTS)

## (1) Clock operation mode select register (OSCCTL)

This register selects the operation modes of the high-speed system and subsystem clocks, and the gain of the onchip oscillator.

OSCCTL can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

## (2) Processor clock control register (PCC)

This register is used to select the CPU clock, the division ratio, and operation mode for subsystem clock. PCC is set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets PCC to 01H.

| Address: FF | FBH After | reset: 01H     | R/W  |                    |        |                 |         |      |

|-------------|-----------|----------------|------|--------------------|--------|-----------------|---------|------|

| Symbol      | 7         | 6              | 5    | 4                  | 3      | 2               | 1       | 0    |

| PCC         | 0         | 0              | 0    | 0                  | 0      | PCC2            | PCC1    | PCC0 |

|             |           |                |      | 1                  |        |                 |         |      |

|             | PCC2      | PCC1           | PCC0 |                    | CPU o  | clock (fcpu) se | lection |      |

|             | 0         | 0              | 0    | fхр                |        |                 |         |      |

|             | 0         | 0              | 1    | fxp/2 (default     | t)     |                 |         |      |

|             | 0         | 1              | 0    | fxp/2 <sup>2</sup> |        |                 |         |      |

|             | 0         | 1              | 1    | fxp/2 <sup>3</sup> |        |                 |         |      |

|             | 1         | 0              | 0    | fxp/2 <sup>4</sup> |        |                 |         |      |

|             | 0         | ther than abov | /e   | Setting proh       | ibited |                 |         |      |

## Figure 6-5. Format of Processor Clock Control Register (PCC) (78K0/KB2)

## Cautions 1. Be sure to clear bits 3 to 7 to 0.

2. The peripheral hardware clock (fprs) is not divided when the division ratio of the PCC is set.

Remark fxp: Main system clock oscillation frequency

## Figure 7-11. Format of 16-Bit Timer Output Control Register 00 (TOC00)

| Address: F | FBDH Afte  | r reset: 00H                                         | R/W          |               |                 |                 |               |          |

|------------|------------|------------------------------------------------------|--------------|---------------|-----------------|-----------------|---------------|----------|

| Symbol     | 7          | <6>                                                  | <5>          | 4             | <3>             | <2>             | 1             | <0>      |

| TOC00      | 0          | OSPT00                                               | OSPE00       | TOC004        | LVS00           | LVR00           | TOC001        | TOE00    |

|            |            | _                                                    |              |               |                 |                 |               |          |

|            | OSPT00     |                                                      | (            | One-shot puls | e output trigge | er via software | e             |          |

|            | 0          |                                                      |              |               | -               |                 |               |          |

|            | 1          | One-shot pu                                          | Ilse output  |               |                 |                 |               |          |

|            | shot pulse | of this bit is alw<br>output mode.<br>1, TM00 is cle |              |               | not set this bi | t to 1 in a mo  | de other than | the one- |

|            |            |                                                      |              |               |                 |                 |               |          |

|            | OSPE00     |                                                      |              | One-shot puls | se output ope   | ration control  |               |          |

|            | 0          | Successive                                           | pulse output |               |                 |                 |               |          |

| OSPE00       | One-shot pulse output operation control                                                                                                                                                                         |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0            | Successive pulse output                                                                                                                                                                                         |  |  |  |

| 1            | 1 One-shot pulse output                                                                                                                                                                                         |  |  |  |

| TI000 pin va | ulse output operates correctly in the free-running timer mode or clear & start mode entered by<br>alid edge input.<br>ot pulse cannot be output in the clear & start mode entered upon a match between TM00 and |  |  |  |

| TOC004                        | TO00 output control on match between CR010 and TM00                |  |  |

|-------------------------------|--------------------------------------------------------------------|--|--|

| 0                             | Disables inversion operation                                       |  |  |

| 1 Enables inversion operation |                                                                    |  |  |

| The interrup                  | The interrupt signal (INTTM010) is generated even when TOC004 = 0. |  |  |

| LVS00 | LVR00                                                                                                                                                                         | Setting of TO00 output status                                            |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--|--|

| 0     | 0                                                                                                                                                                             | No change                                                                |  |  |

| 0     | 1                                                                                                                                                                             | Initial value of TO00 output is low level (TO00 output is cleared to 0). |  |  |

| 1     | 0                                                                                                                                                                             | Initial value of TO00 output is high level (TO00 output is set to 1).    |  |  |

| 1     | 1                                                                                                                                                                             | Setting prohibited                                                       |  |  |

|       | <ul> <li>LVS00 and LVR00 can be used to set the initial value of the TO00 output level. If the initial value does not have to be set, leave LVS00 and LVR00 as 00.</li> </ul> |                                                                          |  |  |

• Be sure to set LVS00 and LVR00 when TOE00 = 1.

LVS00, LVR00, and TOE00 being simultaneously set to 1 is prohibited.

• LVS00 and LVR00 are trigger bits. By setting these bits to 1, the initial value of the TO00 output level can be set. Even if these bits are cleared to 0, TO00 output is not affected.

• The values of LVS00 and LVR00 are always 0 when they are read.

• For how to set LVS00 and LVR00, see 7.5.2 Setting LVS0n and LVR0n.

The actual TO00/TI010/P01 pin output is determined depending on PM01 and P01, besides TO00 output.

| TOC001                         | TO00 output control on match between CR000 and TM00                |  |  |

|--------------------------------|--------------------------------------------------------------------|--|--|

| 0 Disables inversion operation |                                                                    |  |  |

| 1                              | 1 Enables inversion operation                                      |  |  |

| The interrup                   | The interrupt signal (INTTM000) is generated even when TOC001 = 0. |  |  |

| TOE00 | TO00 output control                              |

|-------|--------------------------------------------------|

| 0     | Disables output (TO00 output fixed to low level) |

| 1     | Enables output                                   |

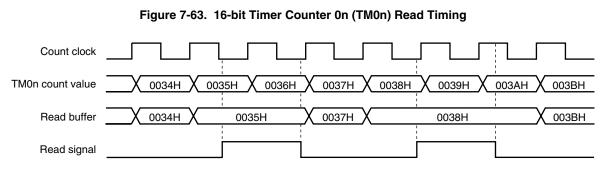

## (12) Reading of 16-bit timer counter 0n (TM0n)

TMOn can be read without stopping the actual counter, because the count values captured to the buffer are fixed when it is read. The buffer, however, may not be updated when it is read immediately before the counter counts up, because the buffer is updated at the timing the counter counts up.

**Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

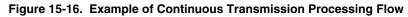

Remark

TXB6:

Transmit buffer register 6

ASIF6:

Asynchronous serial interface transmission status register 6

TXBF6:

Bit 1 of ASIF6 (transmit buffer data flag)

TXSF6:

Bit 0 of ASIF6 (transmit shift register data flag)

## (c) Switching MSB/LSB as start bit

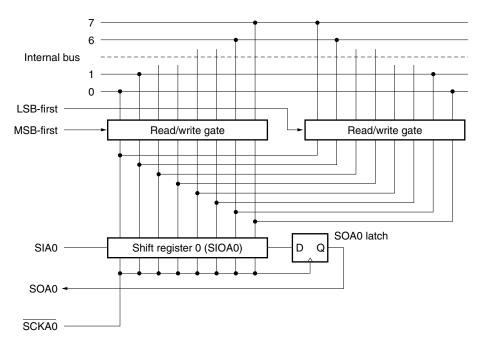

Figure 17-12 shows the configuration of serial I/O shift register 0 (SIOA0) and the internal bus. As shown in the figure, MSB/LSB can be read/written in reverse form.

Switching MSB/LSB as the start bit can be specified using bit 1 (DIR0) of serial operation mode specification register 0 (CSIMA0).

Figure 17-12. Transfer Bit Order Switching Circuit

Start bit switching is realized by switching the bit order for data written to SIOA0. The SIOA0 shift order remains unchanged.

Thus, switching between MSB-first and LSB-first must be performed before writing data to the shift register.

## (d) Communication start

Serial communication is started by setting communication data to serial I/O shift register 0 (SIOA0) when the following two conditions are satisfied.

- Serial interface CSIA0 operation control bit (CSIAE0) = 1

- Serial communication is not in progress

Caution If CSIAE0 is set to 1 after data is written to SIOA0, communication does not start.

Upon termination of 8-bit communication, serial communication automatically stops and the interrupt request flag (ACSIIF) is set.

<R>

## Figure 18-5. Format of IIC Control Register 0 (IICC0) (4/4)

| SPT0                                 |                                                                          | Stop condition trigger                                                                                                                                                                                                                                        |                                                                                     |  |  |  |  |  |

|--------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|--|--|--|--|

| 0                                    | Stop condition                                                           | Stop condition is not generated.                                                                                                                                                                                                                              |                                                                                     |  |  |  |  |  |

| 1                                    | 1 Stop condition is generated (termination of master device's transfer). |                                                                                                                                                                                                                                                               |                                                                                     |  |  |  |  |  |

| Cautions c                           | oncerning set tin                                                        | ning                                                                                                                                                                                                                                                          |                                                                                     |  |  |  |  |  |

| • For mast                           | er reception:                                                            | Cannot be set to 1 during transfer.                                                                                                                                                                                                                           |                                                                                     |  |  |  |  |  |

|                                      |                                                                          | Can be set to 1 only in the waiting period when ACKE0 notified of final reception.                                                                                                                                                                            | has been cleared to 0 and slave has been                                            |  |  |  |  |  |

| <ul> <li>For mast</li> </ul>         | er transmission:                                                         | A stop condition cannot be generated normally during to<br>during the wait period that follows output of the ninth cle                                                                                                                                        | <b>0</b> 1                                                                          |  |  |  |  |  |

| <ul> <li>Cannot b</li> </ul>         | e set to 1 at the                                                        | same time as start condition trigger (STT0).                                                                                                                                                                                                                  |                                                                                     |  |  |  |  |  |

| SPT0 bit                             | can be set to 1 c                                                        | only when in master mode.                                                                                                                                                                                                                                     |                                                                                     |  |  |  |  |  |

| a stop co<br>during the<br>the outpu | ndition will be ge<br>e wait period folle<br>It of the ninth clo         | leared to 0, if SPT0 bit is set to 1 during the wait period to<br>enerated during the high-level period of the ninth clock. Nowing the output of eight clocks, and SPT0 bit should be<br>ck.<br>then setting it again before it is cleared to 0 is prohibited | WTIM0 should be changed from 0 to 1<br>set to 1 during the wait period that follows |  |  |  |  |  |

| Condition f                          | Condition for clearing (SPT0 = 0) Condition for setting (SPT0 = 1)       |                                                                                                                                                                                                                                                               |                                                                                     |  |  |  |  |  |

| Cleared I                            | by loss in arbitrat                                                      | ion                                                                                                                                                                                                                                                           | Set by instruction                                                                  |  |  |  |  |  |

| <ul> <li>Automati</li> </ul>         | cally cleared afte                                                       | r stop condition is detected                                                                                                                                                                                                                                  | -                                                                                   |  |  |  |  |  |

| Cleared b                            | by LREL0 = 1 (ex                                                         | kit from communications)                                                                                                                                                                                                                                      |                                                                                     |  |  |  |  |  |

| When IIC                             | E0 = 0 (operatio                                                         | n stop)                                                                                                                                                                                                                                                       |                                                                                     |  |  |  |  |  |

| <ul> <li>Reset</li> </ul>            |                                                                          |                                                                                                                                                                                                                                                               |                                                                                     |  |  |  |  |  |

Caution When bit 3 (TRC0) of the IIC status register 0 (IICS0) is set to 1 (transmission status), bit 5 (WREL0) of the IICC0 register is set to 1 during the ninth clock and wait is canceled, after which the TRC0 bit is cleared (reception status) and the SDA0 line is set to high impedance. Release the wait performed while the TRC bit is 1 (transmission status) by writing to the IIC shift register.

Remark Bit 0 (SPT0) becomes 0 when it is read after data setting.

## 18.5 I<sup>2</sup>C Bus Definitions and Control Methods

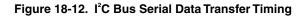

The following section describes the  $l^2C$  bus's serial data communication format and the signals used by the  $l^2C$  bus. Figure 18-12 shows the transfer timing for the "start condition", "address", "data", and "stop condition" output via the  $l^2C$  bus's serial data bus.

The master device generates the start condition, slave address, and stop condition.

The acknowledge (ACK) can be generated by either the master or slave device (normally, it is output by the device that receives 8-bit data).

The serial clock (SCL0) is continuously output by the master device. However, in the slave device, the SCL0's low level period can be extended and a wait can be inserted.

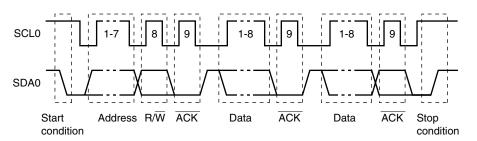

#### 18.5.1 Start conditions

A start condition is met when the SCL0 pin is at high level and the SDA0 pin changes from high level to low level. The start conditions for the SCL0 pin and SDA0 pin are signals that the master device generates to the slave device when starting a serial transfer. When the device is used as a slave, start conditions can be detected.

#### Figure 18-13. Start Conditions

A start condition is output when bit 1 (STT0) of IIC control register 0 (IICC0) is set (to 1) after a stop condition has been detected (SPD0: Bit 0 = 1 in IIC status register 0 (IICS0)). When a start condition is detected, bit 1 (STD0) of IICS0 is set (to 1).

#### (1) Master operation in single-master system

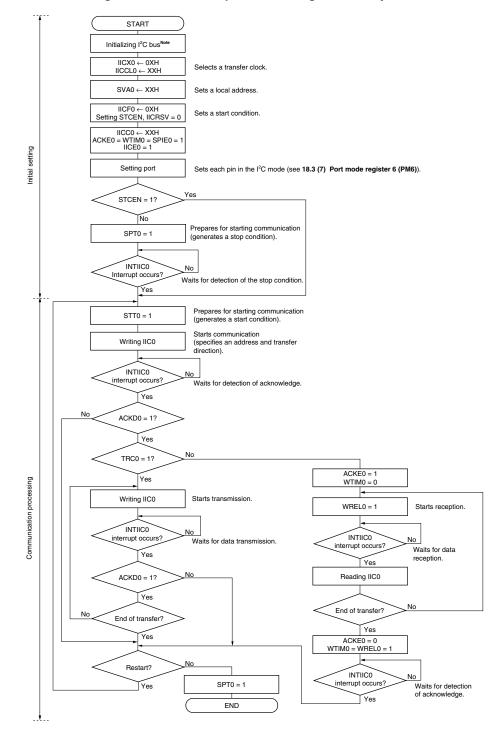

Figure 18-23. Master Operation in Single-Master System

- **Note** Release (SCL0 and SDA0 pins = high level) the  $l^2$ C bus in conformance with the specifications of the product that is communicating. If EEPROM is outputting a low level to the SDA0 pin, for example, set the SCL0 pin in the output port mode, and output a clock pulse from the output port until the SDA0 pin is constantly at high level.

- **Remark** Conform to the specifications of the product that is communicating, with respect to the transmission and reception formats.

## (ii) When WTIM0 = 1

| _          |       |          |         | I I    |              |     |          | T       |     |

|------------|-------|----------|---------|--------|--------------|-----|----------|---------|-----|

| S          | T AD  | 6 to AD0 | R/W     | ACK    | D7 to D0     | ACK | D7 to D0 | ACK     | SP  |

|            |       |          |         | ▲1 ▲   | .2           |     | 3        | <b></b> | 4 Z |

|            |       |          |         |        |              |     |          |         |     |

| ▲1         | IICS0 | = 0110;  | <010B   |        |              |     |          |         |     |

| ▲2         | IICS0 | = 0010;  | <110B   |        |              |     |          |         |     |

| <b>▲</b> 3 | IICS0 | = 0010;  | <100B   |        |              |     |          |         |     |

| <b>▲</b> 4 | IICSO | = 0010;  | <×00B   |        |              |     |          |         |     |

| ∆5         | IICSO | = 00000  | 0001B   |        |              |     |          |         |     |

|            |       |          |         |        |              |     |          |         |     |

| Re         | nark  | ▲: Alv   | vays g  | enerat | ed           |     |          |         |     |

|            |       | ∆: Ge    | nerate  | d only | when SPIE0 = | 1   |          |         |     |

|            |       | ×: Do    | n't car | е      |              |     |          |         |     |

|            |       |          |         |        |              |     |          |         |     |

## (6) Operation when arbitration loss occurs (no communication after arbitration loss)

When the device is used as a master in a multi-master system, read the MSTS0 bit each time interrupt request signal INTIIC0 has occurred to check the arbitration result.

## (a) When arbitration loss occurs during transmission of slave address data (when WTIM0 = 1)

## **18.6 Timing Charts**

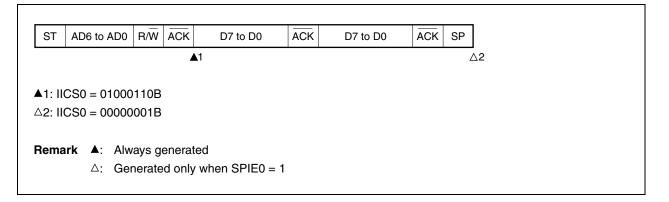

When using the l<sup>2</sup>C bus mode, the master device outputs an address via the serial bus to select one of several slave devices as its communication partner.

After outputting the slave address, the master device transmits the TRC0 bit (bit 3 of IIC status register 0 (IICS0)), which specifies the data transfer direction, and then starts serial communication with the slave device.

Figures 18-27 and 18-28 show timing charts of the data communication.

IIC shift register 0 (IIC0)'s shift operation is synchronized with the falling edge of the serial clock (SCL0). The transmit data is transferred to the SO0 latch and is output (MSB first) via the SDA0 pin.

Data input via the SDA0 pin is captured into IIC0 at the rising edge of SCL0.

#### (2) Interrupt mask flag registers (MK0L, MK0H, MK1L, MK1H)

The interrupt mask flags are used to enable/disable the corresponding maskable interrupt servicing.

MK0L, MK0H, MK1L, and MK1H are set by a 1-bit or 8-bit memory manipulation instruction. When MK0L and MK0H, and MK1L and MK1H are combined to form 16-bit registers MK0 and MK1, they are set by a 16-bit memory manipulation instruction.

Reset signal generation sets these registers to FFH.

#### Figure 20-7. Format of Interrupt Mask Flag Registers (MK0L, MK0H, MK1L, MK1H) (78K0/KB2)

| Address: FF | E4H After r | eset: FFH     | R/W            |         |                 |         |       |        |

|-------------|-------------|---------------|----------------|---------|-----------------|---------|-------|--------|

| Symbol      | <7>         | <6>           | <5>            | <4>     | <3>             | <2>     | <1>   | <0>    |

| MK0L        | SREMK6      | PMK5          | PMK4           | PMK3    | PMK2            | PMK1    | PMK0  | LVIMK  |

|             |             |               |                |         |                 |         |       |        |

| Address: FF | E5H After r | eset: FFH     | R/W            |         |                 |         |       |        |

| Symbol      | <7>         | <6>           | <5>            | <4>     | <3>             | <2>     | <1>   | <0>    |

| МКОН        | TMMK010     | TMMK000       | TMMK50         | TMMKH0  | TMMKH1          | DUALMK0 | STMK6 | SRMK6  |

|             |             |               |                |         |                 | CSIMK10 |       |        |

|             |             |               |                |         |                 | STMK0   |       |        |

|             |             |               |                |         |                 |         |       |        |

| Address: FF | E6H After r | eset: FFH     | R/W            |         |                 |         |       |        |

| Symbol      | 7           | 6             | 5              | 4       | <3>             | 2       | <1>   | <0>    |

| MK1L        | 1           | 1             | 1              | 1       | TMMK51          | 1       | SRMK0 | ADMK   |

|             |             |               |                |         |                 |         |       |        |

| Address: FF | E7H After r | eset: FFH     | R/W            |         |                 |         |       |        |

| Symbol      | 7           | 6             | 5              | 4       | 3               | 2       | 1     | <0>    |

| MK1H        | 1           | 1             | 1              | 1       | 1               | 1       | 1     | IICMK0 |

|             |             |               |                |         |                 |         |       |        |

|             | ХХМКХ       |               |                | Interru | upt servicing o | control |       |        |

|             | 0           | Interrupt ser | vicing enable  | b       |                 |         |       |        |

|             | 1           | Interrupt ser | vicing disable | d       |                 |         |       |        |

Caution Be sure to set bits 2, 4 to 7 of MK1L and bits 1 to 7 of MK1H to 1.

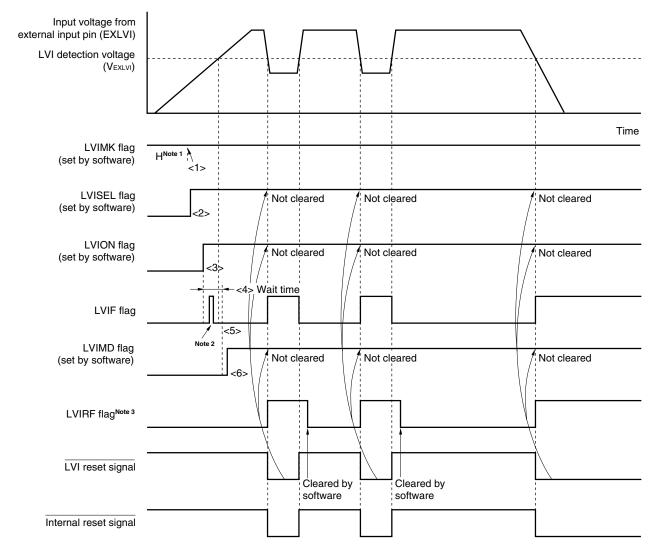

Figure 25-6. Timing of Low-Voltage Detector Internal Reset Signal Generation (Detects Level of Input Voltage from External Input Pin (EXLVI))

- Notes 1. The LVIMK flag is set to "1" by reset signal generation.

- 2. The LVIF flag may be set (1).

- 3. LVIRF is bit 0 of the reset control flag register (RESF). For details of RESF, see CHAPTER 23 RESET FUNCTION.

- Remark <1> to <6> in Figure 25-6 above correspond to <1> to <6> in the description of "When starting operation" in 25.4.1 (2) When detecting level of input voltage from external input pin (EXLVI).

## CHAPTER 27 FLASH MEMORY

The 78K0/Kx2 microcontrollers incorporates the flash memory to which a program can be written, erased, and overwritten while mounted on the board.

## 27.1 Internal Memory Size Switching Register

Select the internal memory capacity using the internal memory size switching register (IMS). IMS is set by an 8-bit memory manipulation instruction. Reset signal generation sets IMS to CFH.

RAM0

```

Caution Be sure to set each product to the values shown in Table 27-1 after a reset release.

```

#### Figure 27-1. Format of Internal Memory Size Switching Register (IMS)

4

0

Address:FFF0HAfter reset:CFHR/WSymbol765

RAM1

RAM2

IMS

| RAM2 | RAM1           | RAM0 | Internal high-speed RAM capacity selection |

|------|----------------|------|--------------------------------------------|

| 0    | 0              | 0    | 768 bytes                                  |

| 0    | 1              | 0    | 512 bytes                                  |

| 1    | 1              | 0    | 1024 bytes                                 |

| C    | Other than abo | ve   | Setting prohibited                         |

3

ROM3

2

ROM2

1

ROM1

0

ROM0

| ROM3 | ROM2     | ROM1     | ROM0 | Internal ROM capacity selection |

|------|----------|----------|------|---------------------------------|

| 0    | 0        | 1        | 0    | 8 KB                            |

| 0    | 1        | 0        | 0    | 16 KB                           |

| 0    | 1        | 1        | 0    | 24 KB                           |

| 1    | 0        | 0        | 0    | 32 KB                           |

| 1    | 1        | 0        | 0    | 48 KB                           |

| 1    | 1        | 1        | 1    | 60 KB                           |

|      | Other th | an above |      | Setting prohibited              |

## Caution To set the memory size, set IMS and then IXS. Set the memory size so that the internal ROM and internal expansion RAM areas do not overlap.

## (2) Non-port functions

| Port                          |                     | 78K0/KB2                                                                      |                 | 78K0/KC2      |                                      | 78K0/KD2   | 78K0/KE2                                                       | 78K0/KF2                                        |  |  |

|-------------------------------|---------------------|-------------------------------------------------------------------------------|-----------------|---------------|--------------------------------------|------------|----------------------------------------------------------------|-------------------------------------------------|--|--|

|                               |                     | 30/36 Pins                                                                    | 38 Pins         | 44 Pins       | 48 Pins                              | 52 Pins    | 64 Pins                                                        | 80 Pins                                         |  |  |

|                               | ver supply,<br>und  | Vdd, EVdd <sup>Note 1</sup> ,<br>Vss, EVss <sup>Note 1</sup> ,<br>AVref, AVss | VDD, AVREF, VSS | s, AVss       | Vdd, EVdd, Vss, EVss, AVref,<br>AVss |            |                                                                |                                                 |  |  |

| Reg                           | gulator             | REGC                                                                          |                 |               |                                      |            |                                                                |                                                 |  |  |

| Res                           | set                 | RESET                                                                         |                 |               |                                      |            |                                                                |                                                 |  |  |

| Clo<br>osc                    | ck<br>illation      | X1, X2,<br>EXCLK                                                              | X1, X2, XT1, X  | T2, EXCLK, EX | CLKS                                 |            |                                                                |                                                 |  |  |

|                               | ting to<br>h memory | FLMD0                                                                         |                 |               |                                      |            |                                                                |                                                 |  |  |

| Inte                          | errupt              | INTP0 to INTP                                                                 | 5               | •             | INTP0 to INTP                        | 6          | INTP0 to INTP3                                                 | 7                                               |  |  |

| Key                           | v interrupt         | -                                                                             | KR0, KR1        | KR0 to KR3    |                                      | KR0 to KR7 |                                                                |                                                 |  |  |

|                               | ТМ00                | TI000, TI010, T                                                               | ГО00            |               |                                      |            |                                                                |                                                 |  |  |

|                               | TM01                |                                                                               |                 | -             |                                      |            | TI001 <sup>Note 2</sup> , TI01                                 | 1 <sup>Note 2</sup> , TO01 <sup>Note 2</sup>    |  |  |

| Timer                         | TM50                | TI50, TO50                                                                    |                 |               |                                      |            |                                                                |                                                 |  |  |

| Ę                             | TM51                | TI51, TO51                                                                    |                 |               |                                      |            |                                                                |                                                 |  |  |

|                               | тмно                | TOH0                                                                          |                 |               |                                      |            |                                                                |                                                 |  |  |

|                               | TMH1                | TOH1                                                                          |                 |               |                                      |            |                                                                |                                                 |  |  |

|                               | UART0               | RxD0, TxD0                                                                    |                 |               |                                      |            |                                                                |                                                 |  |  |

|                               | UART6               | RxD6, TxD6                                                                    | RxD6, TxD6      |               |                                      |            |                                                                |                                                 |  |  |

| ce                            | IIC0                | SCL0, SDA0 SCL0, SDA0, EXSCL0                                                 |                 |               |                                      |            |                                                                |                                                 |  |  |

| iterfa                        | CSI10               | SCK10, SI10, S                                                                | SO10            |               |                                      |            |                                                                |                                                 |  |  |

| Serial interface              | CSI11               |                                                                               |                 | -             |                                      |            | SCK11 <sup>Note 2</sup> , SI1<br>SO11 <sup>Note 2</sup> , SSI1 | $\frac{1}{1}^{Note 2}$ , $\frac{1}{1}^{Note 2}$ |  |  |

| 0,                            | CSIA0               |                                                                               |                 |               | _                                    |            |                                                                | SCKAO, SIAO,<br>SOAO, BUSYO,<br>STBO            |  |  |

| A/D                           | converter           | ANI0 to ANI3                                                                  | ANI0 to ANI5    | ANI0 to ANI7  |                                      |            |                                                                |                                                 |  |  |

| Clo                           | ck output           |                                                                               | -               |               | PCL                                  |            | <u>.</u>                                                       |                                                 |  |  |

| Buz                           | zer output          |                                                                               |                 | -             |                                      |            | BUZ                                                            |                                                 |  |  |

| Low-voltage<br>detector (LVI) |                     | EXLVI                                                                         |                 |               |                                      |            |                                                                |                                                 |  |  |

Notes 1. This is not mounted onto 30-pin products.

2. This is not mounted onto the 78K0/KE2 products whose flash memory is less than 32 KB.

Caution The pins mounted depend on the product. Refer to Caution at the beginning of this chapter.

#### **AC Characteristics**

## (1) Basic operation (1/2)

$(T_A = -40 \text{ to } +125^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{DD} = \text{EV}_{DD} \le 5.5 \text{ V}, \text{AV}_{REF} \le \text{V}_{DD}, \text{V}_{SS} = \text{EV}_{SS} = \text{AV}_{SS} = 0 \text{ V})$

| Parameter                                              | Symbol          |                                                  | Condition                                                                | s                                                                                                                         | MIN.                  | TYP. | MAX.     | Unit     |

|--------------------------------------------------------|-----------------|--------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------|------|----------|----------|

| Instruction cycle (minimum instruction execution time) | Тсү             | Main<br>system<br>clock (fxp)<br>operation       | Conventional-<br>specification<br>Products<br>(µPD78F05xx                | $\frac{4.0 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}}{2.7 \text{ V} \le \text{V}_{\text{DD}} < 4.0 \text{ V}}$ | 0.1<br>0.2            |      | 32<br>32 | μs<br>μs |

|                                                        |                 |                                                  | (A2))<br>Expanded-<br>specification<br>Products<br>(µPD78F05xxA<br>(A2)) | $2.7 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V}$                                                              | 0.1                   |      | 32       | μs       |

|                                                        |                 | Subsystem                                        | n clock (fsuв) opera                                                     | tion <sup>Note 1</sup>                                                                                                    | 114                   | 122  | 125      | μS       |

| Peripheral hardware clock                              | fprs            | fprs = fxH                                       | Conventional-                                                            | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                                                                                     |                       |      | 20       | MHz      |

| frequency                                              |                 | (XSEL =<br>1)                                    | specification<br>Products<br>(µPD78F05xx<br>(A2))                        | $2.7~V \leq V_{\text{DD}} < 4.0~V$                                                                                        |                       |      | 10       | MHz      |

|                                                        |                 |                                                  | Expanded-                                                                | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                                                                                     |                       |      | 20       | MHz      |

|                                                        |                 |                                                  | specification<br>Products<br>(μPD78F05xxA<br>(A2))                       | $2.7~V \leq V_{DD} < 4.0~V$ Note 2                                                                                        |                       |      | 20       | MHz      |

|                                                        |                 | f <sub>PRS</sub> = f <sub>RH</sub><br>(XSEL = 0) |                                                                          | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$                                                                                     | 7.6                   |      | 8.4      | MHz      |

| External main system clock                             | fexclk          | Conventio                                        | nal-specification                                                        | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                                                                                     | 1.0 <sup>Note 3</sup> |      | 20.0     | MHz      |

| frequency                                              |                 | Products<br>(µPD78F0                             | 5xx(A2))                                                                 | $2.7~V \leq V_{\text{DD}} < 4.0~V$                                                                                        | 1.0 <sup>Note 3</sup> |      | 10.0     | MHz      |

|                                                        |                 | Expanded<br>Products<br>(µPD78F0                 | specification<br>5xxA(A2))                                               | $2.7~V \leq V_{DD} \leq 5.5~V$                                                                                            | 1.0 <sup>Note 3</sup> |      | 20.0     | MHz      |

| External main system clock input                       | texclкн,        | Convention                                       | nal-specification                                                        | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                                                                                     | 24                    |      |          | ns       |

| high-level width, low-level width                      | <b>t</b> exclkl | Products<br>(µPD78F05xx(A2))                     |                                                                          | $2.7~V \leq V_{\text{DD}} < 4.0~V$                                                                                        | 48                    |      |          | ns       |

|                                                        |                 | Expanded<br>Products<br>(µPD78F0                 | specification<br>5xxA(A2))                                               | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$                                                                                     | 24                    |      |          | ns       |

**Notes 1.** The 78K0/KB2 is not provided with a subsystem clock.

- 2. Characteristics of the main system clock frequency. Set the division clock to be set by a peripheral function to  $f_{XH/2}$  (10 MHz) or less. The multiplier/divider, however, can operate on  $f_{XH}$  (20 MHz).

- 3. 2.0 MHz (MIN.) when using UART6 during on-board programming.

## Table 35-1. Soldering Conditions of Conventional-specification Products (µPD78F05xx and 78F05xxD) (3/3)

| (3) | 30-pin plastic SSOP (7.62 mm (300))                                         |

|-----|-----------------------------------------------------------------------------|

|     | $\mu$ PD78F050xMC(A)-CAB-AX (x = 0 to 3), 78F050xMC(A2)-CAB-AX (x = 0 to 3) |

|     | 44-pin plastic LQFP (10x10)                                                 |

|     | $\mu$ PD78F051xGB(A)-GAF-AX (x = 1 to 3), 78F051xGB(A2)-GAF-AX (x = 1 to 3) |

|     | 52-pin plastic LQFP (10x10)                                                 |

|     | $\mu$ PD78F052xGB(A)-GAG-AX (x = 1 to 7), 78F052xGB(A2)-GAG-AX (x = 1 to 7) |

|     | 64-pin plastic LQFP (14x14)                                                 |

|     | $\mu$ PD78F053xGC(A)-GAL-AX (x = 1 to 7), 78F053xGC(A2)-GAL-AX (x = 1 to 7) |

|     | 64-pin plastic LQFP (12x12)                                                 |

|     | $\mu$ PD78F053xGK(A)-GAJ-AX (x = 1 to 7), 78F053xGK(A2)-GAJ-AX (x = 1 to 7) |

|     | 80-pin plastic LQFP (14x14)                                                 |

|     | $\mu$ PD78F054xGC(A)-GAD-AX (x = 4 to 7), 78F054xGC(A2)-GAD-AX (x = 4 to 7) |

| Soldering Method | Soldering Conditions                                                                                                                                                                                                                      | Recommended<br>Condition Symbol |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Infrared reflow  | Package peak temperature: 260°C, Time: 60 seconds max. (at 220°C or higher),<br>Count: 3 times or less, Exposure limit: 7 days <sup>№te</sup> (after that, prebake at 125°C for<br>20 to 72 hours)                                        | IR60-207-3                      |

| Wave soldering   | Solder bath temperature: 260°C max., Time: 10 seconds max., Count: Once,<br>Preheating temperature: 120°C max. (package surface temperature),<br>Exposure limit: 7 days <sup>Note</sup> (after that, prebake at 125°C for 20 to 72 hours) | WS60-207-1                      |

| Partial heating  | Pin temperature: 350°C max., Time: 3 seconds max. (per pin row)                                                                                                                                                                           | -                               |

Note After opening the dry pack, store it at 25°C or less and 65% RH or less for the allowable storage period.

Caution Do not use different soldering methods together (except for partial heating).

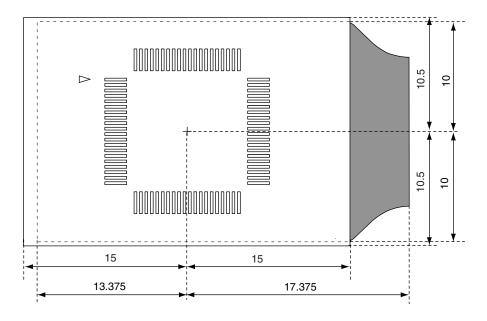

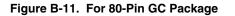

Figure B-10. For 64-Pin GK Package

Exchange adapter area: Components up to 17.45 mm in height can be mounted<sup>Note</sup>

Emulation probe tip area: Components up to 24.45 mm in height can be mounted<sup>Note</sup>

Note Height can be adjusted by using space adapters (each adds 2.4 mm)

Exchange adapter area: Components up to 17.45 mm in height can be mounted<sup>Note</sup>

Emulation probe tip area: Components up to 24.45 mm in height can be mounted<sup>Note</sup>

Note Height can be adjusted by using space adapters (each adds 2.4 mm)