Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | 78K/0                                                                                 |

| Core Size                  | 8-Bit                                                                                 |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                                    |

| Number of I/O              | 55                                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 1K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 8x10b                                                                             |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 64-TQFP                                                                               |

| Supplier Device Package    | -                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0533aga-hab-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.8 Outline of Functions

|           |                                                                          | 15         |                                                                                  |           |          |                                        |                               |                       |             |           |          |             | (1,     |

|-----------|--------------------------------------------------------------------------|------------|----------------------------------------------------------------------------------|-----------|----------|----------------------------------------|-------------------------------|-----------------------|-------------|-----------|----------|-------------|---------|

|           | 78K0/Kx2                                                                 | 78K0/KB2   |                                                                                  |           |          |                                        | 78K0/KC2                      |                       |             |           |          |             |         |

| Item      |                                                                          | 30/36 Pins |                                                                                  |           |          |                                        | 8/44 Pin                      | S                     | 48 Pins     |           |          |             |         |

| Flas      | h memory (KB)                                                            | 8          | 16                                                                               | 24        | 32       | 16                                     | 24                            | 32                    | 16          | 24        | 32       | 48          | 60      |

| High      | n-Speed RAM (KB)                                                         | 0.5        | 0.75                                                                             | 1         | 1        | 0.75                                   | 1                             | 1                     | 0.75        | 1         | 1        | 1           | 1       |

| Ехра      | ansion RAM (KB)                                                          | _          | _                                                                                | _         | _        | _                                      | _                             | -                     | -           | _         | _        | 1           | 2       |

| Ban       | k (flash memory)                                                         |            |                                                                                  |           |          |                                        | -                             | _                     |             |           |          |             |         |

| Pow       | er supply voltage                                                        | Standa     | ard produ                                                                        | ucts, (A) | grade pr | oducts: \                              | /DD = 1.8                     | to 5.5 V              | ′, (A2) gra | ade prod  | ucts: V  | oo = 2.7 to | o 5.5 \ |

| Reg       | ulator                                                                   | Provided   |                                                                                  |           |          |                                        |                               |                       |             |           |          |             |         |

|           | mum instruction<br>cution time                                           |            | 0.1                                                                              |           |          | o = 2.7 to                             |                               |                       |             |           |          | Note 1      |         |

|           | - High-speed system                                                      |            | 20 MHz: $V_{DD}$ = 2.7 to 5.5 V/5 MHz: $V_{DD}$ = 1.8 to 5.5 V <sup>Note 1</sup> |           |          |                                        |                               |                       |             |           |          |             |         |

| ş         | Internal high-speed8 MHz (TYP.): VDD = 1oscillation8 MHz (TYP.): VDD = 1 |            |                                                                                  |           |          |                                        | ) = 1.8 to                    | 5.5 V <sup>Note</sup> | e 1         |           |          |             |         |

| Clock     | Subsystem                                                                |            | -                                                                                | -         |          |                                        | 32.7                          | 768 kHz               | (TYP.): V   | /DD = 1.8 | to 5.5 V | Note 1      |         |

|           | Internal low-speed oscillation                                           |            | 240 kHz (TYP.): V <sub>DD</sub> = 1.8 to 5.5 V <sup>Note 1</sup>                 |           |          |                                        |                               |                       |             |           |          |             |         |

| гоц       | Total                                                                    | 23         |                                                                                  |           |          |                                        | 31 (38 pins)/<br>37 (44 pins) |                       |             |           | 41       |             |         |

|           | N-ch O.D. (6 V tolerance)                                                |            | 2                                                                                | 2         |          |                                        | 4                             |                       | 4           |           |          |             |         |

|           | 16 bits (TM0)                                                            |            | 1 ch                                                                             |           |          |                                        |                               |                       |             |           |          |             |         |

|           | 8 bits (TM5)                                                             | 2 ch       |                                                                                  |           |          |                                        |                               |                       |             |           |          |             |         |

| IImer     | 8 bits (TMH)                                                             |            |                                                                                  |           |          |                                        | 2                             | ch                    |             |           |          |             |         |

| - [       | Watch                                                                    |            | – 1 ch                                                                           |           |          |                                        |                               |                       |             |           |          |             |         |

| Ē         | WDT                                                                      |            | 1 ch                                                                             |           |          |                                        |                               |                       |             |           |          |             |         |

| 1         | 3-wire CSI                                                               |            |                                                                                  |           |          |                                        |                               |                       |             |           |          |             |         |

| <u> </u>  | Automatic transmit/<br>receive 3-wire CSI                                |            |                                                                                  |           |          |                                        | -                             | _                     |             |           |          |             |         |

|           | UART/3-wire CSI <sup>Note 2</sup>                                        |            | 1 ch                                                                             |           |          |                                        |                               |                       |             |           |          |             |         |

| erie      | UART supporting LIN-bus                                                  |            | 1 ch                                                                             |           |          |                                        |                               |                       |             |           |          |             |         |

|           | I <sup>2</sup> C bus                                                     |            |                                                                                  |           |          |                                        | 1                             | ch                    |             |           |          |             |         |

| 10-b      | it A/D                                                                   | D 4 ch     |                                                                                  |           |          | h (38 pin<br>h (44 pir                 |                               | 8 ch                  |             |           |          |             |         |

| tdr       | External                                                                 |            | 6                                                                                | 6         |          | 7                                      |                               |                       | 8           |           |          |             |         |

| Interrupt | Internal                                                                 |            | 14                                                                               | 4         |          | 16                                     |                               |                       |             |           |          |             |         |

| Key       | interrupt                                                                |            |                                                                                  | _         |          | 2 ch (38 pins)/ 4 ch<br>4 ch (44 pins) |                               |                       |             |           |          |             |         |

|           | RESET pin                                                                |            |                                                                                  |           |          |                                        | Prov                          | vided                 |             |           |          |             |         |

| set       | POC                                                                      |            |                                                                                  |           |          |                                        | 1.59 V                        | ±0.15 V               |             |           |          |             |         |

| Heset     | LVI                                                                      |            |                                                                                  | Т         | he deteo | ction leve                             | l of the s                    | upply vo              | Itage is s  | electable | е.       |             |         |

| _         | WDT                                                                      |            |                                                                                  |           |          | -                                      |                               | vided                 | <u> </u>    |           |          |             |         |

|           | k output/buzzer output                                                   |            |                                                                                  |           | _        |                                        |                               |                       |             | Cloc      | k output | only        |         |

|           | iplier/divider                                                           |            |                                                                                  |           |          | -                                      | _                             |                       |             |           |          | · · ·       | vided   |

|           | chip debug function                                                      | μPD7       | 8F0503E<br>on                                                                    |           | 03DA     |                                        | )78F051<br>)513DA             |                       | μPD         | 78F051    | 5D, 78F0 | 0515DA o    |         |

| <b></b>   | ating ambient temperature                                                | Standa     |                                                                                  |           | rade pro | oducts: T                              |                               | ,                     | , (A2) ara  | ade prod  | ucts: TA | = -40 to    | +125°   |

Notes 1. This is applicable to a standard expanded-specification product (μPD78F05xxA and 78F05xxDA). See CHAPTER 30 ELECTRICAL SPECIFICATIONS (STANDARD PRODUCTS) to CHAPTER 33 ELECTRICAL SPECIFICATIONS ((A2) GRADE PRODUCTS: TA: -40 to +125°C) for products with other specifications and grades.

2. Select either of the functions of these alternate-function pins.

Table 2-3. Pin I/O Circuit Types (3/3)

|         | Pin Name             | I/O Circuit Type | I/O   | Recommended Connection of Unused Pins                                                                   |

|---------|----------------------|------------------|-------|---------------------------------------------------------------------------------------------------------|

|         | P140/PCL/INTP6       | 5-AQ             | I/O   | Input: Independently connect to EVDD or EVSS via a resistor.                                            |

|         | P141/BUZ/BUSY0/INTP7 |                  |       | Output: Leave open.                                                                                     |

|         | P142/SCKA0           |                  |       |                                                                                                         |

|         | P143/SIA0            |                  |       |                                                                                                         |

|         | P144/SOA0            | 5-AG             |       |                                                                                                         |

|         | P145/STB0            |                  |       |                                                                                                         |

| <r></r> | AVREF                | _                | _     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                   |

| <r></r> | AVss                 | -                | -     | Make this pin the same potential as the EV $_{\mbox{\scriptsize SS}}$ and V $_{\mbox{\scriptsize SS}}.$ |

|         | FLMD0                | 38-A             | -     | Connect to EVss or Vss <sup>Note</sup> .                                                                |

| <r></r> | RESET                | 2                | Input | Connect directly to EVDD or via a resistor.                                                             |

| <r></r> | REGC                 | -                | -     | Connect to Vss via capacitor (0.47 to 1 $\mu$ F).                                                       |

**Note** FLMD0 is a pin that is used to write data to the flash memory. To rewrite the data of the flash memory on-board, connect this pin to EVss or Vss via a resistor (10 kΩ: recommended). The same applies when executing on-chip debugging with a product with an on-chip debug function (*μ*PD78F05xxD and 78F05xxDA).

**Remark** With products not provided with an EVDD or EVss pin, replace EVDD with VDD, or replace EVss with Vss.

| Memory Bank Number | CPU Address                     | Flash Memory Real Address | Address Representation in Simulator and Debugger <sup>Note 1</sup> |

|--------------------|---------------------------------|---------------------------|--------------------------------------------------------------------|

| Memory bank 0      | 08000H-0BFFFH <sup>Note 2</sup> | 08000H-0BFFFH             | 08000H-0BFFFH                                                      |

| Memory bank 1      |                                 | 0C000H-0FFFFH             | 18000H-1BFFFH                                                      |

| Memory bank 2      |                                 | 10000H-13FFFH             | 28000H-2BFFFH                                                      |

| Memory bank 3      |                                 | 14000H-17FFFH             | 38000H-3BFFFH                                                      |

| Memory bank 4      |                                 | 18000H-1BFFFH             | 48000H-4BFFFH                                                      |

| Memory bank 5      |                                 | 1C000H-1FFFFH             | 58000H-5BFFFH                                                      |

Table 4-1. Memory Bank Address Representation

Notes 1. SM+ for 78K0, SM+ for 78K0/Kx2, and ID78K0-QB

2. Set the memory bank to be used by the memory bank select register (BANK) (see Figure 4-3).

For details, see the RA78K0 Ver. 3.80 Assembler Package Operation User's Manual (U17199E) and the 78K0 Microcontrollers Self Programming Library Type01 User's Manual (U18274E).

# 4.3 Memory Bank Select Register (BANK)

The memory bank select register (BANK) is used to select a memory bank to be used.

BANK can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears BANK to 00H.

#### Figure 4-3. Format of Memory Bank Select Register (BANK)

Address: FFF3H After reset: 00H R/W

| Symbol | 7 | 6 | 5 | 4 | 3 | 2     | 1     | 0     |

|--------|---|---|---|---|---|-------|-------|-------|

| BANK   | 0 | 0 | 0 | 0 | 0 | BANK2 | BANK1 | BANK0 |

| BANK2 | BANK1         | BANK0 | Banks                                       | setting                                          |  |  |  |  |

|-------|---------------|-------|---------------------------------------------|--------------------------------------------------|--|--|--|--|

|       |               |       | μPD78F05x6 and 78F05x6A                     | µPD78F05x7, 78F05x7A,<br>78F05x7D, and 78F05x7DA |  |  |  |  |

| 0     | 0             | 0     | Common area (32 KB) + memo                  | ry bank 0 (16 KB)                                |  |  |  |  |

| 0     | 0             | 1     | Common area (32 KB) + memory bank 1 (16 KB) |                                                  |  |  |  |  |

| 0     | 1             | 0     | Common area (32 KB) + memory bank 2 (16 KB) |                                                  |  |  |  |  |

| 0     | 1             | 1     | Common area (32 KB) + memory bank 3 (16 KB) |                                                  |  |  |  |  |

| 1     | 0             | 0     | Setting prohibited                          | Common area (32 KB) +<br>memory bank 4 (16 KB)   |  |  |  |  |

| 1     | 0             | 1     |                                             | Common area (32 KB) +<br>memory bank 5 (16 KB)   |  |  |  |  |

| 0     | ther than abo | ve    | Setting prohibited                          | Setting prohibited                               |  |  |  |  |

Caution Be sure to change the value of the BANK register in the common area (0000H to 7FFFH). If the value of the BANK register is changed in the bank area (8000H to BFFFH), an inadvertent program loop occurs in the CPU. Therefore, never change the value of the BANK register in the bank area.

**Remark** x = 2 to 4

Г

• Software example (to store a value to be referenced in register A)

| RAMD<br>R_BNKA:<br>R_BNKN:<br>R_BNKRN: |                                                                                     | SADDR<br>2<br>1<br>1                                                                                                     | ; Secures RAM for specifying an address at the reference destination.<br>; Secures RAM for specifying a memory bank number at the reference destination.<br>; Secures RAM for saving a memory bank number at the reference source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ETRC<br>ENTRY:                         | CSEG                                                                                | UNIT                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                        | MOV<br>MOVW<br>CALL                                                                 | R_BNKN,#BANKNUM DATA1<br>R_BNKA,#DATA1<br>!BNKRD<br>:<br>:                                                               | ; Stores the memory bank number at the reference destination.<br>; Stores the address at the reference destination.<br>; Calls a subroutine for referencing between memory banks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| BNKC                                   | CSEG                                                                                | AT 7000H                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| BNKRD:                                 | PUSH<br>MOV<br>XCH<br>MOV<br>XCHW<br>MOV<br>XCHW<br>MOV<br>XCH<br>MOV<br>POP<br>RET | HL<br>A,R_BNKN<br>A,BANK<br>R_BNKRN,A<br>AX,HL<br>AX,R_BNKA<br>AX,HL<br>A,[HL]<br>A,R_BNKRN<br>BANK,A<br>A,R_BNKRN<br>HL | <ul> <li>; Subroutine for referencing between memory banks.</li> <li>; Saves the contents of the HL register.</li> <li>; Acquires the memory bank number at the reference destination.</li> <li>; Swaps the memory bank number at the reference source for that at the reference destination</li> <li>; Saves the memory bank number at the reference source.</li> <li>; Saves the contents of the X register.</li> <li>; Acquires the address at the reference destination.</li> <li>; Specifies the address at the reference destination.</li> <li>; Reads the target value.</li> <li>; Acquires the memory bank number at the reference source.</li> <li>; Specifies the memory bank number at the reference source.</li> <li>; Specifies the memory bank number at the reference source.</li> <li>; Specifies the memory bank number at the reference source.</li> <li>; Specifies the contents of the HL register.</li> <li>; Restores the contents of the HL register.</li> </ul> |

| Data<br>Data1:                         | CSEG<br>DB                                                                          | BANK3<br>0AAH                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| END                                    |                                                                                     |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

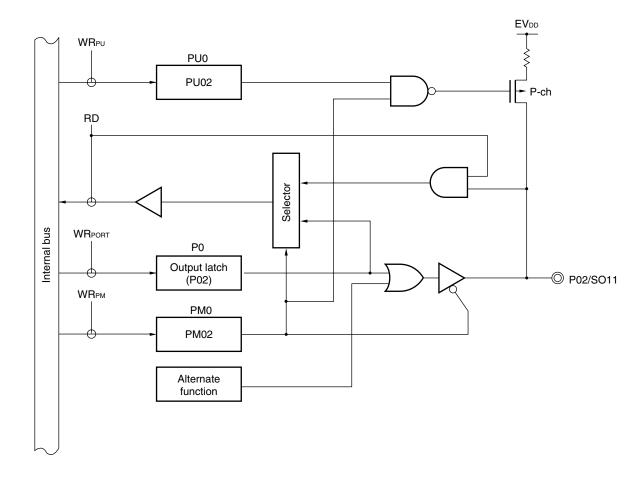

Figure 5-3. Block Diagram of P02 (2/2)

#### (2) 78K0/KE2 products whose flash memory is at least 48 KB and 78K0/KF2

- P0: Port register 0

- PU0: Pull-up resistor option register 0

- PM0: Port mode register 0

- RD: Read signal

- WR××: Write signal

**Remark** With products not provided with an EVDD or EVss pin, replace EVDD with VDD, or replace EVss with Vss.

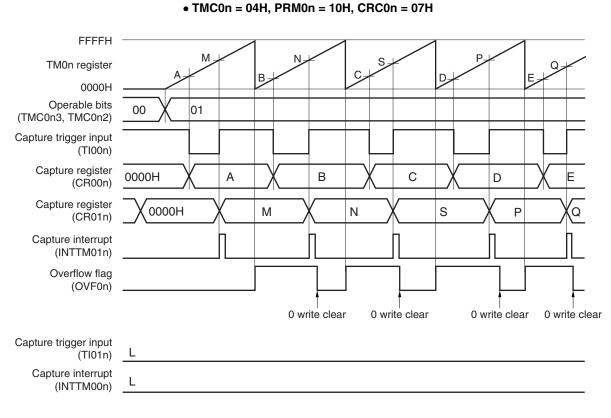

#### (2) Measuring the pulse width by using one input signal of the TI00n pin (free-running timer mode)

Set the free-running timer mode (TMC0n3 and TMC0n2 = 01). The count value of TM0n is captured to CR00n in the phase reverse to the valid edge detected on the Tl00n pin. When the valid edge of the Tl00n pin is detected, the count value of TM0n is captured to CR01n.

By this measurement method, values are stored in separate capture registers when a width from one edge to another is measured. Therefore, the capture values do not have to be saved. By subtracting the value of one capture register from that of another, a high-level width, low-level width, and cycle are calculated.

If an overflow occurs, the value becomes negative if one captured value is simply subtracted from another and, therefore, a borrow occurs (bit 0 (CY) of the program status word (PSW) is set to 1). If this happens, ignore CY and take the calculated value as the pulse width. In addition, clear bit 0 (OVF0n) of 16-bit timer mode control register 0n (TMC0n) to 0.

Figure 7-54. Timing Example of Pulse Width Measurement (2)

**Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

#### Caution Make sure POWER6 = 0 when rewriting TPS63 to TPS60.

Remarks 1. fprs: Peripheral hardware clock frequency

TMC506: Bit 6 of 8-bit timer mode control register 50 (TMC50) TMC501: Bit 1 of TMC50

#### (5) Baud rate generator control register 6 (BRGC6)

This register sets the division value of the 8-bit counter of serial interface UART6. BRGC6 can be set by an 8-bit memory manipulation instruction. Reset signal generation sets this register to FFH.

#### Figure 15-9. Format of Baud Rate Generator Control Register 6 (BRGC6)

Address: FF57H After reset: FFH R/W

Symbol BRGC6

|                                                    | bol | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|----------------------------------------------------|-----|-------|-------|-------|-------|-------|-------|-------|-------|

| C6 MDL67 MDL66 MDL65 MDL64 MDL63 MDL62 MDL61 MDL60 | iC6 | MDL67 | MDL66 | MDL65 | MDL64 | MDL63 | MDL62 | MDL61 | MDL60 |

| MDL67 | MDL66 | MDL65 | MDL64 | MDL63 | MDL62 | MDL61 | MDL60 | k   | Output clock selection of<br>8-bit counter |

|-------|-------|-------|-------|-------|-------|-------|-------|-----|--------------------------------------------|

| 0     | 0     | 0     | 0     | 0     | 0     | ×     | ×     | ×   | Setting prohibited                         |

| 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 4   | fxclk6/4                                   |

| 0     | 0     | 0     | 0     | 0     | 1     | 0     | 1     | 5   | fxclk6/5                                   |

| 0     | 0     | 0     | 0     | 0     | 1     | 1     | 0     | 6   | fxclk6/6                                   |

| •     | •     | •     | •     | •     | •     | •     | •     | •   | •                                          |

| •     | •     | •     | •     | •     | •     | •     | •     | •   | •                                          |

| •     | •     | •     | •     | •     | •     | •     | •     | •   | •                                          |

| •     | •     | •     | •     | •     | •     | •     | •     | •   | •                                          |

| •     | •     | •     | •     | ٠     | ٠     | ٠     | •     | ٠   | •                                          |

| 1     | 1     | 1     | 1     | 1     | 1     | 0     | 0     | 252 | fxclк6/252                                 |

| 1     | 1     | 1     | 1     | 1     | 1     | 0     | 1     | 253 | fxclк6/253                                 |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 0     | 254 | fxclк6/254                                 |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 255 | fxclк6/255                                 |

- Cautions 1. Make sure that bit 6 (TXE6) and bit 5 (RXE6) of the ASIM6 register = 0 when rewriting the MDL67 to MDL60 bits.

- 2. The baud rate is the output clock of the 8-bit counter divided by 2.

Remarks 1. fxclk6: Frequency of base clock selected by the TPS63 to TPS60 bits of CKSR6 register

- **2.** k: Value set by MDL67 to MDL60 bits (k = 4, 5, 6, ..., 255)

- **3.**  $\times$ : Don't care

**Remark** BRGC6 can be refreshed (the same value is written) by software during a communication operation (when bits 7 and 6 (POWER6, TXE6) of ASIM6 = 1 or bits 7 and 5 (POWER6, RXE6) of ASIM6 = 1).

#### 15.4 Operation of Serial Interface UART6

Serial interface UART6 has the following two modes.

- Operation stop mode

- Asynchronous serial interface (UART) mode

#### 15.4.1 Operation stop mode

In this mode, serial communication cannot be executed; therefore, the power consumption can be reduced. In addition, the pins can be used as ordinary port pins in this mode. To set the operation stop mode, clear bits 7, 6, and 5 (POWER6, TXE6, and RXE6) of ASIM6 to 0.

#### (1) Register used

The operation stop mode is set by asynchronous serial interface operation mode register 6 (ASIM6). ASIM6 can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation sets this register to 01H.

Address: FF50H After reset: 01H R/W

| Symbol | <7>    | <6>  | <5>  | 4    | 3    | 2   | 1   | 0     |

|--------|--------|------|------|------|------|-----|-----|-------|

| ASIM6  | POWER6 | TXE6 | RXE6 | PS61 | PS60 | CL6 | SL6 | ISRM6 |

| POWER6              | Enables/disables operation of internal operation clock                                               |

|---------------------|------------------------------------------------------------------------------------------------------|

| 0 <sup>Note 1</sup> | Disables operation of the internal operation clock (fixes the clock to low level) and asynchronously |

|                     | resets the internal circuit <sup>Note 2</sup> .                                                      |

| TXE6 | Enables/disables transmission                                                    |

|------|----------------------------------------------------------------------------------|

| 0    | Disables transmission operation (synchronously resets the transmission circuit). |

| RXE6 | Enables/disables reception                                       |

|------|------------------------------------------------------------------|

| 0    | Disables reception (synchronously resets the reception circuit). |

- **Notes 1.** If POWER6 = 0 is set while transmitting data, the output of the TxD6 pin will be fixed to high level (if TXDLV6 = 0). Furthermore, the input from the RxD6 pin will be fixed to high level.

- 2. Asynchronous serial interface reception error status register 6 (ASIS6), asynchronous serial interface transmission status register 6 (ASIF6), bit 7 (SBRF6) and bit 6 (SBRT6) of asynchronous serial interface control register 6 (ASICL6), and receive buffer register 6 (RXB6) are reset.

- Caution Clear POWER6 to 0 after clearing TXE6 and RXE6 to 0 to stop the operation. To start the communication, set POWER6 to 1, and then set TXE6 or RXE6 to 1.

- Remark To use the RxD6/P14 and TxD6/P13 pins as general-purpose port pins, see CHAPTER 5 PORT FUNCTIONS.

#### (3) Serial trigger register 0 (CSIT0)

This is an 8-bit register used to control execution/stop of automatic data transfer between buffer RAM and serial I/O shift register 0 (SIOA0).

This register can be set by a 1-bit or 8-bit memory manipulation instruction. This register can be set when bit 6 (ATE0) of serial operation mode specification register 0 (CSIMA0) is 1. Reset signal generation clears this register to 00H.

#### Figure 17-4. Format of Serial Trigger Register 0 (CSIT0)

Address: FF92H After reset: 00H R/W

| Symbol | 7 | 6 | 5 | 4 | 3 | 2 | <1>    | <0>    |

|--------|---|---|---|---|---|---|--------|--------|

| CSIT0  | 0 | 0 | 0 | 0 | 0 | 0 | ATSTP0 | ATSTA0 |

| ATSTP0      | Automatic data transfer stop    |

|-------------|---------------------------------|

| 0           | -                               |

| 1           | Automatic data transfer stopped |

|             |                                 |

|             |                                 |

| ATSTA0      | Automatic data transfer start   |

| ATSTA0<br>0 |                                 |

- Cautions 1. Even if ATSTP0 or ATSTA0 is set to 1, automatic transfer cannot be started/stopped until 1-byte transfer is complete.

- 2. ATSTP0 and ATSTA0 change to 0 automatically after the interrupt signal INTACSI is generated.

- After automatic data transfer is stopped, the data address when the transfer stopped is stored in automatic data transfer address count register 0 (ADTC0). However, since no function to restart automatic data transfer is incorporated, when transfer is stopped by setting ATSTP0 = 1, start automatic data transfer by setting ATSTA0 to 1 after re-setting the registers.

#### Remarks 1. ×: don't care

- 2. fPRS: Peripheral hardware clock frequency

- **3**. fEXSCL0: External clock frequency from EXSCL0 pin

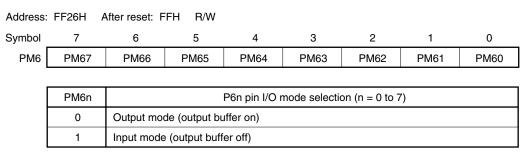

# (7) Port mode register 6 (PM6)

This register sets the input/output of port 6 in 1-bit units.

When using the P60/SCL0 pin as clock I/O and the P61/SDA0 pin as serial data I/O, clear PM60 and PM61, and the output latches of P60 and P61 to 0.

Set IICE0 (bit 7 of IIC control register 0 (IICC0)) to 1 before setting the output mode because the P60/SCL0 and P61/SDA0 pins output a low level (fixed) when IICE0 is 0.

PM6 is set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets PM6 to FFH.

Figure 18-10. Format of Port Mode Register 6 (PM6)

**Remark** The figure shown above presents the format of port mode register 6 of 78K0/KF2 products. For the format of port mode register 6 of other products, see (1) Port mode registers (PMxx) in 5.3 Registers Controlling Port Function.

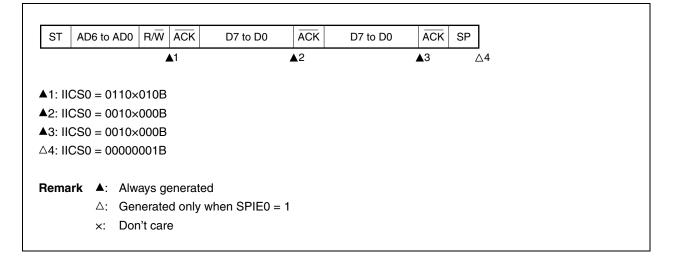

## (ii) When WTIM0 = 1

|                 |               |          | T T       |              |     |          |     |            |

|-----------------|---------------|----------|-----------|--------------|-----|----------|-----|------------|

| ST              | AD6 to A      | AD0 R/W  | ACK       | D7 to D0     | ĀCK | D7 to D0 | ĀCK | SP         |

|                 |               |          | ▲1        |              | ▲2  | 2        |     | <b>3</b> Z |

|                 |               |          |           |              |     |          |     |            |

| <b>▲</b> 1: II0 | CS0 = 01      | 101×110E | 3         |              |     |          |     |            |

| <b>▲</b> 2: II0 | CS0 = 00      | 001×100E | 3         |              |     |          |     |            |

| <b>▲</b> 3: II0 | CS0 = 00      | 001××00E | 3         |              |     |          |     |            |

| ∆4: II(         | CS0 = 00      | 000001E  | 3         |              |     |          |     |            |

|                 |               |          |           |              |     |          |     |            |

| Rema            | rk ▲:         | Always g | generated | k            |     |          |     |            |

|                 | $\triangle$ : | Generate | ed only w | /hen SPIE0 = | 1   |          |     |            |

|                 | ×:            | Don't ca | re        |              |     |          |     |            |

|                 |               |          |           |              |     |          |     |            |

#### (b) When arbitration loss occurs during transmission of extension code

#### (i) When WTIM0 = 0

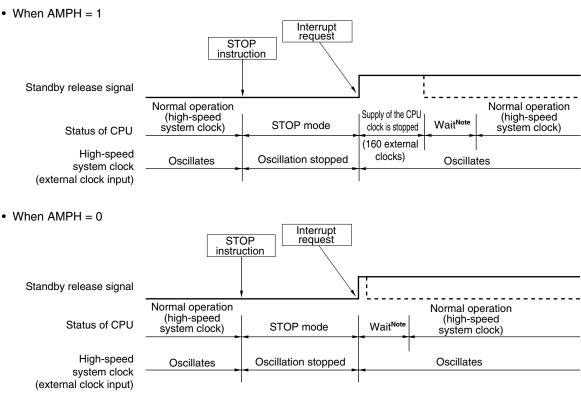

#### (1) When high-speed system clock (X1 oscillation) is used as CPU clock Interrupt request Wait STOP (set by OSTS) instruction Standby release signal Normal operation Normal operation Oscillation stabilization wait (high-speed (high-speed system clock) STOP mode (HALT mode status) system clock) Status of CPU High-speed Oscillates Oscillation stopped Oscillates system clock (X1 oscillation) Oscillation stabilization time (set by OSTS)

## Figure 22-6. STOP Mode Release by Interrupt Request Generation (1/2)

#### (2) When high-speed system clock (external clock input) is used as CPU clock

Note The wait time is as follows:

- When vectored interrupt servicing is carried out: 17 or 18 clocks

- When vectored interrupt servicing is not carried out: 11 or 12 clocks

- **Remark** The broken lines indicate the case when the interrupt request that has released the standby mode is acknowledged.

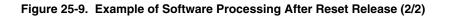

Checking reset source

# CHAPTER 29 INSTRUCTION SET

This chapter lists each instruction set of the 78K0/Kx2 microcontrollers in table form. For details of each operation and operation code, refer to the separate document **78K/0 Series Instructions User's Manual (U12326E)**.

#### 29.1 Conventions Used in Operation List

#### 29.1.1 Operand identifiers and specification methods

Operands are written in the "Operand" column of each instruction in accordance with the specification method of the instruction operand identifier (refer to the assembler specifications for details). When there are two or more methods, select one of them. Uppercase letters and the symbols #, !, \$ and [] are keywords and must be written as they are. Each symbol has the following meaning.

- #: Immediate data specification

- !: Absolute address specification

- \$: Relative address specification

- []: Indirect address specification

In the case of immediate data, describe an appropriate numeric value or a label. When using a label, be sure to write the #, !, \$, and [] symbols.

For operand register identifiers r and rp, either function names (X, A, C, etc.) or absolute names (names in parentheses in the table below, R0, R1, R2, etc.) can be used for specification.

| Identifier | Specification Method                                                                                 |

|------------|------------------------------------------------------------------------------------------------------|

| r          | X (R0), A (R1), C (R2), B (R3), E (R4), D (R5), L (R6), H (R7)                                       |

| rp         | AX (RP0), BC (RP1), DE (RP2), HL (RP3)                                                               |

| sfr        | Special function register symbol <sup>Note</sup>                                                     |

| sfrp       | Special function register symbol (16-bit manipulatable register even addresses only) <sup>Note</sup> |

| saddr      | FE20H to FF1FH Immediate data or labels                                                              |

| saddrp     | FE20H to FF1FH Immediate data or labels (even address only)                                          |

| addr16     | 0000H to FFFFH Immediate data or labels                                                              |

|            | (Only even addresses for 16-bit data transfer instructions)                                          |

| addr11     | 0800H to 0FFFH Immediate data or labels                                                              |

| addr5      | 0040H to 007FH Immediate data or labels (even address only)                                          |

| word       | 16-bit immediate data or label                                                                       |

| byte       | 8-bit immediate data or label                                                                        |

| bit        | 3-bit immediate data or label                                                                        |

| RBn        | RB0 to RB3                                                                                           |

#### Table 29-1. Operand Identifiers and Specification Methods

Note Addresses from FFD0H to FFDFH cannot be accessed with these operands.

Remark For special function register symbols, see Table 3-8 Special Function Register List.

#### Caution The pins mounted depend on the product. Refer to Caution 2 at the beginning of this chapter.

#### **Flash Memory Programming Characteristics**

#### $(T_{A} = -40 \text{ to } +85^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{DD} = \text{EV}_{DD} \le 5.5 \text{ V}, \text{ AV}_{REF} \le \text{V}_{DD}, \text{ V}_{SS} = \text{EV}_{SS} = \text{AV}_{SS} = 0 \text{ V})$

#### Basic characteristics

| Parameter                              |            | Symbol | Conditions                                                                                                                                                                                        |                                                                                                                                                  |                                                                                                                                                                                     |                        |      | TYP.  | MAX. | Unit  |

|----------------------------------------|------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|------|-------|

| VDD supply current                     |            | Idd    | f <sub>XP</sub> = 10 MHz (TYP.), 20 MHz (MAX.)                                                                                                                                                    |                                                                                                                                                  |                                                                                                                                                                                     |                        |      | 4.5   | 11.0 | mA    |

| Erase time All block                   |            | Teraca |                                                                                                                                                                                                   |                                                                                                                                                  |                                                                                                                                                                                     |                        |      | 20    | 200  | ms    |

| Notes 1, 2                             | Block unit | Terasa |                                                                                                                                                                                                   |                                                                                                                                                  |                                                                                                                                                                                     |                        |      | 20    | 200  | ms    |

| Write time<br>units) <sup>Note 1</sup> | (in 8-bit  | Twrwa  |                                                                                                                                                                                                   |                                                                                                                                                  |                                                                                                                                                                                     |                        |      | 10    | 100  | μs    |

| Number of rewrites<br>per chip         |            | Cerwr  | 1 erase +<br>1 write<br>after<br>erase =<br>1 rewrite<br>Note 3                                                                                                                                   | Expanded-<br>specification<br>Products<br>(μΡD78F05xxA,<br>78F05xxDA)                                                                            | <ul> <li>When a flash memory<br/>programmer is used,<br/>and the libraries<sup>Note 4</sup><br/>provided by Renesas<br/>Electronics are used</li> <li>For program update</li> </ul> | Retention:<br>15 years | 1000 |       |      | Times |

|                                        |            |        | <ul> <li>When the EEPROM<br/>emulation libraries<sup>Note 5</sup><br/>provided by Renesas<br/>Electronics are used</li> <li>The rewritable ROM<br/>size: 4 KB</li> <li>For data update</li> </ul> | Retention:<br>5 years                                                                                                                            | 10000                                                                                                                                                                               |                        |      | Times |      |       |

|                                        |            |        |                                                                                                                                                                                                   | Expanded-<br>specification<br>Products<br>(µPD78F05xxA,<br>78F05xxDA)<br>Conventional-<br>specification<br>Products<br>(µPD78F05xx,<br>78F05xxD) | Conditions other than<br>the above <sup>Note 6</sup>                                                                                                                                | Retention:<br>10 years | 100  |       |      | Times |

**Notes 1.** Characteristic of the flash memory. For the characteristic when a dedicated flash programmer, PG-FP4 or PG-FP5, is used and the rewrite time during self programming, see **Tables 27-12** to **27-14**.

- 2. The prewrite time before erasure and the erase verify time (writeback time) are not included.

- **3.** When a product is first written after shipment, "erase  $\rightarrow$  write" and "write only" are both taken as one rewrite.

- The sample library specified by the 78K0/Kx2 Flash Memory Self Programming User's Manual (Document No.: U17516E) is excluded.

- The sample program specified by the 78K0/Kx2 EEPROM Emulation Application Note (Document No.: U17517E) is excluded.

- 6. These include when the sample library specified by the 78K0/Kx2 Flash Memory Self Programming User's Manual (Document No.: U17516E) and the sample program specified by the 78K0/Kx2 EEPROM Emulation Application Note (Document No.: U17517E) are used.

Remarks 1. fxp: Main system clock oscillation frequency

2. For serial write operation characteristics, refer to 78K0/Kx2 Flash Memory Programming (Programmer) Application Note (Document No.: U17739E).

# (2) Non-port functions

| Port                          |                     | 78K0/KB2                                                                      |                                                                | 78K0/KC2                                           |                                      | 78K0/KD2   | 78K0/KE2       | 78K0/KF2                             |  |  |  |  |

|-------------------------------|---------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------|--------------------------------------|------------|----------------|--------------------------------------|--|--|--|--|

|                               |                     | 30/36 Pins                                                                    | 38 Pins                                                        | 44 Pins                                            | 48 Pins                              | 52 Pins    | 64 Pins        | 80 Pins                              |  |  |  |  |

| Power supply, ground          |                     | Vdd, EVdd <sup>Note 1</sup> ,<br>Vss, EVss <sup>Note 1</sup> ,<br>AVref, AVss | VDD, AVREF, VSS                                                | s, AVss                                            | Vdd, EVdd, Vss, EVss, AVref,<br>AVss |            |                |                                      |  |  |  |  |

| Reg                           | gulator             | REGC                                                                          |                                                                |                                                    |                                      |            |                |                                      |  |  |  |  |

| Res                           | set                 | RESET                                                                         |                                                                |                                                    |                                      |            |                |                                      |  |  |  |  |

| Clo<br>osc                    | ck<br>illation      | X1, X2,<br>EXCLK                                                              | X1, X2, XT1, X                                                 | T2, EXCLK, EX                                      | CLKS                                 |            |                |                                      |  |  |  |  |

|                               | ting to<br>h memory | FLMD0                                                                         | FLMD0                                                          |                                                    |                                      |            |                |                                      |  |  |  |  |

| Inte                          | errupt              | INTP0 to INTP                                                                 | 5                                                              | •                                                  | INTP0 to INTP                        | 6          | INTP0 to INTP7 |                                      |  |  |  |  |

| Key                           | v interrupt         | -                                                                             | KR0, KR1                                                       | KR0 to KR3                                         |                                      | KR0 to KR7 |                |                                      |  |  |  |  |

|                               | ТМ00                | TI000, TI010, TO00                                                            |                                                                |                                                    |                                      |            |                |                                      |  |  |  |  |

|                               | TM01                | - TI001 <sup>Note 2</sup> , TI011 <sup>Note 2</sup> , TO01 <sup>Note</sup>    |                                                                |                                                    |                                      |            |                |                                      |  |  |  |  |

| Timer                         | TM50                | TI50, TO50                                                                    |                                                                |                                                    |                                      |            |                |                                      |  |  |  |  |

| Ę                             | TM51                | TI51, TO51                                                                    |                                                                |                                                    |                                      |            |                |                                      |  |  |  |  |

|                               | тмно                | ТОНО                                                                          |                                                                |                                                    |                                      |            |                |                                      |  |  |  |  |

|                               | TMH1                | ТОН1                                                                          |                                                                |                                                    |                                      |            |                |                                      |  |  |  |  |

|                               | UART0               | RxD0, TxD0                                                                    |                                                                |                                                    |                                      |            |                |                                      |  |  |  |  |

|                               | UART6               | RxD6, TxD6                                                                    |                                                                |                                                    |                                      |            |                |                                      |  |  |  |  |

| ce                            | IIC0                | SCL0, SDA0 SCL0, SDA0, EXSCL0                                                 |                                                                |                                                    |                                      |            |                |                                      |  |  |  |  |

| iterfa                        | CSI10               | SCK10, SI10, SO10                                                             |                                                                |                                                    |                                      |            |                |                                      |  |  |  |  |

| Serial interface              | CSI11               |                                                                               | SCK11 <sup>Note 2</sup> , SI1<br>SO11 <sup>Note 2</sup> , SSI1 | SI11 <sup>Note 2</sup> ,<br>SI11 <sup>Note 2</sup> |                                      |            |                |                                      |  |  |  |  |

| 0,                            | CSIA0               |                                                                               |                                                                |                                                    | _                                    |            |                | SCKAO, SIAO,<br>SOAO, BUSYO,<br>STBO |  |  |  |  |

| A/D                           | converter           | ANI0 to ANI3                                                                  | ANI0 to ANI5                                                   | ANI0 to ANI7                                       |                                      |            |                |                                      |  |  |  |  |

| Clo                           | ck output           |                                                                               | -                                                              |                                                    | PCL                                  |            | <u>.</u>       |                                      |  |  |  |  |

| Buz                           | zer output          |                                                                               |                                                                | -                                                  |                                      |            | BUZ            |                                      |  |  |  |  |

| Low-voltage<br>detector (LVI) |                     | EXLVI                                                                         |                                                                |                                                    |                                      |            |                |                                      |  |  |  |  |

Notes 1. This is not mounted onto 30-pin products.

2. This is not mounted onto the 78K0/KE2 products whose flash memory is less than 32 KB.

Unit mA mA mA mA mΑ mΑ mA mA mA mA mΑ mA mA mA mΑ mA mΑ mA mA mΑ mA mΑ mA mA mA mA mA mA mA mA mΑ

#### Caution The pins mounted depend on the product. Refer to Caution at the beginning of this chapter.

| Parameter                             | Symbol | Conditions                                                                                                                        |                                       | MIN. | TYP. | MAX.  |

|---------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------|------|-------|

| Output current, highNote 1            | Іон1   | Per pin for P00 to P06, P10 to                                                                                                    | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | -3.0  |

|                                       |        | P17, P30 to P33, P40 to P47,                                                                                                      | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | -2.5  |

|                                       |        | P50 to P57, P64 to P67, P70 to<br>P77, P120, P130, P140 to P145                                                                   | $1.8~V \leq V_{\text{DD}} < 2.7~V$    |      |      | -1.0  |

|                                       |        | Total of P00 to P04, P40 to P47,                                                                                                  | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | -12.0 |

|                                       |        | P120, P130, P140 to P145 <sup>Note 3</sup>                                                                                        | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | -7.0  |

|                                       |        |                                                                                                                                   | $1.8~V \leq V_{\text{DD}} < 2.7~V$    |      |      | -5.0  |

|                                       |        | Total of P05, P06, P10 to P17,                                                                                                    | $4.0~V \le V_{\text{DD}} \le 5.5~V$   |      |      | -18.0 |

|                                       |        | P30 to P33, P50 to P57, P64 to                                                                                                    | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | -15.0 |

|                                       |        | P67, P70 to P77 <sup>Note 3</sup>                                                                                                 | $1.8~V \leq V_{\text{DD}} < 2.7~V$    |      |      | -10.0 |

|                                       |        | Total of all the pins above Note 3                                                                                                | $4.0~V \le V_{\text{DD}} \le 5.5~V$   |      |      | -23.0 |

|                                       |        |                                                                                                                                   | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | -20.0 |

|                                       |        |                                                                                                                                   | $1.8~V \leq V_{\text{DD}} < 2.7~V$    |      |      | -15.0 |

|                                       | Іон2   | Per pin for P20 to P27                                                                                                            | $AV_{REF} = V_{DD}$                   |      |      | -0.1  |

|                                       |        | Per pin for P121 to P124                                                                                                          |                                       |      |      | -0.1  |

| Dutput current, low <sup>Note 2</sup> | IOL1   | Per pin for P00 to P06, P10 to<br>P17, P30 to P33, P40 to P47,<br>P50 to P57, P64 to P67, P70 to<br>P77, P120, P130, P140 to P145 | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | 8.5   |

|                                       |        |                                                                                                                                   | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | 5.0   |

|                                       |        |                                                                                                                                   | $1.8~V \le V_{\text{DD}} < 2.7~V$     |      |      | 2.0   |

|                                       |        | Per pin for P60 to P63                                                                                                            | $4.0~V \le V_{\text{DD}} \le 5.5~V$   |      |      | 15.0  |

|                                       |        |                                                                                                                                   | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | 5.0   |

|                                       |        |                                                                                                                                   | $1.8~V \leq V_{\text{DD}} < 2.7~V$    |      |      | 2.0   |

|                                       |        | Total of P00 to P04, P40 to P47,                                                                                                  | $4.0~V \le V_{\text{DD}} \le 5.5~V$   |      |      | 20.0  |

|                                       |        | P120, P130, P140 to P145 <sup>Note 3</sup>                                                                                        | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | 15.0  |

|                                       |        |                                                                                                                                   | $1.8~V \leq V_{\text{DD}} < 2.7~V$    |      |      | 9.0   |

|                                       |        | Total of P05, P06, P10 to P17,                                                                                                    | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | 45.0  |

|                                       |        | P30 to P33, P50 to P57, P60 to                                                                                                    | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | 35.0  |

|                                       |        | P67, P70 to P77 <sup>Note 3</sup>                                                                                                 | $1.8~V \leq V_{\text{DD}} < 2.7~V$    |      |      | 20.0  |

|                                       |        | Total of all the pins above Note 3                                                                                                | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | 65.0  |

|                                       |        |                                                                                                                                   | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | 50.0  |

|                                       |        |                                                                                                                                   | $1.8~V \leq V_{\text{DD}} < 2.7~V$    |      |      | 29.0  |

|                                       | IOL2   | Per pin for P20 to P27                                                                                                            | AVREF = VDD                           |      |      | 0.4   |

|                                       |        | Per pin for P121 to P124                                                                                                          |                                       |      |      | 0.4   |

#### DC Characteristics (1/4)

(TA = -40 to +85°C, 1.8 V  $\leq$  Vdd = EVdd  $\leq$  5.5 V, AVREF  $\leq$  Vdd, Vss = EVss = AVss = 0 V)

Notes 1. Value of current at which the device operation is guaranteed even if the current flows from VDD to an output pin.

2. Value of current at which the device operation is guaranteed even if the current flows from an output pin to GND.

**3.** Specification under conditions where the duty factor is 70% (time for which current is output is  $0.7 \times t$  and time for which current is not output is  $0.3 \times t$ , where t is a specific time). The total output current of the pins at a duty factor of other than 70% can be calculated by the following expression.

• Where the duty factor of IoH is n%: Total output current of pins =  $(I_{OH} \times 0.7)/(n \times 0.01)$

<Example> Where the duty factor is 50%,  $I_{OH} = -20.0 \text{ mA}$

Total output current of pins =  $(-20.0 \times 0.7)/(50 \times 0.01) = -28.0 \text{ mA}$

However, the current that is allowed to flow into one pin does not vary depending on the duty factor. A current higher than the absolute maximum rating must not flow into one pin.

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of port pins.

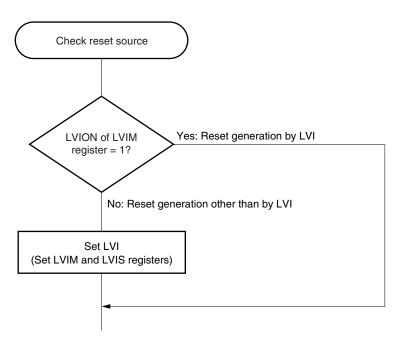

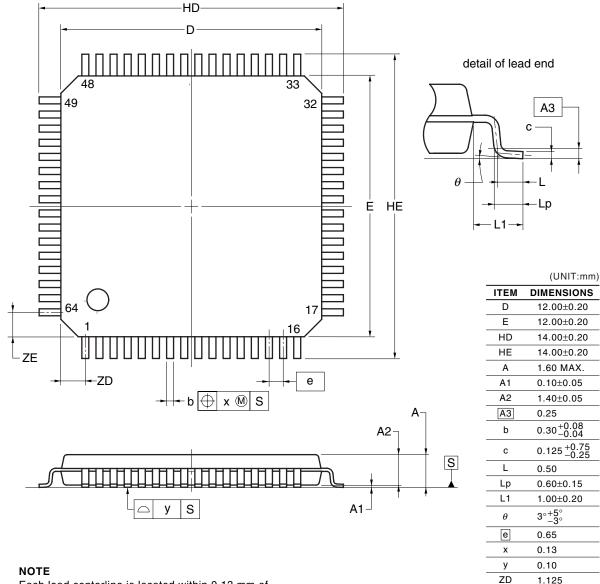

64-PIN PLASTIC LQFP (14x14)

- μPD78F0531GC(A)-GAL-AX, 78F0532GC(A)-GAL-AX, 78F0533GC(A)-GAL-AX, 78F0534GC(A)-GAL-AX, 78F0535GC(A)-GAL-AX, 78F0535GC(A)-GAL-AX, 78F0537GC(A)-GAL-AX

- *μ*PD78F0531GC(A2)-GAL-AX, 78F0532GC(A2)-GAL-AX, 78F0533GC(A2)-GAL-AX, 78F0534GC(A2)-GAL-AX, 78F0535GC(A2)-GAL-AX, 78F0535GC(A2)-GAL-AX, 78F0537GC(A2)-GAL-AX

- μPD78F0531AGC-GAL-AX, 78F0532AGC-GAL-AX, 78F0533AGC-GAL-AX, 78F0535AGC-GAL-AX, 78F0535AGC-GAL-AX, 78F0537AGC-GAL-AX, 78F0537ACC-GAL-AX, 78F0537