Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | 78K/0                                                                                 |

| Core Size                  | 8-Bit                                                                                 |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                                    |

| Number of I/O              | 55                                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 1K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 8x10b                                                                             |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 64-LQFP                                                                               |

| Supplier Device Package    | -                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0533agb-gah-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## (1) Conventional-specification products (µPD78F05xx and 78F05xxD) (3/3)

## <4> When high-speed system clock (X1 oscillation or external clock input) is used and entry RAM is located in short direct addressing range

| Library                   | / Name            |                                             | Processing                 | g Time (μs)                          |                      |  |  |  |  |

|---------------------------|-------------------|---------------------------------------------|----------------------------|--------------------------------------|----------------------|--|--|--|--|

|                           |                   | Normal Model                                | of C Compiler              | Static Model of C Compiler/Assembler |                      |  |  |  |  |

|                           |                   | Min.                                        | Max.                       | Min.                                 | Max.                 |  |  |  |  |

| Self programming start l  | ibrary            | 34/fcpu                                     |                            |                                      |                      |  |  |  |  |

| Initialize library        |                   |                                             | 49/fcpu +                  | 224.6875                             |                      |  |  |  |  |

| Mode check library        |                   | <b>35/f</b> сри +                           | 113.625                    | <b>29/f</b> сри +                    | 113.625              |  |  |  |  |

| Block blank check library | /                 | 174/fcpu +                                  | 6120.9375                  | 134/fcpu +                           | 6120.9375            |  |  |  |  |

| Block erase library       |                   | 174/fcpu +<br>30820.75                      | 174/fсец +<br>298675       | 134/fcpu +<br>30820.75               | 134/fcpu +<br>298675 |  |  |  |  |

| Word write library        |                   | 318 (321)/fcpu +<br>383                     | 318 (321)/fcpu +<br>1230.5 |                                      |                      |  |  |  |  |

| Block verify library      |                   | 174/fcpu + 13175.4375 134/fcpu + 13175.4375 |                            |                                      |                      |  |  |  |  |

| Self programming end li   | brary             | 34/fopu                                     |                            |                                      |                      |  |  |  |  |

| Get information library   | Option value: 03H | 171 (172)/fcp                               | u + 171.3125               | 129 (130)/fcpu + 171.3125            |                      |  |  |  |  |

|                           | Option value: 04H | 181 (182)/fo                                | сец <b>+ 166.75</b>        | 139 (140)/fo                         | CPU + 166.75         |  |  |  |  |

|                           | Option value: 05H | <b>404 (411)/f</b> c                        | ри <b>+ 231.875</b>        | <b>362 (369)/f</b> c                 | ри <b>+ 231.875</b>  |  |  |  |  |

| Set information library   |                   | 75/fcpu +                                   | 75/fcpu +                  | 67/fcpu +                            | 67/fcpu +            |  |  |  |  |

|                           |                   | 78884.5625                                  | 527566.875                 | 78884.5625                           | 527566.875           |  |  |  |  |

| EEPROM write library      |                   | 318 (321)/fcpu +                            | 318 (321)/fcpu +           | 262 (265)/fcpu +                     | 262 (265)/fcpu +     |  |  |  |  |

|                           |                   | 538.75                                      | 1386.25                    | 538.75                               | 1386.25              |  |  |  |  |

- **Remarks 1.** Values in parentheses indicate values when a write start address structure is located other than in the internal high-speed RAM.

- 2. The above processing times are those during stabilized operation of the internal high-speed oscillator (RSTS = 1).

- 3. fcpu: CPU operation clock frequency

- 4. RSTS: Bit 7 of the internal oscillation mode register (RCM)

(4/0)

| 2                            |                                |                                            |                                                                                           | (4/6)                                                                                                                                                                               |

|------------------------------|--------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 78K0/Kx2<br>Microcontrollers | Package                        | Product<br>type                            | Quality<br>grace                                                                          | Part Number                                                                                                                                                                         |

| 78K0/KE2                     | 64-pin plastic<br>LQFP (14x14) | Conventional-<br>specification<br>products | Standard<br>products                                                                      | μPD78F0531GC-UBS-A, 78F0532GC-UBS-A,<br>78F0533GC-UBS-A, 78F0534GC-UBS-A,<br>78F0535GC-UBS-A, 78F0536GC-UBS-A,<br>78F0537GC-UBS-A, 78F0537DGC-UBS-A <sup>Note</sup>                 |

|                              |                                |                                            | (A) grade μPD78F0531GC(A)-GAL-AX, 78F0532GC   products 78F0533GC(A)-GAL-AX, 78F0534GC(A)- | μΡD78F0531GC(A)-GAL-AX, 78F0532GC(A)-GAL-AX,<br>78F0533GC(A)-GAL-AX, 78F0534GC(A)-GAL-AX,<br>78F0535GC(A)-GAL-AX, 78F0536GC(A)-GAL-AX,<br>78F0537GC(A)-GAL-AX                       |

|                              |                                |                                            | (A2) grade<br>products                                                                    | μPD78F0531GC(A2)-GAL-AX, 78F0532GC(A2)-GAL-AX,<br>78F0533GC(A2)-GAL-AX, 78F0534GC(A2)-GAL-AX,<br>78F0535GC(A2)-GAL-AX, 78F0536GC(A2)-GAL-AX,<br>78F0537GC(A2)-GAL-AX                |

|                              |                                | Expanded-<br>specification<br>products     | Standard products                                                                         | μΡD78F0531AGC-GAL-AX, 78F0532AGC-GAL-AX,<br>78F0533AGC-GAL-AX, 78F0534AGC-GAL-AX,<br>78F0535AGC-GAL-AX, 78F0536AGC-GAL-AX,<br>78F0537AGC-GAL-AX, 78F0537DAGC-GAL-AX <sup>Note</sup> |

|                              |                                |                                            | (A) grade<br>products                                                                     | μPD78F0531AGCA-GAL-G, 78F0532AGCA-GAL-G,<br>78F0533AGCA-GAL-G, 78F0534AGCA-GAL-G,<br>78F0535AGCA-GAL-G, 78F0536AGCA-GAL-G,<br>78F0537AGCA-GAL-G                                     |

|                              |                                |                                            | (A2) grade<br>products                                                                    | μPD78F0531AGCA2-GAL-G, 78F0532AGCA2-GAL-G,<br>78F0533AGCA2-GAL-G, 78F0534AGCA2-GAL-G,<br>78F0535AGCA2-GAL-G, 78F0536AGCA2-GAL-G,<br>78F0537AGCA2-GAL-G                              |

**Note** The μPD78F0537D and 78F0537DA have an on-chip debug function, which is provided for development and evaluation. Do not use the on-chip debug function in products designated for mass production, because the guaranteed number of rewritable times of the flash memory may be exceeded when this function is used, and product reliability therefore cannot be guaranteed. Renesas Electronics is not liable for problems occurring when the on-chip debug function is used.

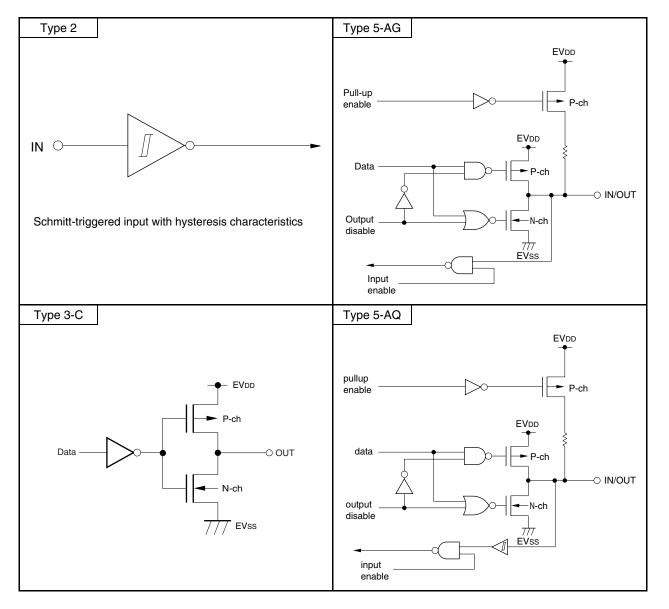

Figure 2-1. Pin I/O Circuit List (1/2)

Remark With products not provided with an EVDD or EVss pin, replace EVDD with VDD, or replace EVss with Vss.

## 5.2.9 Port 12

|                                         | 78K0/KB2     | 78K0/KC2 | 78K0/KF2                                                   |                                                           |  |

|-----------------------------------------|--------------|----------|------------------------------------------------------------|-----------------------------------------------------------|--|

|                                         |              |          | Products<br>whose flash<br>memory is<br>less than<br>32 KB | Products<br>whose flash<br>memory is at<br>least<br>48 KB |  |

| P120/INTP0/EXLVI                        | $\checkmark$ |          | $\checkmark$                                               |                                                           |  |

| P121/X1/OCD0A <sup>Note</sup>           | $\checkmark$ |          |                                                            |                                                           |  |

| P122/X2/EXCLK/<br>OCD0B <sup>Note</sup> | $\checkmark$ |          |                                                            |                                                           |  |

| P123/XT1                                | -            |          |                                                            |                                                           |  |

| P124/XT2/EXCLKS                         | _            |          |                                                            |                                                           |  |

**Note** OCD0A and OCD0B are provided to the products with an on-chip debug function (*µ*PD78F05xxD and 78F05xxDA) only.

## **Remark** $\sqrt{:}$ Mounted, -: Not mounted

Port 12 is an I/O port with an output latch. Port 12 can be set to the input mode or output mode in 1-bit units using port mode register 12 (PM12). When used as an input port only for P120, use of an on-chip pull-up resistor can be specified by pull-up resistor option register 12 (PU12).

This port can also be used as pins for external interrupt request input, potential input for external low-voltage detection, connecting resonator for main system clock, connecting resonator for subsystem clock, external clock input for main system clock, and external clock input for subsystem clock.

Reset signal generation sets port 12 to input mode.

Figures 5-22 and 5-23 show block diagrams of port 12.

Caution 1. When using the P121 to P124 pins to connect a resonator for the main system clock (X1, X2) or subsystem clock (XT1, XT2), or to input an external clock for the main system clock (EXCLK) or subsystem clock (EXCLKS), the X1 oscillation mode, XT1 oscillation mode, or external clock input mode must be set by using the clock operation mode select register (OSCCTL) (for details, see 6.3 (1) Clock operation mode select register (OSCCTL) and (3) Setting of operation mode for subsystem clock pin). The reset value of OSCCTL is 00H (all of the P121 to P124 pins are I/O port pins). At this time, setting of the PM121 to PM124 and P121 to P124 pins is not necessary.

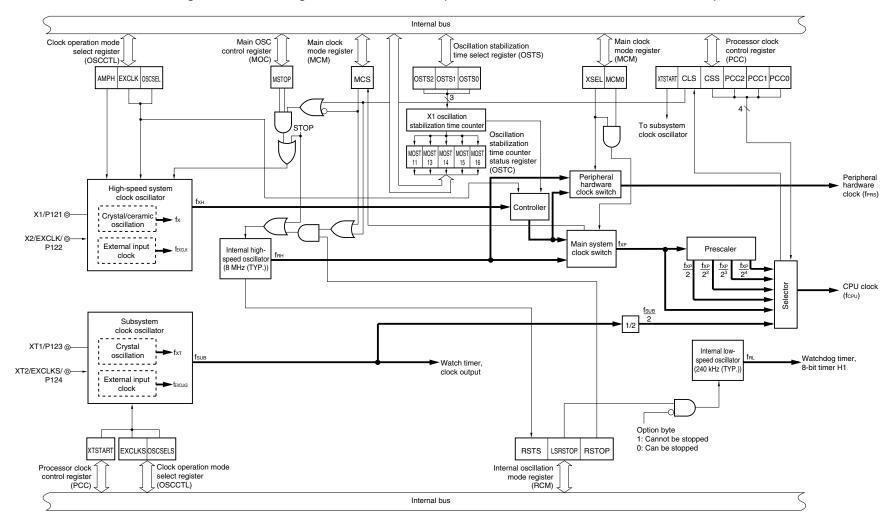

## CHAPTER 6 CLOCK GENERATOR

## 6.1 Functions of Clock Generator

The clock generator generates the clock to be supplied to the CPU and peripheral hardware. The following three kinds of system clocks and clock oscillators are selectable.

#### (1) Main system clock

### <1> X1 oscillator

This circuit oscillates a clock of  $f_x = 1$  to 20 MHz by connecting a resonator to X1 and X2. Oscillation can be stopped by executing the STOP instruction or using the main OSC control register (MOC).

#### <2> Internal high-speed oscillator

This circuit oscillates a clock of  $f_{RH} = 8$  MHz (TYP.). After a reset release, the CPU always starts operating with this internal high-speed oscillation clock. Oscillation can be stopped by executing the STOP instruction or using the internal oscillation mode register (RCM).

An external main system clock ( $f_{EXCLK} = 1$  to 20 MHz) can also be supplied from the EXCLK/X2/P122 pin. An external main system clock input can be disabled by executing the STOP instruction or using RCM. As the main system clock, a high-speed system clock (X1 clock or external main system clock) or internal high-speed oscillation clock can be selected by using the main clock mode register (MCM).

#### (2) Subsystem clock<sup>Note</sup>

#### Subsystem clock oscillator

This circuit oscillates at a frequency of  $f_{XT} = 32.768$  kHz by connecting a 32.768 kHz resonator across XT1 and XT2. Oscillation can be stopped by using the processor clock control register (PCC) and clock operation mode select register (OSCCTL).

An external subsystem clock (fexcLks = 32.768 kHz) can also be supplied from the EXCLKS/XT2/P124 pin. An external subsystem clock input can be disabled by setting PCC and OSCCTL.

Note The 78K0/KB2 is not provided with a subsystem clock.

| <b>Remark</b> fx: X1 clock oscillation frequence | Remark | fx: X | 1 clock | oscillation | frequenc |

|--------------------------------------------------|--------|-------|---------|-------------|----------|

|--------------------------------------------------|--------|-------|---------|-------------|----------|

fRH: Internal high-speed oscillation clock frequency

fexclk: External main system clock frequency

- fxT: XT1 clock oscillation frequency

- fEXCLKS: External subsystem clock frequency

## Figure 7-4. Format of 16-Bit Timer Capture/Compare Register 00n (CR00n)

Address: FF12H, FF13H (CR000), FFB2H, FFB3H (CR001)

FF13H (CR000), FFB3H (CR001)

After reset: 0000H R/W

|            |    |    |    |    |          |    |   |   | 11 1211 (011000), 11 D211 (011001) |   |   |   |          |   |   |   |

|------------|----|----|----|----|----------|----|---|---|------------------------------------|---|---|---|----------|---|---|---|

|            |    |    |    |    | <u> </u> |    |   |   |                                    |   |   |   | <u> </u> |   |   |   |

|            | 15 | 14 | 13 | 12 | 11       | 10 | 9 | 8 | 7                                  | 6 | 5 | 4 | 3        | 2 | 1 | 0 |

| CR00n      |    |    |    |    |          |    |   |   |                                    |   |   |   |          |   |   |   |

| (n = 0, 1) |    |    |    |    |          |    |   |   |                                    |   |   |   |          |   |   |   |

#### (i) When CR00n is used as a compare register

The value set in CR00n is constantly compared with the TM0n count value, and an interrupt request signal (INTTM00n) is generated if they match. The value is held until CR00n is rewritten.

## Caution CR00n does not perform the capture operation when it is set in the comparison mode, even if a capture trigger is input to it.

#### (ii) When CR00n is used as a capture register

The count value of TM0n is captured to CR00n when a capture trigger is input.

As the capture trigger, an edge of a phase reverse to that of the TI00n pin or the valid edge of the TI01n pin can be selected by using CRC0n or PRM0n.

#### Figure 7-5. Format of 16-Bit Timer Capture/Compare Register 01n (CR01n)

| Address:            | FF14H                                                     | H, FF1 | 5H (C | R010 | ), FFB | 4H, FI | FB5H | (CR01 | 1) | After | r reset | : 000 | он | R/W | , |   |

|---------------------|-----------------------------------------------------------|--------|-------|------|--------|--------|------|-------|----|-------|---------|-------|----|-----|---|---|

|                     | FF15H (CR010), FFB5H (CR011) FF14H (CR010), FFB4H (CR011) |        |       |      |        |        |      |       |    |       |         |       |    |     |   |   |

|                     |                                                           |        |       |      |        |        |      |       |    |       |         |       |    |     |   |   |

|                     | 15                                                        | 14     | 13    | 12   | 11     | 10     | 9    | 8     | 7  | 6     | 5       | 4     | 3  | 2   | 1 | 0 |

| CR01n<br>(n = 0, 1) |                                                           |        |       |      |        |        |      |       |    |       |         |       |    |     |   |   |

#### (i) When CR01n is used as a compare register

The value set in CR01n is constantly compared with the TM0n count value, and an interrupt request signal (INTTM01n) is generated if they match.

## Caution CR01n does not perform the capture operation when it is set in the comparison mode, even if a capture trigger is input to it.

#### (ii) When CR01n is used as a capture register

The count value of TM0n is captured to CR01n when a capture trigger is input.

It is possible to select the valid edge of the TI00n pin as the capture trigger. The TI00n pin valid edge is set by PRM0n.

## **Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2,

78K0/KD2 products

n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

## Figure 7-35. Example of Register Settings in Clear & Start Mode Entered by TI00n Pin Valid Edge Input (2/2)

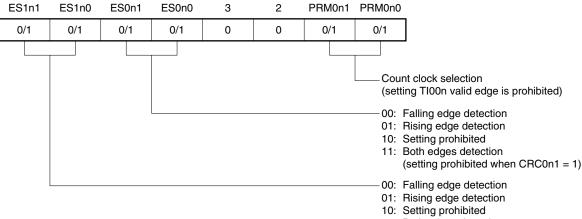

## (d) Prescaler mode register 0n (PRM0n)

#### 11: Both edges detection

#### (e) 16-bit timer counter 0n (TM0n)

By reading TM0n, the count value can be read.

#### (f) 16-bit capture/compare register 00n (CR00n)

When this register is used as a compare register and when its value matches the count value of TM0n, an interrupt signal (INTTM00n) is generated. The count value of TM0n is not cleared.

To use this register as a capture register, select either the TI00n or TI01n pin<sup>Note</sup> input as a capture trigger. When the valid edge of the capture trigger is detected, the count value of TM0n is stored in CR00n.

Note The timer output (TO0n) cannot be used when detection of the valid edge of the TI01n pin is used.

#### (g) 16-bit capture/compare register 01n (CR01n)

When this register is used as a compare register and when its value matches the count value of TM0n, an interrupt signal (INTTM01n) is generated. The count value of TM0n is not cleared. When this register is used as a capture register, the TI00n pin input is used as a capture trigger. When the valid

edge of the capture trigger is detected, the count value of TM0n is stored in CR01n.

**Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

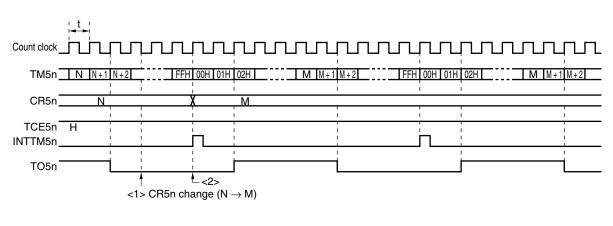

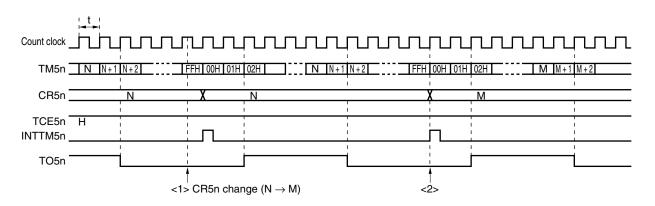

## (2) Operation with CR5n changed

Figure 8-15. Timing of Operation with CR5n Changed

(a) CR5n value is changed from N to M before clock rising edge of FFH  $\rightarrow$  Value is transferred to CR5n at overflow immediately after change.

<sup>(</sup>b) CR5n value is changed from N to M after clock rising edge of FFH  $\rightarrow$  Value is transferred to CR5n at second overflow.

Caution When reading from CR5n between <1> and <2> in Figure 8-15, the value read differs from the actual value (read value: M, actual value of CR5n: N).

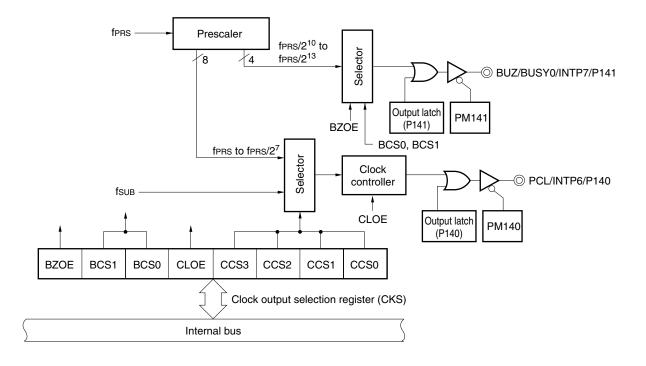

## Figure 12-2. Block Diagram of Clock Output/Buzzer Output Controller (78K0/KE2, 78K0/KF2)

## 12.2 Configuration of Clock Output/Buzzer Output Controller

The clock output/buzzer output controller includes the following hardware.

| Table 12-1. | I. Configuration of Clock Output/Buzzer Output Conti | roller |

|-------------|------------------------------------------------------|--------|

|-------------|------------------------------------------------------|--------|

| Item              | Configuration                         |  |  |  |  |

|-------------------|---------------------------------------|--|--|--|--|

| Control registers | Clock output selection register (CKS) |  |  |  |  |

|                   | Port mode register 14 (PM14)          |  |  |  |  |

|                   | Port register 14 (P14)                |  |  |  |  |

## 12.3 Registers Controlling Clock Output/Buzzer Output Controller

The following two registers are used to control the clock output/buzzer output controller.

- Clock output selection register (CKS)

- Port mode register 14 (PM14)

#### (1) Clock output selection register (CKS)

This register sets output enable/disable for clock output (PCL) and for the buzzer frequency output (BUZ), and sets the output clock.

CKS is set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears CKS to 00H.

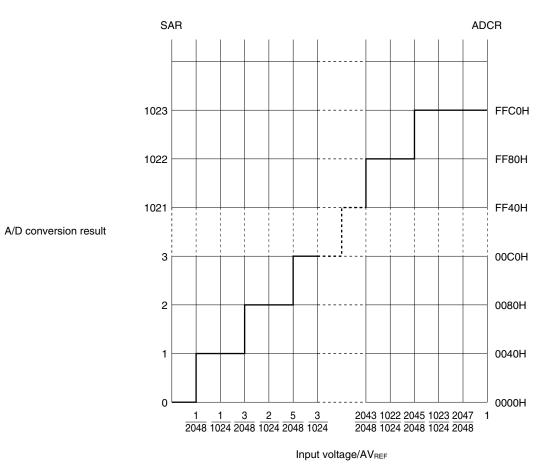

Figure 13-12 shows the relationship between the analog input voltage and the A/D conversion result.

Figure 13-12. Relationship Between Analog Input Voltage and A/D Conversion Result

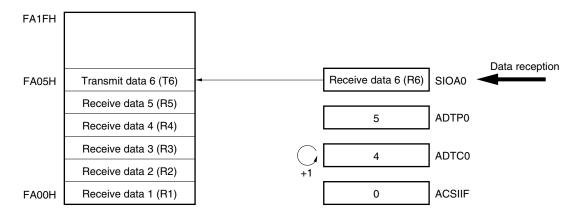

## (3) Serial trigger register 0 (CSIT0)

This is an 8-bit register used to control execution/stop of automatic data transfer between buffer RAM and serial I/O shift register 0 (SIOA0).

This register can be set by a 1-bit or 8-bit memory manipulation instruction. This register can be set when bit 6 (ATE0) of serial operation mode specification register 0 (CSIMA0) is 1. Reset signal generation clears this register to 00H.

### Figure 17-4. Format of Serial Trigger Register 0 (CSIT0)

Address: FF92H After reset: 00H R/W

| Symbol | 7 | 6 | 5 | 4 | 3 | 2 | <1>    | <0>    |

|--------|---|---|---|---|---|---|--------|--------|

| CSIT0  | 0 | 0 | 0 | 0 | 0 | 0 | ATSTP0 | ATSTA0 |

| ATSTP0 | Automatic data transfer stop    |

|--------|---------------------------------|

| 0      | _                               |

| 1      | Automatic data transfer stopped |

|        |                                 |

| ATSTA0 | Automatic data transfer start   |

| 0      | _                               |

| - 1    | Automatic data transfer started |

- Cautions 1. Even if ATSTP0 or ATSTA0 is set to 1, automatic transfer cannot be started/stopped until 1-byte transfer is complete.

- 2. ATSTP0 and ATSTA0 change to 0 automatically after the interrupt signal INTACSI is generated.

- 3. After automatic data transfer is stopped, the data address when the transfer stopped is stored in automatic data transfer address count register 0 (ADTC0). However, since no function to restart automatic data transfer is incorporated, when transfer is stopped by setting ATSTP0 = 1, start automatic data transfer by setting ATSTA0 to 1 after re-setting the registers.

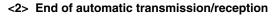

# Figure 17-16. Internal Buffer RAM Operation in Automatic Transmission/Reception Mode (End of Transmission/Reception)

## <1> End of 6th byte transmission/reception

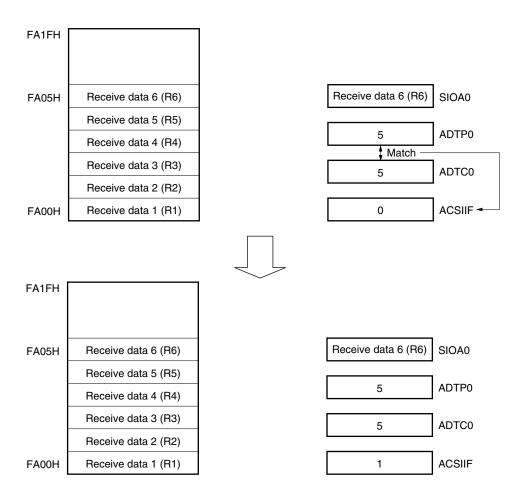

## (2) Master operation in multi-master system

**Note** Confirm that the bus is released (CLD0 bit = 1, DAD0 bit = 1) for a specific period (for example, for a period of one frame). If the SDA0 pin is constantly at low level, decide whether to release the I<sup>2</sup>C bus (SCL0 and SDA0 pins = high level) in conformance with the specifications of the product that is communicating.

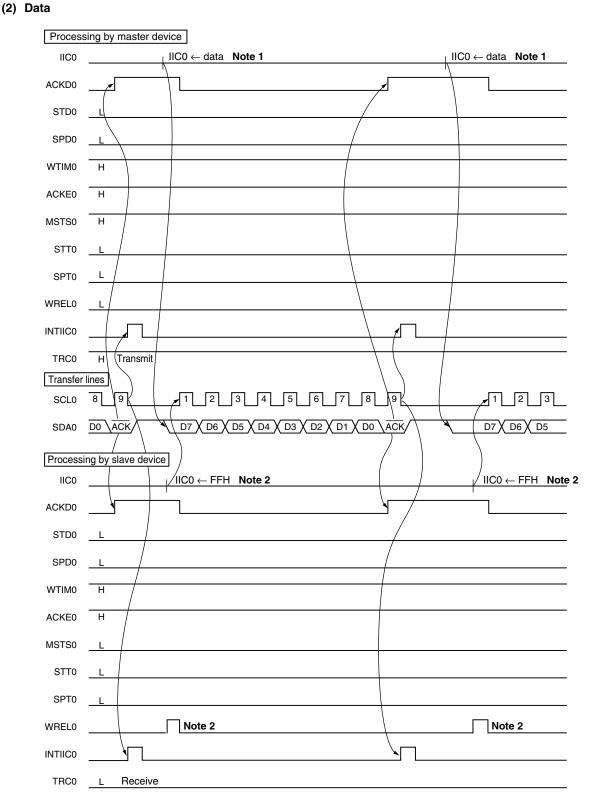

# Figure 18-27. Example of Master to Slave Communication (When 9-Clock Wait Is Selected for Both Master and Slave) (2/3)

RENESAS

| Address: FF                         | E8H After r | eset: FFH I   | R/W                |        |                  |         |       |                       |  |  |  |  |

|-------------------------------------|-------------|---------------|--------------------|--------|------------------|---------|-------|-----------------------|--|--|--|--|

| Symbol                              | <7>         | <6>           | <5>                | <4>    | <3>              | <2>     | <1>   | <0>                   |  |  |  |  |

| PR0L                                | SREPR6      | PPR5          | PPR4               | PPR3   | PPR2             | PPR1    | PPR0  | LVIPR                 |  |  |  |  |

|                                     |             |               |                    |        |                  |         |       |                       |  |  |  |  |

| Address: FFE9H After reset: FFH R/W |             |               |                    |        |                  |         |       |                       |  |  |  |  |

| Symbol                              | <7>         | <6>           | <5>                | <4>    | <3>              | <2>     | <1>   | <0>                   |  |  |  |  |

| PR0H                                | TMPR010     | TMPR000       | TMPR50             | TMPRH0 | TMPRH1           | DUALPR0 | STPR6 | SRPR6                 |  |  |  |  |

|                                     |             |               |                    |        |                  | CSIPR10 |       |                       |  |  |  |  |

|                                     |             |               |                    |        |                  | STPR0   |       |                       |  |  |  |  |

|                                     |             |               |                    |        |                  |         |       |                       |  |  |  |  |

| Address: FFEAH After reset: FFH R/W |             |               |                    |        |                  |         |       |                       |  |  |  |  |

| Symbol                              | 7           | <6>           | <5>                | <4>    | <3>              | <2>     | <1>   | <0>                   |  |  |  |  |

| PR1L                                | 1           | PPR6          | WTPR               | KRPR   | TMPR51           | WTIPR   | SRPR0 | ADPR                  |  |  |  |  |

|                                     |             |               |                    |        |                  |         |       |                       |  |  |  |  |

| Address: FF                         | EBH After r | eset: FFH     | R/W                |        |                  |         |       |                       |  |  |  |  |

| Symbol                              | 7           | 6             | 5                  | 4      | 3                | 2       | 1     | <0>                   |  |  |  |  |

| PR1H                                | 1           | 1             | 1                  | 1      | 1                | 1       | 1     | IICPR0                |  |  |  |  |

|                                     |             |               |                    |        |                  |         |       | DMUPR <sup>Note</sup> |  |  |  |  |

|                                     |             | -             |                    |        |                  |         |       |                       |  |  |  |  |

|                                     | XXPRX       |               |                    | Prio   | rity level seled | ction   |       |                       |  |  |  |  |

|                                     | 0           | High priority | level              |        |                  |         |       |                       |  |  |  |  |

|                                     |             |               | Low priority level |        |                  |         |       |                       |  |  |  |  |

## Figure 20-14. Format of Priority Specification Flag Registers (PR0L, PR0H, PR1L, PR1H) (78K0/KD2)

Note Products whose flash memory is at least 48 KB only.

Caution Be sure to set bit 7 of PR1L and bits 1 to 7 of PR1H to 1.

## 27.9 Processing Time for Each Command When PG-FP4 or PG-FP5 Is Used (Reference)

The following table shows the processing time for each command (reference) when the PG-FP4 or PG-FP5 is used as a dedicated flash memory programmer.

## Table 27-12. Processing Time for Each Command When PG-FP4 or PG-FP5 Is Used (Reference) (1/2)

| Command of<br>PG-FP4 | Port: CSI-Internal-OSC<br>(Internal high-speed oscillation | Port: UART-Ext-FP4CK (External main system clock (f <sub>EXCLK</sub> )),<br>Speed: 115,200 bps |                   |  |  |  |

|----------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------|--|--|--|

|                      | clock (fвн)),<br>Speed: 2.5 MHz                            | Frequency: 2.0 MHz                                                                             | Frequency: 20 MHz |  |  |  |

| Signature            | 0.5 s (TYP.)                                               | 0.5 s (TYP.)                                                                                   | 0.5 s (TYP.)      |  |  |  |

| Blankcheck           | 0.5 s (TYP.)                                               | 0.5 s (TYP.)                                                                                   | 0.5 s (TYP.)      |  |  |  |

| Erase                | 0.5 s (TYP.)                                               | 0.5 s (TYP.)                                                                                   | 0.5 s (TYP.)      |  |  |  |

| Program              | 2.5 s (TYP.)                                               | 5 s (TYP.)                                                                                     | 5 s (TYP.)        |  |  |  |

| Verify               | 1.5 s (TYP.)                                               | 4 s (TYP.)                                                                                     | 3.5 s (TYP.)      |  |  |  |

| E.P.V                | 3.5 s (TYP.)                                               | 6 s (TYP.)                                                                                     | 6 s (TYP.)        |  |  |  |

| Checksum             | 0.5 s (TYP.)                                               | 0.5 s (TYP.)                                                                                   | 0.5 s (TYP.)      |  |  |  |

| Security             | 0.5 s (TYP.)                                               | 0.5 s (TYP.)                                                                                   | 0.5 s (TYP.)      |  |  |  |

(1) Products with internal ROMs of the 32 KB

(2) Products with internal ROMs of the 60 KB

| Command of<br>PG-FP4Port: CSI-Internal-OSC<br>(Internal high-speed oscillation<br>clock (fRH)),<br>Speed: 2.5 MHz |                    | Port: UART-Ext-FP4CK (External main system clock (fexclk)),<br>Speed: 115,200 bps |               |  |  |  |

|-------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------|---------------|--|--|--|

|                                                                                                                   | Frequency: 2.0 MHz | Frequency: 20 MHz                                                                 |               |  |  |  |

| Signature                                                                                                         | 0.5 s (TYP.)       | 0.5 s (TYP.)                                                                      | 0.5 s (TYP.)  |  |  |  |

| Blankcheck                                                                                                        | 1 s (TYP.)         | 1 s (TYP.)                                                                        | 1 s (TYP.)    |  |  |  |

| Erase                                                                                                             | 1 s (TYP.)         | 1 s (TYP.)                                                                        | 1 s (TYP.)    |  |  |  |

| Program                                                                                                           | 5 s (TYP.)         | 9 s (TYP.)                                                                        | 9 s (TYP.)    |  |  |  |

| Verify                                                                                                            | 2 s (TYP.)         | 6.5 s (TYP.)                                                                      | 6.5 s (TYP.)  |  |  |  |

| E.P.V                                                                                                             | 6 s (TYP.)         | 10.5 s (TYP.)                                                                     | 10.5 s (TYP.) |  |  |  |

| Checksum                                                                                                          | 0.5 s (TYP.)       | 1 s (TYP.)                                                                        | 1 s (TYP.)    |  |  |  |

| Security                                                                                                          | 0.5 s (TYP.)       | 0.5 s (TYP.)                                                                      | 0.5 s (TYP.)  |  |  |  |

## Caution When executing boot swapping, do not use the E.P.V. command with the dedicated flash memory programmer.

Caution The pins mounted depend on the product. Refer to Caution at the beginning of this chapter.

### A/D Converter Characteristics

(TA = -40 to +85°C, 2.3 V  $\leq$  AVREF  $\leq$  VDD = EVDD  $\leq$  5.5 V, Vss = EVss = AVss = 0 V)

| Parameter                                      | Symbol | Conditions                                                 |                                         | MIN. | TYP.  | MAX. | Unit |

|------------------------------------------------|--------|------------------------------------------------------------|-----------------------------------------|------|-------|------|------|

| Resolution                                     | Res    |                                                            |                                         |      | 10    | bit  |      |

| Overall error <sup>Notes 1, 2</sup>            | AINL   | $4.0~V \leq AV_{\text{REF}} \leq 5.5~V$                    |                                         |      |       | ±0.4 | %FSR |

|                                                |        | $2.7 \text{ V} \le \text{AV}_{\text{REF}} < 4.0 \text{ V}$ |                                         |      |       | ±0.6 | %FSR |

|                                                |        | $2.3 \text{ V} \leq AV_{\text{REF}} < 2.7$                 |                                         |      | ±1.2  | %FSR |      |

| Conversion time                                | tconv  | Conventional-                                              | $4.0~V \leq AV_{\text{REF}} \leq 5.5~V$ | 6.1  |       | 36.7 | μs   |

|                                                |        | specification                                              | $2.7~V \leq AV_{\text{REF}} < 4.0~V$    | 12.2 |       | 36.7 | μs   |

|                                                |        | Products<br>(µPD78F05xx(A))                                | $2.3~V \leq AV_{\text{REF}} < 2.7~V$    | 27   |       | 66.6 | μS   |

|                                                |        | Expanded-                                                  | $4.0~V \leq AV_{\text{REF}} \leq 5.5~V$ | 6.1  |       | 66.6 | μs   |

|                                                |        | specification                                              | $2.7~V \leq AV_{\text{REF}} < 4.0~V$    | 12.2 |       | 66.6 | μs   |

|                                                |        | Products<br>(µPD78F05xxA(A))                               | $2.3~V \leq AV_{\text{REF}} < 2.7~V$    | 27   |       | 66.6 | μS   |

| Zero-scale error <sup>Notes 1, 2</sup>         | Ezs    | $4.0~V \leq AV_{\text{REF}} \leq 5.5~V$                    |                                         |      |       | ±0.4 | %FSR |

|                                                |        | $2.7~V \leq AV_{\text{REF}} < 4.0~V$                       |                                         |      |       | ±0.6 | %FSR |

|                                                |        | $2.3~V \leq AV_{\text{REF}} < 2.7$                         |                                         |      | ±0.6  | %FSR |      |

| Full-scale error <sup>Notes 1, 2</sup>         | Efs    | $4.0~V \leq AV_{\text{REF}} \leq 5.5$                      |                                         |      | ±0.4  | %FSR |      |

|                                                |        | $2.7~V \leq AV_{\text{REF}} < 4.0~V$                       |                                         |      |       | ±0.6 | %FSR |

|                                                |        | $2.3~V \leq AV_{\text{REF}} < 2.7~V$                       |                                         |      |       | ±0.6 | %FSR |

| Integral non-linearity error <sup>Note 1</sup> | lιε    | $4.0~V \leq AV_{\text{REF}} \leq 5.5~V$                    |                                         |      |       | ±2.5 | LSB  |

|                                                |        | $2.7~V \leq AV_{\text{REF}} < 4.0~V$                       |                                         |      |       | ±4.5 | LSB  |

|                                                |        | $2.3~V \leq AV_{\text{REF}} < 2.7~V$                       |                                         |      |       | ±6.5 | LSB  |

| Differential non-linearity error Note 1        | Dle    | $4.0~V \leq AV_{\text{REF}} \leq 5.5$                      | 5 V                                     |      |       | ±1.5 | LSB  |

|                                                |        | $2.7 \text{ V} \leq AV_{\text{REF}} < 4.0 \text{ V}$       |                                         |      |       | ±2.0 | LSB  |

|                                                |        | $2.3~V \leq AV_{\text{REF}} < 2.7$                         |                                         |      | ±2.0  | LSB  |      |

| Analog input voltage                           | VAIN   |                                                            | AVss                                    |      | AVREF | V    |      |

**Notes 1.** Excludes quantization error ( $\pm 1/2$  LSB).

2. This value is indicated as a ratio (%FSR) to the full-scale value.

## Caution The pins mounted depend on the product. Refer to Caution at the beginning of this chapter.

## DC Characteristics (4/4)

| Parameter                           | Symbol                 | Conditions                                                                            |                                                                                     |                      | MIN. | TYP. | MAX. | Unit |

|-------------------------------------|------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------|------|------|------|------|

| Supply current <sup>Note 1</sup>    | IDD1                   | Operating<br>mode                                                                     | fxн = 20 MHz,                                                                       | Square wave input    |      | 3.2  | 7.2  | mA   |

|                                     |                        |                                                                                       | $V_{\text{DD}} = 5.0 \text{ V}^{\text{Note 2}}$                                     | Resonator connection |      | 4.5  | 9.0  | mA   |

|                                     |                        |                                                                                       | fхн = 10 MHz,                                                                       | Square wave input    |      | 1.6  | 3.7  | mA   |

|                                     |                        |                                                                                       | $V_{DD} = 5.0 \ V^{Notes 2, 3}$                                                     | Resonator connection |      | 2.3  | 5.1  | mA   |

|                                     |                        |                                                                                       | fхн = 10 MHz                                                                        | Square wave input    |      | 1.5  | 3.6  | mA   |

|                                     |                        |                                                                                       | $V_{DD} = 3.0 \ V^{Notes 2, 3}$                                                     | Resonator connection |      | 2.2  | 4.2  | mA   |

|                                     |                        |                                                                                       | fхн = 5 MHz,                                                                        | Square wave input    |      | 0.9  | 2.1  | mA   |

|                                     |                        |                                                                                       | $V_{DD} = 3.0 V^{Notes 2, 3}$                                                       | Resonator connection |      | 1.3  | 2.6  | mA   |

|                                     |                        |                                                                                       | f <sub>RH</sub> = 8 MHz, V <sub>DD</sub> = 5.0 V <sup>Note 4</sup>                  |                      |      | 1.4  | 3.3  | mA   |

|                                     |                        |                                                                                       | fsuв = 32.768 kHz,                                                                  | Square wave input    |      | 6    | 93   | μA   |

|                                     |                        |                                                                                       | $V_{\text{DD}} = 5.0 \text{ V}^{\text{Note 5}}$                                     | Resonator connection |      | 15   | 100  | μA   |

|                                     | Idd2                   | HALT<br>mode                                                                          | fхн = 20 MHz,                                                                       | Square wave input    |      | 0.8  | 3.4  | mA   |

|                                     |                        |                                                                                       | $V_{\text{DD}} = 5.0 \text{ V}^{\text{Note 2}}$                                     | Resonator connection |      | 2.0  | 5.8  | mA   |

|                                     |                        |                                                                                       | fхн = 10 MHz,                                                                       | Square wave input    |      | 0.4  | 1.7  | mA   |

|                                     |                        |                                                                                       | $V_{DD} = 5.0 \ V^{Notes 2, 3}$                                                     | Resonator connection |      | 1.0  | 3.2  | mA   |

|                                     |                        |                                                                                       | fхн = 5 MHz,                                                                        | Square wave input    |      | 0.2  | 0.85 | mA   |

|                                     |                        |                                                                                       | $V_{\text{DD}} = 3.0 \ V^{\text{Notes 2, 3}}$                                       | Resonator connection |      | 0.5  | 1.5  | mA   |

|                                     |                        |                                                                                       | $f_{\text{RH}}=8 \text{ MHz}, \text{ V}_{\text{DD}}=5.0 \text{ V}^{\text{ Note 4}}$ |                      |      | 0.4  | 1.6  | mA   |

|                                     |                        |                                                                                       | fsuв = 32.768 kHz,                                                                  | Square wave input    |      | 3.0  | 89   | μA   |

|                                     |                        |                                                                                       | $V_{\text{DD}} = 5.0 \text{ V}^{\text{Note 5}}$                                     | Resonator connection |      | 12   | 93   | μA   |

|                                     | DD3 <sup>Note 6</sup>  | STOP mode<br>T <sub>A</sub> = -40 to +70 °C                                           |                                                                                     |                      | 1    | 60   | μA   |      |

|                                     |                        |                                                                                       |                                                                                     |                      | 1    | 10   | μA   |      |

| A/D converter<br>operating current  | IADC <sup>Note 7</sup> | $2.7 \text{ V} \le \text{AV}_{\text{REF}} \le \text{V}_{\text{DD}}, \text{ ADCS} = 1$ |                                                                                     |                      |      | 0.86 | 2.5  | mA   |

| Watchdog timer<br>operating current | WDT <sup>Note 8</sup>  | During 240 kHz internal low-speed oscillation clock operation                         |                                                                                     |                      |      | 5    | 13   | μA   |

| LVI operating current               | LVI Note 9             |                                                                                       |                                                                                     |                      |      |      | 24   | μA   |

Remarks 1. fxH: High-speed system clock frequency (X1 clock oscillation frequency or external main system clock frequency)

2. free: Internal high-speed oscillation clock frequency

3. fsub: Subsystem clock frequency (XT1 clock oscillation frequency or external subsystem clock frequency)

(Notes on next page)

## Caution The pins mounted depend on the product. Refer to Caution at the beginning of this chapter.

## DC Characteristics (3/4)

(TA = -40 to +125°C, 2.7 V  $\leq$  VDD = EVDD  $\leq$  5.5 V, AVREF  $\leq$  VDD, VSS = EVSS = AVSS = 0 V)

| Parameter                      | Symbol                 | Conditions                                                                                                                       |                                                                                                                                          |                                                                                                                                 | MIN. | TYP. | MAX.               | Unit |

|--------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------|------|--------------------|------|

| Output voltage, low            | Vol1                   | P30 to P33, P40 to P47,                                                                                                          |                                                                                                                                          | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ I_{\text{OL1}} = 4.0 \ mA \end{array} \end{array} \label{eq:VDD}$ |      |      | 0.7                | V    |

|                                |                        | P50 to P57, P64 to P67,<br>P70 to P77, P120, P130,<br>P140 to P145                                                               | $\begin{array}{l} 2.7 \ V \leq V_{\text{DD}} < 4.0 \ V, \\ I_{\text{OL1}} = 2.0 \ mA \end{array}$                                        |                                                                                                                                 |      |      | 0.7                | V    |

|                                | Vol2                   | P20 to P27                                                                                                                       | $AV_{REF} = V_{DD},$<br>Iol2 = 0.4 mA                                                                                                    |                                                                                                                                 |      |      | 0.4                | V    |

|                                |                        | P121 to P124 IoL2 = 0.4 mA                                                                                                       |                                                                                                                                          |                                                                                                                                 |      | 0.4  | V                  |      |

|                                | Vol3                   | P60 to P63                                                                                                                       | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ I_{\text{OL1}} = 8.0 \ mA \end{array} \end{array} \label{eq:eq:electropy}$ |                                                                                                                                 |      |      | 2.0                | V    |

|                                |                        |                                                                                                                                  | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ I_{\text{OL1}} = 2.0 \ mA \end{array} \label{eq:DD}$                       |                                                                                                                                 |      |      | 0.6                | V    |

|                                |                        |                                                                                                                                  | $\begin{array}{l} 2.7 \ V \leq V_{\text{DD}} < 4.0 \ V, \\ I_{\text{OL1}} = 2.0 \ mA \end{array}$                                        |                                                                                                                                 |      |      | 0.6                | V    |

| Input leakage current,<br>high | Цінт                   | P00 to P06, P10 to P17,<br>P30 to P33, P40 to P47,<br>P50 to P57, P60 to P67,<br>P70 to P77, P120, P140 to<br>P145, FLMD0, RESET | VI = VDD                                                                                                                                 |                                                                                                                                 |      |      | 5                  | μA   |

|                                | ILIH2                  | P20 to P27 VI = AVREF = VDD                                                                                                      |                                                                                                                                          |                                                                                                                                 |      | 5    | μA                 |      |

|                                | Ілнз                   | P121 to 124                                                                                                                      | VI =                                                                                                                                     | I/O port mode                                                                                                                   |      |      | 5                  | μA   |

|                                |                        | (X1, X2, XT1, XT2)                                                                                                               | VDD                                                                                                                                      | OSC mode                                                                                                                        |      |      | 20                 | μA   |

| Input leakage current, low     | Ilil1                  | P00 to P06, P10 to P17,<br>P30 to P33, P40 to P47,<br>P50 to P57, P60 to P67,<br>P70 to P77, P120, P140 to<br>P145, FLMD0, RESET | Vi = Vss                                                                                                                                 |                                                                                                                                 |      |      | -5                 | μA   |

|                                |                        | P20 to P27 VI = Vss, AVREF = VDD                                                                                                 |                                                                                                                                          |                                                                                                                                 |      | -5   | μA                 |      |

|                                | Ililis                 | P121 to 124<br>(X1, X2, XT1, XT2)                                                                                                | Vı =                                                                                                                                     | I/O port mode                                                                                                                   |      |      | -5                 | μA   |

|                                |                        |                                                                                                                                  | Vss                                                                                                                                      | OSC mode                                                                                                                        |      |      | -20                | μA   |

| Pull-up resistor               | p resistor Ru Vi = Vss |                                                                                                                                  |                                                                                                                                          | 10                                                                                                                              | 20   | 100  | kΩ                 |      |

| FLMD0 supply voltage           | VIL                    | In normal operation mode                                                                                                         |                                                                                                                                          |                                                                                                                                 | 0    |      | 0.2V <sub>DD</sub> | V    |

|                                | VIH                    | In self-programming mode                                                                                                         |                                                                                                                                          |                                                                                                                                 |      |      | VDD                | V    |

Remark Unless specified otherwise, the characteristics of alternate-function pins are the same as those of port pins.