# E·X Renesas Electronics America Inc - <u>UPD78F0533AGK-GAJ-AX Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | 78K/0                                                                                 |

| Core Size                  | 8-Bit                                                                                 |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                                    |

| Number of I/O              | 55                                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 1K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 8x10b                                                                             |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 64-LQFP                                                                               |

| Supplier Device Package    | -                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0533agk-gaj-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

| CHAPTE | R 10 WATCH TIMER                                            |     |

|--------|-------------------------------------------------------------|-----|

| 10.1   | Functions of Watch Timer                                    |     |

| 10.2   | Configuration of Watch Timer                                |     |

| 10.3   | Register Controlling Watch Timer                            |     |

| 10.4   | Watch Timer Operations                                      |     |

|        | 10.4.1 Watch timer operation                                |     |

|        | 10.4.2 Interval timer operation                             |     |

| 10.5   | Cautions for Watch Timer                                    |     |

| СНАРТЕ | R 11 WATCHDOG TIMER                                         |     |

|        | Functions of Watchdog Timer                                 |     |

| 11.2   | Configuration of Watchdog Timer                             |     |

| 11.3   | Register Controlling Watchdog Timer                         |     |

| 11.4   | Operation of Watchdog Timer                                 | 399 |

|        | 11.4.1 Controlling operation of watchdog timer              |     |

|        | 11.4.2 Setting overflow time of watchdog timer              | 400 |

|        | 11.4.3 Setting window open period of watchdog timer         |     |

| СНАРТЕ | R 12 CLOCK OUTPUT/BUZZER OUTPUT CONTROLLER                  | 403 |

| 12.1   | Functions of Clock Output/Buzzer Output Controller          |     |

|        | Configuration of Clock Output/Buzzer Output Controller      |     |

|        | Registers Controlling Clock Output/Buzzer Output Controller |     |

|        | Operations of Clock Output/Buzzer Output Controller         |     |

|        | 12.4.1 Operation as clock output                            |     |

|        | 12.4.2 Operation as buzzer output                           |     |

| СНАРТЕ | R 13 A/D CONVERTER                                          | 409 |

| 13 1   | Function of A/D Converter                                   | 409 |

|        | Configuration of A/D Converter                              |     |

|        | Registers Used in A/D Converter                             |     |

|        | A/D Converter Operations                                    |     |

|        | 13.4.1 Basic operations of A/D converter                    |     |

|        | 13.4.2 Input voltage and conversion results                 |     |

|        | 13.4.3 A/D converter operation mode                         |     |

| 13.5   | How to Read A/D Converter Characteristics Table             |     |

|        | Cautions for A/D Converter                                  |     |

| СНАРТЕ | R 14 SERIAL INTERFACE UART0                                 |     |

| 14 1   | Functions of Serial Interface UART0                         | 432 |

|        | Configuration of Serial Interface UART0                     |     |

|        | Registers Controlling Serial Interface UART0                |     |

|        | Operation of Serial Interface UART0                         |     |

| 17.4   | 14.4.1 Operation stop mode                                  |     |

|        | 14.4.1 Operation stop mode                                  |     |

|        | 14.4.2 Asynchronous senai menace (OART) mode                |     |

|        | 14.4.4 Calculation of baud rate                             |     |

|        |                                                             |     |

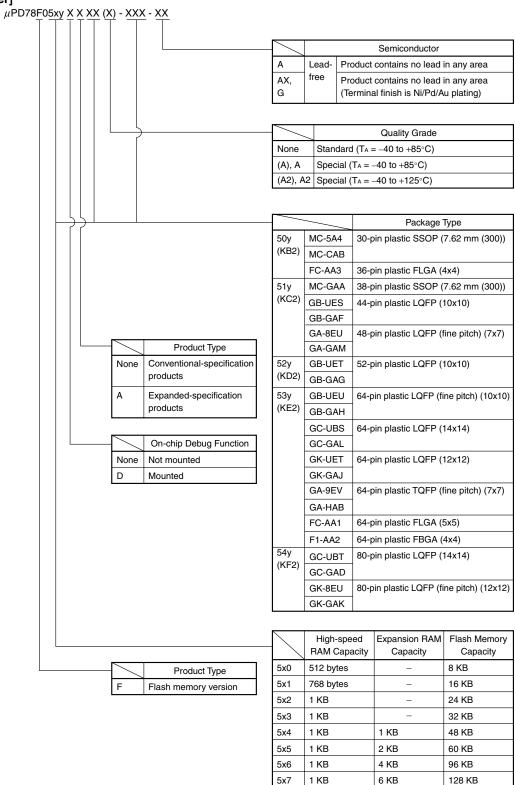

# 1.4 Ordering Information

#### [Part Number]

Please refer to "Quality Grades on NEC Semiconductor Devices" (Document No. C11531E) published by Renesas Electronics to know the specification of quality grade on the devices and its recommended applications.

## 2.1.2 78K0/KC2

# (1) Port functions (1/2): 78K0/KC2

| Function Name                                 | I/O | Function                                                                                                                                                                   | After Reset  | Alternate Function                              |  |

|-----------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------------------------------|--|

| P00                                           | I/O | Port 0.                                                                                                                                                                    | Input port   | TI000                                           |  |

| P01                                           |     | <ul><li>2-bit I/O port.</li><li>Input/output can be specified in 1-bit units.</li><li>Use of an on-chip pull-up resistor can be specified by a software setting.</li></ul> |              | TI010/TO00                                      |  |

| P10                                           | I/O | Port 1.                                                                                                                                                                    | Input port   | SCK10/TxD0                                      |  |

| P11                                           |     | 8-bit I/O port.                                                                                                                                                            |              | SI10/RxD0                                       |  |

| P12                                           |     | Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a software                                                         |              | SO10                                            |  |

| P13                                           |     | setting.                                                                                                                                                                   |              | TxD6                                            |  |

| P14                                           |     |                                                                                                                                                                            |              | RxD6                                            |  |

| P15                                           |     |                                                                                                                                                                            |              | ТОН0                                            |  |

| P16                                           |     |                                                                                                                                                                            |              | TOH1/INTP5                                      |  |

| P17                                           |     |                                                                                                                                                                            |              | TI50/TO50                                       |  |

| P20 to P25                                    | I/O | Port 2.                                                                                                                                                                    | Analog input | ANI0 to ANI5                                    |  |

| P26 <sup>Note 1</sup> , P27 <sup>Note 1</sup> |     | 8-bit I/O port.<br>Input/output can be specified in 1-bit units.                                                                                                           |              | ANI6 <sup>Note 1</sup> , ANI7 <sup>Note 1</sup> |  |

| P30                                           | I/O | Port 3.                                                                                                                                                                    | Input port   | INTP1                                           |  |

| P31                                           |     | 4-bit I/O port.<br>Input/output can be specified in 1-bit units.                                                                                                           |              | INTP2/OCD1ANote 2                               |  |

| P32                                           |     | Use of an on-chip pull-up resistor can be specified by a software                                                                                                          |              | INTP3/OCD1B <sup>Note 2</sup>                   |  |

| P33                                           |     | setting.                                                                                                                                                                   |              | TI51/TO51/INTP4                                 |  |

| P40 <sup>Note 1</sup> , P41 <sup>Note 1</sup> | I/O | Port 4.<br>2-bit I/O port.<br>Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a software<br>setting.               | Input port   | -                                               |  |

| P60                                           | I/O | Port 6.                                                                                                                                                                    | Input port   | SCL0                                            |  |

| P61                                           |     | 4-bit I/O port.                                                                                                                                                            |              | SDA0                                            |  |

| P62                                           |     | Output of P60 to P63 is N-ch open-drain output (6 V tolerance).<br>Input/output can be specified in 1-bit units.                                                           |              | EXSCL0                                          |  |

| P63                                           |     |                                                                                                                                                                            |              |                                                 |  |

| P70, P71                                      | I/O | Port 7.                                                                                                                                                                    | Input port   | KR0, KR1                                        |  |

| P72 <sup>Note 1</sup> , P73 <sup>Note 1</sup> |     | 6-bit I/O port.                                                                                                                                                            |              | KR2 <sup>Note 1</sup> , KR3 <sup>Note 1</sup>   |  |

| P74 <sup>Note 3</sup> , P75 <sup>Note 3</sup> |     | Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a software<br>setting.                                             |              | -                                               |  |

## Notes 1. 44-pin and 48-pin products only

For the 38-pin products, be sure to set bits 6 and 7 of PM2 to "1", and bits 0 and 1 of PM4, bits 2 and 3 of PM7, bits 6 and 7 of P2, bits 0 and 1 of P4, and bits 2 and 3 of P7 to "0".

- 2.  $\mu$ PD78F0513D, 78F0513DA, 78F0515D and 78F0515DA (product with on-chip debug function) only

- 3. 48-pin products only

| KB2          | KC2          | KD2          | KES          | KF2          | Function<br>Name | I/O | Function                                                                                                | After<br>Reset | Alternate<br>Function             |

|--------------|--------------|--------------|--------------|--------------|------------------|-----|---------------------------------------------------------------------------------------------------------|----------------|-----------------------------------|

| $\checkmark$ |              |              | $\checkmark$ |              | P00              | I/O | Port 0.                                                                                                 | Input          | TI000                             |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | P01              |     | I/O port.                                                                                               | port           | TI010/TO00                        |

| -            | -            | Note 1       | Note 2       | $\checkmark$ | P02              |     | Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by |                | SO11                              |

| -            | -            | Note 1       | Note 2       | $\checkmark$ | P03              |     | a software setting.                                                                                     |                | SI11                              |

| -            | -            | _            | Note 2       | $\checkmark$ | P04              |     |                                                                                                         |                | SCK11                             |

| -            | -            | _            | Note 2       | $\checkmark$ | P05              |     |                                                                                                         |                | TI001/SSI11                       |

| _            | -            | -            | Note 2       | $\checkmark$ | P06              |     |                                                                                                         |                | TI011/TO01                        |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | P10              | I/O | Port 1.                                                                                                 | Input          | SCK10/TxD0                        |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | P11              |     | I/O port.                                                                                               | port           | SI10/RxD0                         |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              | P12              |     | Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by |                | SO10                              |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | P13              |     | a software setting.                                                                                     |                | TxD6                              |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | P14              |     |                                                                                                         |                | RxD6                              |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | P15              |     |                                                                                                         |                | ТОН0                              |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | P16              |     |                                                                                                         |                | TOH1/INTP5                        |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | P17              |     |                                                                                                         |                | TI50/TO50                         |

| $\checkmark$ | $\checkmark$ |              | $\checkmark$ |              | P20              | I/O | Port 2.                                                                                                 | Analog         | ANI0                              |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | P21              |     | I/O port.                                                                                               | input          | ANI1                              |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | P22              |     | Input/output can be specified in 1-bit units.                                                           |                | ANI2                              |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | P23              |     |                                                                                                         |                | ANI3                              |

| -            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | P24              |     |                                                                                                         |                | ANI4                              |

| _            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | P25              |     |                                                                                                         |                | ANI5                              |

| _            | Note 3       | $\checkmark$ | $\checkmark$ | $\checkmark$ | P26              |     |                                                                                                         |                | ANI6                              |

| -            | Note 3       | $\checkmark$ | $\checkmark$ | $\checkmark$ | P27              |     |                                                                                                         |                | ANI7                              |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | P30              | I/O | Port 3.                                                                                                 | Analog         | INTP1                             |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | P31              |     | I/O port.<br>Input/output can be specified in 1-bit units.                                              | input          | INTP2/<br>OCD1A <sup>Note 4</sup> |

| V            | V            | V            | V            | V            | P32              |     | Use of an on-chip pull-up resistor can be specified by a software setting.                              |                | INTP3/<br>OCD1B <sup>Note 4</sup> |

| V            | V            | V            | $\checkmark$ | $\checkmark$ | P33              |     |                                                                                                         |                | TI51/TO51/<br>INTP4               |

Table 5-3.

Port Functions (1/3)

Notes 1. The 78K0/KD2 products are only provided with port functions (P02 and P03) and not alternate functions.

- 2. The 78K0/KE2 products whose flash memory is less than 32 KB are only provided with port functions (P02 to P06) and not alternate functions. The 78K0/KE2 products whose flash memory is at least 48 KB are provided with port functions (P02 to P06) and alternate functions.

- **3.** This is not mounted onto 38-pin products of the 78K0/KC2. For the 38-pin products, be sure to set bits 6 and 7 of PM2 to "1" and bits 6 and 7 of P2 to "0".

- **4.** OCD1A and OCD1B are provided to the products with an on-chip debug function (μPD78F05xxD and 78F05xxDA) only.

**Remark**  $\sqrt{:}$  Mounted, -: Not mounted

| Pin Name   | Alternate Function     | PM××   | P×× |   |

|------------|------------------------|--------|-----|---|

|            | Function Name          | I/O    |     |   |

| P30 to P32 | INTP1 to INTP3         | Input  | 1   | × |

| P33        | INTP4                  | Input  | 1   | × |

|            | TI51                   | Input  | 1   | × |

|            | TO51                   | Output | 0   | 0 |

| P60        | SCL0                   | I/O    | 0   | 0 |

| P61        | SDA0                   | I/O    | 0   | 0 |

| P62        | EXSCL0                 | Input  | 1   | × |

| P70 to P77 | KR0 to KR7             | Input  | 1   | × |

| P120       | INTP0                  | Input  | 1   | × |

|            | EXLVI                  | Input  | 1   | × |

| P121       | X1 <sup>Note</sup>     | -      | ×   | × |

| P122       | X2 <sup>Note</sup>     | _      | х   | × |

|            | EXCLK <sup>Note</sup>  | Input  | ×   | × |

| P123       | XT1 <sup>Note</sup>    | -      | ×   | × |

| P124       | XT2 <sup>Note</sup>    | -      | ×   | × |

|            | EXCLKS <sup>Note</sup> | Input  | ×   | × |

| P140       | PCL                    | Output | 0   | 0 |

|            | INTP6                  | Input  | 1   | × |

| P141       | BUZ                    | Output | 0   | 0 |

|            | INTP7                  | Input  | 1   | × |

|            | BUSY0                  | Input  | 1   | × |

| P142       | SCKAO                  | Input  | 1   | × |

|            |                        | Output | 0   | 1 |

| P143       | SIA0                   | Input  | 1   | × |

| P144       | SOA0                   | Output | 0   | 0 |

| P145       | STB0                   | Output | 0   | 0 |

Table 5-6. Settings of Port Mode Register and Output Latch When Using Alternate Function (2/2)

- Note When using the P121 to P124 pins to connect a resonator for the main system clock (X1, X2) or subsystem clock (XT1, XT2), or to input an external clock for the main system clock (EXCLK) or subsystem clock (EXCLKS), the X1 oscillation mode, XT1 oscillation mode, or external clock input mode must be set by using the clock operation mode select register (OSCCTL) (for details, see 6.3 (1) Clock operation mode select register (OSCCTL) and (3) Setting of operation mode for subsystem clock pin). The reset value of OSCCTL is 00H (all of the P121 to P124 are I/O port pins). At this time, setting of PM121 to PM124 and P121 to P124 is not necessary.

- Remarks 1. ×: Don't care

- PM××: Port mode register

- Pxx: Port output latch

- X1, X2, P31, and P32 of the product with an on-chip debug function (μPD78F05xxD and 78F05xxDA) can be used as on-chip debug mode setting pins (OCD0A, OCD0B, OCD1A, and OCD1B) when the on-chip debug function is used. For how to connect an on-chip debug emulator (QB-MINI2), see CHAPTER 28 ON-CHIP DEBUG FUNCTION (μPD78F05xxD AND 78F05xxDA ONLY).

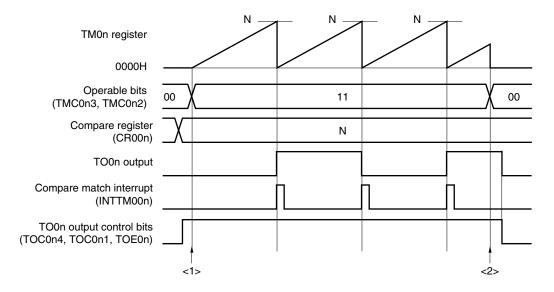

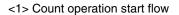

#### Figure 7-26. Example of Software Processing in External Event Counter Mode

<2> Count operation stop flow

The counter is initialized and counting is stopped by clearing the TMC0n3 and TMC0n2 bits to 00.

Note Care must be exercised when setting TOC0n. For details, see 7.3 (3) 16-bit timer output control register 0n (TOC0n).

$\label{eq:Remark} \begin{array}{ll} \textbf{Remark} & \textbf{n} = 0 \text{:} & 78 \text{K0/KE2} \text{ products whose flash memory is less than 32 KB, and 78 K0/KB2, 78 K0/KC2, } \\ & 78 \text{K0/KD2 products} \end{array}$

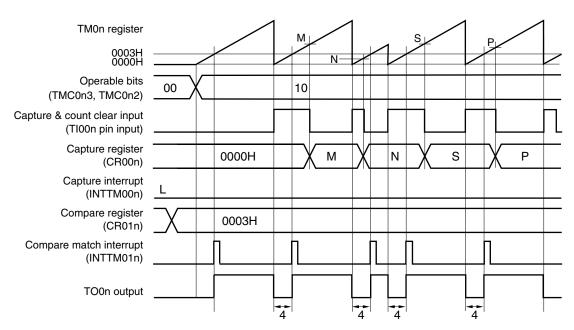

# Figure 7-32. Timing Example of Clear & Start Mode Entered by TI00n Pin Valid Edge Input (CR00n: Capture Register, CR01n: Compare Register) (2/2)

#### (b) TOC0n = 13H, PRM0n = 10H, CRC0n, = 03H, TMC0n = 0AH, CR01n = 0003H

This is an application example where the width set to CR01n (4 clocks in this example) is to be output from the TO0n pin when the count value has been captured & cleared.

TM0n is cleared (to 0000H) at the rising edge detection of the TI00n pin and captured to CR00n at the falling edge detection of the TI00n pin. The TO0n output level is inverted when TM0n is cleared (to 0000H) because the rising edge of the TI00n pin has been detected or when the value of TM0n matches that of a compare register (CR01n). When bit 1 (CRC0n1) of capture/compare control register 0n (CRC0n) is 1, the count value of TM0n is captured to CR00n in the phase reverse to that of the input signal of the TI00n pin, but the capture interrupt signal (INTTM00n) is not generated. However, the INTTM00n interrupt is generated when the valid edge of the TI01n pin is detected. Mask the INTTM00n signal when it is not used.

# **Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

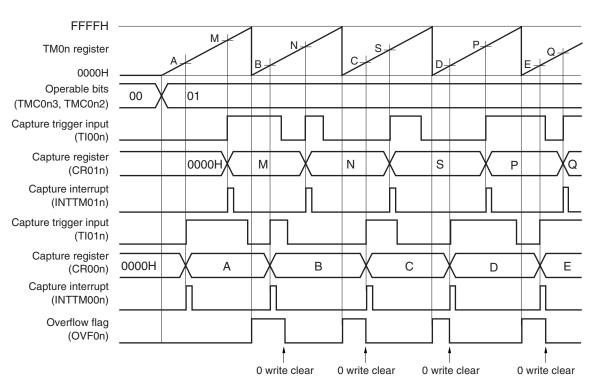

# Figure 7-42. Timing Example of Free-Running Timer Mode (CR00n: Capture Register, CR01n: Capture Register) (1/2)

(a) TOC0n = 13H, PRM0n = 50H, CRC0n = 05H, TMC0n = 04H

This is an application example where the count values that have been captured at the valid edges of separate capture trigger signals are stored in separate capture registers in the free-running timer mode.

The count value is captured to CR01n when the valid edge of the TI00n pin input is detected and to CR00n when the valid edge of the TI01n pin input is detected.

$\label{eq:Remark} \begin{array}{ll} \textbf{Remark} & \textbf{n}=0; & 78 \text{K0/KE2} \ \text{products} \ \text{whose flash memory is less than 32 KB, and 78 K0/KB2, 78 K0/KC2,} \\ & 78 \text{K0/KD2} \ \text{products} \end{array}$

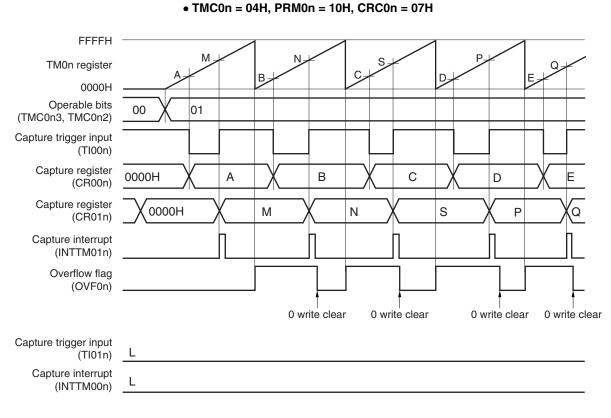

#### (2) Measuring the pulse width by using one input signal of the TI00n pin (free-running timer mode)

Set the free-running timer mode (TMC0n3 and TMC0n2 = 01). The count value of TM0n is captured to CR00n in the phase reverse to the valid edge detected on the Tl00n pin. When the valid edge of the Tl00n pin is detected, the count value of TM0n is captured to CR01n.

By this measurement method, values are stored in separate capture registers when a width from one edge to another is measured. Therefore, the capture values do not have to be saved. By subtracting the value of one capture register from that of another, a high-level width, low-level width, and cycle are calculated.

If an overflow occurs, the value becomes negative if one captured value is simply subtracted from another and, therefore, a borrow occurs (bit 0 (CY) of the program status word (PSW) is set to 1). If this happens, ignore CY and take the calculated value as the pulse width. In addition, clear bit 0 (OVF0n) of 16-bit timer mode control register 0n (TMC0n) to 0.

Figure 7-54. Timing Example of Pulse Width Measurement (2)

**Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

#### (3) Port mode registers 1 and 3 (PM1, PM3)

These registers set port 1 and 3 input/output in 1-bit units.

When using the P17/TO50/TI50 and P33/TO51/TI51/INTP4 pins for timer output, clear PM17 and PM33 and the output latches of P17 and P33 to 0.

When using the P17/TO50/TI50 and P33/TO51/TI51/INTP4 pins for timer input, set PM17 and PM33 to 1. The output latches of P17 and P33 at this time may be 0 or 1.

PM1 and PM3 can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets these registers to FFH.

#### Figure 8-9. Format of Port Mode Register 1 (PM1)

| Address: | FF21H | After reset: FI | H R/W |      |      |      |      |      |

|----------|-------|-----------------|-------|------|------|------|------|------|

| Symbol   | 7     | 6               | 5     | 4    | 3    | 2    | 1    | 0    |

| PM1      | PM17  | PM16            | PM15  | PM14 | PM13 | PM12 | PM11 | PM10 |

|          |       |                 |       |      |      |      |      |      |

| PM1n | P1n pin I/O mode selection (n = 0 to 7) |  |  |  |  |  |  |

|------|-----------------------------------------|--|--|--|--|--|--|

| 0    | Dutput mode (output buffer on)          |  |  |  |  |  |  |

| 1    | Input mode (output buffer off)          |  |  |  |  |  |  |

#### Figure 8-10. Format of Port Mode Register 3 (PM3)

| Address: F | F23H | After reset: FF | H R/W |   |      |      |      |      |

|------------|------|-----------------|-------|---|------|------|------|------|

| Symbol     | 7    | 6               | 5     | 4 | 3    | 2    | 1    | 0    |

| PM3        | 1    | 1               | 1     | 1 | PM33 | PM32 | PM31 | PM30 |

| PM3n | P3n pin I/O mode selection (n = 0 to 3) |  |  |  |  |  |  |

|------|-----------------------------------------|--|--|--|--|--|--|

| 0    | Dutput mode (output buffer on)          |  |  |  |  |  |  |

| 1    | Input mode (output buffer off)          |  |  |  |  |  |  |

**Remark** LIN stands for Local Interconnect Network and is a low-speed (1 to 20 kbps) serial communication protocol intended to aid the cost reduction of an automotive network.

LIN communication is single-master communication, and up to 15 slaves can be connected to one master.

The LIN slaves are used to control the switches, actuators, and sensors, and these are connected to the LIN master via the LIN network.

Normally, the LIN master is connected to a network such as CAN (Controller Area Network).

In addition, the LIN bus uses a single-wire method and is connected to the nodes via a transceiver that complies with ISO9141.

In the LIN protocol, the master transmits a frame with baud rate information and the slave receives it and corrects the baud rate error. Therefore, communication is possible when the baud rate error in the slave is  $\pm 15\%$  or less.

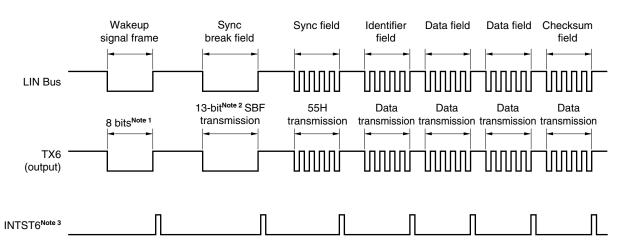

Figures 15-1 and 15-2 outline the transmission and reception operations of LIN.

Figure 15-1. LIN Transmission Operation

Notes 1. The wakeup signal frame is substituted by 80H transmission in the 8-bit mode.

The sync break field is output by hardware. The output width is the bit length set by bits 4 to 2 (SBL62 to SBL60) of asynchronous serial interface control register 6 (ASICL6) (see 15.4.2 (2) (h) SBF transmission).

**3.** INTST6 is output on completion of each transmission. It is also output when SBF is transmitted.

Remark The interval between each field is controlled by software.

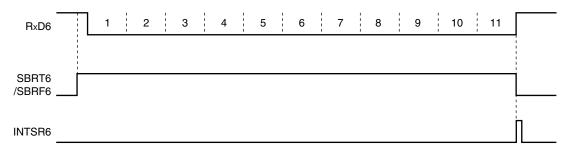

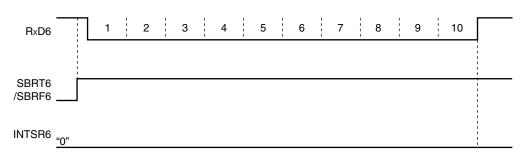

#### (i) SBF reception

When the device is used in LIN communication operation, the SBF (Synchronous Break Field) reception control function is used for reception. For the reception operation of LIN, see **Figure 15-2 LIN Reception Operation**. Reception is enabled when bit 7 (POWER6) of asynchronous serial interface operation mode register 6 (ASIM6) is set to 1 and then bit 5 (RXE6) of ASIM6 is set to 1. SBF reception is enabled when bit 6 (SBRT6) of asynchronous serial interface control register 6 (ASICL6) is set to 1. In the SBF reception enabled status, the

RxD6 pin is sampled and the start bit is detected in the same manner as the normal reception enable status. When the start bit has been detected, reception is started, and serial data is sequentially stored in the receive shift register 6 (RXS6) at the set baud rate. When the stop bit is received and if the width of SBF is 11 bits or more, a reception completion interrupt request (INTSR6) is generated as normal processing. At this time, the SBRF6 and SBRT6 bits are automatically cleared, and SBF reception ends. Detection of errors, such as OVE6, PE6, and FE6 (bits 0 to 2 of asynchronous serial interface reception error status register 6 (ASIS6)) is suppressed, and error detection processing of UART communication is not performed. In addition, data transfer between receive shift register 6 (RXS6) and receive buffer register 6 (RXB6) is not performed, and the reset value of FFH is retained. If the width of SBF is 10 bits or less, an interrupt does not occur as error processing after the stop bit has been received, and the SBF reception mode is restored. In this case, the SBRF6 and SBRT6 bits are not cleared.

#### Figure 15-23. SBF Reception

#### 1. Normal SBF reception (stop bit is detected with a width of more than 10.5 bits)

#### 2. SBF reception error (stop bit is detected with a width of 10.5 bits or less)

**Remark** RxD6: RxD6 pin (input)

SBRT6: Bit 6 of asynchronous serial interface control register 6 (ASICL6)

- SBRF6: Bit 7 of ASICL6

- INTSR6: Reception completion interrupt request

<R>

#### Figure 18-5. Format of IIC Control Register 0 (IICC0) (4/4)

| SPT0                                 |                                                                  | Stop condition trigger                                                                                                                                                                                                                                              |                                                                                     |  |  |  |  |

|--------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|--|--|--|

| 0                                    | Stop condition                                                   | s not generated.                                                                                                                                                                                                                                                    |                                                                                     |  |  |  |  |

| 1                                    | Stop condition                                                   | s generated (termination of master device's transfer).                                                                                                                                                                                                              |                                                                                     |  |  |  |  |

| Cautions c                           | oncerning set tin                                                | ning                                                                                                                                                                                                                                                                |                                                                                     |  |  |  |  |

| <ul> <li>For mast</li> </ul>         | er reception:                                                    | Cannot be set to 1 during transfer.                                                                                                                                                                                                                                 |                                                                                     |  |  |  |  |

|                                      |                                                                  | Can be set to 1 only in the waiting period when ACKE0 notified of final reception.                                                                                                                                                                                  | has been cleared to 0 and slave has been                                            |  |  |  |  |

| <ul> <li>For mast</li> </ul>         | er transmission:                                                 | A stop condition cannot be generated normally during to<br>during the wait period that follows output of the ninth cle                                                                                                                                              | 0                                                                                   |  |  |  |  |

| <ul> <li>Cannot b</li> </ul>         | e set to 1 at the                                                | same time as start condition trigger (STT0).                                                                                                                                                                                                                        |                                                                                     |  |  |  |  |

| SPT0 bit                             | can be set to 1 o                                                | only when in master mode.                                                                                                                                                                                                                                           |                                                                                     |  |  |  |  |

| a stop co<br>during the<br>the outpu | ndition will be ge<br>e wait period folle<br>It of the ninth clo | leared to 0, if SPT0 bit is set to 1 during the wait period of<br>enerated during the high-level period of the ninth clock. No<br>powing the output of eight clocks, and SPT0 bit should be<br>ck.<br>then setting it again before it is cleared to 0 is prohibited | WTIM0 should be changed from 0 to 1<br>set to 1 during the wait period that follows |  |  |  |  |

| Condition f                          | for clearing (SPT                                                | 0 = 0)                                                                                                                                                                                                                                                              | Condition for setting (SPT0 = 1)                                                    |  |  |  |  |

| Cleared I                            | by loss in arbitrat                                              | ion                                                                                                                                                                                                                                                                 | Set by instruction                                                                  |  |  |  |  |

| <ul> <li>Automati</li> </ul>         | cally cleared afte                                               | r stop condition is detected                                                                                                                                                                                                                                        | -                                                                                   |  |  |  |  |

| Cleared I                            | by LREL0 = 1 (ex                                                 | kit from communications)                                                                                                                                                                                                                                            |                                                                                     |  |  |  |  |

| • When IICE0 = 0 (operation stop)    |                                                                  |                                                                                                                                                                                                                                                                     |                                                                                     |  |  |  |  |

| <ul> <li>Reset</li> </ul>            |                                                                  |                                                                                                                                                                                                                                                                     |                                                                                     |  |  |  |  |

Caution When bit 3 (TRC0) of the IIC status register 0 (IICS0) is set to 1 (transmission status), bit 5 (WREL0) of the IICC0 register is set to 1 during the ninth clock and wait is canceled, after which the TRC0 bit is cleared (reception status) and the SDA0 line is set to high impedance. Release the wait performed while the TRC bit is 1 (transmission status) by writing to the IIC shift register.

Remark Bit 0 (SPT0) becomes 0 when it is read after data setting.

| Address                                                                                         | : FFABH   | After re      | set: 00H    | R/W <sup>Note</sup> | 1                                                                                                                                  |                                  |       |        |    |

|-------------------------------------------------------------------------------------------------|-----------|---------------|-------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------|--------|----|

| Symbol                                                                                          | <7>       | <6>           | 5           | 4                   | 3                                                                                                                                  | 2                                | <1>   | <0>    |    |

| IICF0                                                                                           | STCF      | IICBSY        | 0           | 0                   | 0                                                                                                                                  | 0                                | STCEN | IICRSV |    |

|                                                                                                 |           |               |             |                     |                                                                                                                                    |                                  |       |        |    |

|                                                                                                 | STCF      |               |             |                     | S                                                                                                                                  | TT0 clear                        | flag  |        |    |

|                                                                                                 | 0         | Generate      | start condi | tion                |                                                                                                                                    |                                  |       |        |    |

|                                                                                                 | 1         | Start cond    | dition gene | ration unsu         | ccessful: cle                                                                                                                      | ear STT0                         | flag  |        |    |

|                                                                                                 | Condition | n for clearin | g (STCF =   | 0)                  |                                                                                                                                    | Condition for setting (STCF = 1) |       |        | 1) |

| <ul> <li>Cleared by STT0 = 1</li> <li>When IICE0 = 0 (operation stop)</li> <li>Reset</li> </ul> |           |               |             |                     | • Generating start condition unsuccessful and STT0<br>bit cleared to 0 when communication reservation is<br>disabled (IICRSV = 1). |                                  |       |        |    |

#### Figure 18-7. Format of IIC Flag Register 0 (IICF0)

| IICBSY    | I <sup>2</sup> C bus status flag                                       |                                                                                               |  |  |  |  |

|-----------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|--|--|

| 0         | Bus release status (communication initial status when STCEN = 1)       |                                                                                               |  |  |  |  |

| 1         | Bus communication status (communication initial status when STCEN = 0) |                                                                                               |  |  |  |  |

| Condition | n for clearing (IICBSY = 0)                                            | Condition for setting (IICBSY = 1)                                                            |  |  |  |  |

|           | ion of stop condition<br>IICE0 = 0 (operation stop)                    | <ul> <li>Detection of start condition</li> <li>Setting of IICE0 bit when STCEN = 0</li> </ul> |  |  |  |  |

| STCEN                                                          | Initial start enable trigger                                                                                       |                                   |  |  |  |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|--|

| 0                                                              | After operation is enabled (IICE0 = 1), enable generation of a start condition upon detection of a stop condition. |                                   |  |  |  |

| 1                                                              | After operation is enabled (IICE0 = 1), enable generation of a start condition without detecting a stop condition. |                                   |  |  |  |

| Condition for clearing (STCEN = 0)                             |                                                                                                                    | Condition for setting (STCEN = 1) |  |  |  |

| <ul><li> Detection of start condition</li><li> Reset</li></ul> |                                                                                                                    | Set by instruction                |  |  |  |

| IICRSV                                                 | Communication reservation function disable bit |                                    |  |

|--------------------------------------------------------|------------------------------------------------|------------------------------------|--|

| 0                                                      | Enable communication reservation               |                                    |  |

| 1                                                      | Disable communication reservation              |                                    |  |

| Condition for clearing (IICRSV = 0)                    |                                                | Condition for setting (IICRSV = 1) |  |

| <ul><li>Cleared by instruction</li><li>Reset</li></ul> |                                                | Set by instruction                 |  |

**Note** Bits 6 and 7 are read-only.

Cautions 1. Write to STCEN bit only when the operation is stopped (IICE0 = 0).

- As the bus release status (IICBSY = 0) is recognized regardless of the actual bus status when STCEN = 1, when generating the first start condition (STT0 = 1), it is necessary to verify that no third party communications are in progress in order to prevent such communications from being destroyed.

- 3. Write to IICRSV bit only when the operation is stopped (IICE0 = 0).

Remark STT0: Bit 1 of IIC control register 0 (IICC0) IICE0: Bit 7 of IIC control register 0 (IICC0)

#### 19.4.2 Division operation

- Initial setting

- 1. Set operation data to multiplication/division data register A0 (MDA0L and MDA0H) and multiplication/division data register B0 (MDB0).

- 2. Set bits 0 (DMUSEL0) and 7 (DMUE) of multiplier/divider control register 0 (DMUC0) to 0 and 1, respectively. Operation will start.

- During operation

- 3. The operation will be completed when 32 peripheral hardware clocks (fPRs) have been issued after the start of the operation (intermediate data is stored in the MDA0L and MDA0H registers and remainder data register 0 (SDR0) during operation, and therefore the read values of these registers are not guaranteed).

- End of operation

- 4. The result data is stored in the MDA0L, MDA0H, and SDR0 registers.

- 5. DMUE is cleared to 0 (end of operation).

- 6. After the operation, an interrupt request signal (INTDMU) is generated.

- Next operation

- 7. To execute multiplication next, start from the initial setting in **19.4.1** Multiplication operation.

- 8. To execute division next, start from the initial setting in **19.4.2** Division operation.

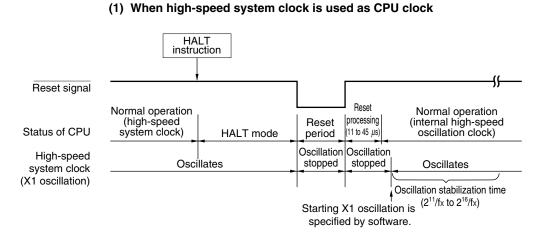

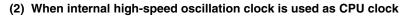

#### (b) Release by reset signal generation

When the reset signal is generated, HALT mode is released, and then, as in the case with a normal reset operation, the program is executed after branching to the reset vector address.

Figure 22-4. HALT Mode Release by Reset

Notes 1. The 78K0/KB2 is not provided with a subsystem clock.

2. Oscillation stabilization time is not required when using the external subsystem clock (fexclks) as the subsystem clock.

Remark fx: X1 clock oscillation frequency

<R>

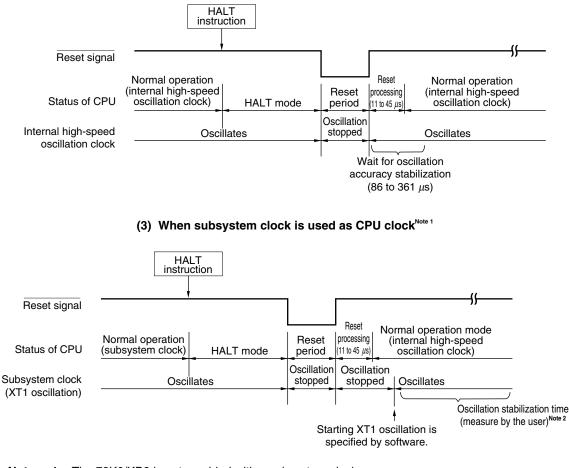

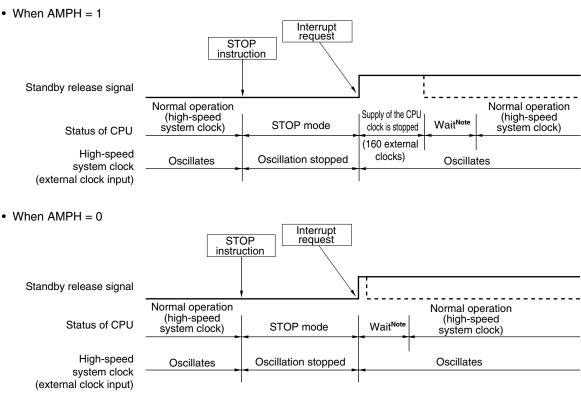

#### (1) When high-speed system clock (X1 oscillation) is used as CPU clock Interrupt request Wait STOP (set by OSTS) instruction Standby release signal Normal operation Normal operation Oscillation stabilization wait (high-speed (high-speed system clock) STOP mode (HALT mode status) system clock) Status of CPU High-speed Oscillates Oscillation stopped Oscillates system clock (X1 oscillation) Oscillation stabilization time (set by OSTS)

## Figure 22-6. STOP Mode Release by Interrupt Request Generation (1/2)

#### (2) When high-speed system clock (external clock input) is used as CPU clock

**Note** The wait time is as follows:

- When vectored interrupt servicing is carried out: 17 or 18 clocks

- When vectored interrupt servicing is not carried out: 11 or 12 clocks

- **Remark** The broken lines indicate the case when the interrupt request that has released the standby mode is acknowledged.

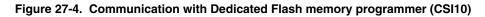

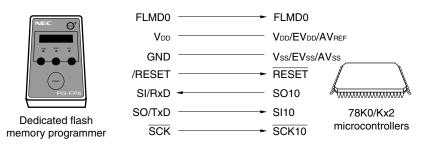

## 27.5 Communication Mode

Communication between the dedicated flash memory programmer and the 78K0/Kx2 microcontrollers is established by serial communication via CSI10 or UART6 of the 78K0/Kx2 microcontrollers.

#### (1) CSI10

Transfer rate: 2.4 kHz to 2.5 MHz

#### (2) UART6

Transfer rate: 115200 bps

#### Figure 27-5. Communication with Dedicated Flash memory programmer (UART6)

Dedicated flash memory programmer

| FLMD0  |   | FLMD0         |                  |  |

|--------|---|---------------|------------------|--|

| VDD    |   | VDD/EVDD/A    | VREF             |  |

| GND    |   | Vss/EVss/AVss |                  |  |

| /RESET |   | RESET         |                  |  |

| SI/RxD | • | TxD6          | AA               |  |

| SO/TxD |   | RxD6          | 78K0/Kx2         |  |

| CLK    |   | EXCLK         | microcontrollers |  |

|        |   |               |                  |  |

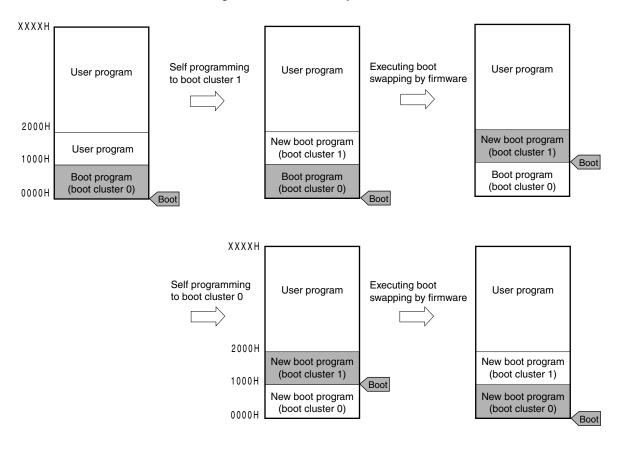

#### 27.10.1 Boot swap function

If rewriting the boot area has failed during self-programming due to a power failure or some other cause, the data in the boot area may be lost and the program may not be restarted by resetting.

The boot swap function is used to avoid this problem.

Before erasing boot cluster 0<sup>Note</sup>, which is a boot program area, by self-programming, write a new boot program to boot cluster 1 in advance. When the program has been correctly written to boot cluster 1, swap this boot cluster 1 and boot cluster 0 by using the set information function of the firmware of the 78K0/Kx2 microcontrollers, so that boot cluster 1 is used as a boot area. After that, erase or write the original boot program area, boot cluster 0.

As a result, even if a power failure occurs while the boot programming area is being rewritten, the program is executed correctly because it is booted from boot cluster 1 to be swapped when the program is reset and started next.

If the program has been correctly written to boot cluster 0, restore the original boot area by using the set information function of the firmware of the 78K0/Kx2 microcontrollers.

Note A boot cluster is a 4 KB area and boot clusters 0 and 1 are swapped by the boot swap function.

Boot cluster 0 (0000H to 0FFFH): Original boot program area Boot cluster 1 (1000H to 1FFFH): Area subject to boot swap function

# Caution When executing boot swapping, do not use the E.P.V command with the dedicated flash memory programmer.

Figure 27-15. Boot Swap Function

**Remark** Boot cluster 1 becomes 0000H to 0FFFH when a reset is generated after the boot flag has been set.

RENESAS