# E·X Renesas Electronics America Inc - <u>UPD78F0534AGC-GAL-AX Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | 78K/0                                                                                 |

| Core Size                  | 8-Bit                                                                                 |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                                    |

| Number of I/O              | 55                                                                                    |

| Program Memory Size        | 48KB (48K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 2K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 8x10b                                                                             |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 64-LQFP                                                                               |

| Supplier Device Package    | -                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0534agc-gal-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

78K0/Kx2 RENESAS MCU

# CHAPTER 1 OUTLINE

# 1.1 Differences Between Conventional-specification Products ( $\mu$ PD78F05xx and 78F05xxD) and Expanded-specification Products ( $\mu$ PD78F05xxA and 78F05xxDA)

The differences between the conventional-specification products ( $\mu$ PD78F05xx and 78F05xxD) and expanded-specification products ( $\mu$ PD78F05xxA and 78F05xxDA) of the 78K0/Kx2 microcontrollers are described below.

- A/D conversion time

- X1 oscillator characteristics

- Instruction cycle, peripheral hardware clock frequency, external main system clock frequency, external main system clock input high-level width, and external main system clock input low-level width (AC characteristics)

- The number of flash memory rewrites and retention time

- Processing time of the self programming library

- Interrupt response time of the self programming library

#### (d) Auxiliary carry flag (AC)

If the operation result has a carry from bit 3 or a borrow at bit 3, this flag is set (1). It is reset (0) in all other cases.

#### (e) In-service priority flag (ISP)

This flag manages the priority of acknowledgeable maskable vectored interrupts. When this flag is 0, low-level vectored interrupt requests specified by a priority specification flag register (PR0L, PR0H, PR1L, PR1H) (see **20.3 (3) Priority specification flag registers (PR0L, PR0H, PR1L, PR1H)**) can not be acknowledged. Actual request acknowledgment is controlled by the interrupt enable flag (IE).

#### (f) Carry flag (CY)

This flag stores overflow and underflow upon add/subtract instruction execution. It stores the shift-out value upon rotate instruction execution and functions as a bit accumulator during bit operation instruction execution.

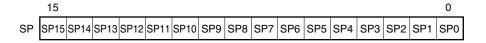

#### (3) Stack pointer (SP)

This is a 16-bit register to hold the start address of the memory stack area. Only the internal high-speed RAM area can be set as the stack area.

#### Figure 3-22. Format of Stack Pointer

The SP is decremented ahead of write (save) to the stack memory and is incremented after read (restored) from the stack memory.

Each stack operation saves/restores data as shown in Figures 3-23 and 3-24.

# Caution Since reset signal generation makes the SP contents undefined, be sure to initialize the SP before using the stack.

Remark Note the following points to use the memory bank select function efficiently.

- Allocate a routine that is used often in the common area.

- If a value that is planned to be referenced is placed in RAM, it can be referenced from all of the areas.

- If the reference destination and the branch destination of the routine placed in a memory bank are placed in the same memory bank, then the code size and processing are more efficient.

- Allocate interrupt servicing that requires a quick response in the common area.

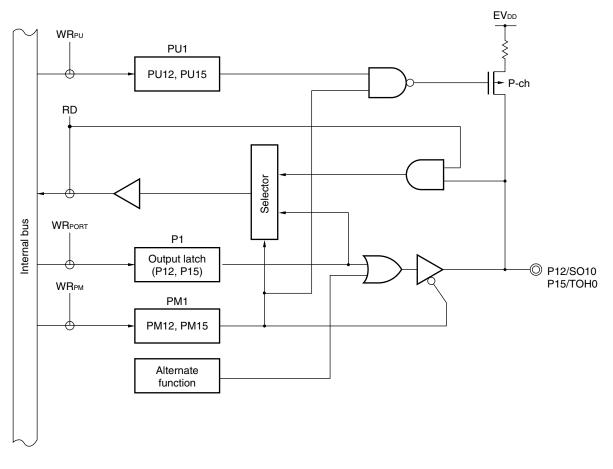

Figure 5-9. Block Diagram of P12 and P15

- P1: Port register 1

- PU1: Pull-up resistor option register 1

- PM1: Port mode register 1

- RD: Read signal

- WR××: Write signal

Remark With products not provided with an EVDD or EVSS pin, replace EVDD with VDD, or replace EVSS with VSS.

### 5.2.4 Port 3

|                                     | 78K0/KB2 | 78K0/KC2                              | 78K0/KD2 | 78K0                                                       | /KE2                                                      | 78K0/KF2 |  |  |

|-------------------------------------|----------|---------------------------------------|----------|------------------------------------------------------------|-----------------------------------------------------------|----------|--|--|

|                                     |          |                                       |          | Products<br>whose flash<br>memory is<br>less than<br>32 KB | Products<br>whose flash<br>memory is at<br>least<br>48 KB |          |  |  |

| P30/INTP1                           |          | · · · · · · · · · · · · · · · · · · · |          |                                                            |                                                           |          |  |  |

| P31/INTP2/<br>OCD1A <sup>Note</sup> |          | $\checkmark$                          |          |                                                            |                                                           |          |  |  |

| P32/INTP3/<br>OCD1B <sup>Note</sup> |          |                                       |          | N                                                          |                                                           |          |  |  |

| P33/INTP4/TI51/<br>TO51             |          |                                       |          | V                                                          |                                                           |          |  |  |

**Note** OCD1A and OCD1B are provided to the products with an on-chip debug function (µPD78F05xxD and 78F05xxDA) only.

#### **Remark** √: Mounted

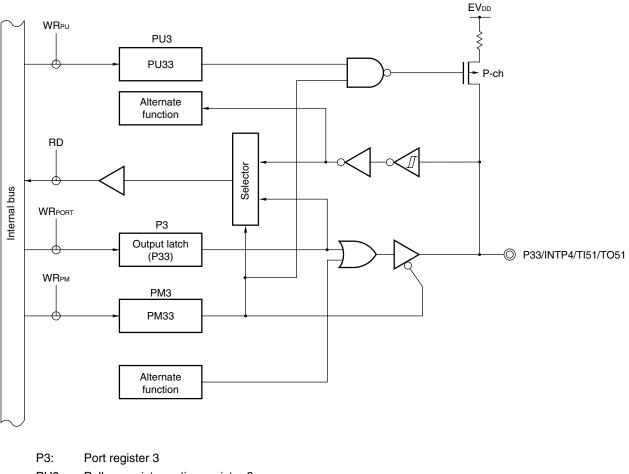

Port 3 is an I/O port with an output latch. Port 3 can be set to the input mode or output mode in 1-bit units using port mode register 3 (PM3). When the P30 to P33 pins are used as an input port, use of an on-chip pull-up resistor can be specified in 1-bit units by pull-up resistor option register 3 (PU3).

This port can also be used for external interrupt request input and timer I/O.

Reset signal generation sets port 3 to input mode.

Figures 5-13 and 5-14 show block diagrams of port 3.

- Cautions 1. In the product with an on-chip debug function ( $\mu$ P78F05xxD and D78F05xxDA), be sure to pull the P31/INTP2/OCD1A pin down before a reset release, to prevent malfunction.

- 2. Process the P31/INTP2/OCD1A pin of the products mounted with the on-chip debug function ( $\mu$ PD78F05xxD and 78F05xxDA) as follows, when it is not used when it is connected to a flash memory programmer or an on-chip debug emulator.

|                                                                                         |                       | P31/INTP2/OCD1A                                                                                                                  |  |  |

|-----------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|

| Flash memory program                                                                    | mer connection        | Connect to EVss <sup>Note</sup> via a resistor.                                                                                  |  |  |

| On-chip debug                                                                           | During reset          |                                                                                                                                  |  |  |

| emulator connection<br>(when it is not used<br>as an on-chip debug<br>mode setting pin) | During reset released | Input: Connect to EV <sub>DD</sub> <sup>Note</sup> or EV <sub>SS</sub> <sup>Note</sup><br>via a resistor.<br>Output: Leave open. |  |  |

Note With products without an EVss pin, connect them to Vss. With products without an EVDD pin, connect them to VDD.

### Figure 5-14. Block Diagram of P33

- PU3: Pull-up resistor option register 3

- PM3: Port mode register 3

- RD: Read signal

- WR××: Write signal

**Remark** With products not provided with an EVDD or EVSS pin, replace EVDD with VDD, or replace EVSS with VSS.

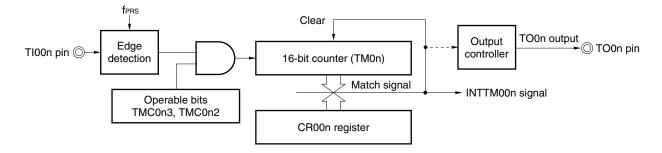

#### 7.4.3 External event counter operation

When bits 1 and 0 (PRM0n1 and PRM0n0) of the prescaler mode register 0n (PRM0n) are set to 11 (for counting up with the valid edge of the TI00n pin) and bits 3 and 2 (TMC0n3 and TMC0n2) of 16-bit timer mode control register 0n (TMC0n) are set to 11, the valid edge of an external event input is counted, and a match interrupt signal indicating matching between TM0n and CR00n (INTTM00n) is generated.

To input the external event, the TI00n pin is used. Therefore, the timer/event counter cannot be used as an external event counter in the clear & start mode entered by the TI00n pin valid edge input (when TMC0n3 and TMC0n2 = 10).

The INTTM00n signal is generated with the following timing.

- Timing of generation of INTTM00n signal (second time or later)

- = Number of times of detection of valid edge of external event × (Set value of CR00n + 1)

However, the first match interrupt immediately after the timer/event counter has started operating is generated with the following timing.

- Timing of generation of INTTM00n signal (first time only)

- = Number of times of detection of valid edge of external event input × (Set value of CR00n + 2)

To detect the valid edge, the signal input to the TI00n pin is sampled during the clock cycle of fPRs. The valid edge is not detected until it is detected two times in a row. Therefore, a noise with a short pulse width can be eliminated.

Remarks 1. For the setting of I/O pins, see 7.3 (5) Port mode register 0 (PM0).

2. For how to enable the INTTM00n signal interrupt, see CHAPTER 20 INTERRUPT FUNCTIONS.

**Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

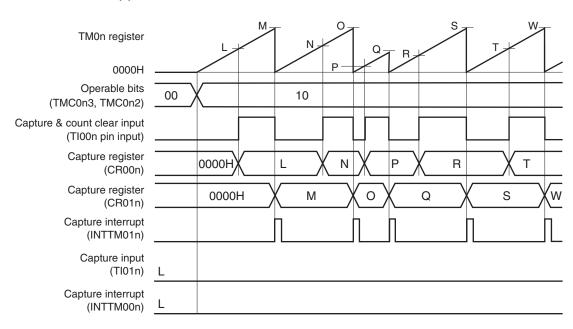

# Figure 7-34. Timing Example of Clear & Start Mode Entered by TI00n Pin Valid Edge Input (CR00n: Capture Register, CR01n: Capture Register) (3/3)

(c) TOC0n = 13H, PRM0n = 00H, CRC0n = 07H, TMC0n = 0AH

This is an application example where the pulse width of the signal input to the TI00n pin is measured.

By setting CRC0n, the count value can be captured to CR00n in the phase reverse to the falling edge of the TI00n pin (i.e., rising edge) and to CR01n at the falling edge of the TI00n pin.

The high- and low-level widths of the input pulse can be calculated by the following expressions.

• High-level width = [CR01n value] - [CR00n value] × [Count clock cycle]

• Low-level width = [CR00n value] × [Count clock cycle]

If the reverse phase of the TI00n pin is selected as a trigger to capture the count value to CR00n, the INTTM00n signal is not generated. Read the values of CR00n and CR01n to measure the pulse width immediately after the INTTM01n signal is generated.

However, if the valid edge specified by bits 6 and 5 (ES1n1 and ES1n0) of prescaler mode register 0n (PRM0n) is input to the TI01n pin, the count value is not captured but the INTTM00n signal is generated. To measure the pulse width of the TI00n pin, mask the INTTM00n signal when it is not used.

Remark n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

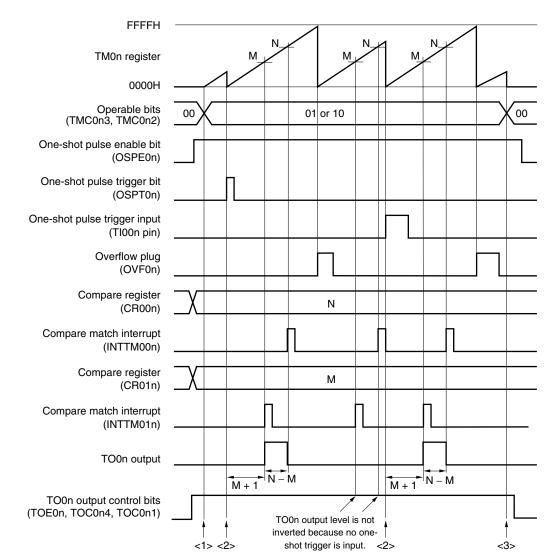

#### Figure 7-50. Example of Software Processing for One-Shot Pulse Output Operation (1/2)

- Time from when the one-shot pulse trigger is input until the one-shot pulse is output

- =  $(M + 1) \times Count clock cycle$

- One-shot pulse output active level width

- =  $(N M) \times Count clock cycle$

- **Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2,] 78K0/KD2 products

- n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

### (1) Receive buffer register 0 (RXB0)

This 8-bit register stores parallel data converted by receive shift register 0 (RXS0).

Each time 1 byte of data has been received, new receive data is transferred to this register from receive shift register 0 (RXS0).

If the data length is set to 7 bits the receive data is transferred to bits 0 to 6 of RXB0 and the MSB of RXB0 is always 0.

If an overrun error (OVE0) occurs, the receive data is not transferred to RXB0. RXB0 can be read by an 8-bit memory manipulation instruction. No data can be written to this register. Reset signal generation and POWER0 = 0 set this register to FFH.

### (2) Receive shift register 0 (RXS0)

This register converts the serial data input to the RxD0 pin into parallel data. RXS0 cannot be directly manipulated by a program.

### (3) Transmit shift register 0 (TXS0)

This register is used to set transmit data. Transmission is started when data is written to TXS0, and serial data is transmitted from the TxD0 pins.

TXS0 can be written by an 8-bit memory manipulation instruction. This register cannot be read.

Reset signal generation, POWER0 = 0, and TXE0 = 0 set this register to FFH.

### Cautions 1. Set transmit data to TXS0 at least one base clock (fxcLK0) after setting TXE0 = 1.

2. Do not write the next transmit data to TXS0 before the transmission completion interrupt signal (INTST0) is generated.

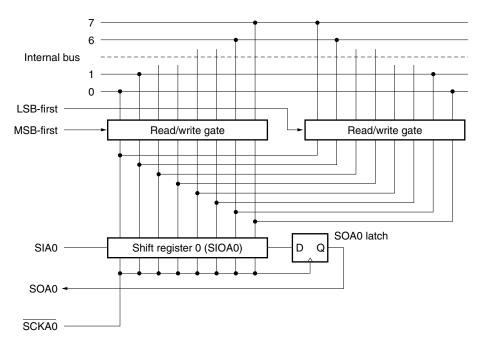

# (c) Switching MSB/LSB as start bit

Figure 17-12 shows the configuration of serial I/O shift register 0 (SIOA0) and the internal bus. As shown in the figure, MSB/LSB can be read/written in reverse form.

Switching MSB/LSB as the start bit can be specified using bit 1 (DIR0) of serial operation mode specification register 0 (CSIMA0).

Figure 17-12. Transfer Bit Order Switching Circuit

Start bit switching is realized by switching the bit order for data written to SIOA0. The SIOA0 shift order remains unchanged.

Thus, switching between MSB-first and LSB-first must be performed before writing data to the shift register.

#### (d) Communication start

Serial communication is started by setting communication data to serial I/O shift register 0 (SIOA0) when the following two conditions are satisfied.

- Serial interface CSIA0 operation control bit (CSIAE0) = 1

- Serial communication is not in progress

Caution If CSIAE0 is set to 1 after data is written to SIOA0, communication does not start.

Upon termination of 8-bit communication, serial communication automatically stops and the interrupt request flag (ACSIIF) is set.

#### (1) Master operation in single-master system

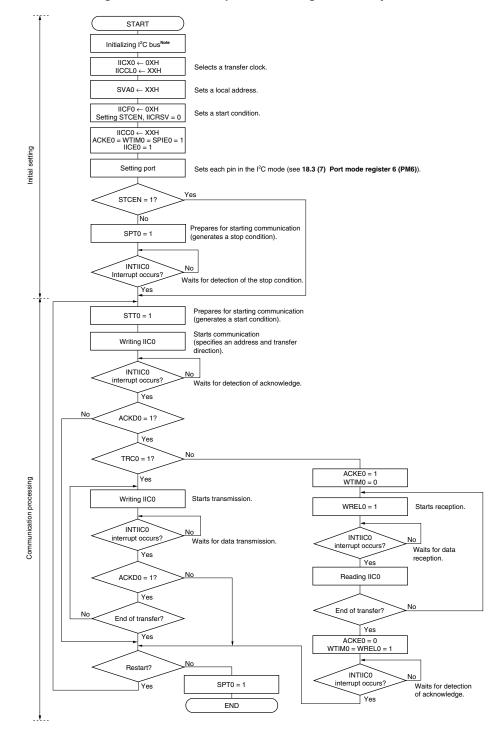

Figure 18-23. Master Operation in Single-Master System

- **Note** Release (SCL0 and SDA0 pins = high level) the  $l^2$ C bus in conformance with the specifications of the product that is communicating. If EEPROM is outputting a low level to the SDA0 pin, for example, set the SCL0 pin in the output port mode, and output a clock pulse from the output port until the SDA0 pin is constantly at high level.

- **Remark** Conform to the specifications of the product that is communicating, with respect to the transmission and reception formats.

RENESAS

| к            | к            | к            | к            | к            | Interrupt         | Interrupt Request        | Flag     | Interrupt Mask F         | lag      | Priority Specification Flag |          |

|--------------|--------------|--------------|--------------|--------------|-------------------|--------------------------|----------|--------------------------|----------|-----------------------------|----------|

| В            | C<br>2       | D<br>2       | E            | F            | Source            |                          | Register |                          | Register |                             | Register |

| 2<br>√       | ∠ √          | ∠<br>√       | 2<br>√       | 2<br>√       | INTAD             | ADIF                     | IF1L     | ADMK                     | MK1L     | ADPR                        | PR1L     |

| ,<br>√       | √            | ,<br>√       | √            | √            | INTSR0            | SRIF0                    |          | SRMK0                    |          | SRPR0                       |          |

| -            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | INTWTI            | WTIIF                    | -        | WTIMK                    | -        | WTIPR                       | -        |

| $\checkmark$ | V            | $\checkmark$ | $\checkmark$ | $\checkmark$ | INTTM51<br>Note 4 | TMIF51                   |          | TMMK51                   |          | TMPR51                      |          |

| -            | $\checkmark$ |              | $\checkmark$ | $\checkmark$ | INTKR             | KRIF                     |          | KRMK                     |          | KRPR                        |          |

| _            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | INTWT             | WTIF                     |          | WTMK                     |          | WTPR                        |          |

| -            | √<br>Note 1  | $\checkmark$ | $\checkmark$ | $\checkmark$ | INTP6             | PIF6                     |          | PMK6                     |          | PPR6                        |          |

| -            |              |              | $\checkmark$ | $\checkmark$ | INTP7             | PIF7                     |          | PMK7                     |          | PPR7                        |          |

| √<br>Note 2  | √<br>Note 2  | √<br>Note 2  | √<br>Note 2  | $\checkmark$ | INTIICO<br>Note 5 | IICIF0 <sup>Note 6</sup> | IF1H     | IICMK0 <sup>Note 7</sup> | MK1H     | IICPR0 <sup>Note 8</sup>    | PR1H     |

|              |              |              |              |              | INTDMU<br>Note 5  | DMUIF <sup>Note 6</sup>  |          | DMUMK <sup>Note 7</sup>  |          |                             |          |

| -            | _            | -            | √<br>Note 3  | $\checkmark$ | INTCSI11          | CSIIF11                  |          | CSIMK11                  |          | CSIPR11                     |          |

| -            | -            | -            | √<br>Note 3  | $\checkmark$ | INTTM001          | TMIF001                  |          | TMMK001                  |          | TMPR001                     |          |

| -            | -            | -            | √<br>Note 3  | $\checkmark$ | INTTM011          | TMIF011                  |          | TMMK011                  |          | TMPR011                     |          |

| _            | -            | -            | -            |              | INTACSI           | ACSIIF                   |          | ACSIMK                   |          | ACSIPR                      |          |

Table 20-2. Flags Corresponding to Interrupt Request Sources (2/2)

Notes 1. 48-pin products only.

- 2. INTIICO: products whose flash memory is less than 32 KB INTIICO/INTDMU: products whose flash memory is at least 48 KB

- 3. Products whose flash memory is at least 48 KB only.

- 4. When 8-bit timer/event counter 51 is used in the carrier generator mode, an interrupt is generated upon the timing when the INTTM5H1 signal is generated (see Figure 9-13 Transfer Timing).

- 5. Do not use serial interface IIC0 and multiplier/divider simultaneously, because the flags corresponding to the interrupt request sources of serial interface IIC0 and multiplier/divider support both of these interrupt request sources. If software which operates serial interface IIC0 is developed by CC78K0 which is C compiler, do not select the check box of "Using Multiplier/Divider" on GUI of PM+.

- 6. If either interrupt source INTIIC0 or INTDMU is generated, bit 0 of IF1H is set (1).

- 7. Bit 0 of MK1H supports both interrupt sources INTIIC0 and INTDMU.

- 8. Bit 0 of PR1H supports both interrupt sources INTIIC0 and INTDMU.

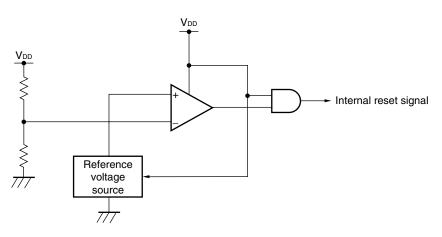

## 24.2 Configuration of Power-on-Clear Circuit

The block diagram of the power-on-clear circuit is shown in Figure 24-1.

### Figure 24-1. Block Diagram of Power-on-Clear Circuit

#### 24.3 Operation of Power-on-Clear Circuit

#### (1) In 1.59 V POC mode (option byte: POCMODE = 0)

- An internal reset signal is generated on power application. When the supply voltage (V<sub>DD</sub>) exceeds the detection voltage (V<sub>POC</sub> = 1.59 V ±0.15 V), the reset status is released.

- The supply voltage (V<sub>DD</sub>) and detection voltage (V<sub>POC</sub> = 1.59 V ±0.15 V) are compared. When V<sub>DD</sub> < V<sub>POC</sub>, the internal reset signal is generated. It is released when V<sub>DD</sub> ≥ V<sub>POC</sub>.

#### (2) In 2.7 V/1.59 V POC mode (option byte: POCMODE = 1)

- An internal reset signal is generated on power application. When the supply voltage (V<sub>DD</sub>) exceeds the detection voltage (V<sub>DDPOC</sub> = 2.7 V ±0.2 V), the reset status is released.

- The supply voltage (V<sub>DD</sub>) and detection voltage (V<sub>POC</sub> = 1.59 V ±0.15 V) are compared. When V<sub>DD</sub> < V<sub>POC</sub>, the internal reset signal is generated. It is released when V<sub>DD</sub> ≥ V<sub>DDPOC</sub>.

The timing of generation of the internal reset signal by the power-on-clear circuit and low-voltage detector is shown below.

# 27.9 Processing Time for Each Command When PG-FP4 or PG-FP5 Is Used (Reference)

The following table shows the processing time for each command (reference) when the PG-FP4 or PG-FP5 is used as a dedicated flash memory programmer.

#### Table 27-12. Processing Time for Each Command When PG-FP4 or PG-FP5 Is Used (Reference) (1/2)

| Command of<br>PG-FP4 | Port: CSI-Internal-OSC<br>(Internal high-speed oscillation | Port: UART-Ext-FP4CK (External main system clock (fexclk)),<br>Speed: 115,200 bps |                   |  |  |  |

|----------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------|--|--|--|

|                      | clock (fвн)),<br>Speed: 2.5 MHz                            | Frequency: 2.0 MHz                                                                | Frequency: 20 MHz |  |  |  |

| Signature            | 0.5 s (TYP.)                                               | 0.5 s (TYP.)                                                                      | 0.5 s (TYP.)      |  |  |  |

| Blankcheck           | 0.5 s (TYP.)                                               | 0.5 s (TYP.)                                                                      | 0.5 s (TYP.)      |  |  |  |

| Erase                | 0.5 s (TYP.)                                               | 0.5 s (TYP.)                                                                      | 0.5 s (TYP.)      |  |  |  |

| Program              | 2.5 s (TYP.)                                               | 5 s (TYP.)                                                                        | 5 s (TYP.)        |  |  |  |

| Verify               | 1.5 s (TYP.)                                               | 4 s (TYP.)                                                                        | 3.5 s (TYP.)      |  |  |  |

| E.P.V                | 3.5 s (TYP.)                                               | 6 s (TYP.)                                                                        | 6 s (TYP.)        |  |  |  |

| Checksum             | 0.5 s (TYP.)                                               | 0.5 s (TYP.)                                                                      | 0.5 s (TYP.)      |  |  |  |

| Security             | 0.5 s (TYP.)                                               | 0.5 s (TYP.)                                                                      | 0.5 s (TYP.)      |  |  |  |

(1) Products with internal ROMs of the 32 KB

(2) Products with internal ROMs of the 60 KB

| Command of<br>PG-FP4 | Port: CSI-Internal-OSC<br>(Internal high-speed oscillation | Port: UART-Ext-FP4CK (External main system clock (fexclk)),<br>Speed: 115,200 bps |                   |  |  |  |

|----------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------|--|--|--|

|                      | 1 s (TYP.) 1   1 s (TYP.) 1   5 s (TYP.) 9                 | Frequency: 2.0 MHz                                                                | Frequency: 20 MHz |  |  |  |

| Signature            | 0.5 s (TYP.)                                               | 0.5 s (TYP.)                                                                      | 0.5 s (TYP.)      |  |  |  |

| Blankcheck           | 1 s (TYP.)                                                 | 1 s (TYP.)                                                                        | 1 s (TYP.)        |  |  |  |

| Erase                | 1 s (TYP.)                                                 | 1 s (TYP.)                                                                        | 1 s (TYP.)        |  |  |  |

| Program              | 5 s (TYP.)                                                 | 9 s (TYP.)                                                                        | 9 s (TYP.)        |  |  |  |

| Verify               | 2 s (TYP.)                                                 | 6.5 s (TYP.)                                                                      | 6.5 s (TYP.)      |  |  |  |

| E.P.V                | 6 s (TYP.)                                                 | 10.5 s (TYP.)                                                                     | 10.5 s (TYP.)     |  |  |  |

| Checksum             | 0.5 s (TYP.)                                               | 1 s (TYP.)                                                                        | 1 s (TYP.)        |  |  |  |

| Security             | 0.5 s (TYP.)                                               | 0.5 s (TYP.)                                                                      | 0.5 s (TYP.)      |  |  |  |

# Caution When executing boot swapping, do not use the E.P.V. command with the dedicated flash memory programmer.

#### 29.1.2 Description of operation column

- A: A register; 8-bit accumulator

- X: X register

- B: B register

- C: C register

- D: D register

- E: E register

- H: H register

- L: L register

- AX: AX register pair; 16-bit accumulator

- BC: BC register pair

- DE: DE register pair

- HL: HL register pair

- PC: Program counter

- SP: Stack pointer

- PSW: Program status word

- CY: Carry flag

- AC: Auxiliary carry flag

- Z: Zero flag

- RBS: Register bank select flag

- IE: Interrupt request enable flag

- (): Memory contents indicated by address or register contents in parentheses

- XH, XL: Higher 8 bits and lower 8 bits of 16-bit register

- A: Logical product (AND)

- v: Logical sum (OR)

- ----: Inverted data

- addr16: 16-bit immediate data or label

- jdisp8: Signed 8-bit data (displacement value)

### 29.1.3 Description of flag operation column

- (Blank): Not affected

- 0: Cleared to 0

- 1: Set to 1

- ×: Set/cleared according to the result

- R: Previously saved value is restored

#### Caution The pins mounted depend on the product. Refer to Caution 2 at the beginning of this chapter.

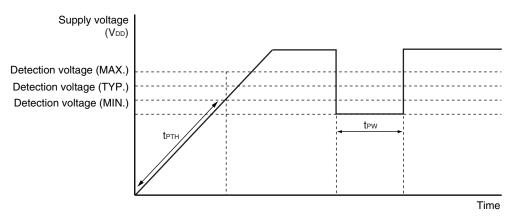

| Parameter                             | Symbol | Conditions                                                                 | MIN. | TYP. | MAX. | Unit |

|---------------------------------------|--------|----------------------------------------------------------------------------|------|------|------|------|

| Detection voltage                     | VPOC   |                                                                            | 1.44 | 1.59 | 1.74 | V    |

| Power supply voltage rise inclination | tртн   | $V_{\text{DD}}$ : 0 $V \rightarrow$ change inclination of $V_{\text{POC}}$ | 0.5  |      |      | V/ms |

| Minimum pulse width                   | tpw    |                                                                            | 200  |      |      | μS   |

#### 1.59 V POC Circuit Characteristics (T<sub>A</sub> = -40 to +85°C, Vss = EVss = 0 V)

#### 1.59 V POC Circuit Timing

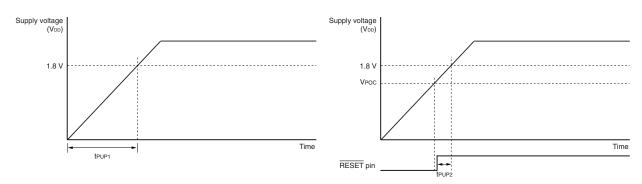

# Supply Voltage Rise Time (T<sub>A</sub> = -40 to +85°C, Vss = EVss = 0 V)

| Parameter                                                                                                               | Symbol        | Conditions                                                 | MIN. | TYP. | MAX. | Unit |

|-------------------------------------------------------------------------------------------------------------------------|---------------|------------------------------------------------------------|------|------|------|------|

| Maximum time to rise to 1.8 V (V_DD (MIN.)) (V_DD: 0 V $\rightarrow$ 1.8 V)                                             | <b>t</b> pup1 | POCMODE (option byte) = 0,<br>when RESET input is not used |      |      | 3.6  | ms   |

| Maximum time to rise to 1.8 V (V <sub>DD</sub> (MIN.))<br>(releasing RESET input $\rightarrow$ V <sub>DD</sub> : 1.8 V) | tpup2         | POCMODE (option byte) = 0,<br>when RESET input is used     |      |      | 1.9  | ms   |

#### Supply Voltage Rise Time Timing

• When RESET pin input is not used

• When RESET pin input is used

#### Caution The pins mounted depend on the product. Refer to Caution at the beginning of this chapter.

# DC Characteristics (3/4)

(TA = -40 to +110°C, 2.7 V  $\leq$  Vdd = EVdd  $\leq$  5.5 V, AVREF  $\leq$  Vdd, Vss = EVss = AVss = 0 V)

| Parameter                      | Symbol           | Conditions                                                                                                                       |                                                                                                                                         |                                    | MIN.   | TYP. | MAX.               | Unit |

|--------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------|------|--------------------|------|

| Output voltage, low            | Vol1             | P00 to P06, P10 to P17,<br>P30 to P33, P40 to P47,<br>P50 to P57, P64 to P67,                                                    | 3, P40 to P47, lo∟1 = 5.0 mA                                                                                                            |                                    |        |      | 0.7                | V    |

|                                |                  | P70 to P77, P120, P130,<br>P140 to P145                                                                                          | 2.7 V ≤<br>lol1 = 3.                                                                                                                    | V <sub>DD</sub> < 4.0 V,<br>.0 mA  |        |      | 0.7                | V    |

|                                | V <sub>OL2</sub> | P20 to P27                                                                                                                       | AV <sub>REF</sub> =                                                                                                                     | ,                                  |        |      | 0.4                | V    |

|                                |                  | P121 to P124                                                                                                                     | IOL2 = 0.                                                                                                                               | .4 mA                              |        |      | 0.4                | V    |

|                                | Vol3             | P60 to P63                                                                                                                       | 4.0 V ≤<br>lol1 = 10                                                                                                                    | V <sub>DD</sub> ≤ 5.5 V,<br>0.0 mA |        |      | 2.0                | V    |

|                                |                  |                                                                                                                                  | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ I_{\text{OL1}} = 3.0 \ mA \end{array} \label{eq:DD}$                      |                                    |        |      | 0.4                | V    |

|                                |                  |                                                                                                                                  | $\begin{array}{l} 2.7 \ \text{V} \leq \text{V}_{\text{DD}} < 4.0 \ \text{V}, \\ \\ \text{I}_{\text{OL1}} = 3.0 \ \text{mA} \end{array}$ |                                    |        |      | 0.6                | V    |

| Input leakage current,<br>high | ILIH1            | P00 to P06, P10 to P17,<br>P30 to P33, P40 to P47,<br>P50 to P57, P60 to P67,<br>P70 to P77, P120, P140 to<br>P145, FLMD0, RESET | Vi = Vdd                                                                                                                                |                                    |        |      | 3                  | μΑ   |

|                                | ILIH2            | P20 to P27                                                                                                                       | $V_{I} = AV_{REF} = V_{DD}$                                                                                                             |                                    |        |      | 3                  | μA   |

|                                | Ілнз             | P121 to 124                                                                                                                      | V1 =                                                                                                                                    | I/O port mode                      |        |      | 3                  | μA   |

|                                |                  | (X1, X2, XT1, XT2)                                                                                                               | Vdd                                                                                                                                     | OSC mode                           |        |      | 20                 | μA   |

| Input leakage current, low     | Ilil1            | P00 to P06, P10 to P17,<br>P30 to P33, P40 to P47,<br>P50 to P57, P60 to P67,<br>P70 to P77, P120, P140 to<br>P145, FLMD0, RESET | VI = VSS                                                                                                                                |                                    |        |      | _3                 | μA   |

|                                |                  | P20 to P27                                                                                                                       | VI = Vss                                                                                                                                | S, AVREF = VDD                     |        |      | -3                 | μA   |

|                                | Ililis           | P121 to 124                                                                                                                      | V1 =                                                                                                                                    | I/O port mode                      |        |      | -3                 | μA   |

|                                |                  | (X1, X2, XT1, XT2)                                                                                                               | Vss                                                                                                                                     | OSC mode                           |        |      | -20                | μA   |

| Pull-up resistor               | Rυ               | VI = Vss                                                                                                                         |                                                                                                                                         |                                    | 10     | 20   | 100                | kΩ   |

| FLMD0 supply voltage           | VIL              | In normal operation mode                                                                                                         |                                                                                                                                         |                                    | 0      |      | 0.2V <sub>DD</sub> | V    |

|                                | VIH              | In self-programming mode                                                                                                         |                                                                                                                                         |                                    | 0.8VDD |      | VDD                | V    |

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of port pins.

# Caution The pins mounted depend on the product. Refer to Caution at the beginning of this chapter.

| Parameter                                                                  | Symbol                                                           |                                                              | Conditions                            | MIN.                 | TYP. | MAX.            | Unit |

|----------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------|----------------------|------|-----------------|------|

| SCKA0 cycle time                                                           | tkcy3 $4.0 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}$ |                                                              | 5 V                                   | 600                  |      |                 | ns   |

|                                                                            |                                                                  | $2.7 \text{ V} \leq V_{\text{DD}} < 4.0 \text{ V}$           |                                       | 1200                 |      |                 | ns   |

| SCKA0 high-/low-level width                                                | tкнз,<br>tк∟з                                                    | $4.0 \ V \leq V_{\text{DD}} \leq 5.$                         | 5 V                                   | tксүз/2 –<br>50      |      |                 | ns   |

|                                                                            |                                                                  | $2.7~V \leq V_{\text{DD}} < 4.0~V$                           |                                       | tксүз/2 –<br>100     |      |                 | ns   |

| SIA0 setup time (to $\overline{\text{SCKA0}}$ )                            | tsik3                                                            |                                                              |                                       | 100                  |      |                 | ns   |

| SIA0 hold time (from $\overline{\text{SCKA0}}\uparrow$ )                   | tหรเง                                                            |                                                              |                                       | 300                  |      |                 | ns   |

| Delay time from $\overline{SCKA0}\downarrow$ to                            | tкsoз                                                            | $C = 100 \text{ pF}^{Note}$                                  | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |                      |      | 200             | ns   |

| SOA0 output                                                                |                                                                  |                                                              | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |                      |      | 300             | ns   |

| Time from $\overline{\text{SCKA0}}^{\uparrow}$ to $\text{STB0}^{\uparrow}$ | tsbd                                                             |                                                              |                                       | tксүз/2 –<br>100     |      |                 | ns   |

| Strobe signal high-level width                                             | tsвw                                                             | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                        |                                       | tксүз –<br><b>30</b> |      |                 | ns   |

|                                                                            |                                                                  | $2.7 \text{ V} \leq \text{V}_{\text{DD}} < 4.0 \text{ V}$    |                                       | tксүз –<br>60        |      |                 | ns   |

| Busy signal setup time (to busy signal detection timing)                   | tвys                                                             |                                                              |                                       | 100                  |      |                 | ns   |

| Busy signal hold time (from busy signal detection timing)                  | tвүн                                                             |                                                              |                                       | 100                  |      |                 | ns   |

| Time from busy inactive to $\overline{\text{SCKA0}}\downarrow$             | tsps                                                             | $4.0 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V}$ |                                       |                      |      | 2tксүз +<br>100 | ns   |

|                                                                            |                                                                  | $2.7 \text{ V} \leq V_{\text{DD}} < 4.$                      | 0 V                                   |                      |      | 2tксүз –<br>150 | ns   |

# (f) CSIA0 (master mode, SCKA0...internal clock output)

Note C is the load capacitance of the  $\overline{SCKA0}$  and SOA0 output lines.