Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 20MHz                                                                                |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                                   |

| Number of I/O              | 55                                                                                   |

| Program Memory Size        | 60KB (60K × 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 3K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 8x10b                                                                            |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 64-VFLGA                                                                             |

| Supplier Device Package    | 64-FLGA (5x5)                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0535afc-aa1-a |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# (1) Conventional-specification products ( $\mu$ PD78F05xx and 78F05xxD) (2/2)

# <3> When high-speed system clock is used (static model of C compiler/assembler)

| Library Name                         | Interrupt Response Time (µs (Max.))    |                                          |                                        |                                          |

|--------------------------------------|----------------------------------------|------------------------------------------|----------------------------------------|------------------------------------------|

|                                      | RSTOP = 0, RSTS = 1                    |                                          | RSTOP = 1                              |                                          |

|                                      | Entry RAM location<br>is outside short | Entry RAM location<br>is in short direct | Entry RAM location<br>is outside short | Entry RAM location<br>is in short direct |

|                                      | direct addressing                      | addressing range                         | direct addressing                      | addressing range                         |

|                                      | range                                  |                                          | range                                  |                                          |

| Block blank check library            | 136/fcpu + 507                         | 136/fcpu + 407                           | 136/fcpu + 1650                        | 136/fcpu + 714                           |

| Block erase library                  | 136/fcpu + 559                         | 136/fcpu + 460                           | 136/fcpu + 1702                        | 136/fcpu + 767                           |

| Word write library                   | 272/fcpu + 1589                        | 272/fcpu + 1298                          | 272/fcpu + 2732                        | 272/fcpu + 1605                          |

| Block verify library                 | 136/fcpu + 518                         | 136/fcpu + 418                           | 136/fcpu + 1661                        | 136/fcpu + 725                           |

| Set information library              | 72/fcpu + 370                          | 72/fcpu + 165                            | 72/fcpu + 1513                         | 72/fcpu + 472                            |

| EEPROM write library <sup>Note</sup> | 19/fcpu + 1759                         | 19/fcpu + 1468                           | 19/fcpu + 1759                         | 19/fcpu + 1468                           |

|                                      | 268/fcpu + 834                         | 268/fcpu + 512                           | 268/fcpu + 2061                        | 268/fcpu + 873                           |

**Note** The longer value of the EEPROM write library interrupt response time becomes the Max. value, depending on the value of fcPu.

Remarks 1. fcPu: CPU operation clock frequency

- 2. RSTOP: Bit 0 of the internal oscillation mode register (RCM)

- 3. RSTS: Bit 7 of the internal oscillation mode register (RCM)

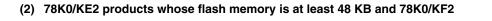

Figure 5-6. Block Diagram of P06 (2/2)

P0: Port register 0

PU0: Pull-up resistor option register 0

PM0: Port mode register 0

RD: Read signal

WR××: Write signal

**Remark** With products not provided with an EVDD or EVss pin, replace EVDD with VDD, or replace EVss with Vss.

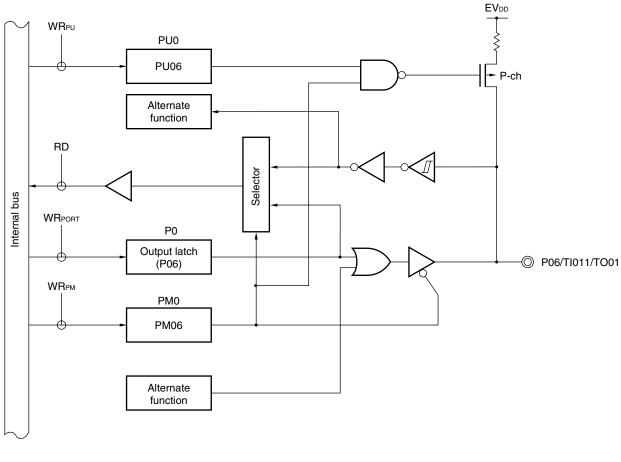

# (2) Capture/compare control register 0n (CRC0n)

CRC0n is the register that controls the operation of CR00n and CR01n. Changing the value of CRC0n is prohibited during operation (when TMC0n3 and TMC0n2 = other than 00). CRC0n can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears CRC0n to 00H.

# Figure 7-8. Format of Capture/Compare Control Register 00 (CRC00)

| Address: FFBCH After reset: 00H |   | R/W |   |   |   |        |        |        |

|---------------------------------|---|-----|---|---|---|--------|--------|--------|

| Symbol                          | 7 | 6   | 5 | 4 | 3 | 2      | 1      | 0      |

| CRC00                           | 0 | 0   | 0 | 0 | 0 | CRC002 | CRC001 | CRC000 |

| CRC002 | CR010 operating mode selection |  |

|--------|--------------------------------|--|

| 0      | Operates as compare register   |  |

| 1      | Operates as capture register   |  |

| CRC001                                | 001 CR000 capture trigger selection                                                                                                           |  |  |  |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0 Captures on valid edge of TI010 pin |                                                                                                                                               |  |  |  |

| 1                                     | 1 Captures on valid edge of TI000 pin by reverse phase <sup>Note</sup>                                                                        |  |  |  |

|                                       | ge of the TI010 and TI000 pin is set by PRM00.<br>d ES000 are set to 11 (both edges) when CRC001 is 1, the valid edge of the TI000 pin cannot |  |  |  |

| CRC000 | CR000 operating mode selection                                                                                                   |  |  |  |

|--------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0      | 0 Operates as compare register                                                                                                   |  |  |  |

| 1      | Operates as capture register                                                                                                     |  |  |  |

|        | If TMC003 and TMC002 are set to 11 (clear & start mode entered upon a match between TM00 and CR000), be sure to set CRC000 to 0. |  |  |  |

- **Note** When the valid edge is detected from the TI010 pin, the capture operation is not performed but the INTTM000 signal is generated as an external interrupt signal.

- Caution To ensure that the capture operation is performed properly, the capture trigger requires a pulse two cycles longer than the count clock selected by prescaler mode register 00 (PRM00).

- **Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

- n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

# Figure 7-12. Format of 16-Bit Timer Output Control Register 01 (TOC01)

| Address: FF | B9H After | reset: 00H | R/W    |               |                 |                 |        |       |

|-------------|-----------|------------|--------|---------------|-----------------|-----------------|--------|-------|

| Symbol      | 7         | <6>        | <5>    | 4             | <3>             | <2>             | 1      | <0>   |

| TOC01       | 0         | OSPT01     | OSPE01 | TOC014        | LVS01           | LVR01           | TOC011 | TOE01 |

|             |           |            |        |               |                 |                 |        |       |

|             | OSPT01    |            | (      | One-shot puls | e output trigge | er via software | )      |       |

| OSPT01                                                                                                        | One-shot pulse output trigger via software |  |

|---------------------------------------------------------------------------------------------------------------|--------------------------------------------|--|

| 0 –                                                                                                           |                                            |  |

| 1 One-shot pulse output                                                                                       |                                            |  |

| The value of this bit is always 0 when it is read. Do not set this bit to 1 in a mode other than the one-shot |                                            |  |

pulse output mode. If it is set to 1, TM01 is cleared and started.

| OSPE01       | One-shot pulse output operation control                                                                                                                                                                       |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0            | 0 Successive pulse output                                                                                                                                                                                     |  |  |  |

| 1            | One-shot pulse output                                                                                                                                                                                         |  |  |  |

| Tl001 pin va | lse output operates correctly in the free-running timer mode or clear & start mode entered by<br>lid edge input.<br>It pulse cannot be output in the clear & start mode entered upon a match between TM01 and |  |  |  |

| TOC014                                                             | TO01 output control on match between CR011 and TM01 |  |

|--------------------------------------------------------------------|-----------------------------------------------------|--|

| 0                                                                  | Disables inversion operation                        |  |

| 1                                                                  | Enables inversion operation                         |  |

| The interrupt signal (INTTM011) is generated even when TOC014 = 0. |                                                     |  |

| LVS01                                                                                                                                                       | LVR01 | Setting of TO01 output status                                        |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------------|--|--|--|--|

| 0                                                                                                                                                           | 0     | No change                                                            |  |  |  |  |

| 0                                                                                                                                                           | 1     | ial value of TO01 output is low level (TO01 output is cleared to 0). |  |  |  |  |

| 1                                                                                                                                                           | 0     | nitial value of TO01 output is high level (TO01 output is set to 1). |  |  |  |  |

| 1                                                                                                                                                           | 1     | Setting prohibited                                                   |  |  |  |  |

| • LVS01 and LVR01 can be used to set the initial value of the TO01 output level. If the initial value does not have to be set, leave LVS01 and LVR01 as 00. |       |                                                                      |  |  |  |  |

• Be sure to set LVS01 and LVR01 when TOE01 = 1.

LVS01, LVR01, and TOE01 being simultaneously set to 1 is prohibited.

• LVS01 and LVR01 are trigger bits. By setting these bits to 1, the initial value of the TO01 output level can be set. Even if these bits are cleared to 0, TO01 output is not affected.

• The values of LVS01 and LVR01 are always 0 when they are read.

• For how to set LVS01 and LVR01, see 7.5.2 Setting LVS0n and LVR0n.

The actual TO01/TI011/P06 pin output is determined depending on PM06 and P06, besides TO01 output.

| TOC011       | TO01 output control on match between CR001 and TM01                |  |

|--------------|--------------------------------------------------------------------|--|

| 0            | Disables inversion operation                                       |  |

| 1            | Enables inversion operation                                        |  |

| The interrup | The interrupt signal (INTTM001) is generated even when TOC011 = 0. |  |

| TOE0 | 1 | TO01 output control                                 |  |  |  |

|------|---|-----------------------------------------------------|--|--|--|

| 0    |   | Disables output (TO01 output is fixed to low level) |  |  |  |

| 1    |   | Enables output                                      |  |  |  |

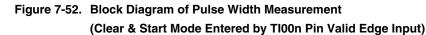

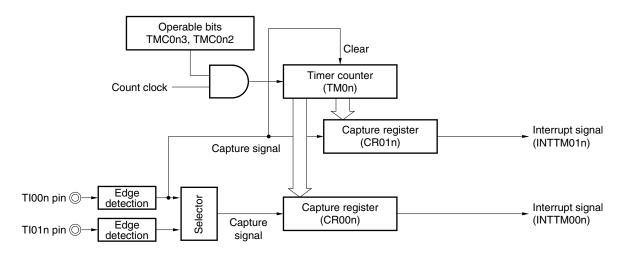

# 7.4.8 Pulse width measurement operation

TM0n can be used to measure the pulse width of the signal input to the TI00n and TI01n pins.

Measurement can be accomplished by operating the 16-bit timer/event counter 0n in the free-running timer mode or by restarting the timer in synchronization with the signal input to the TI00n pin.

When an interrupt is generated, read the value of the valid capture register and measure the pulse width. Check bit 0 (OVF0n) of 16-bit timer mode control register 0n (TMC0n). If it is set (to 1), clear it to 0 by software.

Figure 7-51. Block Diagram of Pulse Width Measurement (Free-Running Timer Mode)

**Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

#### Figure 7-57. Example of Software Processing for Pulse Width Measurement (2/2)

<1> Count operation start flow

<3> Count operation stop flow

- **Note** The capture interrupt signal (INTTM00n) is not generated when the reverse-phase edge of the TI00n pin input is selected to the valid edge of CR00n.

- **Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

- n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

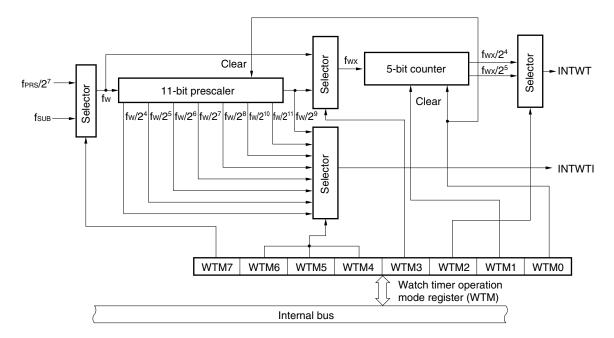

# CHAPTER 10 WATCH TIMER

|             | 78K0/KB2 | 78K0/KC2 | 78K0/KD2 | 78K0/KE2     | 78K0/KF2 |

|-------------|----------|----------|----------|--------------|----------|

| Watch timer | _        |          | ٦        | $\checkmark$ |          |

**Remark**  $\sqrt{}$ : Mounted, -: Not mounted

# 10.1 Functions of Watch Timer

The watch timer has the following functions.

- Watch timer

- Interval timer

The watch timer and the interval timer can be used simultaneously. Figure 10-1 shows the watch timer block diagram.

#### Figure 10-1. Block Diagram of Watch Timer

- **Remark** fprs: Peripheral hardware clock frequency

- fsub: Subsystem clock frequency

- fw: Watch timer clock frequency (fprs/2<sup>7</sup> or fsub)

- fwx: fw or fw/2 $^{9}$

| SBL62 | SBL61 | SBL60 | SBF transmission output width control |  |

|-------|-------|-------|---------------------------------------|--|

| 1     | 0     | 1     | SBF is output with 13-bit length.     |  |

| 1     | 1     | 0     | SBF is output with 14-bit length.     |  |

| 1     | 1     | 1     | SBF is output with 15-bit length.     |  |

| 0     | 0     | 0     | SBF is output with 16-bit length.     |  |

| 0     | 0     | 1     | SBF is output with 17-bit length.     |  |

| 0     | 1     | 0     | SBF is output with 18-bit length.     |  |

| 0     | 1     | 1     | SBF is output with 19-bit length.     |  |

| 1     | 0     | 0     | SBF is output with 20-bit length.     |  |

Figure 15-10. Format of Asynchronous Serial Interface Control Register 6 (ASICL6) (2/2)

| DIR6 | First-bit specification |

|------|-------------------------|

| 0    | MSB                     |

| 1    | LSB                     |

| TXDLV6 | Enables/disables inverting TxD6 output |

|--------|----------------------------------------|

| 0      | Normal output of TxD6                  |

| 1      | Inverted output of TxD6                |

Cautions 1. In the case of an SBF reception error, the mode returns to the SBF reception mode. The status of the SBRF6 flag is held (1).

- 2. Before setting the SBRT6 bit, make sure that bit 7 (POWER6) and bit 5 (RXE6) of ASIM6 = 1. After setting the SBRT6 bit to 1, do not clear it to 0 before SBF reception is completed (before an interrupt request signal is generated).

- 3. The read value of the SBRT6 bit is always 0. SBRT6 is automatically cleared to 0 after SBF reception has been correctly completed.

- 4. Before setting the SBTT6 bit to 1, make sure that bit 7 (POWER6) and bit 6 (TXE6) of ASIM6 = 1. After setting the SBTT6 bit to 1, do not clear it to 0 before SBF transmission is completed (before an interrupt request signal is generated).

- 5. The read value of the SBTT6 bit is always 0. SBTT6 is automatically cleared to 0 at the end of SBF transmission.

- 6. Do not set the SBRT6 bit to 1 during reception, and do not set the SBTT6 bit to 1 during transmission.

- 7. Before rewriting the DIR6 and TXDLV6 bits, clear the TXE6 and RXE6 bits to 0.

- 8. When the TXDLV6 bit is set to 1 (inverted TxD6 output), the TxD6/SCLA0/P60 pin cannot be used as a general-purpose port, regardless of the settings of POWER6 and TXE6. When using the TxD6/SCLA0/P60 pin as a general-purpose port, clear the TXDLV6 bit to 0 (normal TxD6 output).

# (2) Serial status register 0 (CSIS0)

This is an 8-bit register used to select the base clock, control the communication operation, and indicate the status of serial interface CSIA0.

This register can be set by a 1-bit or 8-bit memory manipulation instruction. However, rewriting CSIS0 is prohibited when bit 0 (TSF0) is 1.

Reset signal generation clears this register to 00H.

#### Figure 17-3. Format of Serial Status Register 0 (CSIS0) (1/2)

Address: FF91H After reset: 00H R/WNote 1

| Symbol |

|--------|

| CSIS0  |

| mbol | 7 | 6                       | 5     | 4      | 3       | 2     | 1     | 0    |

|------|---|-------------------------|-------|--------|---------|-------|-------|------|

| SIS0 | 0 | CKS00 <sup>Note 2</sup> | STBE0 | BUSYE0 | BUSYLV0 | ERRE0 | ERRF0 | TSF0 |

| CKS00 |                        | Base clock (fw) selection <sup>Note 3</sup> |              |               |                          |  |  |  |

|-------|------------------------|---------------------------------------------|--------------|---------------|--------------------------|--|--|--|

|       |                        | fprs = 2 MHz                                | fprs = 5 MHz | fprs = 10 MHz | fprs = 20 MHz            |  |  |  |

| 0     | fprs <sup>Note 4</sup> | 2 MHz                                       | 5 MHz        | 10 MHz        | 20 MHz <sup>Note 5</sup> |  |  |  |

| 1     | fprs/2                 | 1 MHz                                       | 2.5 MHz      | 5 MHz         | 10 MHz                   |  |  |  |

| S | STBE0 <sup>Notes 6, 7</sup> | Strobe output enable/disable |

|---|-----------------------------|------------------------------|

|   | 0                           | Strobe output disabled       |

|   | 1                           | Strobe output enabled        |

### Notes 1. Bits 0 and 1 are read-only.

- 2. Make sure that bit 7 (CSIAE0) of the Serial Operation Mode Specification Register 0 (CSIMA0) = 0 when rewriting the CKS00 bit.

- 3. The frequency that can be used for the peripheral hardware clock (fprs) differs depending on the power supply voltage and product specifications.

| Supply Voltage                                                                                                           | Conventional-specification Products<br>(µPD78F05xx and 78F05xxD) | Expanded-specification Products (µPD78F05xxA and 78F05xxDA) |

|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------|

| $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                                                                                    | $f_{PRS} \le 20 \text{ MHz}$                                     | $f_{PRS} \le 20 \text{ MHz}$                                |

| $2.7~V \leq V_{\text{DD}} < 4.0~V$                                                                                       | fprs ≤ 10 MHz                                                    |                                                             |

| $\begin{array}{l} 1.8 \ V \leq V_{DD} < 2.7 \ V \\ (Standard products and \\ (A) \ grade \ products \ only) \end{array}$ | fprs ≤ 5 MHz                                                     | fprs ≤ 5 MHz                                                |

(The values shown in the table above are those when fPRS = fXH (XSEL = 1).)

- If the peripheral hardware clock (fPRs) operates on the internal high-speed oscillation clock (fRH) (XSEL = 0), when 1.8 V ≤ VDD < 2.7 V, the setting of CKS00 = 0 (base clock: fPRs) is prohibited.</li>

- 5. This is settable only if 4.0 V  $\leq$  V\_{DD}  $\leq$  5.5 V.

- 6. STBE0 is valid only in master mode.

- 7. When STBE0 is set to 1, two transfer clocks are consumed between byte transfers regardless of the setting of automatic data transfer interval specification register 0 (ADTI0). That is, 10 transfer clocks are used for 1-byte transfer if ADTI0 = 00H is set.

## Caution Be sure to clear bit 7 to 0.

**Remark** fprs: Peripheral hardware clock frequency

# (5) Automatic data transfer address point specification register 0 (ADTP0)

This is an 8-bit register used to specify the buffer RAM address that ends transfer during automatic data transfer (bit 6 (ATE0) of serial operation mode specification register 0 = 1).

This register can be set by an 8-bit memory manipulation instruction. However, during transfer (TSF0 = 1), rewriting ADTP0 is prohibited.

In the 78K0/KF2, 00H to 1FH can be specified because 32 bytes of buffer RAM are incorporated.

# Example When ADTP0 is set to 07H

8 bytes of FA00H to FA07H are transferred.

In repeat transfer mode (bit 5 (ATM0) of CSIMA0 = 1), transfer is performed repeatedly up to the address specified with ADTP0.

Example When ADTP0 is set to 07H (repeat transfer mode)

Transfer is repeated as FA00H to FA07H, FA00H to FA07H, ....

### Figure 17-6. Format of Automatic Data Transfer Address Point Specification Register 0 (ADTP0)

Address: FF94H After reset: 00H R/W

| Symbol | 7 | 6 | 5 | 4      | 3      | 2      | 1      | 0      |

|--------|---|---|---|--------|--------|--------|--------|--------|

| ADTP0  | 0 | 0 | 0 | ADTP04 | ADTP03 | ADTP02 | ADTP01 | ADTP00 |

#### Caution Be sure to clear bits 7 to 5 to "0".

The relationship between transfer end buffer RAM address values and ADTP0 setting values is shown below.

#### Table 17-2. Relationship Between Transfer End Buffer RAM Address Values and ADTP0 Setting Values

| Transfer End Buffer RAM<br>Address Value | ADTP0 Setting Value |

|------------------------------------------|---------------------|

| FAxxH                                    | ххН                 |

Remark xx: 00 to 1F

# 18.3 Registers to Control Serial Interface IIC0

Serial interface IIC0 is controlled by the following seven registers.

- IIC control register 0 (IICC0)

- IIC flag register 0 (IICF0)

- IIC status register 0 (IICS0)

- IIC clock selection register 0 (IICCL0)

- IIC function expansion register 0 (IICX0)

- Port mode register 6 (PM6)

- Port register 6 (P6)

# (1) IIC control register 0 (IICC0)

This register is used to enable/stop I<sup>2</sup>C operations, set wait timing, and set other I<sup>2</sup>C operations.

IICC0 register is set by a 1-bit or 8-bit memory manipulation instruction. However, set the SPIE0, WTIM0, and ACKE0 bits while IICE0 bit = 0 or during the wait period. These bits can be set at the same time when the IICE0 bit is set from "0" to "1".

Reset signal generation clears IICC0 to 00H.

## 18.5.14 Communication reservation

(1) When communication reservation function is enabled (bit 0 (IICRSV) of IIC flag register 0 (IICF0) = 0)

To start master device communications when not currently using a bus, a communication reservation can be made to enable transmission of a start condition when the bus is released. There are two modes under which the bus is not used.

- When arbitration results in neither master nor slave operation

- When an extension code is received and slave operation is disabled (ACK is not returned and the bus was released when bit 6 (LREL0) of IIC control register 0 (IICC0) was set to 1).

If bit 1 (STT0) of IICC0 is set to 1 while the bus is not used (after a stop condition is detected), a start condition is automatically generated and wait state is set.

If an address is written to IIC shift register 0 (IIC0) after bit 4 (SPIE0) of IICC0 was set to 1, and it was detected by generation of an interrupt request signal (INTIIC0) that the bus was released (detection of the stop condition), then the device automatically starts communication as the master. Data written to IIC0 before the stop condition is detected is invalid.

When STT0 has been set to 1, the operation mode (as start condition or as communication reservation) is determined according to the bus status.

- If the bus has been released ......a start condition is generated

- If the bus has not been released (standby mode)...... communication reservation

Check whether the communication reservation operates or not by using MSTS0 bit (bit 7 of IIC status register 0 (IICS0)) after STT0 bit is set to 1 and the wait time elapses.

The wait periods, which should be set via software, are listed in Table 18-6.

| CLX0 | SMC0 | CL01 | CL00 | Wait Period |

|------|------|------|------|-------------|

| 0    | 0    | 0    | 0    | 46 clocks   |

| 0    | 0    | 0    | 1    | 86 clocks   |

| 0    | 0    | 1    | 0    | 172 clocks  |

| 0    | 0    | 1    | 1    | 34 clocks   |

| 0    | 1    | 0    | 0    | 30 clocks   |

| 0    | 1    | 0    | 1    |             |

| 0    | 1    | 1    | 0    | 60 clocks   |

| 0    | 1    | 1    | 1    | 12 clocks   |

| 1    | 1    | 0    | 0    | 18 clocks   |

| 1    | 1    | 0    | 1    |             |

| 1    | 1    | 1    | 0    | 36 clocks   |

#### Table 18-6. Wait Periods

Figure 18-20 shows the communication reservation timing.

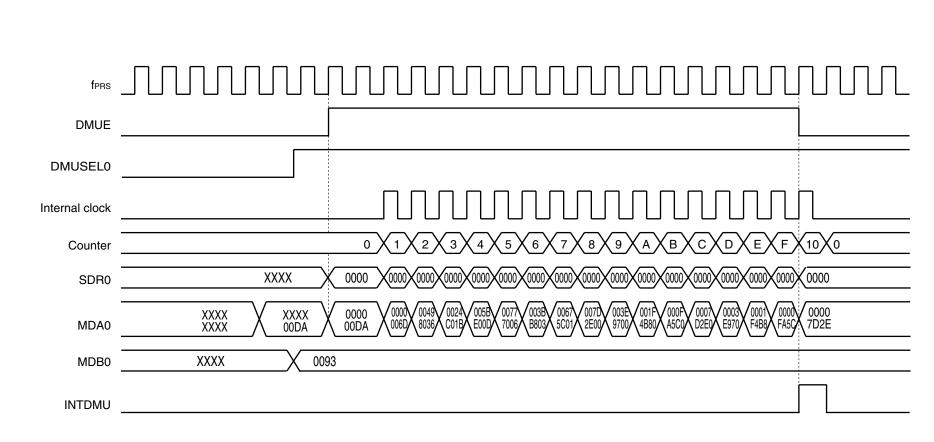

Figure 19-6. Timing Chart of Multiplication Operation (00DAH × 0093H)

R01UH0008EJ0401 Rev.4.01 Jul 15, 2010 78K0/Kx2

627

## (2) Interrupt mask flag registers (MK0L, MK0H, MK1L, MK1H)

The interrupt mask flags are used to enable/disable the corresponding maskable interrupt servicing.

MK0L, MK0H, MK1L, and MK1H are set by a 1-bit or 8-bit memory manipulation instruction. When MK0L and MK0H, and MK1L and MK1H are combined to form 16-bit registers MK0 and MK1, they are set by a 16-bit memory manipulation instruction.

Reset signal generation sets these registers to FFH.

#### Figure 20-7. Format of Interrupt Mask Flag Registers (MK0L, MK0H, MK1L, MK1H) (78K0/KB2)

| Address: FF | E4H After r | eset: FFH                   | R/W                   |        |        |         |       |        |  |

|-------------|-------------|-----------------------------|-----------------------|--------|--------|---------|-------|--------|--|

| Symbol      | <7>         | <6>                         | <5>                   | <4>    | <3>    | <2>     | <1>   | <0>    |  |

| MK0L        | SREMK6      | PMK5                        | PMK4                  | PMK3   | PMK2   | PMK1    | PMK0  | LVIMK  |  |

|             |             |                             |                       |        |        |         |       |        |  |

| Address: FF | E5H After r | eset: FFH                   | R/W                   |        |        |         |       |        |  |

| Symbol      | <7>         | <6>                         | <5>                   | <4>    | <3>    | <2>     | <1>   | <0>    |  |

| МКОН        | TMMK010     | TMMK000                     | TMMK50                | TMMKH0 | TMMKH1 | DUALMK0 | STMK6 | SRMK6  |  |

|             |             |                             |                       |        |        | CSIMK10 |       |        |  |

|             |             |                             |                       |        |        | STMK0   |       |        |  |

|             |             |                             |                       |        |        |         |       |        |  |

| Address: FF | E6H After r | eset: FFH                   | R/W                   |        |        |         |       |        |  |

| Symbol      | 7           | 6                           | 5                     | 4      | <3>    | 2       | <1>   | <0>    |  |

| MK1L        | 1           | 1                           | 1                     | 1      | TMMK51 | 1       | SRMK0 | ADMK   |  |

|             |             |                             |                       |        |        |         |       |        |  |

| Address: FF | E7H After r | eset: FFH                   | R/W                   |        |        |         |       |        |  |

| Symbol      | 7           | 6                           | 5                     | 4      | 3      | 2       | 1     | <0>    |  |

| MK1H        | 1           | 1                           | 1                     | 1      | 1      | 1       | 1     | IICMK0 |  |

|             |             |                             |                       |        |        |         |       |        |  |

|             | ХХМКХ       | Interrupt servicing control |                       |        |        |         |       |        |  |

|             | 0           | Interrupt ser               | vicing enable         | b      |        |         |       |        |  |

|             | 1           | Interrupt ser               | pt servicing disabled |        |        |         |       |        |  |

Caution Be sure to set bits 2, 4 to 7 of MK1L and bits 1 to 7 of MK1H to 1.

# Table 27-13. Processing Time for Self Programming Library(Conventional-specification Products ( $\mu$ PD78F05xx and 78F05xxD)) (3/4)

# (3) When high-speed system clock (X1 oscillation or external clock input) is used and entry RAM is located outside short direct addressing range

| Librar                   | y Name            |                             | Processing                               | g Time (μs)                          |                              |  |  |  |

|--------------------------|-------------------|-----------------------------|------------------------------------------|--------------------------------------|------------------------------|--|--|--|

|                          |                   | Normal Model                | of C Compiler                            | Static Model of C Compiler/Assembler |                              |  |  |  |

|                          |                   | Min.                        | Max.                                     | Min.                                 | Max.                         |  |  |  |

| Self programming start I | ibrary            | <b>34/f</b> gpu             |                                          |                                      |                              |  |  |  |

| Initialize library       |                   |                             | 49/fcpu +                                | 485.8125                             |                              |  |  |  |

| Mode check library       |                   | 35/fсри -                   | - 374.75                                 | <b>29/f</b> сри -                    | - 374.75                     |  |  |  |

| Block blank check librar | y                 | 174/fcpu +                  | 6382.0625                                | 134/fcpu +                           | 6382.0625                    |  |  |  |

| Block erase library      |                   | 174/fcpu +<br>31093.875     | 174/fсри +<br>298948.125                 | 134/fcpu +<br>31093.875              | 134/fcpu +<br>298948.125     |  |  |  |

| Word write library       |                   | 318 (321)/fcpu +<br>644.125 | 318 (321)/fcpu +<br>1491.625             | 262 (265)/fcpu +<br>644.125          | 262 (265)/fсри +<br>1491.625 |  |  |  |

| Block verify library     |                   | <b>174/f</b> сри + 1        | 174/fcpu + 13448.5625 134/fcpu + 13448.5 |                                      |                              |  |  |  |

| Self programming end li  | brary             | 34/fcpu                     |                                          |                                      |                              |  |  |  |

| Get information library  | Option value: 03H | 171 (172 )/fc               | •∪ + 432.4375                            | 129 (130)/fcpu + 432.4375            |                              |  |  |  |

|                          | Option value: 04H | <b>181 (182)/f</b> c        | ри <b>+ 427.875</b>                      | <b>139 (140)/f</b> c                 | ри <b>+ 427.875</b>          |  |  |  |

| Option value: 05H        |                   | <b>404 (411)/f</b> c        | ри <b>+ 496.125</b>                      | 362 (369)/fcpu+ 496.125              |                              |  |  |  |

| Set information library  |                   | 75/fcpu +<br>79157.6875     | 75/fcpu + 652400                         | 67fсец +<br>79157.6875               | 67fcpu + 652400              |  |  |  |

| EEPROM write library     |                   | 318 (321)/fcpu +<br>799.875 | 318 (321)/fcթu +<br>1647.375             | 262 (265)/fcpu +<br>799.875          | 262 (265)/fсри +<br>1647.375 |  |  |  |

**Remarks 1.** Values in parentheses indicate values when a write start address structure is located other than in the internal high-speed RAM.

- 2. The above processing times are those during stabilized operation of the internal high-speed oscillator (RSTS = 1).

- **3.** fcpu: CPU operation clock frequency

- 4. RSTS: Bit 7 of the internal oscillation mode register (RCM)

| Instruction | Magmonia | Onerende       | Dutos          | Clocks |        | Operation                                    |   | Fla | g   |

|-------------|----------|----------------|----------------|--------|--------|----------------------------------------------|---|-----|-----|

| Group       | Mnemonic | Operands       | Bytes          | Note 1 | Note 2 | Operation                                    | Z | AC  | CCY |

| 16-bit data | MOVW     | rp, #word      | 3              | 6      | -      | $rp \leftarrow word$                         |   |     |     |

| transfer    |          | saddrp, #word  | 4              | 8      | 10     | $(saddrp) \leftarrow word$                   |   |     |     |

|             |          | sfrp, #word    | 4              | -      | 10     | $sfrp \leftarrow word$                       |   |     |     |

|             |          | AX, saddrp     | 2              | 6      | 8      | $AX \leftarrow (saddrp)$                     |   |     |     |

|             |          | saddrp, AX     | 2              | 6      | 8      | $(saddrp) \leftarrow AX$                     |   |     |     |

|             |          | AX, sfrp       | 2              | -      | 8      | AX ← sfrp                                    |   |     |     |

|             |          | sfrp, AX       | 2              | -      | 8      | sfrp $\leftarrow$ AX                         |   |     |     |

|             |          | AX, rp         | <sup>3</sup> 1 | 4      | -      | $AX \leftarrow rp$                           |   |     |     |

|             |          | rp, AX         | <sup>3</sup> 1 | 4      | -      | $rp \leftarrow AX$                           |   |     |     |

|             |          | AX, !addr16    | 3              | 10     | 12     | $AX \leftarrow (addr16)$                     |   |     |     |

|             |          | !addr16, AX    | 3              | 10     | 12     | (addr16) ← AX                                |   |     |     |

|             | XCHW     | AX, rp         | <sup>3</sup> 1 | 4      | -      | $AX \leftrightarrow rp$                      |   |     |     |

| 8-bit       | ADD      | A, #byte       | 2              | 4      | -      | A, CY $\leftarrow$ A + byte                  | × | ×   | ×   |

| operation   |          | saddr, #byte   | 3              | 6      | 8      | (saddr), CY $\leftarrow$ (saddr) + byte      | × | ×   | ×   |

|             |          | A, r           | 4 2            | 4      | -      | A, CY $\leftarrow$ A + r                     | × | x   | ×   |

|             |          | r, A           | 2              | 4      | -      | $r, CY \leftarrow r + A$                     | × | ×   | ×   |

|             |          | A, saddr       | 2              | 4      | 5      | A, CY $\leftarrow$ A + (saddr)               | × | х   | ×   |

|             |          | A, !addr16     | 3              | 8      | 9      | A, CY $\leftarrow$ A + (addr16)              | × | ×   | ×   |

|             |          | A, [HL]        | 1              | 4      | 5      | A, CY $\leftarrow$ A + (HL)                  | × | х   | ×   |

|             |          | A, [HL + byte] | 2              | 8      | 9      | A, CY $\leftarrow$ A + (HL + byte)           | × | х   | ×   |

|             |          | A, [HL + B]    | 2              | 8      | 9      | A, CY $\leftarrow$ A + (HL + B)              | × | ×   | ×   |

|             |          | A, [HL + C]    | 2              | 8      | 9      | $A,CY \leftarrow A + (HL + C)$               | × | ×   | ×   |

|             | ADDC     | A, #byte       | 2              | 4      | -      | A, CY $\leftarrow$ A + byte + CY             | × | х   | ×   |

|             |          | saddr, #byte   | 3              | 6      | 8      | (saddr), $CY \leftarrow (saddr) + byte + CY$ | × | ×   | ×   |

|             |          | A, r           | 4 2            | 4      | -      | $A,CY \leftarrow A + r + CY$                 | × | ×   | ×   |

|             |          | r, A           | 2              | 4      | _      | $r, CY \leftarrow r + A + CY$                | × | ×   | ×   |

|             |          | A, saddr       | 2              | 4      | 5      | A, CY $\leftarrow$ A + (saddr) + CY          | × | ×   | ×   |

|             |          | A, !addr16     | 3              | 8      | 9      | A, CY $\leftarrow$ A + (addr16) + C          | × | ×   | ×   |

|             |          | A, [HL]        | 1              | 4      | 5      | $A,CY \leftarrow A + (HL) + CY$              | × | ×   | ×   |

|             |          | A, [HL + byte] | 2              | 8      | 9      | A, CY $\leftarrow$ A + (HL + byte) + CY      | × | ×   | ×   |

|             |          | A, [HL + B]    | 2              | 8      | 9      | $A,CY \leftarrow A + (HL + B) + CY$          | × | ×   | ×   |

|             |          | A, [HL + C]    | 2              | 8      | 9      | $A, CY \leftarrow A + (HL + C) + CY$         | × | ×   | ×   |

Notes 1. When the internal high-speed RAM area is accessed or for an instruction with no data access

2. When an area except the internal high-speed RAM area is accessed

- **3.** Only when rp = BC, DE or HL

- 4. Except "r = A"

- **Remarks 1.** One instruction clock cycle is one cycle of the CPU clock (fcPu) selected by the processor clock control register (PCC).

- 2. This clock cycle applies to the internal ROM program.

# Caution The pins mounted depend on the product. Refer to Caution 2 at the beginning of this chapter.

| Parameter                                                          | Symbol        |                                                 | Conditions                                                | MIN.                            | TYP. | MAX.                            | Unit |

|--------------------------------------------------------------------|---------------|-------------------------------------------------|-----------------------------------------------------------|---------------------------------|------|---------------------------------|------|

| SCKA0 cycle time                                                   | <b>t</b> ксү4 | $4.0~V \leq V_{\text{DD}} \leq 5.4$             | 5 V                                                       | 600                             |      |                                 | ns   |

|                                                                    |               | $2.7~V \leq V_{\text{DD}} < 4.4$                | 0 V                                                       | 1200                            |      |                                 | ns   |

|                                                                    |               | $1.8 \text{ V} \leq \text{V}_{\text{DD}} < 2.7$ | 7 V                                                       | 1800                            |      |                                 | ns   |

| SCKA0 high-/low-level width                                        | tкн4,         | $4.0~V \leq V_{\text{DD}} \leq 5.4$             | 5 V                                                       | 300                             |      |                                 | ns   |

|                                                                    | tkl4          | $2.7 \text{ V} \leq \text{V}_{\text{DD}} < 4.9$ | 600                                                       |                                 |      | ns                              |      |

|                                                                    |               | $1.8 \text{ V} \leq \text{V}_{\text{DD}} < 2.7$ | 900                                                       |                                 |      | ns                              |      |

| SIA0 setup time (to $\overline{\text{SCKA0}}$ )                    | tsik4         |                                                 |                                                           | 100                             |      |                                 | ns   |

| SIA0 hold time (from $\overline{\text{SCKA0}}^{\uparrow}$ )        | tksi4         |                                                 |                                                           | 2/fw +<br>100 <sup>Note 1</sup> |      |                                 | ns   |

| Delay time from $\overline{\text{SCKA0}}\downarrow$ to SOA0 output |               |                                                 | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                     |                                 |      | 2/fw +<br>100 <sup>Note 1</sup> | ns   |

|                                                                    |               |                                                 | $2.7 \text{ V} \leq \text{V}_{\text{DD}} < 4.0 \text{ V}$ |                                 |      | 2/fw +<br>200 <sup>Note 1</sup> | ns   |

|                                                                    |               |                                                 | $1.8~V \leq V_{\text{DD}} < 2.7~V$                        |                                 |      | 2/fw +<br>300 <sup>Note 1</sup> | ns   |

| SCKA0 rise/fall time                                               | tr4, tr4      |                                                 |                                                           |                                 |      | 1000                            | ns   |

# (g) CSIA0 (slave mode, SCKA0...external clock input)

Notes 1. fw is the CSIA0 base clock selected by the CSIS0 register.

**2.** C is the load capacitance of the SOA0 output line.

# Caution The pins mounted depend on the product. Refer to Caution at the beginning of this chapter.

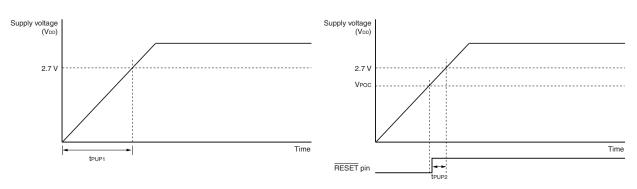

# Supply Voltage Rise Time (T<sub>A</sub> = -40 to +110°C, Vss = EVss = 0 V)

| Parameter                                                                                                                                         | Symbol        | Conditions                                                                           | MIN. | TYP. | MAX. | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------------|------|------|------|------|

| Maximum time to rise to 2.7 V (V_{DD} (MIN.)) (V_{DD}: 0 V $\rightarrow$ 2.7 V)                                                                   | <b>t</b> pup1 | POCMODE (option byte) = 0,<br>when $\overrightarrow{\text{RESET}}$ input is not used |      |      | 3.6  | ms   |

| Maximum time to rise to 2.7 V (V <sub>DD</sub> (MIN.))<br>(releasing $\overrightarrow{\text{RESET}}$ input $\rightarrow$ V <sub>DD</sub> : 2.7 V) | tpup2         | POCMODE (option byte) = 0,<br>when RESET input is used                               |      |      | 1.9  | ms   |

# Supply Voltage Rise Time Timing

$\bullet$  When  $\overline{\text{RESET}}$  pin input is not used

# • When $\overline{\text{RESET}}$ pin input is used

| Serial trigger register 0 (CSIT0)                 | 519 |

|---------------------------------------------------|-----|

| Slave address register 0 (SVA0)                   | 553 |

| 16-bit timer capture/compare register 000 (CR000) | 273 |

| 16-bit timer capture/compare register 001 (CR001) | 273 |

| 16-bit timer capture/compare register 010 (CR010) | 273 |

| 16-bit timer capture/compare register 011 (CR011) | 273 |

| 16-bit timer counter 00 (TM00)                    | 272 |

| 16-bit timer counter 01 (TM00)                    | 272 |

| 16-bit timer mode control register 00 (TMC00)     | 277 |

| 16-bit timer mode control register 01 (TMC01)     | 277 |

| 16-bit timer output control register 00 (TOC00)   | 282 |

| 16-bit timer output control register 01 (TOC01)   | 282 |

# [T]

| Timer clock selection register 50 (TCL50)    | . 348 |

|----------------------------------------------|-------|

| Timer clock selection register 51 (TCL51)    | . 348 |

| 10-bit A/D conversion result register (ADCR) | . 416 |

| Transmit buffer register 10 (SOTB10)         | . 492 |

| Transmit buffer register 11 (SOTB11)         | . 492 |

| Transmit buffer register 6 (TXB6)            | . 459 |

| Transmit shift register 0 (TXS0)             | . 435 |

| Transmit shift register 6 (TXS6)             | . 459 |

| [W]                                          |       |

| Watch timer operation mode register (WTM) | 391 |

|-------------------------------------------|-----|

| Watchdog timer enable register (WDTE)     | 398 |

|            |                |                        |                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                               | (11/3  | 30) |

|------------|----------------|------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|

| Chapter    | Classification | Function               | Details of<br>Function                                                                                     | Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page   |     |

| Chapter 9  |                | 8-bit timers<br>H0, H1 | TMCYC1: 8-bit<br>timer H carrier<br>register 1                                                             | Do not rewrite RMC1 when TMHE = 1. However, TMCYC1 can be refreshed (the same value is written).                                                                                                                                                                                                                                                                                                                                              | p. 371 |     |

| C          | Hard           |                        | PWM output                                                                                                 | The set value of the CMP1n register can be changed while the timer counter is operating. However, this takes a duration of three operating clocks (signal selected by the CKSn2 to CKSn0 bits of the TMHMDn register) from when the value of the CMP1n register is changed until the value is transferred to the register.                                                                                                                    | p. 377 |     |

|            | Soft           |                        |                                                                                                            | Be sure to set the CMP1n register when starting the timer count operation (TMHEn = 1) after the timer count operation was stopped (TMHEn = 0) (be sure to set again even if setting the same value to the CMP1n register).                                                                                                                                                                                                                    | p. 377 |     |

|            |                |                        |                                                                                                            | Make sure that the CMP1n register setting value (M) and CMP0n register setting value (N) are within the following range.<br>$00H \le CMP1n (M) < CMP0n (N) \le FFH$                                                                                                                                                                                                                                                                           | p. 377 |     |

|            |                |                        | Carrier<br>generator (8-bit                                                                                | Do not rewrite the NRZB1 bit again until at least the second clock after it has been rewritten, or else the transfer from the NRZB1 bit to the NRZ1 bit is not guaranteed.                                                                                                                                                                                                                                                                    | p. 383 |     |

|            |                |                        | timer H1 only)                                                                                             | When the 8-bit timer/event counter 51 is used in the carrier generator mode, an interrupt is generated at the timing of $<1>$ . When the 8-bit timer/event counter 51 is used in a mode other than the carrier generator mode, the timing of the interrupt generation differs.                                                                                                                                                                | p. 383 |     |

|            |                |                        |                                                                                                            | Be sure to set the CMP11 register when starting the timer count operation (TMHE1 = 1) after the timer count operation was stopped (TMHE1 = 0) (be sure to set again even if setting the same value to the CMP11 register).                                                                                                                                                                                                                    | p. 385 |     |

|            |                |                        | Set so that the count clock frequency of TMH1 becomes more than 6 times the count clock frequency of TM51. | p. 385                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |     |

|            |                |                        |                                                                                                            | Set the values of the CMP01 and CMP11 registers in a range of 01H to FFH.                                                                                                                                                                                                                                                                                                                                                                     | p. 385 |     |

|            |                |                        |                                                                                                            | The set value of the CMP11 register can be changed while the timer counter is operating. However, it takes the duration of three operating clocks (signal selected by the CKS12 to CKS10 bits of the TMHMD1 register) since the value of the CMP11 register has been changed until the value is transferred to the register.                                                                                                                  | p. 385 |     |

|            |                |                        |                                                                                                            | Be sure to set the RMC1 bit before the count operation is started.                                                                                                                                                                                                                                                                                                                                                                            | p. 385 |     |

| Chapter 10 | Soft           | Watch<br>timer         | WTM: Watch<br>timer operation<br>mode register                                                             | Do not change the count clock and interval time (by setting bits 4 to 7 (WTM4 to WTM7) of WTM) during watch timer operation.                                                                                                                                                                                                                                                                                                                  | p. 393 |     |

| Ch         | Hard           |                        | Interrupt request                                                                                          | When operation of the watch timer and 5-bit counter is enabled by the watch timer mode control register (WTM) (by setting bits 0 (WTM0) and 1 (WTM1) of WTM to 1), the interval until the first interrupt request signal (INTWT) is generated after the register is set does not exactly match the specification made with bits 2 and 3 (WTM2, WTM3) of WTM. Subsequently, however, the INTWT signal is generated at the specified intervals. | p. 395 |     |

| Chapter 11 | timer e        |                        | WDTE:<br>Watchdog timer<br>enable register                                                                 | If a value other than ACH is written to WDTE, an internal reset signal is generated. If the source clock to the watchdog timer is stopped, however, an internal reset signal is generated when the source clock to the watchdog timer resumes operation.                                                                                                                                                                                      | p. 398 |     |

| Ch         |                |                        |                                                                                                            | If a 1-bit memory manipulation instruction is executed for WDTE, an internal reset signal is generated. If the source clock to the watchdog timer is stopped, however, an internal reset signal is generated when the source clock to the watchdog timer resumes operation.                                                                                                                                                                   | p. 398 |     |

|            |                |                        |                                                                                                            | The value read from WDTE is 9AH/1AH (this differs from the written value (ACH)).                                                                                                                                                                                                                                                                                                                                                              | p. 398 |     |

|            |                |                        | Operation<br>control                                                                                       | The first writing to WDTE after a reset release clears the watchdog timer, if it is made before the overflow time regardless of the timing of the writing, and the watchdog timer starts counting again.                                                                                                                                                                                                                                      | p. 399 |     |

|            |                |                        |                                                                                                            | If the watchdog timer is cleared by writing "ACH" to WDTE, the actual overflow time may be different from the overflow time set by the option byte by up to 2/fRL seconds.                                                                                                                                                                                                                                                                    | p. 399 |     |