Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | 78K/0                                                                                 |

| Core Size                  | 8-Bit                                                                                 |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                                    |

| Number of I/O              | 55                                                                                    |

| Program Memory Size        | 96KB (96K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 5K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 8x10b                                                                             |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 64-TQFP                                                                               |

| Supplier Device Package    | ·                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0536aga-hab-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

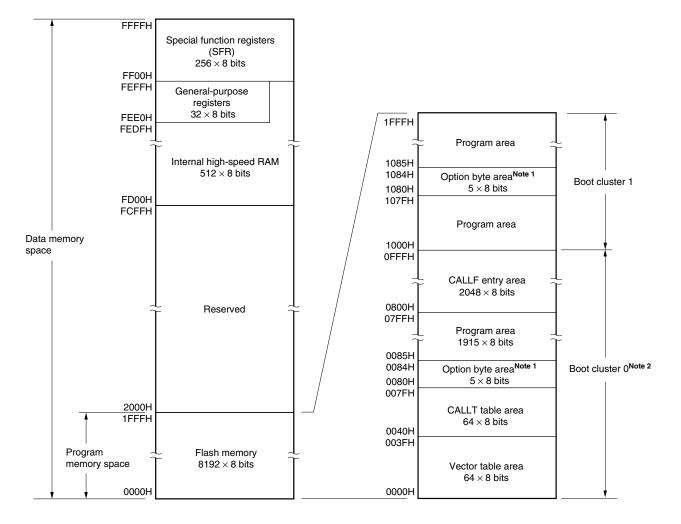

Figure 3-1. Memory Map (µPD78F0500 and 78F0500A)

Notes 1. When boot swap is not used: Set the option bytes to 0080H to 0084H.

When boot swap is used: Set the option bytes to 0080H to 0084H and 1080H to 1084H.

- 2. Writing boot cluster 0 can be prohibited depending on the setting of security (see 27.8 Security Settings).

- **Remark** The flash memory is divided into blocks (one block = 1 KB). For the address values and block numbers, see **Table 3-3 Correspondence Between Address Values and Block Numbers in Flash Memory**.

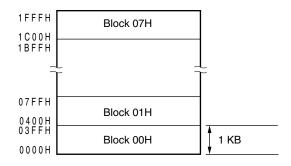

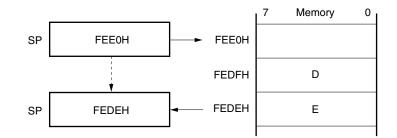

## 3.4.9 Stack addressing

## [Function]

The stack area is indirectly addressed with the stack pointer (SP) contents.

This addressing method is automatically employed when the PUSH, POP, subroutine call and return instructions are executed or the register is saved/reset upon generation of an interrupt request.

With stack addressing, only the internal high-speed RAM area can be accessed.

## [Description example]

PUSH DE; when saving DE register

Operation code

1 0 1 1 0 1 0 1

## [Illustration]

## 5.4 Port Function Operations

Port operations differ depending on whether the input or output mode is set, as shown below.

## 5.4.1 Writing to I/O port

## (1) Output mode

A value is written to the output latch by a transfer instruction, and the output latch contents are output from the pin. Once data is written to the output latch, it is retained until data is written to the output latch again. The data of the output latch is cleared when a reset signal is generated.

## (2) Input mode

A value is written to the output latch by a transfer instruction, but since the output buffer is off, the pin status does not change.

Once data is written to the output latch, it is retained until data is written to the output latch again. The data of the output latch is cleared when a reset signal is generated.

## 5.4.2 Reading from I/O port

## (1) Output mode

The output latch contents are read by a transfer instruction. The output latch contents do not change.

## (2) Input mode

The pin status is read by a transfer instruction. The output latch contents do not change.

## 5.4.3 Operations on I/O port

## (1) Output mode

An operation is performed on the output latch contents, and the result is written to the output latch. The output latch contents are output from the pins.

Once data is written to the output latch, it is retained until data is written to the output latch again. The data of the output latch is cleared when a reset signal is generated.

## (2) Input mode

The pin level is read and an operation is performed on its contents. The result of the operation is written to the output latch, but since the output buffer is off, the pin status does not change.

The data of the output latch is cleared when a reset signal is generated.

## 5.5 Settings of Port Mode Register and Output Latch When Using Alternate Function

To use the alternate function of a port pin, set the port mode register and output latch as shown in Table 5-6.

Remark The port pins mounted depend on the product. See Table 5-3. Port Functions.

| Pin Name   | Alternate Function     | PM××   | P×× |   |

|------------|------------------------|--------|-----|---|

|            | Function Name          | I/O    |     |   |

| P30 to P32 | INTP1 to INTP3         | Input  | 1   | × |

| P33        | INTP4                  | Input  | 1   | × |

|            | TI51                   | Input  | 1   | × |

|            | TO51                   | Output | 0   | 0 |

| P60        | SCL0                   | I/O    | 0   | 0 |

| P61        | SDA0                   | I/O    | 0   | 0 |

| P62        | EXSCL0                 | Input  | 1   | × |

| P70 to P77 | KR0 to KR7             | Input  | 1   | × |

| P120       | INTP0                  | Input  | 1   | × |

|            | EXLVI                  | Input  | 1   | × |

| P121       | X1 <sup>Note</sup>     | -      | ×   | × |

| P122       | X2 <sup>Note</sup>     | _      | х   | × |

|            | EXCLK <sup>Note</sup>  | Input  | ×   | × |

| P123       | XT1 <sup>Note</sup>    | -      | ×   | × |

| P124       | XT2 <sup>Note</sup>    | -      | ×   | × |

|            | EXCLKS <sup>Note</sup> | Input  | ×   | × |

| P140       | PCL                    | Output | 0   | 0 |

|            | INTP6                  | Input  | 1   | × |

| P141       | BUZ                    | Output | 0   | 0 |

|            | INTP7                  | Input  | 1   | × |

|            | BUSY0                  | Input  | 1   | × |

| P142       | SCKAO                  | Input  | 1   | × |

|            |                        | Output | 0   | 1 |

| P143       | SIA0                   | Input  | 1   | × |

| P144       | SOA0                   | Output | 0   | 0 |

| P145       | STB0                   | Output | 0   | 0 |

Table 5-6. Settings of Port Mode Register and Output Latch When Using Alternate Function (2/2)

- Note When using the P121 to P124 pins to connect a resonator for the main system clock (X1, X2) or subsystem clock (XT1, XT2), or to input an external clock for the main system clock (EXCLK) or subsystem clock (EXCLKS), the X1 oscillation mode, XT1 oscillation mode, or external clock input mode must be set by using the clock operation mode select register (OSCCTL) (for details, see 6.3 (1) Clock operation mode select register (OSCCTL) and (3) Setting of operation mode for subsystem clock pin). The reset value of OSCCTL is 00H (all of the P121 to P124 are I/O port pins). At this time, setting of PM121 to PM124 and P121 to P124 is not necessary.

- Remarks 1. ×: Don't care

- PM××: Port mode register

- Pxx: Port output latch

- X1, X2, P31, and P32 of the product with an on-chip debug function (μPD78F05xxD and 78F05xxDA) can be used as on-chip debug mode setting pins (OCD0A, OCD0B, OCD1A, and OCD1B) when the on-chip debug function is used. For how to connect an on-chip debug emulator (QB-MINI2), see CHAPTER 28 ON-CHIP DEBUG FUNCTION (μPD78F05xxD AND 78F05xxDA ONLY).

| Address: FF         | FBH Afte | r reset: 01H  | R/W <sup>Note 1</sup> |      |                    |               |                |      |

|---------------------|----------|---------------|-----------------------|------|--------------------|---------------|----------------|------|

| Symbol              | 7        | 6             | <5>                   | <4>  | 3                  | 2             | 1              | 0    |

| PCC                 | 0        | XTSTART Note2 | CLS                   | CSS  | 0                  | PCC2          | PCC1           | PCC0 |

|                     |          |               |                       |      |                    |               |                |      |

|                     | CLS      |               |                       | C    | PU clock statu     | JS            |                |      |

| 0 Main system clock |          |               |                       |      |                    |               |                |      |

|                     | 1        | Subsystem c   | lock                  |      |                    |               |                |      |

|                     | 1        | 1             |                       |      |                    |               |                |      |

|                     | CSS      | PCC2          | PCC1                  | PCC0 |                    | CPU clock (fe | CPU) selection |      |

|                     | 0        | 0             | 0                     | 0    | fxp                |               |                |      |

|                     |          | 0             | 0                     | 1    | fxp/2 (default     | t)            |                |      |

|                     |          | 0             | 1                     | 0    | fxp/2 <sup>2</sup> |               |                |      |

|                     |          | 0             | 1                     | 1    | fxp/2 <sup>3</sup> |               |                |      |

|                     |          | 1             | 0                     | 0    | fxp/2 <sup>4</sup> |               |                |      |

|                     | 1        | 0             | 0                     | 0    | fsuв/2             |               |                |      |

|                     |          | 0             | 0                     | 1    |                    |               |                |      |

|                     |          | 0             | 1                     | 0    |                    |               |                |      |

|                     |          | 0             | 1                     | 1    |                    |               |                |      |

| 1 0 0               |          |               |                       |      |                    |               |                |      |

|                     |          | Other tha     | n above               |      | Setting proh       | ibited        |                |      |

## Figure 6-6. Format of Processor Clock Control Register (PCC) (78K0/KC2, 78K0/KD2, 78K0/KE2, and 78K0/KF2)

Notes 1. Bit 5 is read-only.

XTSTART is used in combination with EXCLKS and OSCSELS (bits 5 and 4 of the clock operation mode select register (OSCCTL)). See (3) Setting of operation mode for subsystem clock pin.

## Cautions 1. Be sure to clear bits 3 and 7 to "0".

- 2. The peripheral hardware clock (fprs) is not divided when the division ratio of the PCC is set.

- Remark

fxp:

Main system clock oscillation frequency

fsub:

Subsystem clock oscillation frequency

The fastest instruction can be executed in 2 clocks of the CPU clock in the 78K0/Kx2 microcontrollers. Therefore, the relationship between the CPU clock (fcPu) and the minimum instruction execution time is as shown in Table 6-2.

## (3) Example of setting procedure when stopping the internal high-speed oscillation clock

- The internal high-speed oscillation clock can be stopped in the following two ways.

- Executing the STOP instruction to set the STOP mode

- Setting RSTOP to 1 and stopping the internal high-speed oscillation clock

## (a) To execute a STOP instruction

<1> Setting of peripheral hardware

Stop peripheral hardware that cannot be used in the STOP mode (for peripheral hardware that cannot be used in STOP mode, see **CHAPTER 22 STANDBY FUNCTION**).

<2> Setting the X1 clock oscillation stabilization time after standby release

When the CPU is operating on the X1 clock, set the value of the OSTS register before the STOP instruction is executed. To operate the CPU immediately after the STOP mode has been released, set MCM0 to 0, switch the CPU clock to the internal high-speed oscillation clock, and check that RSTS is 1.

<3> Executing the STOP instruction When the STOP instruction is executed, the system is placed in the STOP mode and internal high-speed oscillation clock is stopped.

## (b) To stop internal high-speed oscillation clock by setting RSTOP to 1

<1> Confirming the CPU clock status (PCC and MCM registers)

Confirm with CLS and MCS that the CPU is operating on a clock other than the internal high-speed oscillation clock.

When CLS = 0 and MCS = 0, the internal high-speed oscillation clock is supplied to the CPU, so change the CPU clock to a clock other than the internal high-speed oscillation clock.

## • 78K0/KB2

| MCS | CPU Clock Status                     |  |  |  |  |

|-----|--------------------------------------|--|--|--|--|

| 0   | nternal high-speed oscillation clock |  |  |  |  |

| 1   | High-speed system clock              |  |  |  |  |

## • 78K0/KC2, 78K0/KD2, 78K0/KE2, and 78K0/KF2

| CLS | MCS | CPU Clock Status                     |  |  |  |  |

|-----|-----|--------------------------------------|--|--|--|--|

| 0   | 0   | nternal high-speed oscillation clock |  |  |  |  |

| 0   | 1   | gh-speed system clock                |  |  |  |  |

| 1   | ×   | Subsystem clock                      |  |  |  |  |

<2> Stopping the internal high-speed oscillation clock (RCM register) When RSTOP is set to 1, internal high-speed oscillation clock is stopped.

Caution Be sure to confirm that MCS = 1 or CLS = 1 when setting RSTOP to 1. In addition, stop peripheral hardware that is operating on the internal high-speed oscillation clock.

## 6.6.3 Example of controlling subsystem clock

- The following two types of subsystem clocks<sup>Note</sup> are available.

- XT1 clock: Crystal/ceramic resonator is connected across the XT1 and XT2 pins.

- External subsystem clock: External clock is input to the EXCLKS pin.

When the subsystem clock is not used, the XT1/P123 and XT2/EXCLKS/P124 pins can be used as I/O port pins.

Note The 78K0/KB2 is not provided with a subsystem clock.

## Cautions 1. The XT1/P123 and XT2/EXCLKS/P124 pins are in the I/O port mode after a reset release.

2. Do not start the peripheral hardware operation with the external clock from peripheral hardware pins when the internal high-speed oscillation clock and high-speed system clock are stopped while the CPU operates with the subsystem clock, or when in the STOP mode.

The following describes examples of setting procedures for the following cases.

- (1) When oscillating XT1 clock

- (2) When using external subsystem clock

- (3) When using subsystem clock as CPU clock

- (4) When stopping subsystem clock

## (1) Example of setting procedure when oscillating the XT1 clock

<1> Setting XT1 and XT2 pins and selecting operation mode (PCC and OSCCTL registers) When XTSTART, EXCLKS, and OSCSELS are set as any of the following, the mode is switched from port mode to XT1 oscillation mode.

| XTSTART | EXCLKS | OSCSELS | Operation Mode of<br>Subsystem Clock Pin | P123/XT1 Pin                         | P124/XT2/<br>EXCLKS Pin |  |

|---------|--------|---------|------------------------------------------|--------------------------------------|-------------------------|--|

| 0       | 0      | 1       | XT1 oscillation mode                     | Crystal/ceramic resonator connection |                         |  |

| 1       | ×      | ×       |                                          |                                      |                         |  |

**Remark** ×: don't care

<2> Waiting for the stabilization of the subsystem clock oscillation Wait for the oscillation stabilization time of the subsystem clock by software, using a timer function.

# Caution Do not change the value of XTSTART, EXCLKS, and OSCSELS while the subsystem clock is operating.

## (2) Example of setting procedure when using the external subsystem clock

<1> Setting XT1 and XT2 pins, selecting XT1 clock/external clock and controlling oscillation (PCC and OSCCTL registers)

When XTSTART is cleared to 0 and EXCLKS and OSCSELS are set to 1, the mode is switched from port mode to external clock input mode. In this case, input the external clock to the EXCLKS/XT2/P124 pins.

| XTSTART | EXCLKS | OSCSELS | Operation Mode of<br>Subsystem Clock Pin | P123/XT1 Pin | P124/XT2/<br>EXCLKS Pin |

|---------|--------|---------|------------------------------------------|--------------|-------------------------|

| 0       | 1      | 1       | External clock input mode                | I/O port     | External clock input    |

# Caution Do not change the value of XTSTART, EXCLKS, and OSCSELS while the subsystem clock is operating.

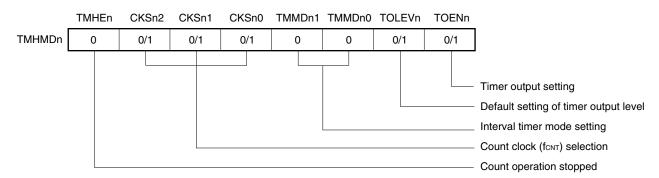

## 9.4 Operation of 8-Bit Timers H0 and H1

## 9.4.1 Operation as interval timer/square-wave output

When the 8-bit timer counter Hn and compare register 0n (CMP0n) match, an interrupt request signal (INTTMHn) is generated and the 8-bit timer counter Hn is cleared to 00H.

Compare register 1n (CMP1n) is not used in interval timer mode. Since a match of the 8-bit timer counter Hn and the CMP1n register is not detected even if the CMP1n register is set, timer output is not affected.

By setting bit 0 (TOENn) of timer H mode register n (TMHMDn) to 1, a square wave of any frequency (duty = 50%) is output from TOHn.

Setting

<1> Set each register.

## Figure 9-9. Register Setting During Interval Timer/Square-Wave Output Operation

## (i) Setting timer H mode register n (TMHMDn)

## (ii) CMP0n register setting

The interval time is as follows if N is set as a comparison value.

- Interval time = (N +1)/fCNT

- <2> Count operation starts when TMHEn = 1.

- <3> When the values of the 8-bit timer counter Hn and the CMP0n register match, the INTTMHn signal is generated and the 8-bit timer counter Hn is cleared to 00H.

- <4> Subsequently, the INTTMHn signal is generated at the same interval. To stop the count operation, clear TMHEn to 0.

Remarks 1. For the setting of the output pin, see 9.3 (3) Port mode register 1 (PM1).

2. For how to enable the INTTMHn signal interrupt, see CHAPTER 20 INTERRUPT FUNCTIONS.

3. n = 0, 1

## Setting

<1> Set each register.

## Figure 9-14. Register Setting in Carrier Generator Mode

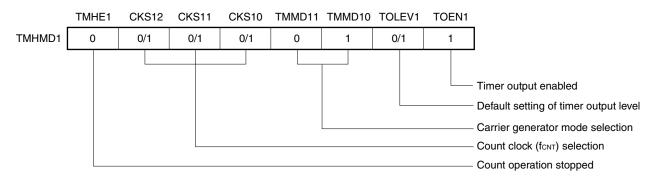

#### (i) Setting 8-bit timer H mode register 1 (TMHMD1)

#### (ii) CMP01 register setting

· Compare value

#### (iii) CMP11 register setting

• Compare value

#### (iv) TMCYC1 register setting

- RMC1 = 1 ... Remote control output enable bit

- NRZB1 = 0/1 ... carrier output enable bit

## (v) TCL51 and TMC51 register setting

- See 8.3 Registers Controlling 8-Bit Timer/Event Counters 50 and 51.

- <2> When TMHE1 = 1, the 8-bit timer H1 starts counting.

- <3> When TCE51 of the 8-bit timer mode control register 51 (TMC51) is set to 1, the 8-bit timer/event counter 51 starts counting.

- <4> After the count operation is enabled, the first compare register to be compared is the CMP01 register. When the count value of the 8-bit timer counter H1 and the CMP01 register value match, the INTTMH1 signal is generated, the 8-bit timer counter H1 is cleared. At the same time, the compare register to be compared with the 8-bit timer counter H1 is switched from the CMP01 register to the CMP11 register.

- <5> When the count value of the 8-bit timer counter H1 and the CMP11 register value match, the INTTMH1 signal is generated, the 8-bit timer counter H1 is cleared. At the same time, the compare register to be compared with the 8-bit timer counter H1 is switched from the CMP11 register to the CMP01 register.

- <6> By performing procedures <4> and <5> repeatedly, a carrier clock is generated.

- <7> The INTTM51 signal is synchronized with count clock of the 8-bit timer H1 and output as the INTTM5H1 signal. The INTTM5H1 signal becomes the data transfer signal for the NRZB1 bit, and the NRZB1 bit value is transferred to the NRZ1 bit.

- <8> Write the next value to the NRZB1 bit in the interrupt servicing program that has been started by the INTTM5H1 interrupt or after timing has been checked by polling the interrupt request flag. Write data to count the next time to the CR51 register.

- <9> When the NRZ1 bit is high level, a carrier clock is output by TOH1 output.

## **10.4 Watch Timer Operations**

## 10.4.1 Watch timer operation

The watch timer generates an interrupt request signal (INTWT) at a specific time interval by using the peripheral hardware clock or subsystem clock.

When bit 0 (WTM0) and bit 1 (WTM1) of the watch timer operation mode register (WTM) are set to 1, the count operation starts. When these bits are cleared to 0, the 5-bit counter is cleared and the count operation stops.

When the interval timer is simultaneously operated, zero-second start can be achieved only for the watch timer by clearing WTM1 to 0. In this case, however, the 11-bit prescaler is not cleared. Therefore, an error up to  $2^9 \times 1/f_W$  seconds occurs in the first overflow (INTWT) after zero-second start.

The interrupt request is generated at the following time intervals.

| WTM3 | WTM2 | Interrupt Time<br>Selection | When Operated at<br>fsub = 32.768 kHz | •          | When Operated at<br>fprs = 5 MHz | When Operated at<br>fPRS = 10 MHz | When Operated at<br>fPRS = 20 MHz |

|------|------|-----------------------------|---------------------------------------|------------|----------------------------------|-----------------------------------|-----------------------------------|

|      |      |                             | (WTM7 = 1)                            | (WTM7 = 0) | (WTM7 = 0)                       | (WTM7 = 0)                        | (WTM7 = 0)                        |

| 0    | 0    | 2 <sup>14</sup> /fw         | 0.5 s                                 | 1.05 s     | 0.419 s                          | 0.210 s                           | 0.105 s                           |

| 0    | 1    | 2 <sup>13</sup> /fw         | 0.25 s                                | 0.52 s     | 0.210 s                          | 0.105 s                           | 52.5 ms                           |

| 1    | 0    | 2⁵/fw                       | 977 <i>μ</i> s                        | 2.05 ms    | 819 <i>µ</i> s                   | 410 <i>µ</i> s                    | 205 <i>μ</i> s                    |

| 1    | 1    | 2 <sup>4</sup> /fw          | 488 <i>µ</i> s                        | 1.02 ms    | 410 <i>μ</i> s                   | 205 <i>μ</i> s                    | 102 <i>μ</i> s                    |

Table 10-4. Watch Timer Interrupt Time

**Remarks 1.** fw: Watch timer clock frequency (fprs/2<sup>7</sup> or fsub)

2. fprs: Peripheral hardware clock frequency

3. fsub: Subsystem clock frequency

#### 10.4.2 Interval timer operation

The watch timer operates as interval timer which generates interrupt request signals (INTWTI) repeatedly at an interval of the preset count value.

The interval time can be selected with bits 4 to 6 (WTM4 to WTM6) of the watch timer operation mode register (WTM).

When bit 0 (WTM0) of the WTM is set to 1, the count operation starts. When this bit is set to 0, the count operation stops.

| WTM6 | WTM5 | WTM4 | Interval Time       | When Operated<br>at f <sub>SUB</sub> = 32.768<br>kHz (WTM7 = 1) | When Operated<br>at fPRS = 2 MHz<br>(WTM7 = 0) | •              | When Operated<br>at fPRS = 10 MHz<br>(WTM7 = 0) | When Operated<br>at fPRS = 20 MHz<br>(WTM7 = 0) |

|------|------|------|---------------------|-----------------------------------------------------------------|------------------------------------------------|----------------|-------------------------------------------------|-------------------------------------------------|

| 0    | 0    | 0    | 2 <sup>4</sup> /fw  | 488 <i>μ</i> s                                                  | 1.02 ms                                        | 410 <i>μ</i> s | 205 <i>µ</i> s                                  | 102 <i>μ</i> s                                  |

| 0    | 0    | 1    | 2⁵/fw               | 977 <i>μ</i> s                                                  | 2.05 ms                                        | 820 <i>µ</i> s | 410 <i>μ</i> s                                  | 205 <i>µ</i> s                                  |

| 0    | 1    | 0    | 2 <sup>6</sup> /fw  | 1.95 ms                                                         | 4.10 ms                                        | 1.64 ms        | 820 <i>µ</i> s                                  | 410 <i>µ</i> s                                  |

| 0    | 1    | 1    | 2 <sup>7</sup> /fw  | 3.91 ms                                                         | 8.20 ms                                        | 3.28 ms        | 1.64 ms                                         | 820 <i>µ</i> s                                  |

| 1    | 0    | 0    | 2 <sup>8</sup> /fw  | 7.81 ms                                                         | 16.4 ms                                        | 6.55 ms        | 3.28 ms                                         | 1.64 ms                                         |

| 1    | 0    | 1    | 2 <sup>9</sup> /fw  | 15.6 ms                                                         | 32.8 ms                                        | 13.1 ms        | 6.55 ms                                         | 3.28 ms                                         |

| 1    | 1    | 0    | 2 <sup>10</sup> /fw | 31.3 ms                                                         | 65.5 ms                                        | 26.2 ms        | 13.1 ms                                         | 6.55 ms                                         |

| 1    | 1    | 1    | 2 <sup>11</sup> /fw | 62.5 ms                                                         | 131.1 ms                                       | 52.4 ms        | 26.2 ms                                         | 13.1 ms                                         |

Table 10-5. Interval Timer Interval Time

**Remarks 1.** fw: Watch timer clock frequency (fprs/2<sup>7</sup> or fsub)

2. fprs: Peripheral hardware clock frequency

**3.** fsub: Subsystem clock frequency

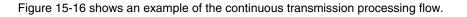

Remark

TXB6:

Transmit buffer register 6

ASIF6:

Asynchronous serial interface transmission status register 6

TXBF6:

Bit 1 of ASIF6 (transmit buffer data flag)

TXSF6:

Bit 0 of ASIF6 (transmit shift register data flag)

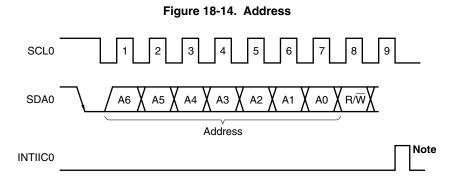

#### 18.5.2 Addresses

The address is defined by the 7 bits of data that follow the start condition.

An address is a 7-bit data segment that is output in order to select one of the slave devices that are connected to the master device via the bus lines. Therefore, each slave device connected via the bus lines must have a unique address.

The slave devices include hardware that detects the start condition and checks whether or not the 7-bit address data matches the data values stored in slave address register 0 (SVA0). If the address data matches the SVA0 register values, the slave device is selected and communicates with the master device until the master device generates a start condition or stop condition.

Note INTIIC0 is not issued if data other than a local address or extension code is received during slave device operation.

The slave address and the eighth bit, which specifies the transfer direction as described in **18.5.3** Transfer direction specification below, are together written to IIC shift register 0 (IIC0) and are then output. Received addresses are written to IIC0.

The slave address is assigned to the higher 7 bits of IIC0 register.

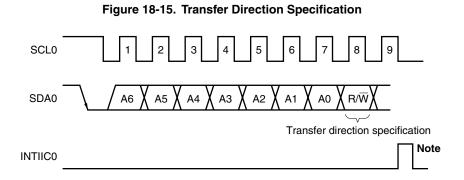

#### 18.5.3 Transfer direction specification

In addition to the 7-bit address data, the master device sends 1 bit that specifies the transfer direction.

When this transfer direction specification bit has a value of "0", it indicates that the master device is transmitting data to a slave device. When the transfer direction specification bit has a value of "1", it indicates that the master device is receiving data from a slave device.

Note INTIIC0 is not issued if data other than a local address or extension code is received during slave device operation.

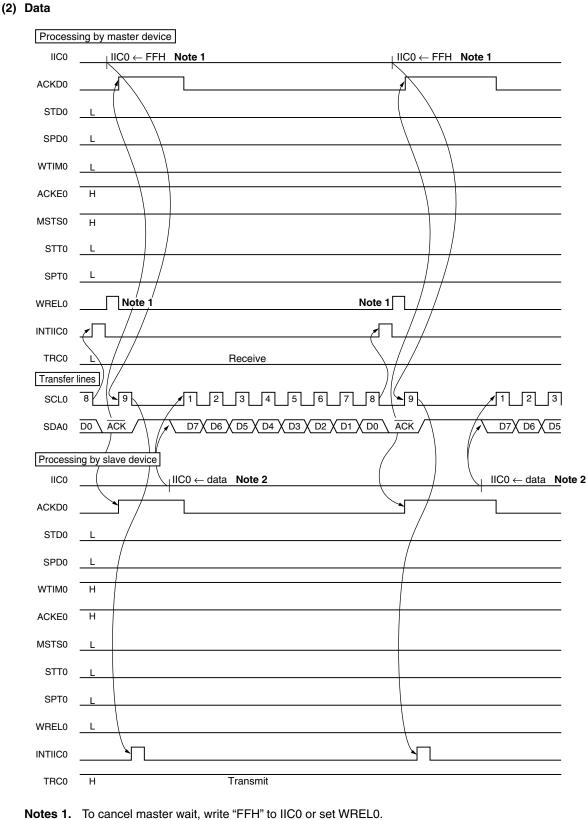

## **18.6 Timing Charts**

When using the l<sup>2</sup>C bus mode, the master device outputs an address via the serial bus to select one of several slave devices as its communication partner.

After outputting the slave address, the master device transmits the TRC0 bit (bit 3 of IIC status register 0 (IICS0)), which specifies the data transfer direction, and then starts serial communication with the slave device.

Figures 18-27 and 18-28 show timing charts of the data communication.

IIC shift register 0 (IIC0)'s shift operation is synchronized with the falling edge of the serial clock (SCL0). The transmit data is transferred to the SO0 latch and is output (MSB first) via the SDA0 pin.

Data input via the SDA0 pin is captured into IIC0 at the rising edge of SCL0.

## Figure 18-28. Example of Slave to Master Communication (When 8-Clock Wait Is Selected for Master, 9-Clock Wait Is Selected for Slave) (2/3)

2. Write data to IIC0, not setting WREL0, in order to cancel a wait state during slave transmission.

#### 20.4.3 Multiple interrupt servicing

Multiple interrupt servicing occurs when another interrupt request is acknowledged during execution of an interrupt.

Multiple interrupt servicing does not occur unless the interrupt request acknowledgment enabled state is selected (IE = 1). When an interrupt request is acknowledged, interrupt request acknowledgment becomes disabled (IE = 0). Therefore, to enable multiple interrupt servicing, it is necessary to set (1) the IE flag with the EI instruction during interrupt servicing to enable interrupt acknowledgment.

Moreover, even if interrupts are enabled, multiple interrupt servicing may not be enabled, this being subject to interrupt priority control. Two types of priority control are available: default priority control and programmable priority control. Programmable priority control is used for multiple interrupt servicing.

In the interrupt enabled state, if an interrupt request with a priority equal to or higher than that of the interrupt currently being serviced is generated, it is acknowledged for multiple interrupt servicing. If an interrupt with a priority lower than that of the interrupt currently being serviced is generated during interrupt servicing, it is not acknowledged for multiple interrupt servicing. Interrupt requests that are not enabled because interrupts are in the interrupt disabled state or because they have a lower priority are held pending. When servicing of the current interrupt ends, the pending interrupt request is acknowledged following execution of at least one main processing instruction execution.

Table 20-5 shows relationship between interrupt requests enabled for multiple interrupt servicing and Figure 20-22 shows multiple interrupt servicing examples.

# Table 20-5. Relationship Between Interrupt Requests Enabled for Multiple Interrupt Servicing During Interrupt Servicing

| Multiple Interru         |         | Software |        |        |           |         |

|--------------------------|---------|----------|--------|--------|-----------|---------|

|                          | PR = 0  |          | PR = 1 |        | Interrupt |         |

| Interrupt Being Serviced |         | IE = 1   | IE = 0 | IE = 1 | IE = 0    | Request |

| Maskable interrupt       | ISP = 0 | 0        | ×      | ×      | ×         | 0       |

|                          | ISP = 1 | 0        | ×      | 0      | ×         | 0       |

| Software interrupt       |         | 0        | ×      | 0      | ×         | 0       |

Remarks 1. O: Multiple interrupt servicing enabled

- 2. ×: Multiple interrupt servicing disabled

- 3. ISP and IE are flags contained in the PSW.

- ISP = 0: An interrupt with higher priority is being serviced.

- ISP = 1: No interrupt request has been acknowledged, or an interrupt with a lower priority is being serviced.

- IE = 0: Interrupt request acknowledgment is disabled.

- IE = 1: Interrupt request acknowledgment is enabled.

- 4. PR is a flag contained in PR0L, PR0H, PR1L, and PR1H.

- PR = 0: Higher priority level

- PR = 1: Lower priority level

## 23.1 Register for Confirming Reset Source

Many internal reset generation sources exist in the 78K0/Kx2 microcontrollers. The reset control flag register (RESF) is used to store which source has generated the reset request.

RESF can be read by an 8-bit memory manipulation instruction.

RESET input, reset by power-on-clear (POC) circuit, and reading RESF set RESF to 00H.

#### Figure 23-5. Format of Reset Control Flag Register (RESF)

| Address: FFA | ACH After | reset: 00H <sup>Note</sup> | R |       |   |   |   |       |

|--------------|-----------|----------------------------|---|-------|---|---|---|-------|

| Symbol       | 7         | 6                          | 5 | 4     | 3 | 2 | 1 | 0     |

| RESF         | 0         | 0                          | 0 | WDTRF | 0 | 0 | 0 | LVIRF |

| ſ | WDTRF | Internal reset request by watchdog timer (WDT)               |

|---|-------|--------------------------------------------------------------|

| ſ | 0     | Internal reset request is not generated, or RESF is cleared. |

|   | 1     | Internal reset request is generated.                         |

| LVIRF | Internal reset request by low-voltage detector (LVI)         |  |  |

|-------|--------------------------------------------------------------|--|--|

| 0     | Internal reset request is not generated, or RESF is cleared. |  |  |

| 1     | Internal reset request is generated.                         |  |  |

Note The value after reset varies depending on the reset source.

#### Caution Do not read data by a 1-bit memory manipulation instruction.

The status of RESF when a reset request is generated is shown in Table 23-3.

#### Table 23-3. RESF Status When Reset Request Is Generated

| Reset Source | RESET Input | Reset by POC | Reset by WDT | Reset by LVI |

|--------------|-------------|--------------|--------------|--------------|

| Flag         |             |              |              |              |

| WDTRF        | Cleared (0) | Cleared (0)  | Set (1)      | Held         |

| LVIRF        |             |              | Held         | Set (1)      |

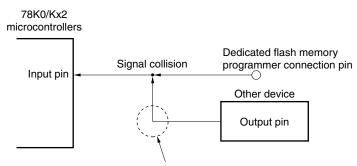

## (1) Signal collision

If the dedicated flash memory programmer (output) is connected to a pin (input) of a serial interface connected to another device (output), signal collision takes place. To avoid this collision, either isolate the connection with the other device, or make the other device go into an output high-impedance state.

Figure 27-7. Signal Collision (Input Pin of Serial Interface)

In the flash memory programming mode, the signal output by the device collides with the signal sent from the dedicated flash programmer. Therefore, isolate the signal of the other device.

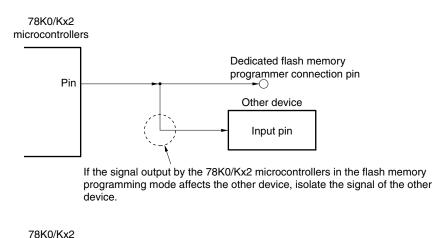

## (2) Malfunction of other device

If the dedicated flash memory programmer (output or input) is connected to a pin (input or output) of a serial interface connected to another device (input), a signal may be output to the other device, causing the device to malfunction. To avoid this malfunction, isolate the connection with the other device.

If the signal output by the dedicated flash memory programmer in the flash memory programming mode affects the other device, isolate the signal of the other device.

## CHAPTER 31 ELECTRICAL SPECIFICATIONS ((A) GRADE PRODUCTS)

| Target Products | Conventional-specification Products                                                         | Expanded-specification Products                                                                    |

|-----------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| 78K0/KB2        | μθD78F0500(A), 78F0501(A), 78F0502(A),<br>78F0503(A)                                        | μΦD78F0500A(A), 78F0501A(A), 78F0502A(A),<br>78F0503A(A)                                           |

| 78K0/KC2        | μPD78F0511(A), 78F0512(A), 78F0513(A),<br>78F0514(A), 78F0515(A)                            | μΦD78F0511A(A), 78F0512A(A), 78F0513A(A),<br>78F0514A(A), 78F0515A(A)                              |

| 78K0/KD2        | μPD78F0521(A), 78F0522(A), 78F0523(A),<br>78F0524(A), 78F0525(A), 78F0526(A),<br>78F0527(A) | μPD78F0521A(A), 78F0522A(A), 78F0523A(A),<br>78F0524A(A), 78F0525A(A), 78F0526A(A),<br>78F0527A(A) |

| 78K0/KE2        | μPD78F0531(A), 78F0532(A), 78F0533(A),<br>78F0534(A), 78F0535(A), 78F0536(A),<br>78F0537(A) | μPD78F0531A(A), 78F0532A(A), 78F0533A(A),<br>78F0534A(A), 78F0535A(A), 78F0536A(A),<br>78F0537A(A) |

| 78K0/KF2        | μιΡD78F0544(A), 78F0545(A), 78F0546(A),<br>78F0547(A)                                       | μΦD78F0544A(A), 78F0545A(A), 78F0546A(A),<br>78F0547A(A)                                           |

The following items are described separately for conventional-specification products ( $\mu$ PD78F05xx(A)) and expanded-specification products ( $\mu$ PD78F05xxA(A)).

- X1 clock oscillation frequency (X1 oscillator characteristics)

- Instruction cycle, peripheral hardware clock frequency, external main system clock frequency, external main system clock input high-level width, and external main system clock input low-level width (**(1) Basic operation** in **AC characteristics**)

- A/D conversion time (A/D Converter Characteristics)

- Number of rewrites per chip (Flash Memory Programming Characteristics)

## Caution The pins mounted depend on the product as follows.

## (1) Port functions

| Port    | 78K0/KB2     | 78K0/KC2     |            |            | 78K0/KD2   | 78K0/KE2   | 78K0/KF2     |

|---------|--------------|--------------|------------|------------|------------|------------|--------------|

|         | 30/36 Pins   | 38 Pins      | 44 Pins    | 48 Pins    | 52 Pins    | 64 Pins    | 80 Pins      |

| Port 0  | P00, P01     |              |            |            | P00 to P03 | P00 to P06 |              |

| Port 1  | P10 to P17   |              |            |            |            |            |              |

| Port 2  | P20 to P23   | P20 to P25   | P20 to P27 |            |            |            |              |

| Port 3  | P30 to P33   |              |            |            |            |            |              |

| Port 4  | -            | _            | P40, P41   |            |            | P40 to P43 | P40 to P47   |

| Port 5  |              |              | -          |            |            | P50 to P53 | P50 to P57   |

| Port 6  | P60, P61     | P60 to P63   |            |            |            |            | P60 to P67   |

| Port 7  | -            | P70, P71     | P70 to P73 | P70 to P75 | P70 to P77 |            |              |

| Port 12 | P120 to P122 | P120 to P124 |            |            |            |            |              |

| Port 13 | -            |              |            | P130       |            |            |              |

| Port 14 | _            |              |            | P140       |            | P140, P141 | P140 to P145 |

(The remaining table is on the next page.)

|             | Ι                                                                                                                                                                                                                        | (2/                                                              |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|

| Edition     | Description                                                                                                                                                                                                              | Chapter                                                          |  |

| 3nd Edition | Modification of Note 1 in and addition of Note 4 to Figure 8-5 Format of Timer<br>Clock Selection Register 50 (TCL50) and Figure 8-6 Format of Timer Clock<br>Selection Register 51 (TCL51)                              | CHAPTER 8 8-BIT<br>TIMER/EVENT<br>COUNTERS 50 AND 5 <sup>1</sup> |  |

|             | Modification of Note 1 in and addition of Note 3 to Figure 9-5 Format of 8-Bit Timer<br>H Mode Register 0 (TMHMD0) and Figure 9-6 Format of 8-Bit Timer H Mode<br>Register 1 (TMHMD1)                                    | CHAPTER 9 8-BIT<br>TIMERS H0 AND H1                              |  |

|             | Addition of Note to Figure 10-2 Format of Watch Timer Operation Mode Register (WTM)                                                                                                                                      | CHAPTER 10 WATCH<br>TIMER                                        |  |

|             | Modification of Note and description in 11.1 Functions of Watchdog Timer                                                                                                                                                 | CHAPTER 11                                                       |  |

|             | Modification of Note and description in 11.4.1 Controlling operation of watchdog timer                                                                                                                                   | WATCHDOG TIMER                                                   |  |

|             | Modification of <b>Remark</b> in 11.4.3 Setting window open period of watchdog timer                                                                                                                                     |                                                                  |  |

|             | Modification of Note 1 in Figure 12-3 Format of Clock Output Selection Register<br>(CKS) (78K0/KD2, 48-pin Products of 78K0/KC2) and Figure 12-4 Format of<br>Clock Output Selection Register (CKS) (78K0/KE2, 78K0/KF2) | CHAPTER 12 CLOCK<br>OUTPUT/BUZZER<br>OUTPUT<br>CONTROLLER        |  |

|             | Addition of Table 13-2 A/D Conversion Time Selection (Conventional-<br>specification Products                                                                                                                            | CHAPTER 13 A/D<br>CONVERTER                                      |  |

|             | (μPD78F05xx and 78F05xxD))                                                                                                                                                                                               |                                                                  |  |

|             | Modification of Table 13-3 A/D Conversion Time Selection (Expanded-<br>specification Products                                                                                                                            |                                                                  |  |

|             | (μPD78F05xxA and 78F05xxDA))                                                                                                                                                                                             |                                                                  |  |

|             | Modification of Figure 13-6 Format of 10-Bit A/D Conversion Result Register (ADCR)                                                                                                                                       |                                                                  |  |

|             | Modification of Note 1 in Figure 14-4 Format of Baud Rate Generator Control Register 0 (BRGC0)                                                                                                                           | CHAPTER 14 SERIAL<br>INTERFACE UART0                             |  |

|             | Modification of Note 1 in Table 14-4 Set Value of TPS01 and TPS00                                                                                                                                                        |                                                                  |  |

|             | Modification of Table 14-5 Set Data of Baud Rate Generator                                                                                                                                                               |                                                                  |  |

|             | Modification of Note 1 in Figure 15-5 Format of Asynchronous Serial Interface<br>Operation Mode Register 6 (ASIM6) (1/2)                                                                                                 | CHAPTER 15 SERIAL<br>INTERFACE UART6                             |  |

|             | Modification of Note 1 in and addition of Note 3 to Figure 15-8 Format of Clock<br>Selection Register 6 (CKSR6)                                                                                                          |                                                                  |  |

|             | Addition of <b>Caution 8</b> to <b>Figure 15-10 Format of Asynchronous Serial Interface</b><br><b>Control Register 6 (ASICL6) (2/2)</b>                                                                                  |                                                                  |  |

|             | Modification of Note 1 in 15.4.1 (1) Register used                                                                                                                                                                       |                                                                  |  |

|             | Modification of Note 1 in and addition of Note 3 to Table 15-4 Set Value of TPS63 to TPS60                                                                                                                               |                                                                  |  |

|             | Modification of Notes 1 and 2 in Figure 16-5 Format of Serial Clock Selection<br>Register 10 (CSIC10) and Figure 16-6 Format of Serial Clock Selection Register<br>11 (CSIC11)                                           | CHAPTER 16 SERIAL<br>INTERFACES CSI10<br>AND CSI11               |  |

|             | Addition of <b>Note 2</b> in and modification of <b>Table 16-2 Relationship Between</b><br><b>Register Settings and Pins</b>                                                                                             |                                                                  |  |

|             | Modification of 16.4.2 (5) SO1n output                                                                                                                                                                                   |                                                                  |  |

## 78K0/Kx2 User's Manual: Hardware

| Publication Date: | Rev.0.01<br>Rev.4.01 | January 10, 2008<br>July 15, 2010 |

|-------------------|----------------------|-----------------------------------|

| Published by:     | Renesas E            | lectronics Corporation            |