# E·X Renesas Electronics America Inc - <u>UPD78F0536AGC-GAL-AX Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                   |

|----------------------------|---------------------------------------------------------------------------------------|

| Core Processor             | 78K/0                                                                                 |

| Core Size                  | 8-Bit                                                                                 |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                                    |

| Number of I/O              | 55                                                                                    |

| Program Memory Size        | 96KB (96K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                |                                                                                       |

| RAM Size                   | 5K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 8x10b                                                                             |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 64-LQFP                                                                               |

| Supplier Device Package    |                                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0536agc-gal-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## (1) Conventional-specification products ( $\mu$ PD78F05xx and 78F05xxD) (2/2)

## <3> When high-speed system clock is used (static model of C compiler/assembler)

| Library Name                         | Interrupt Response Time (µs (Max.))    |                                          |                                        |                                          |  |

|--------------------------------------|----------------------------------------|------------------------------------------|----------------------------------------|------------------------------------------|--|

|                                      | RSTOP = 0                              | ), RSTS = 1                              | RSTC                                   | )P = 1                                   |  |

|                                      | Entry RAM location<br>is outside short | Entry RAM location<br>is in short direct | Entry RAM location<br>is outside short | Entry RAM location<br>is in short direct |  |

|                                      | direct addressing                      | addressing range                         | direct addressing                      | addressing range                         |  |

|                                      | range                                  |                                          | range                                  |                                          |  |

| Block blank check library            | 136/fcpu + 507                         | 136/fcpu + 407                           | 136/fcpu + 1650                        | 136/fcpu + 714                           |  |

| Block erase library                  | 136/fcpu + 559                         | 136/fcpu + 460                           | 136/fcpu + 1702                        | 136/fcpu + 767                           |  |

| Word write library                   | 272/fcpu + 1589                        | 272/fcpu + 1298                          | 272/fcpu + 2732                        | 272/fcpu + 1605                          |  |

| Block verify library                 | 136/fcpu + 518                         | 136/fcpu + 418                           | 136/fcpu + 1661                        | 136/fcpu + 725                           |  |

| Set information library              | 72/fcpu + 370                          | 72/fcpu + 165                            | 72/fcpu + 1513                         | 72/fcpu + 472                            |  |

| EEPROM write library <sup>Note</sup> | 19/fcpu + 1759                         | 19/fcpu + 1468                           | 19/fcpu + 1759                         | 19/fcpu + 1468                           |  |

|                                      | 268/fcpu + 834                         | 268/fcpu + 512                           | 268/fcpu + 2061                        | 268/fcpu + 873                           |  |

**Note** The longer value of the EEPROM write library interrupt response time becomes the Max. value, depending on the value of fcPu.

Remarks 1. fcPu: CPU operation clock frequency

- 2. RSTOP: Bit 0 of the internal oscillation mode register (RCM)

- 3. RSTS: Bit 7 of the internal oscillation mode register (RCM)

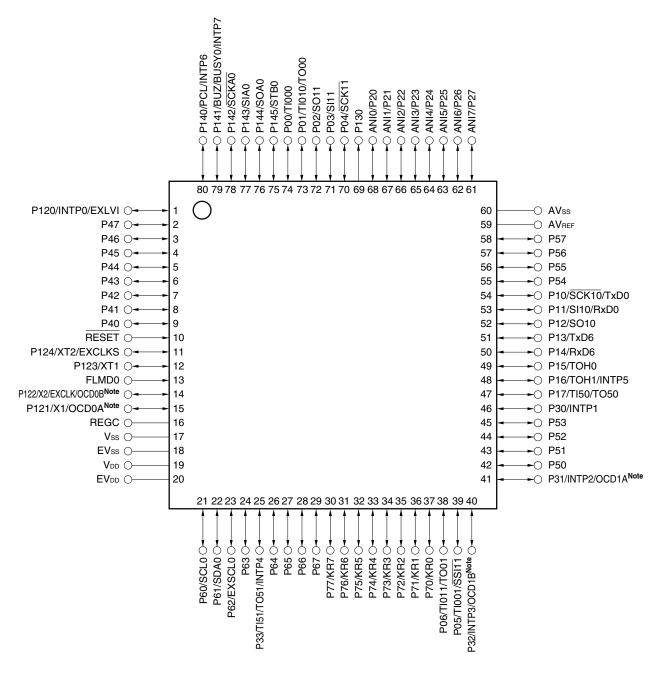

## 1.5.5 78K0/KF2

- 80-pin plastic LQFP (14  $\times$  14)

- 80-pin plastic LQFP (fine pitch) (12  $\times$  12)

Note Products with on-chip debug function only

Cautions 1. Make AVss and EVss the same potential as Vss.

- 2. Make EVDD the same potential as VDD.

- 3. Connect the REGC pin to Vss via a capacitor (0.47 to 1  $\mu$ F).

- 4. ANI0/P20 to ANI7/P27 are set in the analog input mode after release of reset.

Remark For pin identification, see 1.6 Pin Identification.

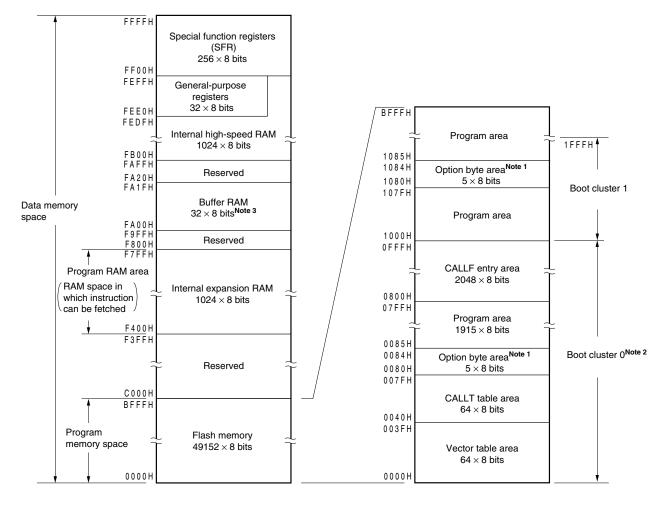

## Figure 3-6. Memory Map (μPD78F0514, 78F0514A, 78F0524, 78F0524A, 78F0534, 78F0534A, 78F0544, and 78F0544A)

Notes 1. When boot swap is not used: Set the option bytes to 0080H to 0084H.

When boot swap is used: Set the option bytes to 0080H to 0084H and 1080H to 1084H.

- 2. Writing boot cluster 0 can be prohibited depending on the setting of security (see 27.8 Security Settings).

- 3. The buffer RAM is incorporated only in the  $\mu$ PD78F0544 and 78F0544A (78K0/KF2). The area from FA00H to FA1FH cannot be used with the  $\mu$ PD78F0514, 78F0514A, 78F0524A, 78F0524A, 78F0534A, and 78F0534A.

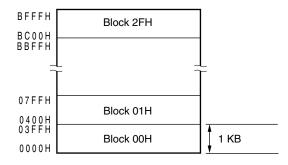

- **Remark** The flash memory is divided into blocks (one block = 1 KB). For the address values and block numbers, see **Table 3-3 Correspondence Between Address Values and Block Numbers in Flash Memory**.

## 3.2 Processor Registers

The 78K0/Kx2 microcontrollers incorporate the following processor registers.

## 3.2.1 Control registers

The control registers control the program sequence, statuses and stack memory. The control registers consist of a program counter (PC), a program status word (PSW) and a stack pointer (SP).

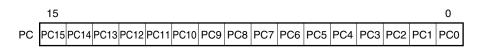

## (1) Program counter (PC)

The program counter is a 16-bit register that holds the address information of the next program to be executed. In normal operation, PC is automatically incremented according to the number of bytes of the instruction to be fetched. When a branch instruction is executed, immediate data and register contents are set.

Reset signal generation sets the reset vector table values at addresses 0000H and 0001H to the program counter.

## Figure 3-20. Format of Program Counter

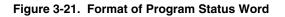

## (2) Program status word (PSW)

The program status word is an 8-bit register consisting of various flags set/reset by instruction execution.

Program status word contents are stored in the stack area upon vectored interrupt request acknowledgement or PUSH PSW instruction execution and are restored upon execution of the RETB, RETI and POP PSW instructions. Reset signal generation sets PSW to 02H.

## (a) Interrupt enable flag (IE)

This flag controls the interrupt request acknowledge operations of the CPU.

When 0, the IE flag is set to the interrupt disabled (DI) state, and all maskable interrupt requests are disabled.

When 1, the IE flag is set to the interrupt enabled (EI) state and interrupt request acknowledgment is controlled with an in-service priority flag (ISP), an interrupt mask flag for various interrupt sources, and a priority specification flag.

The IE flag is reset (0) upon DI instruction execution or interrupt acknowledgment and is set (1) upon EI instruction execution.

## (b) Zero flag (Z)

When the operation result is zero, this flag is set (1). It is reset (0) in all other cases.

## (c) Register bank select flags (RBS0 and RBS1)

These are 2-bit flags to select one of the four register banks. In these flags, the 2-bit information that indicates the register bank selected by SEL RBn instruction execution is stored.

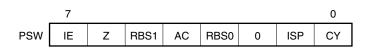

## 3.3.3 Table indirect addressing

## [Function]

Table contents (branch destination address) of the particular location to be addressed by bits 1 to 5 of the immediate data of an operation code are transferred to the program counter (PC) and branched.

This function is carried out when the CALLT [addr5] instruction is executed.

This instruction references the address that is indicated by addr5 and is stored in the memory table from 0040H to 007FH, and allows branching to the entire memory space.

## [Illustration]

Г

• Software example (to store a value to be referenced in register A)

| RAMD<br>R_BNKA:<br>R_BNKN:<br>R_BNKRN: |                                                                                     | SADDR<br>2<br>1<br>1                                                                                                    | ; Secures RAM for specifying an address at the reference destination.<br>; Secures RAM for specifying a memory bank number at the reference destination.<br>; Secures RAM for saving a memory bank number at the reference source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ETRC<br>ENTRY:                         | CSEG                                                                                | UNIT                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                        | MOV<br>MOVW<br>CALL                                                                 | R_BNKN,#BANKNUM DATA1<br>R_BNKA,#DATA1<br>!BNKRD<br>:<br>:                                                              | ; Stores the memory bank number at the reference destination.<br>; Stores the address at the reference destination.<br>; Calls a subroutine for referencing between memory banks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BNKC                                   | CSEG                                                                                | AT 7000H                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| BNKRD:                                 | PUSH<br>MOV<br>XCH<br>MOV<br>XCHW<br>MOV<br>XCHW<br>MOV<br>XCH<br>MOV<br>POP<br>RET | HL<br>A,R_BNKN<br>A,BANK<br>R_BNKRN,A<br>AX,HL<br>AX,R_BNKA<br>AX,HL<br>A,HL]<br>A,R_BNKRN<br>BANK,A<br>A,R_BNKRN<br>HL | <ul> <li>; Subroutine for referencing between memory banks.</li> <li>; Saves the contents of the HL register.</li> <li>; Acquires the memory bank number at the reference destination.</li> <li>; Swaps the memory bank number at the reference source for that at the reference (destination)</li> <li>; Saves the memory bank number at the reference source.</li> <li>; Saves the contents of the X register.</li> <li>; Acquires the address at the reference destination.</li> <li>; Specifies the address at the reference destination.</li> <li>; Reads the target value.</li> <li>; Acquires the memory bank number at the reference source.</li> <li>; Specifies the memory bank number at the reference source.</li> <li>; Specifies the memory bank number at the reference source.</li> <li>; Specifies the memory bank number at the reference source.</li> <li>; Specifies the memory bank number at the reference source.</li> <li>; Specifies the contents of the HL register.</li> <li>; Restores the contents of the HL register.</li> <li>; Return</li> </ul> |

| Data<br>Data1:                         | CSEG<br>DB                                                                          | BANK3<br>0AAH                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| END                                    |                                                                                     |                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## 5.2.6 Port 5

|     | 78K0/KB2 | 78K0/KC2 | 78K0/KD2 | 78K0                                                       | /KE2                                                      | 78K0/KF2     |

|-----|----------|----------|----------|------------------------------------------------------------|-----------------------------------------------------------|--------------|

|     |          |          |          | Products<br>whose flash<br>memory is<br>less than<br>32 KB | Products<br>whose flash<br>memory is at<br>least<br>48 KB |              |

| P50 |          | _        |          | $\checkmark$                                               |                                                           | $\checkmark$ |

| P51 |          | _        |          | $\checkmark$                                               |                                                           |              |

| P52 |          | _        |          | $\checkmark$                                               |                                                           | $\checkmark$ |

| P53 | -        |          |          | $\checkmark$                                               |                                                           | $\checkmark$ |

| P54 |          | _        |          | -                                                          |                                                           |              |

| P55 | -        |          | =        |                                                            | $\checkmark$                                              |              |

| P56 | -        |          |          | -                                                          |                                                           |              |

| P57 |          | _        |          | -                                                          | _                                                         |              |

## **Remark** $\sqrt{:}$ Mounted, -: Not mounted

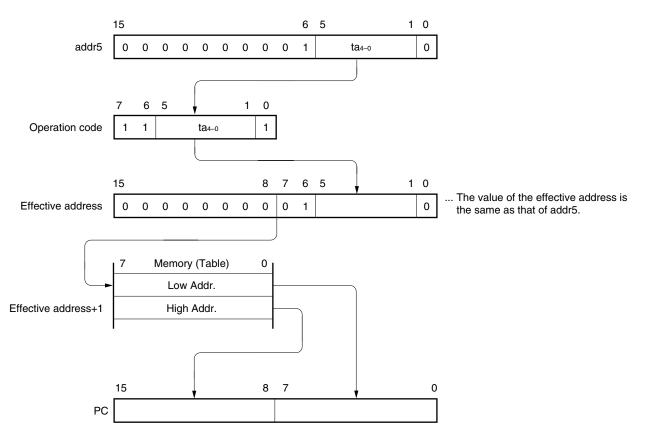

Port 5 is an I/O port with an output latch. Port 5 can be set to the input mode or output mode in 1-bit units using port mode register 5 (PM5). When the P50 to P57 pins are used as an input port, use of an on-chip pull-up resistor can be specified in 1-bit units by pull-up resistor option register 5 (PU5).

Reset signal generation sets port 5 to input mode.

Figure 5-16 shows a block diagram of port 5.

Figure 5-16. Block Diagram of P50 to P57

Remark With products not provided with an EVDD or EVSS pin, replace EVDD with VDD, or replace EVSS with VSS.

| Pin Name   | Alternate Function     |        | PM×× | P×× |

|------------|------------------------|--------|------|-----|

|            | Function Name          | I/O    |      |     |

| P30 to P32 | INTP1 to INTP3         | Input  | 1    | ×   |

| P33        | INTP4                  | Input  | 1    | ×   |

|            | TI51                   | Input  | 1    | ×   |

|            | TO51                   | Output | 0    | 0   |

| P60        | SCL0                   | I/O    | 0    | 0   |

| P61        | SDA0                   | I/O    | 0    | 0   |

| P62        | EXSCL0                 | Input  | 1    | ×   |

| P70 to P77 | KR0 to KR7             | Input  | 1    | ×   |

| P120       | INTP0                  | Input  | 1    | ×   |

|            | EXLVI                  | Input  | 1    | ×   |

| P121       | X1 <sup>Note</sup>     | -      | ×    | ×   |

| P122       | X2 <sup>Note</sup>     | -      | ×    | ×   |

|            | EXCLK <sup>Note</sup>  | Input  | ×    | ×   |

| P123       | XT1 <sup>Note</sup>    | -      | ×    | ×   |

| P124       | XT2 <sup>Note</sup>    | _      | ×    | ×   |

|            | EXCLKS <sup>Note</sup> | Input  | ×    | ×   |

| P140       | PCL                    | Output | 0    | 0   |

|            | INTP6                  | Input  | 1    | ×   |

| P141       | BUZ                    | Output | 0    | 0   |

|            | INTP7                  | Input  | 1    | ×   |

|            | BUSY0                  | Input  | 1    | ×   |

| P142       | SCKAO                  | Input  | 1    | ×   |

|            |                        | Output | 0    | 1   |

| P143       | SIA0                   | Input  | 1    | ×   |

| P144       | SOA0                   | Output | 0    | 0   |

| P145       | STB0                   | Output | 0    | 0   |

Table 5-6. Settings of Port Mode Register and Output Latch When Using Alternate Function (2/2)

- Note When using the P121 to P124 pins to connect a resonator for the main system clock (X1, X2) or subsystem clock (XT1, XT2), or to input an external clock for the main system clock (EXCLK) or subsystem clock (EXCLKS), the X1 oscillation mode, XT1 oscillation mode, or external clock input mode must be set by using the clock operation mode select register (OSCCTL) (for details, see 6.3 (1) Clock operation mode select register (OSCCTL) and (3) Setting of operation mode for subsystem clock pin). The reset value of OSCCTL is 00H (all of the P121 to P124 are I/O port pins). At this time, setting of PM121 to PM124 and P121 to P124 is not necessary.

- Remarks 1. ×: Don't care

- PM××: Port mode register

- Pxx: Port output latch

- X1, X2, P31, and P32 of the product with an on-chip debug function (μPD78F05xxD and 78F05xxDA) can be used as on-chip debug mode setting pins (OCD0A, OCD0B, OCD1A, and OCD1B) when the on-chip debug function is used. For how to connect an on-chip debug emulator (QB-MINI2), see CHAPTER 28 ON-CHIP DEBUG FUNCTION (μPD78F05xxD AND 78F05xxDA ONLY).

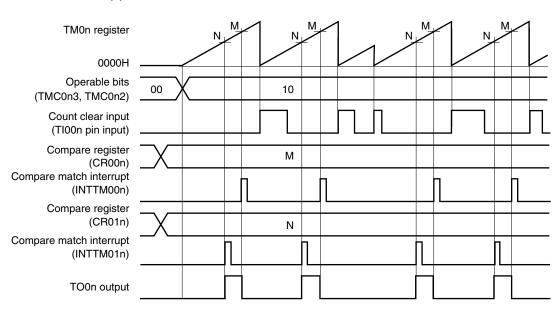

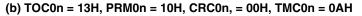

## Figure 7-28. Timing Example of Clear & Start Mode Entered by TI00n Pin Valid Edge Input (CR00n: Compare Register, CR01n: Compare Register)

(a) TOC0n = 13H, PRM0n = 10H, CRC0n, = 00H, TMC0n = 08H

(a) and (b) differ as follows depending on the setting of bit 1 (TMC0n1) of the 16-bit timer mode control register 0n (TMC0n).

- (a) The TOOn output level is inverted when TMOn matches a compare register.

- (b) The TOOn output level is inverted when TMOn matches a compare register or when the valid edge of the TI00n pin is detected.

- **Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

- n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

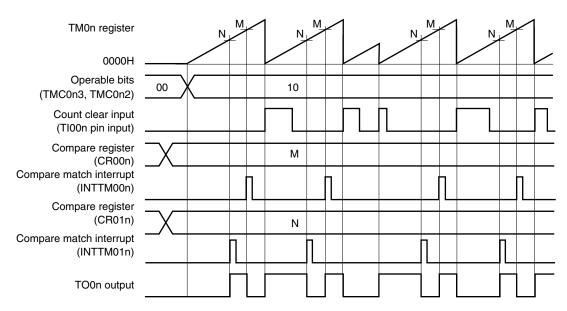

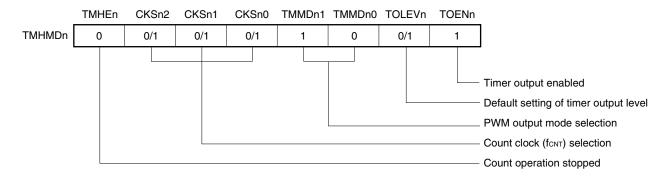

## (4) Timing of holding data by capture register

(a) When the valid edge is input to the TI00n/TI01n pin and the reverse phase of the TI00n pin is detected while CR00n/CR01n is read, CR01n performs a capture operation but the read value of CR00n/CR01n is not guaranteed. At this time, an interrupt signal (INTTM00n/INTTM01n) is generated when the valid edge of the TI00n/TI01n pin is detected (the interrupt signal is not generated when the reverse-phase edge of the TI00n pin is detected).

When the count value is captured because the valid edge of the TI00n/TI01n pin was detected, read the value of CR00n/CR01n after INTTM00n/INTTM01n is generated.

(b) The values of CR00n and CR01n are not guaranteed after 16-bit timer/event counter 0n stops.

## (5) Setting valid edge

Set the valid edge of the TI00n pin while the timer operation is stopped (TMC0n3 and TMC0n2 = 00). Set the valid edge by using ES0n0 and ES0n1.

#### (6) Re-triggering one-shot pulse

Make sure that the trigger is not generated while an active level is being output in the one-shot pulse output mode. Be sure to input the next trigger after the current active level is output.

- **Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

- n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

## 9.4.2 Operation as PWM output

In PWM output mode, a pulse with an arbitrary duty and arbitrary cycle can be output.

The 8-bit timer compare register 0n (CMP0n) controls the cycle of timer output (TOHn). Rewriting the CMP0n register during timer operation is prohibited.

The 8-bit timer compare register 1n (CMP1n) controls the duty of timer output (TOHn). Rewriting the CMP1n register during timer operation is possible.

The operation in PWM output mode is as follows.

PWM output (TOHn output) outputs an active level and 8-bit timer counter Hn is cleared to 0 when 8-bit timer counter Hn and the CMP0n register match after the timer count is started. PWM output (TOHn output) outputs an inactive level when 8-bit timer counter Hn and the CMP1n register match.

#### Setting

<1> Set each register.

#### Figure 9-11. Register Setting in PWM Output Mode

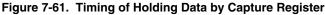

#### (i) Setting timer H mode register n (TMHMDn)

#### (ii) Setting CMP0n register

• Compare value (N): Cycle setting

## (iii) Setting CMP1n register

• Compare value (M): Duty setting

Remarks 1. n = 0, 1

**2.**  $00H \le CMP1n (M) < CMP0n (N) \le FFH$

- <2> The count operation starts when TMHEn = 1.

- <3> The CMP0n register is the compare register that is to be compared first after counter operation is enabled. When the values of the 8-bit timer counter Hn and the CMP0n register match, the 8-bit timer counter Hn is cleared, an interrupt request signal (INTTMHn) is generated, and an active level is output. At the same time, the compare register to be compared with the 8-bit timer counter Hn is changed from the CMP0n register to the CMP1n register.

- <4> When the 8-bit timer counter Hn and the CMP1n register match, an inactive level is output and the compare register to be compared with the 8-bit timer counter Hn is changed from the CMP1n register to the CMP0n register. At this time, the 8-bit timer counter Hn is not cleared and the INTTMHn signal is not generated.

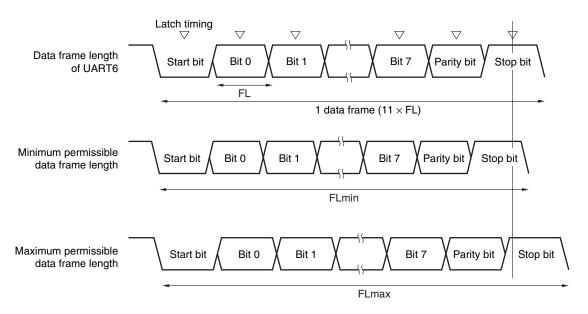

## (4) Permissible baud rate range during reception

The permissible error from the baud rate at the transmission destination during reception is shown below.

## Caution Make sure that the baud rate error during reception is within the permissible error range, by using the calculation expression shown below.

As shown in Figure 15-25, the latch timing of the receive data is determined by the counter set by baud rate generator control register 6 (BRGC6) after the start bit has been detected. If the last data (stop bit) meets this latch timing, the data can be correctly received.

Assuming that 11-bit data is received, the theoretical values can be calculated as follows.

$FL = (Brate)^{-1}$

Brate:Baud rate of UART6k:Set value of BRGC6FL:1-bit data lengthMargin of latch timing: 2 clocks

## 17.4 Operation of Serial Interface CSIA0

Serial interface CSIA0 has the following three modes.

- Operation stop mode

- 3-wire serial I/O mode

- 3-wire serial I/O mode with automatic transmit/receive function

## 17.4.1 Operation stop mode

Serial communication is not executed in this mode. Therefore, the power consumption can be reduced. In addition, the P142/SCKA0, P143/SIA0, and P144/SOA0 pins can be used as ordinary I/O port pins in this mode.

## (1) Register used

The operation stop mode is set by serial operation mode specification register 0 (CSIMA0). To set the operation stop mode, clear bit 7 (CSIAE0) of CSIMA0 to 0.

## (a) Serial operation mode specification register 0 (CSIMA0)

This is an 8-bit register used to control the serial communication operation. This register can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation clears this register to 00H.

Address: FF90H After reset: 00H R/W

<7> 6 5 4 <3> <2> 1 0 CSIMA0 CSIAE0 ATE0 ATM0 MASTER0 TXEA0 RXEA0 DIR0 0

| CSIAE0 | Control of CSIA0 operation enable/disable                                                                    |

|--------|--------------------------------------------------------------------------------------------------------------|

| 0      | CSIA0 operation disabled (SOA0: Low level, SCKA0: High level) and asynchronously resets the internal circuit |

| Interrupt | Internal/ | Basic                  | Default                    |                     | Interrupt Source                                                                                                                                | Vector  | к            | к            | К            | к                                                                                                                                               | к            |              |              |              |              |              |                                                                      |

|-----------|-----------|------------------------|----------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------|--------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|----------------------------------------------------------------------|

| Туре      | External  | Configuration          | Priority <sup>Note 2</sup> | Name                | Trigger                                                                                                                                         | Table   | В            | С            | D            | Е                                                                                                                                               | F            |              |              |              |              |              |                                                                      |

|           |           | Type <sup>Note 1</sup> |                            |                     |                                                                                                                                                 | Address | 2            | 2            | 2            | 2                                                                                                                                               | 2            |              |              |              |              |              |                                                                      |

| Maskable  | Internal  | (A)                    | 0                          | INTLVI              | Low-voltage detection <sup>Note 3</sup>                                                                                                         | 0004H   |              |              |              |                                                                                                                                                 | $\checkmark$ |              |              |              |              |              |                                                                      |

|           | External  | (B)                    | 1                          | INTP0               | Pin input edge detection                                                                                                                        | 0006H   | $\checkmark$ | $\checkmark$ |              | $\checkmark$                                                                                                                                    | $\checkmark$ |              |              |              |              |              |                                                                      |

|           |           |                        | 2                          | INTP1               |                                                                                                                                                 | 0008H   | $\checkmark$ | $\checkmark$ |              | $\checkmark$                                                                                                                                    | $\checkmark$ |              |              |              |              |              |                                                                      |

|           |           |                        | 3                          | INTP2               |                                                                                                                                                 | 000AH   | $\checkmark$ | $\checkmark$ |              | $\checkmark$                                                                                                                                    | $\checkmark$ |              |              |              |              |              |                                                                      |

|           |           |                        | 4                          | INTP3               |                                                                                                                                                 | 000CH   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$                                                                                                                                    | $\checkmark$ |              |              |              |              |              |                                                                      |

|           |           |                        | 5                          | INTP4               |                                                                                                                                                 | 000EH   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$                                                                                                                                    | $\checkmark$ |              |              |              |              |              |                                                                      |

|           |           |                        | 6                          | INTP5               |                                                                                                                                                 | 0010H   | $\checkmark$ | $\checkmark$ |              | $\checkmark$                                                                                                                                    | $\checkmark$ |              |              |              |              |              |                                                                      |

|           | Internal  | (A)                    | 7                          | INTSRE6             | UART6 reception error generation                                                                                                                | 0012H   | $\checkmark$ | $\checkmark$ |              | $\checkmark$                                                                                                                                    | $\checkmark$ |              |              |              |              |              |                                                                      |

|           |           |                        | 8                          | INTSR6              | End of UART6 reception                                                                                                                          | 0014H   |              | $\checkmark$ |              | $\checkmark$                                                                                                                                    |              |              |              |              |              |              |                                                                      |

|           |           |                        | 9                          | INTST6              | End of UART6 transmission                                                                                                                       | 0016H   |              | $\checkmark$ |              | $\checkmark$                                                                                                                                    |              |              |              |              |              |              |                                                                      |

|           |           |                        | 10                         | INTCSI10/<br>INTST0 | End of CSI10 communication/end of UART0 transmission                                                                                            | 0018H   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$                                                                                                                                    | $\checkmark$ |              |              |              |              |              |                                                                      |

|           |           |                        |                            |                     |                                                                                                                                                 |         |              | 11           | INTTMH1      | Match between TMH1 and CMP01<br>(when compare register is specified)                                                                            | 001AH        | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |                                                                      |

|           |           |                        |                            |                     |                                                                                                                                                 |         |              |              |              |                                                                                                                                                 |              |              |              |              | 12           | INTTMHO      | Match between TMH0 and CMP00<br>(when compare register is specified) |

|           |           |                        | 13                         | INTTM50             | Match between TM50 and CR50<br>(when compare register is specified)                                                                             | 001EH   | $\checkmark$ | V            | V            | V                                                                                                                                               | $\checkmark$ |              |              |              |              |              |                                                                      |

|           |           |                        |                            |                     |                                                                                                                                                 |         |              | 14           | INTTM000     | Match between TM00 and CR000<br>(when compare register is specified),<br>TI010 pin valid edge detection<br>(when capture register is specified) | 0020H        | V            | V            | $\checkmark$ | V            | $\checkmark$ |                                                                      |

|           |           |                        | 15                         | INTTM010            | Match between TM00 and CR010<br>(when compare register is specified),<br>TI000 pin valid edge detection<br>(when capture register is specified) | 0022H   | V            | V            | $\checkmark$ | V                                                                                                                                               | $\checkmark$ |              |              |              |              |              |                                                                      |

|           |           |                        | 16                         | INTAD               | End of A/D conversion                                                                                                                           | 0024H   | $\checkmark$ | $\checkmark$ |              | $\checkmark$                                                                                                                                    | $\checkmark$ |              |              |              |              |              |                                                                      |

|           |           |                        | 17                         | INTSR0              | End of UART0 reception or reception error generation                                                                                            | 0026H   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$                                                                                                                                    | $\checkmark$ |              |              |              |              |              |                                                                      |

|           |           |                        | 18                         | INTWTI              | Watch timer reference time interval signal                                                                                                      | 0028H   | -            | $\checkmark$ |              | $\checkmark$                                                                                                                                    |              |              |              |              |              |              |                                                                      |

|           |           |                        | 19                         | INTTM51<br>Note 4   | Match between TM51 and CR51<br>(when compare register is specified)                                                                             | 002AH   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$                                                                                                                                    | $\checkmark$ |              |              |              |              |              |                                                                      |

| Table 20-1. | Interrupt Source List (1/2) |

|-------------|-----------------------------|

|-------------|-----------------------------|

Notes 1. Basic configuration types (A) to (D) correspond to (A) to (D) in Figure 20-1.

- 2. The default priority determines the sequence of processing vectored interrupts if two or more maskable interrupts occur simultaneously. Zero indicates the highest priority and 28 indicates the lowest priority.

- 3. When bit 1 (LVIMD) of the low-voltage detection register (LVIM) is cleared to 0.

- 4. When 8-bit timer/event counter 51 is used in the carrier generator mode, an interrupt is generated upon the timing when the INTTM5H1 signal is generated (see Figure 9-13 Transfer Timing).

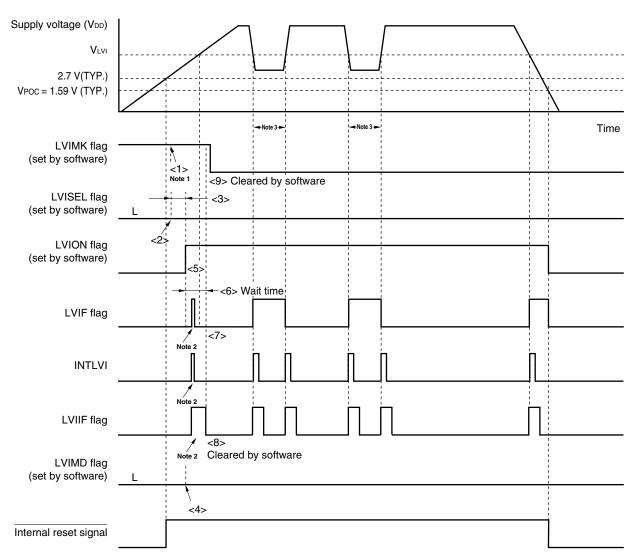

## Figure 25-7. Timing of Low-Voltage Detector Interrupt Signal Generation (Detects Level of Supply Voltage (VDD)) (2/2)

## (2) In 2.7 V/1.59 V POC mode (option byte: POCMODE = 1)

Notes 1. The LVIMK flag is set to "1" by reset signal generation.

- 2. The interrupt request signal (INTLVI) is generated and the LVIF and LVIIF flags may be set (1).

- **3.** If LVION is cleared (0) in a state below the LVI detection voltage, an INTLVI signal is generated and LVIIF becomes 1.

- **Remark** <1> to <9> in Figure 25-7 above correspond to <1> to <9> in the description of "When starting operation" in **25.4.2 (1) When detecting level of supply voltage (V**<sub>DD</sub>).

## (2) When detecting level of input voltage from external input pin (EXLVI)

- When starting operation

- <1> Mask the LVI interrupt (LVIMK = 1).

- <2> Set bit 2 (LVISEL) of the low-voltage detection register (LVIM) to 1 (detects level of input voltage from external input pin (EXLVI)).

- <3> Clear bit 1 (LVIMD) of LVIM to 0 (generates interrupt signal when the level is detected) (default value).

- <4> Set bit 7 (LVION) of LVIM to 1 (enables LVI operation).

- <5> Use software to wait for an operation stabilization time (10  $\mu$ s (MIN.)).

- <6> Confirm that "input voltage from external input pin (EXLVI) ≥ detection voltage (VEXLVI = 1.21 V (TYP.)" when detecting the falling edge of EXLVI, or "input voltage from external input pin (EXLVI) < detection voltage (VEXLVI = 1.21 V (TYP.)" when detecting the rising edge of EXLVI, at bit 0 (LVIF) of LVIM.</p>

- <7> Clear the interrupt request flag of LVI (LVIIF) to 0.

- <8> Release the interrupt mask flag of LVI (LVIMK).

- <9> Execute the El instruction (when vector interrupts are used).

Figure 25-8 shows the timing of the interrupt signal generated by the low-voltage detector. The numbers in this timing chart correspond to <1> to <8> above.

## Caution Input voltage from external input pin (EXLVI) must be EXLVI < VDD.

- When stopping operation Either of the following procedures must be executed.

- When using 8-bit memory manipulation instruction: Write 00H to LVIM.

- When using 1-bit memory manipulation instruction: Clear LVION to 0.

## Caution The pins mounted depend on the product. Refer to Caution at the beginning of this chapter.

| Parameter              | Symbol | Conditions                                                                                                                                                          | Ratings                                                                                    | Unit |

|------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------|

| Supply voltage         | VDD    |                                                                                                                                                                     | -0.5 to +6.5                                                                               | V    |

|                        | EVDD   |                                                                                                                                                                     | –0.5 to +6.5                                                                               | V    |

|                        | Vss    |                                                                                                                                                                     | –0.5 to +0.3                                                                               | V    |

|                        | EVss   |                                                                                                                                                                     | –0.5 to +0.3                                                                               | V    |

|                        | AVREF  |                                                                                                                                                                     | -0.5 to V <sub>DD</sub> + 0.3 <sup>Note</sup>                                              | V    |

|                        | AVss   |                                                                                                                                                                     | -0.5 to +0.3                                                                               | V    |

| REGC pin input voltage | VIREGC |                                                                                                                                                                     | $-0.5$ to +3.6 and $-0.5$ to $V_{\text{DD}}$                                               | V    |

| Input voltage          | VII    | P00 to P06, P10 to P17, P20 to P27, P30<br>to P33, P40 to P47, P50 to P57, P64 to<br>P67, P70 to P77, P120 to P124, P140 to<br>P145, X1, X2, XT1, XT2, RESET, FLMD0 | $-0.3$ to V <sub>DD</sub> + $0.3^{Note}$                                                   | V    |

|                        | VI2    | P60 to P63 (N-ch open drain)                                                                                                                                        | –0.3 to +6.5                                                                               | V    |

| Output voltage         | Vo     |                                                                                                                                                                     | -0.3 to V <sub>DD</sub> + 0.3 <sup>Note</sup>                                              | V    |

| Analog input voltage   | Van    | ANI0 to ANI7                                                                                                                                                        | $-0.3$ to AV <sub>REF</sub> + $0.3^{Note}$<br>and $-0.3$ to V <sub>DD</sub> + $0.3^{Note}$ | V    |

## Absolute Maximum Ratings (T<sub>A</sub> = 25°C) (1/2)

Note Must be 6.5 V or lower.

- Caution Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

- **Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of port pins.

## Caution The pins mounted depend on the product. Refer to Caution at the beginning of this chapter.

| Parameter                     | Symbol |                             | Conditions                                                                                                               | Ratings     | Unit |

|-------------------------------|--------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------|------|

| Output current, high          | Іон    | Per pin                     | P00 to P06, P10 to P17,<br>P30 to P33, P40 to P47,<br>P50 to P57, P64 to P67,<br>P70 to P77, P120,<br>P130, P140 to P145 | -10         | mA   |

|                               |        | Total of all pins<br>-80 mA | P00 to P04, P40 to P47,<br>P120, P130, P140 to<br>P145                                                                   | -25         | mA   |

|                               |        |                             | P05, P06, P10 to P17,<br>P30 to P33, P50 to P57,<br>P64 to P67, P70 to P77                                               | -55         | mA   |

|                               |        | Per pin                     | P20 to P27                                                                                                               | -0.5        | mA   |

|                               |        | Total of all pins           |                                                                                                                          | -2          | mA   |

|                               |        | Per pin                     | P121 to P124                                                                                                             | -1          | mA   |

|                               |        | Total of all pins           |                                                                                                                          | -4          | mA   |

| Output current, low           | Ιοι    | Per pin                     | P00 to P06, P10 to P17,<br>P30 to P33, P40 to P47,<br>P50 to P57, P60 to P67,<br>P70 to P77, P120, P130,<br>P140 to P145 | 30          | mA   |

|                               |        | Total of all pins<br>200 mA | P00 to P04, P40 to P47,<br>P120, P130, P140 to<br>P145                                                                   | 60          | mA   |

|                               |        |                             | P05, P06, P10 to P17,<br>P30 to P33, P50 to P57,<br>P60 to P67, P70 to P77                                               | 140         | mA   |

|                               |        | Per pin                     | P20 to P27                                                                                                               | 1           | mA   |

|                               |        | Total of all pins           |                                                                                                                          | 5           | mA   |

|                               |        | Per pin                     | P121 to P124                                                                                                             | 4           | mA   |

|                               |        | Total of all pins           |                                                                                                                          | 10          | mA   |

| Operating ambient temperature | TA     |                             |                                                                                                                          | -40 to +110 | °C   |

| Storage temperature           | Tstg   |                             |                                                                                                                          | -65 to +150 | °C   |

## Absolute Maximum Ratings (T<sub>A</sub> = 25°C) (2/2)

- Cautions 1. Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

- 2. The value of the current that can be run per pin must satisfy the value of the current per pin and the total value of the currents of all pins.

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of port pins.

Caution The pins mounted depend on the product. Refer to Caution at the beginning of this chapter.

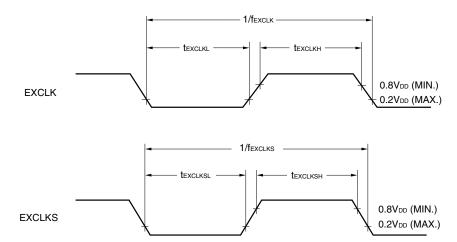

**AC Timing Test Points**

Vн Vін Test points Vı∟ VIL \*

External Main System Clock Timing, External Subsystem Clock Timing

| r          |                |                            | Γ                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (25            | 5/30) |

|------------|----------------|----------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------|

| Chapter    | Classification | Function                   | Details of<br>Function                                        | Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Pag            | e     |

| Chapter 22 | Hard           | Standby<br>function        | OSTS:<br>Oscillation<br>stabilization time<br>select register | The X1 clock oscillation stabilization wait time does not include the time until clock oscillation starts ("a" below).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | p. 669         |       |

|            | Soft           |                            | STOP mode                                                     | Because the interrupt request signal is used to clear the standby mode, if there is an interrupt source with the interrupt request flag set and the interrupt mask flag reset, the standby mode is immediately cleared if set. Thus, the STOP mode is reset to the HALT mode immediately after execution of the STOP instruction and the system returns to the operating mode as soon as the wait time set using the oscillation stabilization time select register (OSTS) has elapsed.                                                                                                                                                                                                                                                                                                                                                                                                                                                             | p. 674         |       |

|            |                |                            |                                                               | To use the peripheral hardware that stops operation in the STOP mode, and the peripheral hardware for which the clock that stops oscillating in the STOP mode after the STOP mode is released, restart the peripheral hardware.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | p. 676         |       |

|            |                |                            |                                                               | Even if "internal low-speed oscillator can be stopped by software" is selected by the option byte, the internal low-speed oscillation clock continues in the STOP mode in the status before the STOP mode is set. To stop the internal low-speed oscillator's oscillation in the STOP mode, stop it by software and then execute the STOP instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | p. 676         |       |

|            |                |                            |                                                               | To shorten oscillation stabilization time after the STOP mode is released when the CPU operates with the high-speed system clock (X1 oscillation), switch the CPU clock to the internal highspeed oscillation clock before the execution of the STOP instruction using the following procedure.<br><1> Set RSTOP to 0 (starting oscillation of the internal high-speed oscillator)<br><2> Set MCM0 to 0 (switching the CPU from X1 oscillation to internal high-speed oscillation) <3> Check that MCS is 0 (checking the CPU clock) <4> Check that<br>RSTS is 1 (checking internal high-speed oscillation operation) <5> Execute the<br>STOP instruction<br>Before changing the CPU clock from the internal high-speed oscillation clock to the<br>high-speed system clock (X1 oscillation) after the STOP mode is released, check the<br>oscillation stabilization time with the oscillation stabilization time counter status<br>register (OSTC). | p. 676         |       |

|            |                |                            |                                                               | If the STOP instruction is executed when AMPH = 1, supply of the CPU clock is stopped for 4.06 to 16.12 $\mu$ s after the STOP mode is released when the internal high-speed oscillation clock is selected as the CPU clock, or for the duration of 160 external clocks when the high-speed system clock (external clock input) is selected as the CPU clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | p. 676         |       |

|            |                |                            |                                                               | Execute the STOP instruction after having confirmed that the internal high-speed oscillator is operating stably (RSTS = 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | p. 676         |       |

| r 23       | łard           | Reset<br>function          | _                                                             | For an external reset, input a low level for 10 $\mu$ s or more to the RESET pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | p. 681         |       |

| Chapter 23 | -              | Tunction                   |                                                               | During reset input, the X1 clock, XT1 clock, internal high-speed oscillation clock, and internal low-speed oscillation clock stop oscillating. External main system clock input and external subsystem clock input become invalid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | p. 681         |       |

|            |                |                            |                                                               | When the STOP mode is released by a reset, the STOP mode contents are held during reset input. However, the port pins become high-impedance, except for P130, which is set to low-level output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | p. 681         |       |

|            |                |                            | Block diagram of<br>reset function                            | An LVI circuit internal reset does not reset the LVI circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | p. 682         |       |

|            |                |                            | Watchdog timer<br>overflow                                    | A watchdog timer internal reset resets the watchdog timer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | p. 684         |       |

|            | Soft           |                            | RESF: Reset<br>control flag<br>register                       | Do not read data by a 1-bit memory manipulation instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | p. 691         |       |

| Chapter 24 | Soft           | Power-on-<br>clear circuit | _                                                             | If an internal reset signal is generated in the POC circuit, the reset control flag register (RESF) is cleared to 00H.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | p. 692         |       |