# E·X Renesas Electronics America Inc - <u>UPD78F0536AGK-GAJ-AX Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | 78K/0                                                                                 |

| Core Size                  | 8-Bit                                                                                 |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                                    |

| Number of I/O              | 55                                                                                    |

| Program Memory Size        | 96KB (96K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 5K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 8x10b                                                                             |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 64-LQFP                                                                               |

| Supplier Device Package    | -                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0536agk-gaj-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Related DocumentsThe related documents indicated in this publication may include preliminary versions.However, preliminary versions are not marked as such.

#### **Documents Related to Devices**

| Document Name                                                       | Document No. |

|---------------------------------------------------------------------|--------------|

| 78K0/Kx2 User's Manual                                              | This manual  |

| 78K/0 Series Instructions User's Manual                             | U12326E      |

| 78K0/Kx2 Flash Memory Programming (Programmer) Application Note     | U17739E      |

| 78K0/Kx2 Flash Memory Self Programming User's Manual                | U17516E      |

| 78K0/Kx2 EEPROM <sup>™</sup> Emulation Application Note             | U17517E      |

| 78K0 Microcontrollers Self Programming Library Type01 User's Manual | U18274E      |

| 78K0 Microcontrollers EEPROM Emulation Library Type01 User's Manual | U18275E      |

#### **Documents Related to Flash Memory Programming**

| Document Name                                | Document No. |

|----------------------------------------------|--------------|

| PG-FP5 Flash Memory Programmer User's Manual | U18865E      |

| PG-FP4 Flash Memory Programmer User's Manual | U15260E      |

## **Documents Related to Development Tools (Hardware)**

| Document Name                                                           | Document No. |

|-------------------------------------------------------------------------|--------------|

| QB-78K0KX2 In-Circuit Emulator User's Manual                            | U17341E      |

| QB-MINI2 On-Chip Debug Emulator with Programming Function User's Manual | U18371E      |

# Caution The related documents listed above are subject to change without notice. Be sure to use the latest version of each document when designing.

1.1.3 Time Instruction cycle, peripheral hardware clock frequency, external main system clock frequency, external main system clock input high-level width, and external main system clock input low-level width (AC characteristics)

| Parameter                         | Symbol          | Cor                                                               | ditions                                                | MIN.                  | TYP. | MAX. | Unit |

|-----------------------------------|-----------------|-------------------------------------------------------------------|--------------------------------------------------------|-----------------------|------|------|------|

| Instruction cycle (minimum        | Тсү             | Main system clock (fxp)                                           | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                  | 0.1                   |      | 32   | μS   |

| instruction execution time)       |                 | operation                                                         | $2.7~V \leq V_{\text{DD}} < 4.0~V$                     | 0.2                   |      | 32   | μS   |

|                                   |                 |                                                                   | $1.8 \ V \le V_{\text{DD}} < 2.7 \ V^{\text{Note 1}}$  | 0.4 <sup>Note 3</sup> |      | 32   | μs   |

|                                   |                 | Subsystem clock (fsub)                                            | operation <sup>Note 2</sup>                            | 114                   | 122  | 125  | μs   |

| Peripheral hardware clock         | fprs            | fprs = fxн                                                        | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                  |                       |      | 20   | MHz  |

| frequency                         |                 | (XSEL = 1)                                                        | $2.7~V \leq V_{\text{DD}} < 4.0~V$                     |                       |      | 10   | MHz  |

|                                   |                 |                                                                   | $1.8~V \leq V_{\text{DD}} < 2.7~V^{\text{Note 1}}$     |                       |      | 5    | MHz  |

|                                   |                 | fprs = frн                                                        | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$                  | 7.6                   |      | 8.4  | MHz  |

|                                   |                 | (XSEL = 0)                                                        | $1.8~V \leq V_{\text{DD}} < 2.7~V^{\text{Notes 1, 5}}$ | 7.6                   |      | 10.4 | MHz  |

| External main system clock        | fexclk          | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                             |                                                        | 1.0 <sup>Note 6</sup> |      | 20.0 | MHz  |

| frequency                         |                 | $2.7~V \leq V_{\text{DD}} < 4.0~V$                                |                                                        | 1.0 <sup>Note 6</sup> |      | 10.0 | MHz  |

|                                   |                 | $1.8 \text{ V} \le V_{\text{DD}} < 2.7 \text{ V}^{\text{Note 1}}$ |                                                        |                       |      | 5.0  | MHz  |

| External main system clock input  | texclkh,        | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                             | 24                                                     |                       |      | ns   |      |

| high-level width, low-level width | <b>t</b> exclkl | $2.7~V \leq V_{\text{DD}} < 4.0~V$                                |                                                        | 48                    |      |      | ns   |

|                                   |                 | $1.8 \text{ V} \le V_{\text{DD}} < 2.7 \text{ V}^{\text{Note 1}}$ |                                                        | 96                    |      |      | ns   |

#### (1) Conventional-specification products (µPD78F05xx and 78F05xxD)

#### (2) Expanded-specification products (µPD78F05xxA and 78F05xxDA)

| Parameter                           | Symbol          | Cor                                                | nditions                                               | MIN.                  | TYP. | MAX. | Unit |

|-------------------------------------|-----------------|----------------------------------------------------|--------------------------------------------------------|-----------------------|------|------|------|

| Instruction cycle (minimum          | Тсү             | Main system clock (fxp)                            | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$                  | 0.1                   |      | 32   | μS   |

| instruction execution time)         |                 | operation                                          | $1.8~V \leq V_{\text{DD}} < 2.7~V^{\text{Note 1}}$     | 0.4 <sup>Note 3</sup> |      | 32   | μs   |

|                                     |                 | Subsystem clock (fsub)                             | operation <sup>Note 2</sup>                            | 114                   | 122  | 125  | μs   |

| Peripheral hardware clock fPRs fPRs |                 | fprs = fxh                                         | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                  |                       |      | 20   | MHz  |

| frequency                           |                 | (XSEL = 1)                                         | $2.7~V \leq V_{\text{DD}} < 4.0~V^{\text{Note 4}}$     |                       |      | 20   | MHz  |

|                                     |                 |                                                    | $1.8~V \leq V_{\text{DD}} < 2.7~V^{\text{Note 1}}$     |                       |      | 5    | MHz  |

|                                     |                 | fprs = frh                                         | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$                  | 7.6                   |      | 8.4  | MHz  |

|                                     |                 | (XSEL = 0)                                         | $1.8~V \leq V_{\text{DD}} < 2.7~V^{\text{Notes 1, 5}}$ | 7.6                   |      | 10.4 | MHz  |

| External main system clock          | <b>f</b> exclk  | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$              |                                                        | 1.0 <sup>Note 6</sup> |      | 20.0 | MHz  |

| frequency                           |                 | $1.8~V \leq V_{\text{DD}} < 2.7~V^{\text{Note 1}}$ | 1.0                                                    |                       | 5.0  | MHz  |      |

| External main system clock input    | texclkh,        | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$              | 24                                                     |                       |      | ns   |      |

| high-level width, low-level width   | <b>t</b> exclkl | $1.8~V \leq V_{\text{DD}} < 2.7~V^{\text{Note 1}}$ | 96                                                     |                       |      | ns   |      |

Notes 1. Standard and (A) grade products only

- 2. The 78K0/KB2 is not provided with a subsystem clock.

- **3.** 0.38  $\mu$ s when operating with the 8 MHz internal oscillator.

- Characteristics of the main system clock frequency. Set the division clock to be set by a peripheral function to fxH/2 (10 MHz) or less. The multiplier/divider, however, can operate on fxH (20 MHz).

- 5. Characteristics of the main system clock frequency. Set the division clock to be set by a peripheral function to fRH/2 or less.

- 6. 2.0 MHz (MIN.) when using UART6 during on-board programming.

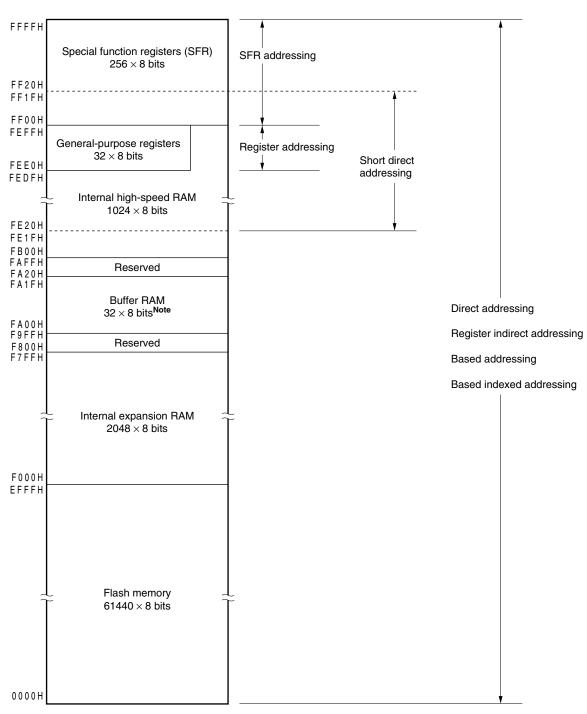

# Figure 3-17. Correspondence Between Data Memory and Addressing (μPD78F0515, 78F0515A, 78F0525, 78F0525A, 78F0535A, 78F0545, 78F0545A, 78F0515D and 78F0515DA)

Note The buffer RAM is incorporated only in the  $\mu$ PD78F0545 and 78F0545A (78K0/KF2). The area from FA00H to FA1FH cannot be used with the  $\mu$ PD78F0515, 78F0515A, 78F0525, 78F0525A, 78F0535A, 78F0515D, and 78F0515DA.

Remark Note the following points to use the memory bank select function efficiently.

- Allocate a routine that is used often in the common area.

- If a value that is planned to be referenced is placed in RAM, it can be referenced from all of the areas.

- If the reference destination and the branch destination of the routine placed in a memory bank are placed in the same memory bank, then the code size and processing are more efficient.

- Allocate interrupt servicing that requires a quick response in the common area.

## 5.2.7 Port 6

|            | 78K0/KB2     | 78K0/KC2 | 78K0/KD2     | 78K0                                                       | /KE2                                                      | 78K0/KF2     |  |

|------------|--------------|----------|--------------|------------------------------------------------------------|-----------------------------------------------------------|--------------|--|

|            |              |          |              | Products<br>whose flash<br>memory is<br>less than<br>32 KB | Products<br>whose flash<br>memory is at<br>least<br>48 KB |              |  |

| P60/SCL0   | $\checkmark$ |          | $\checkmark$ |                                                            |                                                           |              |  |

| P61/SDA0   | $\checkmark$ |          | $\checkmark$ |                                                            |                                                           |              |  |

| P62/EXSCL0 | -            |          | $\checkmark$ |                                                            |                                                           |              |  |

| P63        | -            |          | $\checkmark$ |                                                            |                                                           |              |  |

| P64        | _            |          | _            |                                                            |                                                           |              |  |

| P65        | _            |          |              |                                                            |                                                           |              |  |

| P66        | _            |          |              |                                                            |                                                           |              |  |

| P67        | _            |          | _            | _                                                          |                                                           | $\checkmark$ |  |

**Remark**  $\sqrt{:}$  Mounted, -: Not mounted

Port 6 is an I/O port with an output latch. Port 6 can be set to the input mode or output mode in 1-bit units using port mode register 6 (PM6). When the P64 to P67 pins are used as an input port, use of an on-chip pull-up resistor can be specified in 1-bit units by pull-up resistor option register 6 (PU6).

The output of the P60 to P63 pins is N-ch open-drain output (6 V tolerance).

This port can also be used for serial interface data I/O, clock I/O, and external clock input.

Reset signal generation sets port 6 to input mode.

Figures 5-17 to 5-20 show block diagrams of port 6.

**Remark** When using P62/EXSCL0 as an external clock input pin of the serial interface, input a clock of 6.4 MHz to it.

| Symbol | 7    | 6         | 5                                    | 4    | 3        | 2          | 1           | 0             | Address | After reset | R/W |

|--------|------|-----------|--------------------------------------|------|----------|------------|-------------|---------------|---------|-------------|-----|

| PU0    | 0    | PU06      | PU05                                 | PU04 | PU03     | PU02       | PU01        | PU00          | FF30H   | 00H         | R/W |

|        |      |           |                                      |      |          |            |             |               |         |             |     |

| PU1    | PU17 | PU16      | PU15                                 | PU14 | PU13     | PU12       | PU11        | PU10          | FF31H   | 00H         | R/W |

|        |      |           |                                      |      |          |            | 1           |               | 1       |             |     |

| PU3    | 0    | 0         | 0                                    | 0    | PU33     | PU32       | PU31        | PU30          | FF33H   | 00H         | R/W |

|        | L    | <u>.</u>  | . <u> </u>                           | ·    | <u> </u> | .1         | <u>.</u>    | <u>.</u>      | 1       |             |     |

| PU4    | 0    | 0         | 0                                    | 0    | PU43     | PU42       | PU41        | PU40          | FF34H   | 00H         | R/W |

|        | L    |           | . <u> </u>                           | ·    |          |            |             |               | 1       |             |     |

| PU5    | 0    | 0         | 0                                    | 0    | PU53     | PU52       | PU51        | PU50          | FF35H   | 00H         | R/W |

|        |      |           |                                      | ·    |          |            | <u>I</u>    |               | 1       |             |     |

| PU7    | PU77 | PU76      | PU75                                 | PU74 | PU73     | PU72       | PU71        | PU70          | FF37H   | 00H         | R/W |

|        | L    |           |                                      | ·    |          |            |             |               | 1       |             |     |

| PU12   | 0    | 0         | 0                                    | 0    | 0        | 0          | 0           | PU120         | FF3CH   | 00H         | R/W |

|        | L    | <u>.</u>  |                                      | ·    | 1        |            | <u>.</u>    | <u>.</u>      | 1       |             |     |

| PU14   | 0    | 0         | 0                                    | 0    | 0        | 0          | PU141       | PU140         | FF3EH   | 00H         | R/W |

|        |      |           | <u> </u>                             | ·    |          |            |             |               | 1       |             |     |

|        | PUmn | Γ         |                                      |      | Pmn p    | in on-chip | pull-up res | istor select  | lion    |             |     |

|        |      |           |                                      |      | •        |            | • •         | 4; n = 0 to 7 |         |             |     |

|        | 0    | Ore albim | n akin pullum resister not connected |      |          |            |             |               |         |             |     |

# Figure 5-42. Format of Pull-up Resistor Option Register (78K0/KE2)

| PUmn | Pmn pin on-chip pull-up resistor selection |  |  |  |

|------|--------------------------------------------|--|--|--|

|      | (m = 0, 1, 3 to 5, 7, 12, 14; n = 0 to 7)  |  |  |  |

| 0    | Dn-chip pull-up resistor not connected     |  |  |  |

| 1    | On-chip pull-up resistor connected         |  |  |  |

#### 6.4.3 When subsystem clock is not used

If it is not necessary to use the subsystem  $clock^{Note}$  for low power consumption operations, or if not using the subsystem clock as an I/O port, set the XT1 and XT2 pins to I/O mode (OSCSELS = 0) and connect them as follows.

Note The 78K0/KB2 is not provided with a subsystem clock.

Input (PM123/PM124 = 1): Independently connect to  $V_{DD}$  or  $V_{SS}$  via a resistor. Output (PM123/PM124 = 0): Leave open.

Remark OSCSELS: Bit 4 of clock operation mode select register (OSCCTL) PM123, PM124: Bits 3 and 4 of port mode register 12 (PM12)

#### 6.4.4 Internal high-speed oscillator

The internal high-speed oscillator is incorporated in the 78K0/Kx2 microcontrollers. Oscillation can be controlled by the internal oscillation mode register (RCM).

After a reset release, the internal high-speed oscillator automatically starts oscillation (8 MHz (TYP.)).

#### 6.4.5 Internal low-speed oscillator

The internal low-speed oscillator is incorporated in the 78K0/Kx2 microcontrollers.

The internal low-speed oscillation clock is only used as the watchdog timer and the clock of 8-bit timer H1. The internal low-speed oscillation clock cannot be used as the CPU clock.

"Can be stopped by software" or "Cannot be stopped" can be selected by the option byte. When "Can be stopped by software" is set, oscillation can be controlled by the internal oscillation mode register (RCM).

After a reset release, the internal low-speed oscillator automatically starts oscillation, and the watchdog timer is driven (240 kHz (TYP.)) if the watchdog timer operation is enabled using the option byte.

#### 6.4.6 Prescaler

The prescaler generates the CPU clock by dividing the main system clock when the main system clock is selected as the clock to be supplied to the CPU.

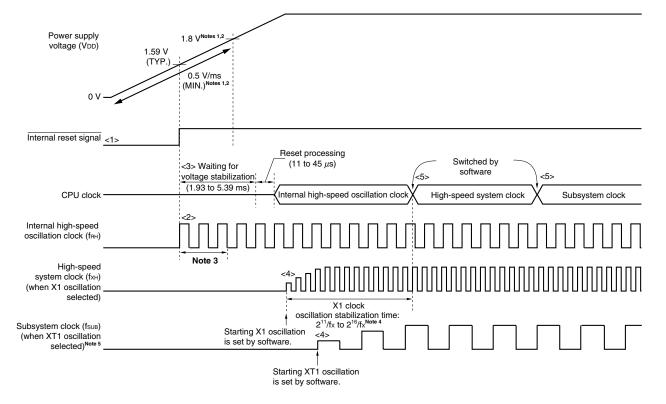

# Figure 6-15. Clock Generator Operation When Power Supply Voltage Is Turned On (When 1.59 V POC Mode Is Set (Option Byte: POCMODE = 0))

- <1> When the power is turned on, an internal reset signal is generated by the power-on-clear (POC) circuit.

- <2> When the power supply voltage exceeds 1.59 V (TYP.), the reset is released and the internal high-speed oscillator automatically starts oscillation.

- <3> When the power supply voltage rises with a slope of 0.5 V/ms (MIN.), the CPU starts operation on the internal high-speed oscillation clock after the reset is released and after the stabilization times for the voltage of the power supply and regulator have elapsed, and then reset processing is performed.

- <4> Set the start of oscillation of the X1 or XT1 clock via software (see (1) in 6.6.1 Example of controlling high-speed system clock and (1) in 6.6.3 Example of controlling subsystem clock).

- <5> When switching the CPU clock to the X1 or XT1 clock, wait for the clock oscillation to stabilize, and then set switching via software (see (3) in 6.6.1 Example of controlling high-speed system clock and (3) in 6.6.3 Example of controlling subsystem clock).

- Notes 1. With standard and (A) grade products, if the voltage rises with a slope of less than 0.5 V/ms (MIN.) from power application until the voltage reaches 1.8 V, input a low level to the RESET pin from power application until the voltage reaches 1.8 V, or set the 2.7 V/1.59 V POC mode by using the option byte (POCMODE = 1) (see Figure 6-16). When a low level has been input to the RESET pin until the voltage reaches 1.8 V, the CPU operates with the same timing as <2> and thereafter in Figure 6-15, after the reset has been released by the RESET pin.

- 2. With (A2) grade products, if the voltage rises with a slope of less than 0.75 V/ms (MIN.) from power application until the voltage reaches 2.7 V, input a low level to the RESET pin from power application until the voltage reaches 2.7 V. When a low level has been input to the RESET pin until the voltage reaches 2.7 V, the CPU operates with the same timing as <2> and thereafter in Figure 6-15, after the reset has been released by the RESET pin.

- **3.** The internal voltage stabilization time includes the oscillation accuracy stabilization time of the internal high-speed oscillation clock.

| Address: FFE | 36H After re | eset: 00H R   | /W                |                                                                                                                              |                  |                   |            |       |  |

|--------------|--------------|---------------|-------------------|------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|------------|-------|--|

| Symbol       | 7            | 6             | 5                 | 4                                                                                                                            | 3                | 2                 | 1          | <0>   |  |

| TMC01        | 0            | 0             | 0                 | 0                                                                                                                            | TMC013           | TMC012            | TMC011     | OVF01 |  |

|              |              |               |                   |                                                                                                                              |                  |                   |            |       |  |

|              | TMC013       | TMC012        |                   | Operatio                                                                                                                     | n enable of 16-b | oit timer/event c | counter 01 |       |  |

|              | 0            | 0             |                   | Disables 16-bit timer/event counter 01 operation. Stops supplying operating clock.<br>Clears 16-bit timer counter 01 (TM01). |                  |                   |            |       |  |

|              | 0            | 1             | Free-running      | Free-running timer mode                                                                                                      |                  |                   |            |       |  |

|              | 1            | 0             | Clear & start     | Clear & start mode entered by TI001 pin valid edge input <sup>Note</sup>                                                     |                  |                   |            |       |  |

|              | 1            | 1             | Clear & start     | mode entered                                                                                                                 | upon a match b   | etween TM01       | and CR001  |       |  |

|              |              |               |                   |                                                                                                                              |                  |                   |            |       |  |

|              | TMC011       |               |                   | Condition to                                                                                                                 | reverse timer o  | utput (TO01)      |            |       |  |

|              | 0            | Match betw    | veen TM01 and     | CR001 or ma                                                                                                                  | tch between TM   | 01 and CR011      |            |       |  |

|              | 1            | Match betw    | veen TM01 and     | CR001 or ma                                                                                                                  | tch between TM   | 01 and CR011      |            |       |  |

|              |              | Trigger input | ut of TI001 pin v | valid edge                                                                                                                   |                  |                   |            |       |  |

|              |              | -             |                   |                                                                                                                              |                  |                   |            |       |  |

|              | OVF01        |               |                   | Т                                                                                                                            | M01 overflow fla | ag                |            |       |  |

|              | Clear (0)    | Clears OVF0   | 1 to 0 or TMC0    | 13 and TMC0                                                                                                                  | 12 = 00          |                   |            |       |  |

|              | Set (1)      | Overflow occ  | urs.              |                                                                                                                              |                  |                   |            |       |  |

# Figure 7-7. Format of 16-Bit Timer Mode Control Register 01 (TMC01)

OVF01 is set to 1 when the value of TM01 changes from FFFFH to 0000H in all the operation modes (free-running timer mode, clear & start mode entered by Tl001 pin valid edge input, and clear & start mode entered upon a match between TM01 and CR001). It can also be set to 1 by writing 1 to OVF01.

Note The TI001 pin valid edge is set by bits 5 and 4 (ES011, ES010) of prescaler mode register 01 (PRM01).

#### (7) 8-bit A/D conversion result register (ADCRH)

The A/D conversion result is loaded from the successive approximation register to this register each time A/D conversion is completed, and the ADCRH register stores the higher 8 bits of the A/D conversion result.

# Caution When data is read from ADCR and ADCRH, a wait cycle is generated. Do not read data from ADCR and ADCRH when the peripheral hardware clock (fPRs) is stopped. For details, see CHAPTER 36 CAUTIONS FOR WAIT.

#### (8) Controller

This circuit controls the conversion time of an input analog signal that is to be converted into a digital signal, as well as starting and stopping of the conversion operation. When A/D conversion has been completed, this controller generates INTAD.

#### (9) AVREF pin

This pin inputs an analog power/reference voltage to the A/D converter. Make this pin the same potential as the V<sub>DD</sub> pin when port 2 is used as a digital port.

The signal input to ANI0 to ANI7 is converted into a digital signal, based on the voltage applied across  $AV_{REF}$  and  $AV_{SS}$ .

#### (10) AVss pin

This is the ground potential pin of the A/D converter. Always use this pin at the same potential as that of the Vss pin even when the A/D converter is not used.

#### (11) A/D converter mode register (ADM)

This register is used to set the conversion time of the analog input signal to be converted, and to start or stop the conversion operation.

#### (12) A/D port configuration register (ADPC)

This register switches the ANI0/P20 to ANI7/P27 pins to analog input of A/D converter or digital I/O of port.

#### (13) Analog input channel specification register (ADS)

This register is used to specify the port that inputs the analog voltage to be converted into a digital signal.

#### (14) Port mode register 2 (PM2)

This register switches the ANI0/P20 to ANI7/P27 pins to input or output.

Remark ANI0 to ANI3: 78K0/KB2

ANI0 to ANI5: 38-pin products of the 78K0/KC2 ANI0 to ANI7: Products other than above

#### (2) Asynchronous serial interface reception error status register 0 (ASIS0)

This register indicates an error status on completion of reception by serial interface UARTO. It includes three error flag bits (PE0, FE0, OVE0).

This register is read-only by an 8-bit memory manipulation instruction.

Reset signal generation, or clearing bit 7 (POWER0) or bit 5 (RXE0) of ASIM0 to 0 clears this register to 00H. 00H is read when this register is read. If a reception error occurs, read ASIS0 and then read receive buffer register 0 (RXB0) to clear the error flag.

#### Figure 14-3. Format of Asynchronous Serial Interface Reception Error Status Register 0 (ASIS0)

#### Address: FF73H After reset: 00H R

| Symbol | 7 | 6 | 5 | 4 | 3 | 2   | 1   | 0    |

|--------|---|---|---|---|---|-----|-----|------|

| ASIS0  | 0 | 0 | 0 | 0 | 0 | PE0 | FE0 | OVE0 |

| PE0 | Status flag indicating parity error                                                      |

|-----|------------------------------------------------------------------------------------------|

| 0   | If POWER0 = 0 or RXE0 = 0, or if ASIS0 register is read.                                 |

| 1   | If the parity of transmit data does not match the parity bit on completion of reception. |

| FE0 | Status flag indicating framing error                        |  |  |  |

|-----|-------------------------------------------------------------|--|--|--|

| 0   | If POWER0 = 0 or RXE0 = 0, or if ASIS0 register is read.    |  |  |  |

| 1   | If the stop bit is not detected on completion of reception. |  |  |  |

| OVE0 | Status flag indicating overrun error                                                                               |

|------|--------------------------------------------------------------------------------------------------------------------|

| 0    | If POWER0 = 0 and RXE0 = 0, or if ASIS0 register is read.                                                          |

| 1    | If receive data is set to the RXB0 register and the next reception operation is completed before the data is read. |

Cautions 1. The operation of the PE0 bit differs depending on the set values of the PS01 and PS00 bits of asynchronous serial interface operation mode register 0 (ASIM0).

- 2. Only the first bit of the receive data is checked as the stop bit, regardless of the number of stop bits.

- 3. If an overrun error occurs, the next receive data is not written to receive buffer register 0 (RXB0) but discarded.

- 4. If data is read from ASIS0, a wait cycle is generated. Do not read data from ASIS0 when the peripheral hardware clock (fprs) is stopped. For details, see CHAPTER 36 CAUTIONS FOR WAIT.

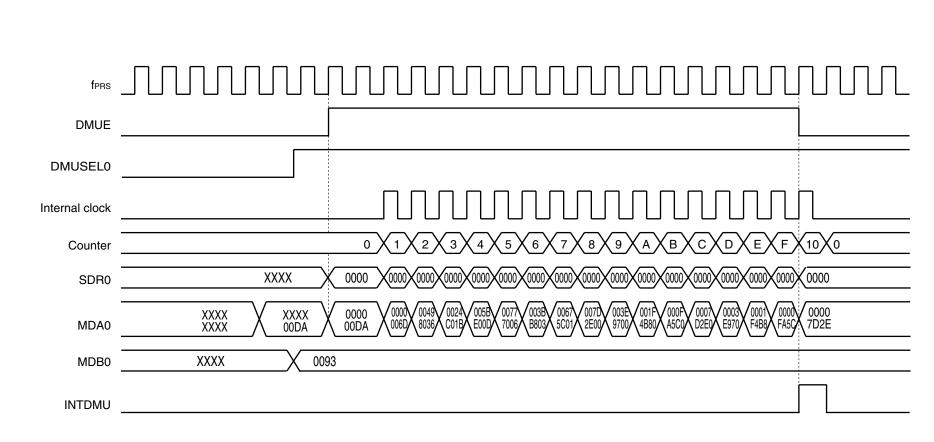

Figure 19-6. Timing Chart of Multiplication Operation (00DAH × 0093H)

R01UH0008EJ0401 Rev.4.01 Jul 15, 2010 78K0/Kx2

627

- Cautions 1. To use the peripheral hardware that stops operation in the STOP mode, and the peripheral hardware for which the clock that stops oscillating in the STOP mode after the STOP mode is released, restart the peripheral hardware.

- 2. Even if "internal low-speed oscillator can be stopped by software" is selected by the option byte, the internal low-speed oscillation clock continues in the STOP mode in the status before the STOP mode is set. To stop the internal low-speed oscillator's oscillation in the STOP mode, stop it by software and then execute the STOP instruction.

- 3. To shorten oscillation stabilization time after the STOP mode is released when the CPU operates with the high-speed system clock (X1 oscillation), switch the CPU clock to the internal high-speed oscillation clock before the execution of the STOP instruction using the following procedure.

<1> Set RSTOP to 0 (starting oscillation of the internal high-speed oscillator)  $\rightarrow$  <2> Set MCM0 to 0 (switching the CPU from X1 oscillation to internal high-speed oscillation)  $\rightarrow$  <3> Check that MCS is 0 (checking the CPU clock)  $\rightarrow$  <4> Check that RSTS is 1 (checking internal high-speed oscillation operation)  $\rightarrow$  <5> Execute the STOP instruction

Before changing the CPU clock from the internal high-speed oscillation clock to the high-speed system clock (X1 oscillation) after the STOP mode is released, check the oscillation stabilization time with the oscillation stabilization time counter status register (OSTC).

- 4. If the STOP instruction is executed when AMPH = 1, supply of the CPU clock is stopped for 4.06 to 16.12  $\mu$ s after the STOP mode is released when the internal high-speed oscillation clock is selected as the CPU clock, or for the duration of 160 external clocks when the high-speed system clock (external clock input) is selected as the CPU clock.

- 5. Execute the STOP instruction after having confirmed that the internal high-speed oscillator is operating stably (RSTS = 1).

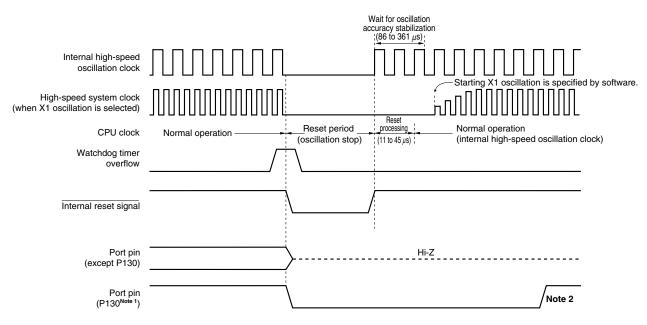

#### Figure 23-3. Timing of Reset Due to Watchdog Timer Overflow

- **Notes 1.** P130 pin is not mounted onto 78K0/KB2, and 38-pin and 44-pin products of the 78K0/KC2.

- 2. Set P130 to high-level output by software.

#### Caution A watchdog timer internal reset resets the watchdog timer.

**Remark** When reset is effected, P130 outputs a low level. If P130 is set to output a high level before reset is effected, the output signal of P130 can be dummy-output as the CPU reset signal.

# Table 27-12. Processing Time for Each Command When PG-FP4 or PG-FP5 Is Used (Reference) (2/2)

| Command of Port: CSI-Internal-OSC<br>PG-FP4 (Internal high-speed oscillation<br>clock (f <sub>RH</sub> )),<br>Speed: 2.5 MHz | (Internal high-speed oscillation | Port: UART-Ext-FP4CK (External main system clock (fexclk)),<br>Speed: 115,200 bps |               |  |  |

|------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------|---------------|--|--|

|                                                                                                                              | Frequency: 2.0 MHz               | Frequency: 20 MHz                                                                 |               |  |  |

| Signature                                                                                                                    | 0.5 s (TYP.)                     | 0.5 s (TYP.)                                                                      | 0.5 s (TYP.)  |  |  |

| Blankcheck                                                                                                                   | 1 s (TYP.)                       | 1 s (TYP.)                                                                        | 1 s (TYP.)    |  |  |

| Erase                                                                                                                        | 1.5 s (TYP.)                     | 1.5 s (TYP.)                                                                      | 1.5 s (TYP.)  |  |  |

| Program                                                                                                                      | 9.5 s (TYP.)                     | 18 s (TYP.)                                                                       | 18 s (TYP.)   |  |  |

| Verify                                                                                                                       | 4.5 s (TYP.)                     | 13.5 s (TYP.)                                                                     | 13.5 s (TYP.) |  |  |

| E.P.V                                                                                                                        | 11 s (TYP.)                      | 19.5 s (TYP.)                                                                     | 19.5 s (TYP.) |  |  |

| Checksum                                                                                                                     | 1 s (TYP.)                       | 1 s (TYP.)                                                                        | 1 s (TYP.)    |  |  |

| Security                                                                                                                     | 0.5 s (TYP.)                     | 0.5 s (TYP.)                                                                      | 0.5 s (TYP.)  |  |  |

(3) Products with internal ROMs of the 128 KB

Caution When executing boot swapping, do not use the E.P.V. command with the dedicated flash memory programmer.

# Caution The pins mounted depend on the product. Refer to Caution at the beginning of this chapter.

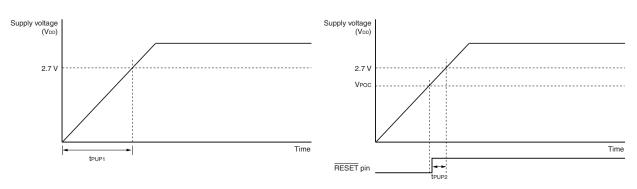

#### Supply Voltage Rise Time (T<sub>A</sub> = -40 to +110°C, Vss = EVss = 0 V)

| Parameter                                                                                                                                         | Symbol        | Conditions                                                                           | MIN. | TYP. | MAX. | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------------|------|------|------|------|

| Maximum time to rise to 2.7 V (V_{DD} (MIN.)) (V_{DD}: 0 V $\rightarrow$ 2.7 V)                                                                   | <b>t</b> pup1 | POCMODE (option byte) = 0,<br>when $\overrightarrow{\text{RESET}}$ input is not used |      |      | 3.6  | ms   |

| Maximum time to rise to 2.7 V (V <sub>DD</sub> (MIN.))<br>(releasing $\overrightarrow{\text{RESET}}$ input $\rightarrow$ V <sub>DD</sub> : 2.7 V) | tpup2         | POCMODE (option byte) = 0,<br>when RESET input is used                               |      |      | 1.9  | ms   |

#### Supply Voltage Rise Time Timing

$\bullet$  When  $\overline{\text{RESET}}$  pin input is not used

#### • When $\overline{\text{RESET}}$ pin input is used

# Caution The pins mounted depend on the product. Refer to Caution at the beginning of this chapter.

## 2.7 V POC Circuit Characteristics (T<sub>A</sub> = -40 to +125°C, Vss = EVss = 0 V)

| Parameter                                  | Symbol | Conditions               | MIN. | TYP. | MAX. | Unit |

|--------------------------------------------|--------|--------------------------|------|------|------|------|

| Detection voltage on application of supply | VDDPOC | POCMODE (option bye) = 1 | 2.50 | 2.70 | 2.90 | V    |

| voltage                                    |        |                          |      |      |      |      |

#### **Remark** The operations of the POC circuit are as described below, depending on the POCMODE (option byte) setting.

| Option Byte Setting | POC Mode                    | Operation                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POCMODE = 0         | 1.59 V mode operation       | A reset state is retained until V <sub>POC</sub> = 1.59 V (TYP.) is reached<br>after the power is turned on, and the reset is released when<br>V <sub>POC</sub> is exceeded. After that, POC detection is performed at<br>V <sub>POC</sub> , similarly as when the power was turned on.<br>The power supply voltage must be raised at a time of t <sub>PUP1</sub> or<br>t <sub>PUP2</sub> when POCMODE is 0.                           |

| POCMODE = 1         | 2.7 V/1.59 V mode operation | A reset state is retained until VDDPOC = 2.7 V (TYP.) is<br>reached after the power is turned on, and the reset is<br>released when VDDPOC is exceeded. After that, POC detection<br>is performed at VPOC = $1.59$ V (TYP.) and not at VDDPOC.<br>The use of the 2.7 V/1.59 V POC mode is recommended<br>when the rise of the voltage, after the power is turned on and<br>until the voltage reaches 1.8 V, is more relaxed than tPTH. |

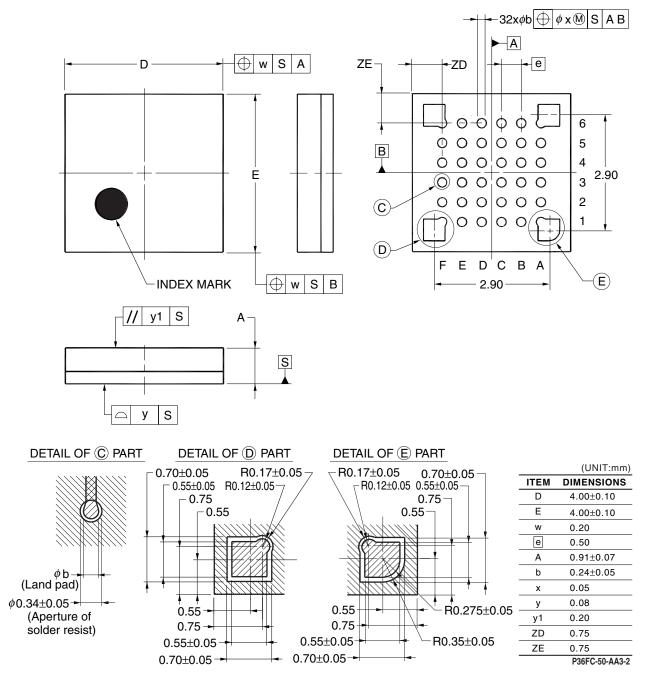

- μPD78F0500FC-AA3-A, 78F0501FC-AA3-A, 78F0502FC-AA3-A, 78F0503FC-AA3-A, 78F0503DFC-AA3-A

- μPD78F0500AFC-AA3-A, 78F0501AFC-AA3-A, 78F0502AFC-AA3-A, 78F0503AFC-AA3-A, 78F0503DAFC-AA3-A

# 36-PIN PLASTIC FLGA (4x4)

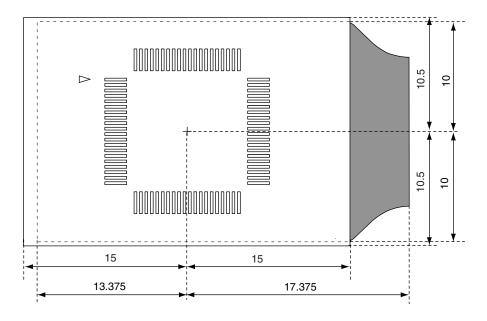

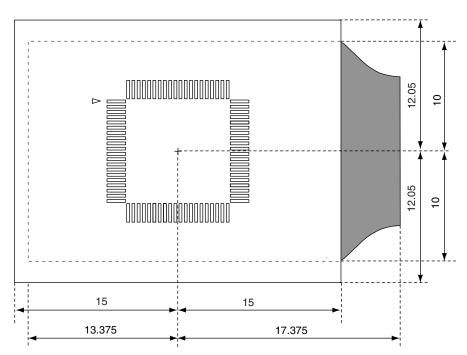

Figure B-10. For 64-Pin GK Package

Exchange adapter area: Components up to 17.45 mm in height can be mounted<sup>Note</sup>

Emulation probe tip area: Components up to 24.45 mm in height can be mounted<sup>Note</sup>

Note Height can be adjusted by using space adapters (each adds 2.4 mm)

Exchange adapter area: Components up to 17.45 mm in height can be mounted<sup>Note</sup>

Emulation probe tip area: Components up to 24.45 mm in height can be mounted<sup>Note</sup>

Note Height can be adjusted by using space adapters (each adds 2.4 mm)

|             |                          | (4/4)                                                                                         |

|-------------|--------------------------|-----------------------------------------------------------------------------------------------|

| Edition     | Description              | Chapter                                                                                       |

| 3rd Edition | Revision of this chapter | CHAPTER 30<br>ELECTRICAL<br>SPECIFICATIONS<br>(STANDARD<br>PRODUCTS)                          |

|             | Revision of this chapter | CHAPTER 31<br>ELECTRICAL<br>SPECIFICATIONS ((A)<br>GRADE PRODUCTS)                            |

|             | Addition of this chapter | CHAPTER 32<br>ELECTRICAL<br>SPECIFICATIONS<br>((A2) GRADE<br>PRODUCTS: TA = -40<br>to +110°C) |

|             | Addition of this chapter | CHAPTER 33<br>ELECTRICAL<br>SPECIFICATIONS<br>((A2) GRADE<br>PRODUCTS: TA = -40<br>to +125°C) |

|             | Revision of this chapter | CHAPTER 35<br>RECOMMENDED<br>SOLDERING<br>CONDITIONS                                          |

|             | Revision of this chapter | APPENDIX A<br>DEVELOPMENT<br>TOOLS                                                            |

|             | Addition of this chapter | APPENDIX E<br>REVISION HISTORY                                                                |