# E·XF Renesas Electronics America Inc - <u>UPD78F0537AFC-AA1-A Datasheet</u>

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 20MHz                                                                                |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                                   |

| Number of I/O              | 55                                                                                   |

| Program Memory Size        | 128KB (128K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 7K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 8x10b                                                                            |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 64-VFLGA                                                                             |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0537afc-aa1-a |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Documents Related to Development Tools (Software)**

| Document Nam                                              | Document No.                 |                  |

|-----------------------------------------------------------|------------------------------|------------------|

| RA78K0 Ver.3.80 Assembler Package                         | Operation                    | U17199E          |

| User's Manual <sup>Note 1</sup>                           | Language                     | U17198E          |

|                                                           | Structured Assembly Language | U17197E          |

| 78K0 Assembler Package RA78K0 Ver.4.01 Operating Precau   | ZUD-CD-07-0181-E             |                  |

| CC78K0 Ver.3.70 C Compiler                                | Operation                    | U17201E          |

| User's Manual <sup>Note 2</sup>                           | Language                     | U17200E          |

| 78K0 C Compiler CC78K0 Ver. 4.00 Operating Precautions (N | otification Document) Note 2 | ZUD-CD-07-0103-E |

| SM+ System Simulator                                      | Operation                    | U18601E          |

| User's Manual                                             | User Open Interface          | U18212E          |

| ID78K0-QB Ver.2.94 Integrated Debugger User's Manual      | Operation                    | U18330E          |

| ID78K0-QB Ver.3.00 Integrated Debugger User's Manual      | Operation                    | U18492E          |

| PM plus Ver.5.20 <sup>Note 3</sup> User's Manual          | U16934E                      |                  |

| PM+ Ver.6.30 <sup>Note 4</sup> User's Manual              |                              | U18416E          |

**Notes 1.** This document is installed into the PC together with the tool when installing RA78K0 Ver. 4.01. For descriptions not included in "78K0 Assembler Package RA78K0 Ver. 4.01 Operating Precautions", refer to the user's manual of RA78K0 Ver. 3.80.

- This document is installed into the PC together with the tool when installing CC78K0 Ver. 4.00. For descriptions not included in "78K0 C Compiler CC78K0 Ver. 4.00 Operating Precautions", refer to the user's manual of CC78K0 Ver. 3.70.

- 3. PM plus Ver. 5.20 is the integrated development environment included with RA78K0 Ver. 3.80.

- **4.** PM+ Ver. 6.30 is the integrated development environment included with RA78K0 Ver. 4.01. Software tool (assembler, C compiler, debugger, and simulator) products of different versions can be managed.

#### **Other Documents**

| Document Name                                                                      | Document No. |

|------------------------------------------------------------------------------------|--------------|

| SEMICONDUCTOR SELECTION GUIDE - Products and Packages -                            | X13769X      |

| Semiconductor Device Mount Manual                                                  | Note         |

| Quality Grades on NEC Semiconductor Devices                                        | C11531E      |

| NEC Semiconductor Device Reliability/Quality Control System                        | C10983E      |

| Guide to Prevent Damage for Semiconductor Devices by Electrostatic Discharge (ESD) | C11892E      |

Note See the "Semiconductor Device Mount Manual" website (http://www2.renesas.com/pkg/en/mount/index.html).

# Caution The related documents listed above are subject to change without notice. Be sure to use the latest version of each document when designing.

All trademarks and registered trademarks are the property of their respective owners.

EEPROM is a trademark of Renesas Electronics Corporation.

Windows is a registered trademark or trademark of Microsoft Corporation in the United States and/or other countries. SuperFlash is a registered trademark of Silicon Storage Technology, Inc. in several countries including the United States and Japan.

Caution: This product uses SuperFlash® technology licensed from Silicon Storage Technology, Inc.

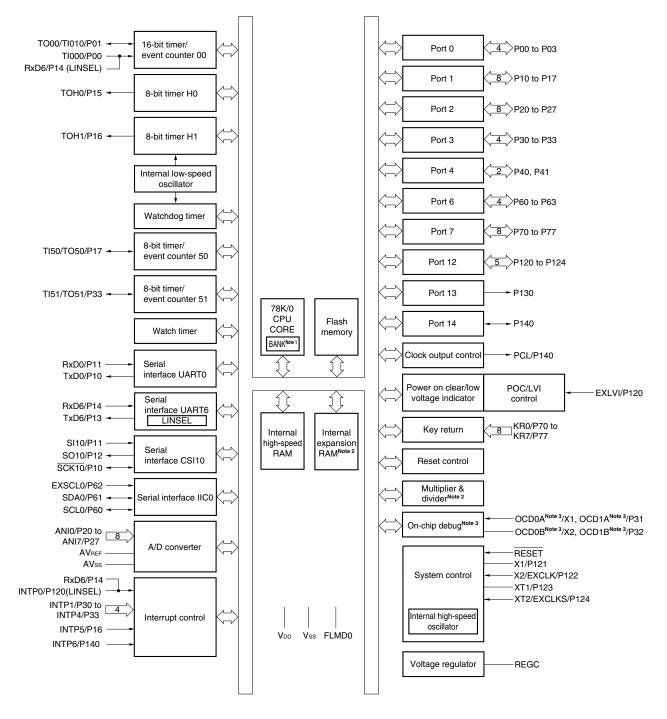

#### 1.7.3 78K0/KD2

- 2. Available only in the products whose flash memory is at least 48 KB.

- 3. Available only in the products with on-chip debug function.

Caution 2. Process the P31/INTP2/OCD1A pin of the products mounted with the on-chip debug function (μPD78F05xxD and 78F05xxDA) as follows, when it is not used when it is connected to a flash memory programmer or an on-chip debug emulator.

|                                                                                         |                       | P31/INTP2/OCD1A                                                                                                                  |

|-----------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Flash memory program                                                                    | mer connection        | Connect to EVss <sup>Note</sup> via a resistor.                                                                                  |

| On-chip debug                                                                           | During reset          |                                                                                                                                  |

| emulator connection<br>(when it is not used<br>as an on-chip debug<br>mode setting pin) | During reset released | Input: Connect to EV <sub>DD</sub> <sup>Note</sup> or EV <sub>SS</sub> <sup>Note</sup><br>via a resistor.<br>Output: Leave open. |

- Note With products without an EVss pin, connect them to Vss. With products without an EVbb pin, connect them to Vbb.

- Remark P31 and P32 of the product with an on-chip debug function (μPD78F05xxD and 78F05xxDA) can be used as on-chip debug mode setting pins (OCD1A and OCD1B) when the on-chip debug function is used. For how to connect an on-chip debug emulator (QB-MINI2), see CHAPTER 28 ON-CHIP DEBUG FUNCTION (μPD78F05xxD and 78F05xxDA ONLY).

#### 2.2.5 P40 to P47 (port 4)

P40 to P47 function as an I/O port. P40 to P47 can be set to input or output port in 1-bit units using port mode register 4 (PM4). Use of an on-chip pull-up resistor can be specified by pull-up resistor option register 4 (PU4).

|     | 78K0/KB2 | 78K0/KC2         | 78K0/KD2     | 78K0                                                       | /KE2                                                      | 78K0/KF2     |

|-----|----------|------------------|--------------|------------------------------------------------------------|-----------------------------------------------------------|--------------|

|     |          |                  |              | Products<br>whose flash<br>memory is<br>less than<br>32 KB | Products<br>whose flash<br>memory is at<br>least<br>48 KB |              |

| P40 | _        | $\sqrt{Note}$ $$ |              |                                                            |                                                           | $\checkmark$ |

| P41 | _        | $\sqrt{^{Note}}$ | $\checkmark$ | V                                                          |                                                           | $\checkmark$ |

| P42 | -        | -                | _            | V                                                          |                                                           | $\checkmark$ |

| P43 | -        | -                | _            | V                                                          |                                                           | $\checkmark$ |

| P44 | -        | -                | -            |                                                            | _                                                         |              |

| P45 | _        | -                |              | =                                                          |                                                           |              |

| P46 | _        | -                |              | -                                                          |                                                           |              |

| P47 | _        |                  | -            | -                                                          |                                                           |              |

**Note** This is not mounted onto 38-pin products of the 78K0/KC2. For the 38-pin products, be sure to set bits 0 and 1 of PM4 and P4 to "0".

**Remark**  $\sqrt{:}$  Mounted, -: Not mounted

### 3.1.1 Internal program memory space

The internal program memory space stores the program and table data. Normally, it is addressed with the program counter (PC).

78K0/Kx2 microcontrollers incorporate internal ROM (flash memory), as shown below.

|                           |                           |                           | 1                                                    |                                                      | 1                                                    |                                                                                                           |

|---------------------------|---------------------------|---------------------------|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 78K0/KB2                  | 78K0                      | 78K0/KC2                  |                                                      | 78K0/KE2                                             | 78K0/KF2                                             | Internal ROM                                                                                              |

| 30/36 Pins                | 38/44 Pins                | 48 Pins                   | 52 Pins                                              | 64 Pins                                              | 80 Pins                                              | (Flash memory)                                                                                            |

| μPD78F0500,<br>PD78F0500A | _                         | _                         | _                                                    | _                                                    | _                                                    | 8192 × 8 bits<br>(0000H to 1FFFH)                                                                         |

| μPD78F0501,<br>78F0501A   | μPD78F0511,<br>78F0511A   | μ PD78F0511,<br>78F0511A  | μPD78F0521,<br>78F0521A                              | μPD78F0531,<br>78F0531A                              | _                                                    | 16384 × 8 bits<br>(0000H to 3FFFH)                                                                        |

| μPD78F0502,<br>78F0502A   | μPD78F0512,<br>78F0512A   | μPD78F0512,<br>78F0512A   | μ PD78F0522,<br>78F0522A                             | μΡD78F0532,<br>78F0532A                              | _                                                    | 24576 × 8 bits<br>(0000H to 5FFFH)                                                                        |

| μPD78F0503D,<br>78F0503DA | μPD78F0513D,<br>78F0513DA | μPD78F0513,<br>78F0513A   | μPD78F0523,<br>78F0523A                              | μPD78F0533,<br>78F0533A                              | -                                                    | 32768 × 8 bits<br>(0000H to 7FFFH)                                                                        |

| μPD78F0503,<br>78F0503A   | μ PD78F0513,<br>78F0513A  |                           |                                                      |                                                      |                                                      |                                                                                                           |

| -                         | -                         | μPD78F0514,<br>78F0514A   | μPD78F0524,<br>78F0524A                              | μPD78F0534,<br>78F0534A                              | μPD78F0544,<br>78F0544A                              | 49152 × 8 bits<br>(0000H to BFFFH)                                                                        |

| _                         | _                         | μPD78F0515D,<br>78F0515DA | μPD78F0525,<br>78F0525A                              | μΡD78F0535,<br>78F0535A                              | μPD78F0545,<br>78F0545A                              | 61440 × 8 bits<br>(0000H to EFFFH)                                                                        |

|                           |                           | μPD78F0515,<br>78F0515A   |                                                      |                                                      |                                                      |                                                                                                           |

| _                         | _                         | _                         | μPD78F0526,<br>78F0526A                              | μPD78F0536,<br>78F0536A                              | μΡD78F0546,<br>78F0546A                              | 98304 × 8 bits<br>(0000H to 7FFFH<br>(common area: 32 KB)<br>+ 8000H to BFFFH<br>(bank area: 16 KB) × 4)  |

| _                         | _                         | _                         | μΡD78F0527D,<br>78F0527DA<br>μΡD78F0527,<br>78F0527A | μPD78F0537D,<br>78F0537DA<br>μPD78F0537,<br>78F0537A | μΡD78F0547D,<br>78F0547DA<br>μΡD78F0547,<br>78F0547A | 131072 × 8 bits<br>(0000H to 7FFFH<br>(common area: 32 KB)<br>+ 8000H to BFFFH<br>(bank area: 16 KB) × 6) |

| Table 3-4. | Internal | ROM | Capacity |

|------------|----------|-----|----------|

|------------|----------|-----|----------|

The internal program memory space is divided into the following areas.

#### (1) Vector table area

The 64-byte area 0000H to 003FH is reserved as a vector table area. The program start addresses for branch upon reset or generation of each interrupt request are stored in the vector table area.

Of the 16-bit address, the lower 8 bits are stored at even addresses and the higher 8 bits are stored at odd addresses.

#### (d) Auxiliary carry flag (AC)

If the operation result has a carry from bit 3 or a borrow at bit 3, this flag is set (1). It is reset (0) in all other cases.

#### (e) In-service priority flag (ISP)

This flag manages the priority of acknowledgeable maskable vectored interrupts. When this flag is 0, low-level vectored interrupt requests specified by a priority specification flag register (PR0L, PR0H, PR1L, PR1H) (see **20.3 (3) Priority specification flag registers (PR0L, PR0H, PR1L, PR1H)**) can not be acknowledged. Actual request acknowledgment is controlled by the interrupt enable flag (IE).

#### (f) Carry flag (CY)

This flag stores overflow and underflow upon add/subtract instruction execution. It stores the shift-out value upon rotate instruction execution and functions as a bit accumulator during bit operation instruction execution.

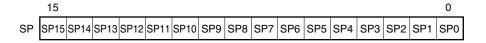

#### (3) Stack pointer (SP)

This is a 16-bit register to hold the start address of the memory stack area. Only the internal high-speed RAM area can be set as the stack area.

#### Figure 3-22. Format of Stack Pointer

The SP is decremented ahead of write (save) to the stack memory and is incremented after read (restored) from the stack memory.

Each stack operation saves/restores data as shown in Figures 3-23 and 3-24.

# Caution Since reset signal generation makes the SP contents undefined, be sure to initialize the SP before using the stack.

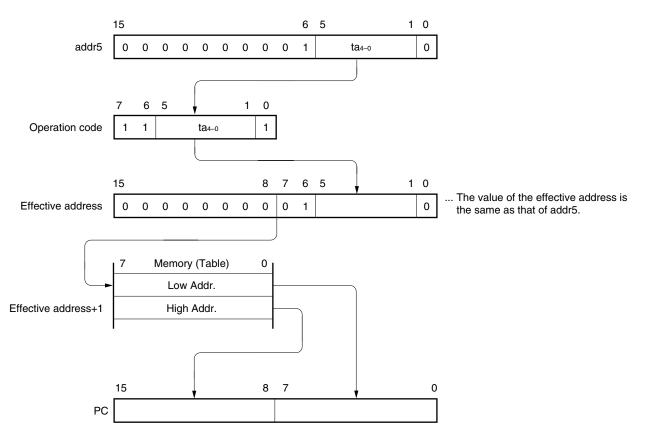

#### 3.3.3 Table indirect addressing

#### [Function]

Table contents (branch destination address) of the particular location to be addressed by bits 1 to 5 of the immediate data of an operation code are transferred to the program counter (PC) and branched.

This function is carried out when the CALLT [addr5] instruction is executed.

This instruction references the address that is indicated by addr5 and is stored in the memory table from 0040H to 007FH, and allows branching to the entire memory space.

## [Illustration]

### (2) Port registers (Pxx)

These registers write the data that is output from the chip when data is output from a port.

If the data is read in the input mode, the pin level is read. If it is read in the output mode, the output latch value is read.

These registers can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears these registers to 00H.

| Symbol | 7   | 6   | 5   | 4   | 3   | 2                    | 1                    | 0    | Address | After reset        | R/W |

|--------|-----|-----|-----|-----|-----|----------------------|----------------------|------|---------|--------------------|-----|

| P0     | 0   | 0   | 0   | 0   | 0   | 0                    | P01                  | P00  | FF00H   | 00H (output latch) | R/W |

|        |     |     |     |     |     |                      |                      |      |         |                    |     |

| P1     | P17 | P16 | P15 | P14 | P13 | P12                  | P11                  | P10  | FF01H   | 00H (output latch) | R/W |

|        |     |     |     |     |     | 1                    |                      |      | 1       |                    |     |

| P2     | 0   | 0   | 0   | 0   | P23 | P22                  | P21                  | P20  | FF02H   | 00H (output latch) | R/W |

| _      |     | -   | -   | -   |     |                      |                      |      | 1       |                    |     |

| P3     | 0   | 0   | 0   | 0   | P33 | P32                  | P31                  | P30  | FF03H   | 00H (output latch) | R/W |

|        |     |     |     | 0   |     |                      | Det                  |      | 1       |                    |     |

| P6     | 0   | 0   | 0   | 0   | 0   | 0                    | P61                  | P60  | FF06H   | 00H (output latch) | R/W |

| Dio    |     | 0   | 0   | 0   | 0   | D 4 00 Note          |                      | Diag |         |                    | DAA |

| P12    | 0   | 0   | 0   | 0   | 0   | P122 <sup>Note</sup> | P121 <sup>Note</sup> | P120 | FF0CH   | 00H (output latch) | R/W |

|        |     |     |     |     |     |                      |                      |      |         |                    |     |

#### Figure 5-34. Format of Port Register (78K0/KB2)

| Pmn | m = 0 to 3, 6, 12; n = 0 to 7        |                                 |  |  |  |  |  |

|-----|--------------------------------------|---------------------------------|--|--|--|--|--|

|     | Output data control (in output mode) | Input data read (in input mode) |  |  |  |  |  |

| 0   | Output 0                             | Input low level                 |  |  |  |  |  |

| 1   | Output 1                             | Input high level                |  |  |  |  |  |

Note "0" is always read from the output latch of P121 and P122 if the pin is in the external clock input mode.

| Address: FF | BBH After | reset: 00H | R/W                            |             |           |              |                     |                          |

|-------------|-----------|------------|--------------------------------|-------------|-----------|--------------|---------------------|--------------------------|

| Symbol      | 7         | 6          | 5                              | 4           | 3         | 2            | 1                   | 0                        |

| PRM00       | ES101     | ES100      | ES001                          | ES000       | 0         | 0            | PRM00 <sup>-</sup>  | 1 PRM000                 |

|             |           |            |                                |             |           |              |                     |                          |

|             | ES101     | ES100      |                                | TIO         | 10 pin va | alid edge se | election            |                          |

|             | 0         | 0          | Falling edge                   |             |           |              |                     |                          |

|             | 0         | 1          | Rising edge                    |             |           |              |                     |                          |

|             | 1         | 0          | Setting prohi                  | bited       |           |              |                     |                          |

|             | 1         | 1          | Both falling and rising edges  |             |           |              |                     |                          |

|             |           |            |                                |             |           |              |                     |                          |

|             | ES001     | ES000      | TI000 pin valid edge selection |             |           |              |                     |                          |

|             | 0         | 0          | Falling edge                   |             |           |              |                     |                          |

|             | 0         | 1          | Rising edge                    |             |           |              |                     |                          |

|             | 1         | 0          | Setting prohibited             |             |           |              |                     |                          |

|             | 1         | 1          | Both falling and rising edges  |             |           |              |                     |                          |

|             |           |            |                                |             |           |              |                     |                          |

|             | PRM001    | PRM000     |                                |             | Count clo | ck selectio  | n <sup>Note 1</sup> |                          |

|             |           |            |                                | fprs = 2 MH | Iz fprs   | = 5 MHz      | fprs = 10 MHz       | fprs = 20 MHz            |

|             | 0         | 0          | fprs <sup>Note 2</sup>         | 2 MHz       | 5 MI      | Hz           | 10 MHz              | 20 MHz <sup>Note 3</sup> |

|             | 0         | 1          | fprs/2 <sup>2</sup>            | 500 kHz     | 1.25      | MHz          | 2.5 MHz             | 5 MHz                    |

#### Figure 7-13. Format of Prescaler Mode Register 00 (PRM00)

| Notes 1. | The frequency that can be used for the peripheral hardware clock (fprs) differs depending on the power |  |

|----------|--------------------------------------------------------------------------------------------------------|--|

|          | supply voltage and product specifications.                                                             |  |

7.81 kHz

| Supply Voltage                                                                                                               | Conventional-specification Products<br>(µPD78F05xx and 78F05xxD) | Expanded-specification Products (µPD78F05xxA and 78F05xxDA) |

|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------|

| $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                                                                                        | fprs ≤ 20 MHz                                                    | fprs ≤ 20 MHz                                               |

| $2.7~V \leq V_{\text{DD}} < 4.0~V$                                                                                           | $f_{PRS} \leq 10 \text{ MHz}$                                    |                                                             |

| $\begin{array}{l} 1.8 \ V \leq V_{DD} < 2.7 \ V \\ (Standard \ products \ and \\ (A) \ grade \ products \ only) \end{array}$ | fprs ≤ 5 MHz                                                     | fprs ≤ 5 MHz                                                |

19.53 kHz

39.06 kHz

78.12 kHz

(The values shown in the table above are those when fPRS = fXH (XSEL = 1).)

- 2. If the peripheral hardware clock (fPRs) operates on the internal high-speed oscillation clock (fRH) (XSEL = 0), when  $1.8 \text{ V} \le \text{V}_{\text{DD}} < 2.7 \text{ V}$ , the setting of PRM001 = PRM000 = 0 (count clock: fPRs) is prohibited.

- 3. This is settable only if 4.0 V  $\leq$  V\_{DD}  $\leq$  5.5 V.

0

1

1

1

fprs/2<sup>8</sup>

TI000 valid edge<sup>Notes 4, 5</sup>

- 4. The external clock from the TI000 pin requires a pulse longer than twice the cycle of the peripheral hardware clock (fPRs).

- 5. Do not start timer operation with the external clock from the TI000 pin when the internal high-speed oscillation clock and high-speed system clock are stopped while the CPU operates with the subsystem clock, or when in the STOP mode.

Remark fPRS: Peripheral hardware clock frequency

## CHAPTER 8 8-BIT TIMER/EVENT COUNTERS 50 AND 51

#### 8.1 Functions of 8-Bit Timer/Event Counters 50 and 51

8-bit timer/event counters 50 and 51 are mounted onto all 78K0/Kx2 microcontroller products.8-bit timer/event counters 50 and 51 have the following functions.

- Interval timer

- External event counter

- Square-wave output

- PWM output

#### 8.2 Configuration of 8-Bit Timer/Event Counters 50 and 51

8-bit timer/event counters 50 and 51 include the following hardware.

| Item              | Configuration                                                                                                                                                                                         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timer register    | 8-bit timer counter 5n (TM5n)                                                                                                                                                                         |

| Register          | 8-bit timer compare register 5n (CR5n)                                                                                                                                                                |

| Timer input       | TI5n                                                                                                                                                                                                  |

| Timer output      | TO5n                                                                                                                                                                                                  |

| Control registers | Timer clock selection register 5n (TCL5n)<br>8-bit timer mode control register 5n (TMC5n)<br>Port mode register 1 (PM1) or port mode register 3 (PM3)<br>Port register 1 (P1) or port register 3 (P3) |

#### Table 8-1. Configuration of 8-Bit Timer/Event Counters 50 and 51

Figures 8-1 and 8-2 show the block diagrams of 8-bit timer/event counters 50 and 51.

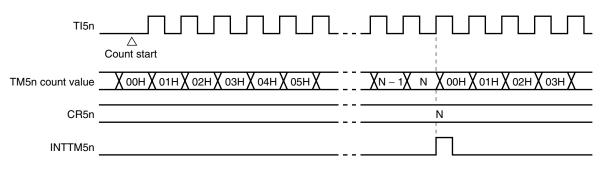

#### 8.4.2 Operation as external event counter

The external event counter counts the number of external clock pulses to be input to the TI5n pin by 8-bit timer counter 5n (TM5n).

TM5n is incremented each time the valid edge specified by timer clock selection register 5n (TCL5n) is input. Either the rising or falling edge can be selected.

When the TM5n count value matches the value of 8-bit timer compare register 5n (CR5n), TM5n is cleared to 0 and an interrupt request signal (INTTM5n) is generated.

Whenever the TM5n value matches the value of CR5n, INTTM5n is generated.

#### Setting

<1> Set each register.

- Set the port mode register (PM17 or PM33)<sup>Note</sup> to 1.

- TCL5n: Select TI5n pin input edge. TI5n pin falling edge  $\rightarrow$  TCL5n = 00H TI5n pin rising edge  $\rightarrow$  TCL5n = 01H

- CR5n: Compare value

- TMC5n: Stop the count operation, select the mode in which clear & start occurs on match of TM5n and CR5n, disable the timer F/F inversion operation, disable timer output. (TMC5n = 0000000B)

- <2> When TCE5n = 1 is set, the number of pulses input from the TI5n pin is counted.

- <3> When the values of TM5n and CR5n match, INTTM5n is generated (TM5n is cleared to 00H).

- <4> After these settings, INTTM5n is generated each time the values of TM5n and CR5n match.

- Note 8-bit timer/event counter 50: PM17 8-bit timer/event counter 51: PM33

**Remark** For how to enable the INTTM5n signal interrupt, see CHAPTER 20 INTERRUPT FUNCTIONS.

#### Figure 8-12. External Event Counter Operation Timing (with Rising Edge Specified)

**Remark** N = 00H to FFH n = 0, 1

## CHAPTER 15 SERIAL INTERFACE UART6

#### 15.1 Functions of Serial Interface UART6

Serial interface UART6 are mounted onto all 78K0/Kx2 microcontroller products. Serial interface UART6 has the following two modes.

#### (1) Operation stop mode

This mode is used when serial communication is not executed and can enable a reduction in the power consumption. For details, see **15.4.1 Operation stop mode**.

#### (2) Asynchronous serial interface (UART) mode

This mode supports the LIN (Local Interconnect Network)-bus. The functions of this mode are outlined below. For details, see **15.4.2** Asynchronous serial interface (UART) mode and **15.4.3** Dedicated baud rate generator.

- Maximum transfer rate: 625 kbps

- Two-pin configuration TxD6: Transmit data output pin

- RxD6: Receive data input pin

- Data length of communication data can be selected from 7 or 8 bits.

- Dedicated internal 8-bit baud rate generator allowing any baud rate to be set

- Transmission and reception can be performed independently (full duplex operation).

- MSB- or LSB-first communication selectable

- Inverted transmission operation

- Sync break field transmission from 13 to 20 bits

- More than 11 bits can be identified for sync break field reception (SBF reception flag provided).

- Cautions 1. The TxD6 output inversion function inverts only the transmission side and not the reception side. To use this function, the reception side must be ready for reception of inverted data.

- 2. If clock supply to serial interface UART6 is not stopped (e.g., in the HALT mode), normal operation continues. If clock supply to serial interface UART6 is stopped (e.g., in the STOP mode), each register stops operating, and holds the value immediately before clock supply was stopped. The TxD6 pin also holds the value immediately before clock supply was stopped and outputs it. However, the operation is not guaranteed after clock supply is resumed. Therefore, reset the circuit so that POWER6 = 0, RXE6 = 0, and TXE6 = 0.

- 3. Set POWER6 = 1 and then set TXE6 = 1 (transmission) or RXE6 = 1 (reception) to start communication.

- 4. TXE6 and RXE6 are synchronized by the base clock (fxcLK6) set by CKSR6. To enable transmission or reception again, set TXE6 or RXE6 to 1 at least two clocks of the base clock after TXE6 or RXE6 has been cleared to 0. If TXE6 or RXE6 is set within two clocks of the base clock, the transmission circuit or reception circuit may not be initialized.

- 5. Set transmit data to TXB6 at least one base clock (fxcLK6) after setting TXE6 = 1.

- 6. If data is continuously transmitted, the communication timing from the stop bit to the next start bit is extended two operating clocks of the macro. However, this does not affect the result of communication because the reception side initializes the timing when it has detected a start bit. Do not use the continuous transmission function if the interface is used in LIN communication operation.

#### (6) Asynchronous serial interface control register 6 (ASICL6)

This register controls the serial communication operations of serial interface UART6. ASICL6 can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation sets this register to 16H.

Caution ASICL6 can be refreshed (the same value is written) by software during a communication operation (when bits 7 and 6 (POWER6, TXE6) of ASIM6 = 1 or bits 7 and 5 (POWER6, RXE6) of ASIM6 = 1). However, do not set both SBRT6 and SBTT6 to 1 by a refresh operation during SBF reception (SBRT6 = 1) or SBF transmission (until INTST6 occurs since SBTT6 has been set (1)), because it may re-trigger SBF reception or SBF transmission.

Figure 15-10. Format of Asynchronous Serial Interface Control Register 6 (ASICL6) (1/2)

Address: FF58H After reset: 16H R/WNote

| Symbol | <7>   | <6>   | 5     | 4     | 3     | 2     | 1    | 0      |

|--------|-------|-------|-------|-------|-------|-------|------|--------|

| ASICL6 | SBRF6 | SBRT6 | SBTT6 | SBL62 | SBL61 | SBL60 | DIR6 | TXDLV6 |

| SBRF6 | SBF reception status flag                                                   |

|-------|-----------------------------------------------------------------------------|

| 0     | If POWER6 = 0 and RXE6 = 0 or if SBF reception has been completed correctly |

| 1     | SBF reception in progress                                                   |

| SBRT6 | SBF reception trigger |

|-------|-----------------------|

| 0     | _                     |

| 1     | SBF reception trigger |

| SBTT6 | SBF transmission trigger |

|-------|--------------------------|

| 0     | _                        |

| 1     | SBF transmission trigger |

Note Bit 7 is read-only.

#### (2) Communication operation

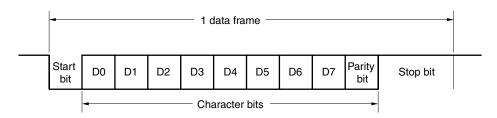

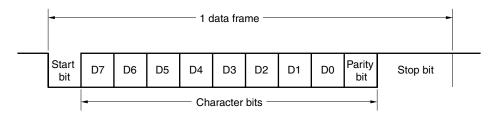

#### (a) Format and waveform example of normal transmit/receive data

Figures 15-13 and 15-14 show the format and waveform example of the normal transmit/receive data.

#### Figure 15-13. Format of Normal UART Transmit/Receive Data

#### 1. LSB-first transmission/reception

#### 2. MSB-first transmission/reception

One data frame consists of the following bits.

- Start bit ... 1 bit

- Character bits ... 7 or 8 bits

- Parity bit ... Even parity, odd parity, 0 parity, or no parity

- Stop bit ... 1 or 2 bits

The character bit length, parity, and stop bit length in one data frame are specified by asynchronous serial interface operation mode register 6 (ASIM6).

Whether data is communicated with the LSB or MSB first is specified by bit 1 (DIR6) of asynchronous serial interface control register 6 (ASICL6).

Whether the TxD6 pin outputs normal or inverted data is specified by bit 0 (TXDLV6) of ASICL6.

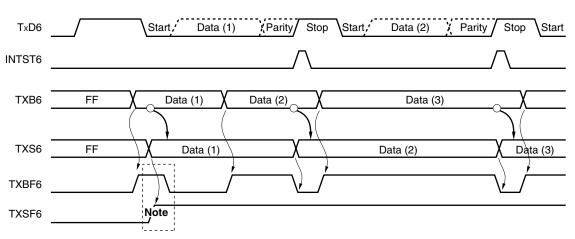

Figure 15-17 shows the timing of starting continuous transmission, and Figure 15-18 shows the timing of ending continuous transmission.

Figure 15-17. Timing of Starting Continuous Transmission

**Note** When ASIF6 is read, there is a period in which TXBF6 and TXSF6 = 1, 1. Therefore, judge whether writing is enabled using only the TXBF6 bit.

**Remark** TxD6: TxD6 pin (output)

INTST6: Interrupt request signal

TXB6: Transmit buffer register 6

TXS6: Transmit shift register 6

ASIF6: Asynchronous serial interface transmission status register 6

TXBF6: Bit 1 of ASIF6

TXSF6: Bit 0 of ASIF6

| HALT M                | ode Setting           | When HALT Instruction Is Executed Wh                                                                                                  | ile CPU Is Operating on Subsystem Clock                        |  |

|-----------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|

| Item                  |                       | When CPU Is Operating on XT1 Clock (fxr)                                                                                              | When CPU Is Operating on External<br>Subsystem Clock (fexclks) |  |

| System clock          |                       | Clock supply to the CPU is stopped                                                                                                    |                                                                |  |

| Main system clo       | ck fвн                | Status before HALT mode was set is retained                                                                                           |                                                                |  |

|                       | fx                    |                                                                                                                                       |                                                                |  |

|                       | <b>f</b> exclk        | Operates or stops by external clock input                                                                                             |                                                                |  |

| Subsystem clock       | <b>с</b> fхт          | Operation continues (cannot be stopped)                                                                                               | Status before HALT mode was set is retained                    |  |

|                       | <b>f</b> exclks       | Operates or stops by external clock input                                                                                             | Operation continues (cannot be stopped)                        |  |

| fr∟                   |                       | Status before HALT mode was set is retained                                                                                           |                                                                |  |

| CPU                   |                       | Operation stopped                                                                                                                     |                                                                |  |

| Flash memory          |                       |                                                                                                                                       |                                                                |  |

| RAM                   |                       | Status before HALT mode was set is retained                                                                                           |                                                                |  |

| Port (latch)          |                       |                                                                                                                                       |                                                                |  |

| 16-bit timer/event    | 00 <sup>Note</sup>    | Operable                                                                                                                              |                                                                |  |

| counter               | 01 <sup>Note</sup>    |                                                                                                                                       |                                                                |  |

| 8-bit timer/event     | 50 <sup>Note</sup>    |                                                                                                                                       |                                                                |  |

| counter               | 51 <sup>Note</sup>    |                                                                                                                                       |                                                                |  |

| 8-bit timer           | HO                    |                                                                                                                                       |                                                                |  |

|                       | H1                    |                                                                                                                                       |                                                                |  |

| Watch timer           |                       |                                                                                                                                       |                                                                |  |

| Watchdog timer        |                       | Operable. Clock supply to watchdog timer stops when "internal low-speed oscillator can be stopped by software" is set by option byte. |                                                                |  |

| Clock output          |                       | Operable                                                                                                                              |                                                                |  |

| Buzzer output         |                       | Operable. However, operation disabled when peripheral hardware clock (fPRs) is stopped.                                               |                                                                |  |

| A/D converter         |                       |                                                                                                                                       |                                                                |  |

| Serial interface      | JART0                 | Operable                                                                                                                              |                                                                |  |

|                       | JART6                 |                                                                                                                                       |                                                                |  |

|                       | CSI10 <sup>Note</sup> |                                                                                                                                       |                                                                |  |

|                       | CSI11 <sup>№te</sup>  |                                                                                                                                       |                                                                |  |

|                       | CSIA0 <sup>Note</sup> |                                                                                                                                       |                                                                |  |

|                       | IC0 <sup>Note</sup>   |                                                                                                                                       |                                                                |  |

| Multiplier/divider    |                       |                                                                                                                                       |                                                                |  |

| Power-on-clear func   | tion                  |                                                                                                                                       |                                                                |  |

| Low-voltage detection | n function            |                                                                                                                                       |                                                                |  |

| External interrupt    |                       |                                                                                                                                       |                                                                |  |

| Table 22-1. | Operating | Statuses in | HALT N | lode (2/2) |

|-------------|-----------|-------------|--------|------------|

|-------------|-----------|-------------|--------|------------|

**Note** When the CPU is operating on the subsystem clock and the internal high-speed oscillation clock and high-speed system clock have been stopped, do not start operation of these functions on the external clock input from peripheral hardware pins.

| Remarks 1. | fвн:     | Internal high-speed oscillation clock, | fx:  | X1 clock                             |

|------------|----------|----------------------------------------|------|--------------------------------------|

|            | fexclk:  | External main system clock,            | fx⊤: | XT1 clock                            |

|            | fexclks: | External subsystem clock,              | frL: | Internal low-speed oscillation clock |

2. The functions mounted depend on the product. See 1.7 Block Diagram and 1.8 Outline of Functions.

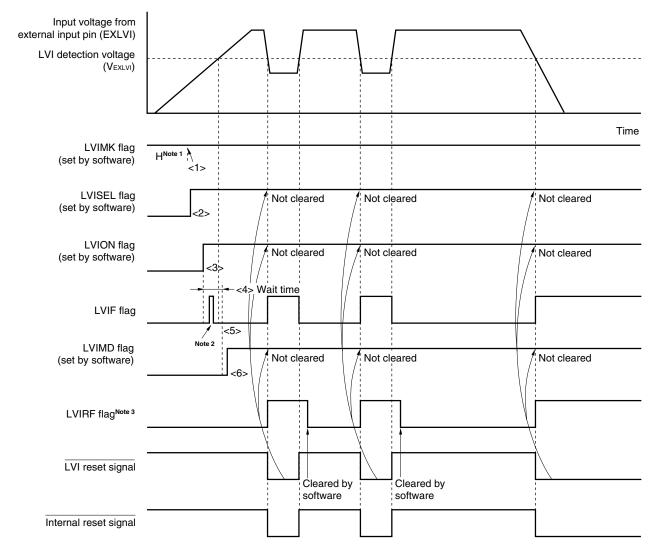

Figure 25-6. Timing of Low-Voltage Detector Internal Reset Signal Generation (Detects Level of Input Voltage from External Input Pin (EXLVI))

- Notes 1. The LVIMK flag is set to "1" by reset signal generation.

- 2. The LVIF flag may be set (1).

- 3. LVIRF is bit 0 of the reset control flag register (RESF). For details of RESF, see CHAPTER 23 RESET FUNCTION.

- Remark <1> to <6> in Figure 25-6 above correspond to <1> to <6> in the description of "When starting operation" in 25.4.1 (2) When detecting level of input voltage from external input pin (EXLVI).

- µPD78F0500MC(A)-CAB-AX, 78F0501MC(A)-CAB-AX, 78F0502MC(A)-CAB-AX, 78F0503MC(A)-CAB-AX

- *μ*PD78F0500MC(A2)-CAB-AX, 78F0501MC(A2)-CAB-AX, 78F0502MC(A2)-CAB-AX, 78F0503MC(A2)-CAB-AX

- μPD78F0500AMC-CAB-AX, 78F0501AMC-CAB-AX, 78F0502AMC-CAB-AX, 78F0503AMC-CAB-AX, 78F0503DAMC-CAB-AX

- µPD78F0500AMCA-CAB-G, 78F0501AMCA-CAB-G, 78F0502AMCA-CAB-G, 78F0503AMCA-CAB-G

- µPD78F0500AMCA2-CAB-G, 78F0501AMCA2-CAB-G, 78F0502AMCA2-CAB-G, 78F0503AMCA2-CAB-G

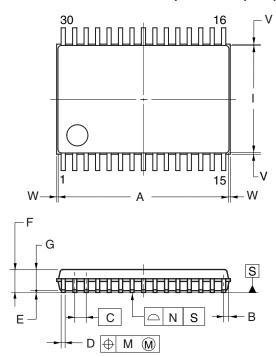

## 30-PIN PLASTIC SSOP (7.62mm (300))

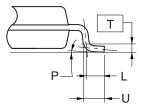

detail of lead end

### NOTE

Each lead centerline is located within 0.13 mm of its true position (T.P.) at maximum material condition.

|      | (UNIT:mm)                       |

|------|---------------------------------|

| ITEM | DIMENSIONS                      |

| Α    | 9.70±0.10                       |

| В    | 0.30                            |

| С    | 0.65 (T.P.)                     |

| D    | $0.22\substack{+0.10 \\ -0.05}$ |

| E    | 0.10±0.05                       |

| F    | 1.30±0.10                       |

| G    | 1.20                            |

| Н    | 8.10±0.20                       |

| I    | 6.10±0.10                       |

| J    | 1.00±0.20                       |

| к    | $0.15^{+0.05}_{-0.01}$          |

| L    | 0.50                            |

| М    | 0.13                            |

| Ν    | 0.10                            |

| Р    | 3° <sup>+5°</sup> 3°            |

| Т    | 0.25(T.P.)                      |

| U    | 0.60±0.15                       |

| V    | 0.25 MAX.                       |

| W    | 0.15 MAX.                       |

|      | P30MC-65-CAB                    |

## 34.3 78K0/KD2

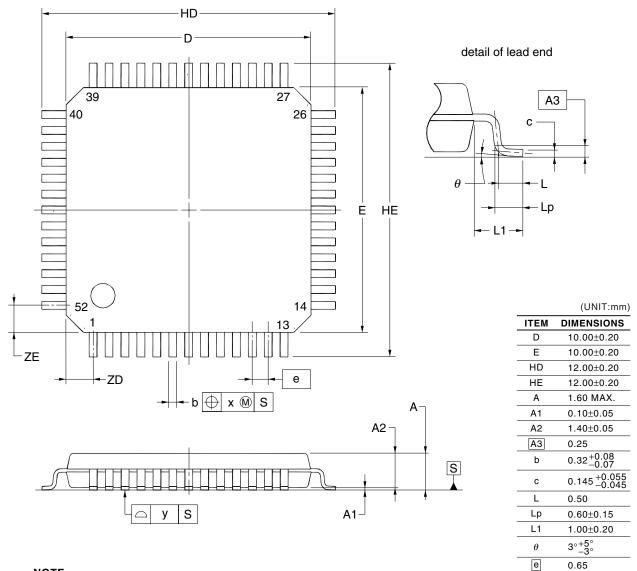

• *µ*PD78F0521GB-UET-A, 78F0522GB-UET-A, 78F0523GB-UET-A, 78F0524GB-UET-A, 78F0525GB-UET-A, 78F0526GB-UET-A, 78F0527GB-UET-A, 78F0527DGB-UET-A

# 52-PIN PLASTIC LQFP(10x10)

## NOTE

Each lead centerline is located within 0.13 mm of its true position at maximum material condition.

1.10 P52GB-65-UET-1

0.13

0.10

1.10

Х

y

ZD

ΖE

| Serial trigger register 0 (CSIT0)                 | 519 |

|---------------------------------------------------|-----|

| Slave address register 0 (SVA0)                   | 553 |

| 16-bit timer capture/compare register 000 (CR000) | 273 |

| 16-bit timer capture/compare register 001 (CR001) | 273 |

| 16-bit timer capture/compare register 010 (CR010) | 273 |

| 16-bit timer capture/compare register 011 (CR011) | 273 |

| 16-bit timer counter 00 (TM00)                    | 272 |

| 16-bit timer counter 01 (TM00)                    | 272 |

| 16-bit timer mode control register 00 (TMC00)     | 277 |

| 16-bit timer mode control register 01 (TMC01)     | 277 |

| 16-bit timer output control register 00 (TOC00)   | 282 |

| 16-bit timer output control register 01 (TOC01)   | 282 |

# [T]

| Timer clock selection register 50 (TCL50)    | . 348 |

|----------------------------------------------|-------|

| Timer clock selection register 51 (TCL51)    | . 348 |

| 10-bit A/D conversion result register (ADCR) | . 416 |

| Transmit buffer register 10 (SOTB10)         | . 492 |

| Transmit buffer register 11 (SOTB11)         | . 492 |

| Transmit buffer register 6 (TXB6)            | . 459 |

| Transmit shift register 0 (TXS0)             | . 435 |

| Transmit shift register 6 (TXS6)             | . 459 |

| [W]                                          |       |

| Watch timer operation mode register (WTM) | 391 |

|-------------------------------------------|-----|

| Watchdog timer enable register (WDTE)     | 398 |

|            |                |                              | 1                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |     | 6/30) |

|------------|----------------|------------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|-------|

| Chapter    | Classification | Function                     | Details of<br>Function                          | Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    | Pag | e     |

| Chapter 14 | 0              | Serial<br>interface<br>UART0 | POWER0, TXE0,<br>RXE0: Bits 7, 6,<br>5 of ASIM0 | Clear POWER0 to 0 after clearing TXE0 and RXE0 to 0 to set the operation stop<br>mode.<br>To start the communication, set POWER0 to 1, and then set TXE0 or RXE0 to 1.                                                                                                                                                                                                                                                                                                                                                                                         | p. | 441 |       |

|            |                |                              | UART mode                                       | Take relationship with the other party of communication when setting the port mode register and port register.                                                                                                                                                                                                                                                                                                                                                                                                                                                 | p. | 442 |       |

|            |                |                              | UART<br>transmission                            | After transmit data is written to TXS0, do not write the next transmit data before the transmission completion interrupt signal (INTST0) is generated.                                                                                                                                                                                                                                                                                                                                                                                                         | p. | 445 |       |

|            |                |                              | UART reception                                  | If a reception error occurs, read asynchronous serial interface reception error status register 0 (ASIS0) and then read receive buffer register 0 (RXB0) to clear the error flag.<br>Otherwise, an overrun error will occur when the next data is received, and the reception error status will persist.                                                                                                                                                                                                                                                       | p. | 446 |       |

|            |                |                              |                                                 | Reception is always performed with the "number of stop bits = 1". The second stop bit is ignored.                                                                                                                                                                                                                                                                                                                                                                                                                                                              | p. | 446 |       |

|            |                |                              | Error of baud rate                              | Keep the baud rate error during transmission to within the permissible error range at the reception destination.                                                                                                                                                                                                                                                                                                                                                                                                                                               | p. | 450 |       |

|            |                |                              |                                                 | Make sure that the baud rate error during reception satisfies the range shown in (4)<br>Permissible baud rate range during reception.                                                                                                                                                                                                                                                                                                                                                                                                                          | p. | 450 |       |

|            |                |                              |                                                 | Make sure that the baud rate error during reception is within the permissible error range, by using the calculation expression shown below.                                                                                                                                                                                                                                                                                                                                                                                                                    | p. | 451 |       |

| Chapter 15 | Soft           | Serial<br>interface<br>UART6 |                                                 | The TxD6 output inversion function inverts only the transmission side and not the reception side. To use this function, the reception side must be ready for reception of inverted data.                                                                                                                                                                                                                                                                                                                                                                       | p. | 453 |       |

| Ch         |                |                              |                                                 | If clock supply to serial interface UART6 is not stopped (e.g., in the HALT mode),<br>normal operation continues. If clock supply to serial interface UART6 is stopped (e.g.,<br>in the STOP mode), each register stops operating, and holds the value immediately<br>before clock supply was stopped. The TxD6 pin also holds the value immediately<br>before clock supply was stopped and outputs it. However, the operation is not<br>guaranteed after clock supply is resumed. Therefore, reset the circuit so that<br>POWER6 = 0, RXE6 = 0, and TXE6 = 0. | p. | 453 |       |

|            |                |                              |                                                 | Set POWER6 = 1 and then set TXE6 = 1 (transmission) or RXE6 = 1 (reception) to start communication.                                                                                                                                                                                                                                                                                                                                                                                                                                                            | p. | 453 |       |

|            |                |                              |                                                 | TXE6 and RXE6 are synchronized by the base clock (fxcLk6) set by CKSR6. To enable transmission or reception again, set TXE6 or RXE6 to 1 at least two clocks of the base clock after TXE6 or RXE6 has been cleared to 0. If TXE6 or RXE6 is set within two clocks of the base clock, the transmission circuit or reception circuit may not be initialized.                                                                                                                                                                                                     | p. | 453 |       |

|            |                |                              |                                                 | Set transmit data to TXB6 at least one base clock ( $f_{XCLK6}$ ) after setting TXE6 = 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | p. | 453 |       |

|            |                |                              |                                                 | If data is continuously transmitted, the communication timing from the stop bit to the next start bit is extended two operating clocks of the macro. However, this does not affect the result of communication because the reception side initializes the timing when it has detected a start bit. Do not use the continuous transmission function if the interface is used in LIN communication operation.                                                                                                                                                    | p. | 453 |       |

|            |                |                              | buffer register 6                               | Do not write data to TXB6 when bit 1 (TXBF6) of asynchronous serial interface transmission status register 6 (ASIF6) is 1.                                                                                                                                                                                                                                                                                                                                                                                                                                     | p. | 459 |       |

|            |                |                              |                                                 | Do not refresh (write the same value to) TXB6 by software during a communication operation (when bits 7 and 6 (POWER6, TXE6) of asynchronous serial interface operation mode register 6 (ASIM6) are 1 or when bits 7 and 5 (POWER6, RXE6) of ASIM6 are 1).                                                                                                                                                                                                                                                                                                     | p. | 459 |       |

|            |                |                              |                                                 | Set transmit data to TXB6 at least one base clock (fxcLk6) after setting TXE6 = 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | p. | 459 |       |