Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | 78K/0                                                                                 |

| Core Size                  | 8-Bit                                                                                 |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                                    |

| Number of I/O              | 55                                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                                      |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 7K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 8x10b                                                                             |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 64-TQFP                                                                               |

| Supplier Device Package    | ·                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0537aga-hab-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| CHAPTER 15 SERIAL INTERFACE UART6                                      |     |

|------------------------------------------------------------------------|-----|

| 15.1 Functions of Serial Interface UART6                               |     |

| 15.2 Configuration of Serial Interface UART6                           |     |

| 15.3 Registers Controlling Serial Interface UART6                      |     |

| 15.4 Operation of Serial Interface UART6                               |     |

| 15.4.1 Operation stop mode                                             | 469 |

| 15.4.2 Asynchronous serial interface (UART) mode                       | 470 |

| 15.4.3 Dedicated baud rate generator                                   | 483 |

| 15.4.4 Calculation of baud rate                                        |     |

| CHAPTER 16 SERIAL INTERFACES CSI10 AND CSI11                           | 490 |

| 16.1 Functions of Serial Interfaces CSI10 and CSI11                    |     |

| 16.2 Configuration of Serial Interfaces CSI10 and CSI11                |     |

| 16.3 Registers Controlling Serial Interfaces CSI10 and CSI11           |     |

| 16.4 Operation of Serial Interfaces CSI10 and CSI11                    |     |

| 16.4.1 Operation stop mode                                             |     |

| 16.4.2 3-wire serial I/O mode                                          |     |

|                                                                        |     |

| CHAPTER 17 SERIAL INTERFACE CSIA0                                      | 512 |

| 17.1 Functions of Serial Interface CSIA0                               |     |

| 17.2 Configuration of Serial Interface CSIA0                           |     |

| 17.3 Registers Controlling Serial Interface CSIA0                      |     |

| 17.4 Operation of Serial Interface CSIA0                               |     |

| 17.4.1 Operation stop mode                                             |     |

| 17.4.2 3-wire serial I/O mode                                          | 525 |

| 17.4.3 3-wire serial I/O mode with automatic transmit/receive function | 530 |

| CHAPTER 18 SERIAL INTERFACE IIC0                                       | 550 |

| 18.1 Functions of Serial Interface IIC0                                | 550 |

| 18.2 Configuration of Serial Interface IIC0                            |     |

| 18.3 Registers to Control Serial Interface IIC0                        |     |

| 18.4 I <sup>2</sup> C Bus Mode Functions                               |     |

| 18.4.1 Pin configuration                                               |     |

| 18.5 I <sup>2</sup> C Bus Definitions and Control Methods              |     |

| 18.5.1 Start conditions                                                |     |

| 18.5.2 Addresses                                                       |     |

| 18.5.3 Transfer direction specification                                |     |

| 18.5.4 Acknowledge (ACK)                                               |     |

| 18.5.5 Stop condition                                                  |     |

| 18.5.6 Wait                                                            |     |

| 18.5.7 Canceling wait                                                  |     |

| 18.5.8 Interrupt request (INTIIC0) generation timing and wait control  |     |

| 18.5.9 Address match detection method                                  |     |

| 18.5.10 Error detection                                                |     |

| 18.5.11 Extension code                                                 |     |

| 18.5.12 Arbitration                                                    |     |

| 18.5.13 Wakeup function                                                |     |

| 18.5.14 Communication reservation                                      |     |

|                                                                        |     |

### (1) Port functions (2/2): 78K0/KE2

| Function Name | I/O    | Function                                                                                                                                                     | After Reset | Alternate Function             |

|---------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------------|

| P70 to P77    | I/O    | Port 7.<br>8-bit I/O port.<br>Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a<br>software setting. | Input port  | KR0 to KR7                     |

| P120          | I/O    | Port 12.                                                                                                                                                     | Input port  | INTP0/EXLVI                    |

| P121          |        | 5-bit I/O port.                                                                                                                                              |             | X1/OCD0A <sup>Note</sup>       |

| P122          |        | Input/output can be specified in 1-bit units.<br>Only for P120, use of an on-chip pull-up resistor can be<br>specified by a software setting.                |             | X2/EXCLK/OCD0B <sup>Note</sup> |

| P123          |        |                                                                                                                                                              |             | XT1                            |

| P124          |        |                                                                                                                                                              |             | XT2/EXCLKS                     |

| P130          | Output | Port 13.<br>1-bit output-only port.                                                                                                                          | Output port | -                              |

| P140          | I/O    | Port 14.                                                                                                                                                     | Input port  | PCL/INTP6                      |

| P141          |        | 2-bit I/O port.<br>Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a<br>software setting.            |             | BUZ/INTP7                      |

Note µPD78F0537D and 78F0537DA (product with on-chip debug function) only

### (2) Non-port functions (1/3): 78K0/KE2

| Function Name | I/O    | Function                                                                                                                                     | After Reset  | Alternate Function        |

|---------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------|

| ANI0 to ANI7  | Input  | A/D converter analog input                                                                                                                   | Analog input | P20 to P27                |

| BUZ           | Output | Buzzer output                                                                                                                                | Input port   | P141/INTP7                |

| EXLVI         | Input  | Potential input for external low-voltage detection                                                                                           | Input port   | P120/INTP0                |

| EXSCL0        | Input  | External clock input for I <sup>2</sup> C.<br>To input an external clock, input a clock of 6.4 MHz.                                          | Input port   | P62                       |

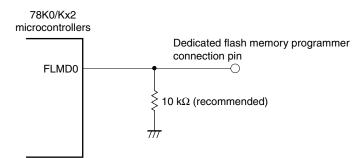

| FLMD0         | _      | Flash memory programming mode setting                                                                                                        | _            | -                         |

| INTP0         | Input  | External interrupt request input for which the valid edge (rising                                                                            | Input port   | P120/EXLVI                |

| INTP1         |        | edge, falling edge, or both rising and falling edges) can be                                                                                 |              | P30                       |

| INTP2         |        | specified                                                                                                                                    |              | P31/OCD1A <sup>Note</sup> |

| INTP3         |        |                                                                                                                                              |              | P32/OCD1B <sup>Note</sup> |

| INTP4         |        |                                                                                                                                              |              | P33/TI51/TO51             |

| INTP5         |        |                                                                                                                                              |              | P16/TOH1                  |

| INTP6         |        |                                                                                                                                              |              | P140/PCL                  |

| INTP7         |        |                                                                                                                                              |              | P141/BUZ                  |

| KR0 to KR7    | Input  | Key interrupt input                                                                                                                          | Input port   | P70 to P77                |

| PCL           | Output | Clock output (for trimming of high-speed system clock, subsystem clock)                                                                      | Input port   | P140/INTP6                |

| REGC          | -      | Connecting regulator output (2.5 V) stabilization capacitance for internal operation.<br>Connect to Vss via a capacitor (0.47 to 1 $\mu$ F). | -            | _                         |

**Note** *µ*PD78F0537D and 78F0537DA (product with on-chip debug function) only

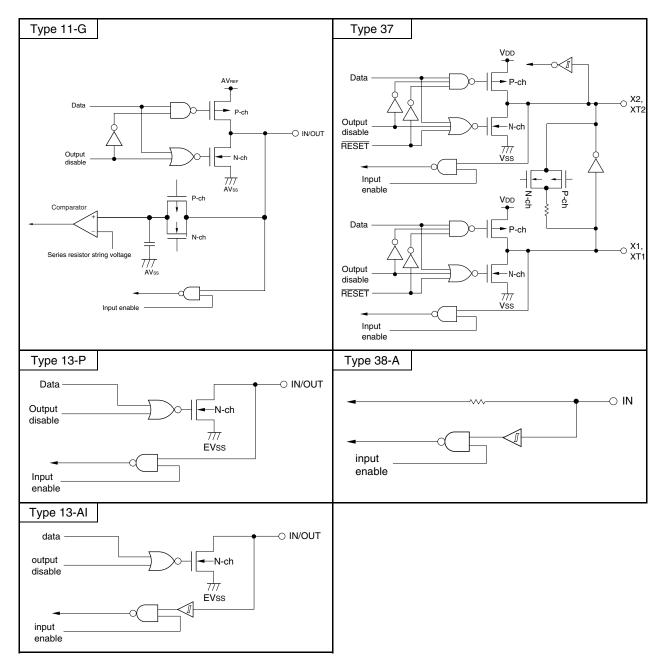

Figure 2-1. Pin I/O Circuit List (2/2)

Remark With products not provided with an EVDD or EVss pin, replace EVDD with VDD, or replace EVss with Vss.

| Address | Special Function Register (SFR) Name Symbol                         |      | R/W  | Manip | ulatable     | Bit Unit     | After        | К     | К            | К            | К            | К            |              |

|---------|---------------------------------------------------------------------|------|------|-------|--------------|--------------|--------------|-------|--------------|--------------|--------------|--------------|--------------|

|         |                                                                     |      |      |       | 1 Bit        | 8 Bits       | 16 Bits      | Reset | В            | С            | D            | E            | F            |

|         |                                                                     |      |      |       |              |              |              |       | 2            | 2            | 2            | 2            | 2            |

| FFE8H   | Priority specification flag register 0L                             | PR0  | PR0L | R/W   | $\checkmark$ |              | $\checkmark$ | FFH   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| FFE9H   | Priority specification flag register 0H                             |      | PR0H | R/W   | $\checkmark$ |              |              | FFH   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| FFEAH   | Priority specification flag register 1L                             | PR1  | PR1L | R/W   | $\checkmark$ |              | $\checkmark$ | FFH   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| FFEBH   | Priority specification flag register 1H                             |      | PR1H | R/W   | $\checkmark$ |              |              | FFH   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| FFF0H   | Internal memory size switching register <sup>Notes 3,4</sup>        | IMS  |      | R/W   | -            | $\checkmark$ | -            | CFH   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| FFF3H   | Memory bank select register                                         | BANK | (    | R/W   | -            |              | -            | 00H   | -            | -            | Note 1       | Note 1       | Note 1       |

| FFF4H   | Internal expansion RAM size switching register <sup>Notes 3,4</sup> | IXS  |      | R/W   | _            | V            | -            | 0CH   | Note<br>2    | Note<br>2    | Note<br>2    | Note<br>2    | $\checkmark$ |

| FFFBH   | Processor clock control register                                    | PCC  |      | R/W   | $\checkmark$ |              | -            | 01H   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

Table 3-8.

Special Function Register List (5/5)

Notes 1. This register is incorporated only in products whose flash memory is at least 96 KB.

2. Set this register only in products with internal expansion RAM.

**3.** Regardless of the internal memory capacity, the initial values of the internal memory size switching register (IMS) and internal expansion RAM size switching register (IXS) of all products in the 78K0/Kx2 microcontrollers are fixed (IMS = CFH, IXS = 0CH). Therefore, set the value corresponding to each product as indicated in Tables 3-1 and 3-2.

4. The ROM and RAM capacities of the products with the on-chip debug function can be debugged by setting IMS and IXS, according to the debug target products. Set IMS and IXS according to the debug target products.

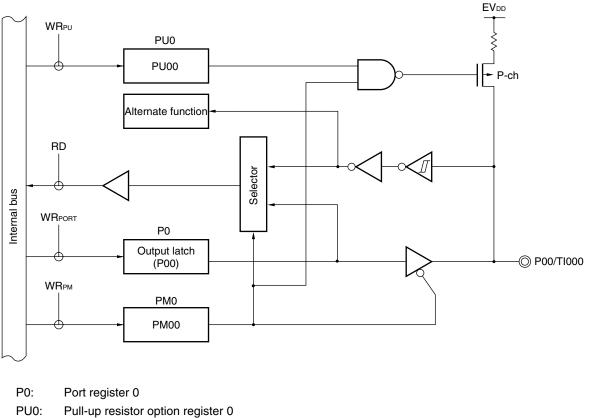

Figure 5-1. Block Diagram of P00

- PM0: Port mode register 0

- RD: Read signal

- WR××: Write signal

**Remark** With products not provided with an EVDD or EVSS pin, replace EVDD with VDD, or replace EVSS with VSS.

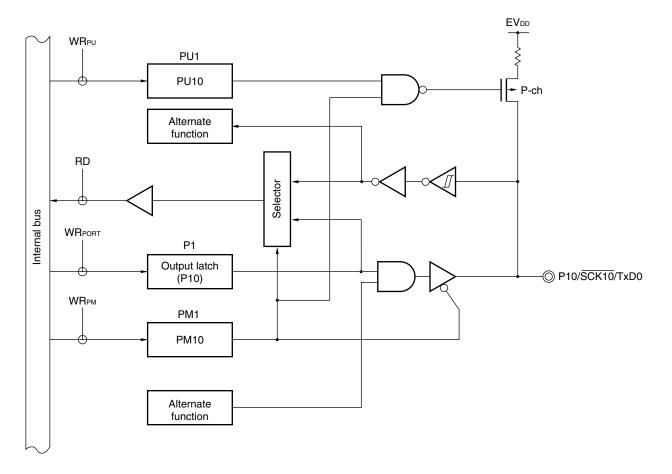

Figure 5-7. Block Diagram of P10

- P1: Port register 1

- PU1: Pull-up resistor option register 1

- PM1: Port mode register 1

- RD: Read signal

- WR××: Write signal

Remark With products not provided with an EVDD or EVSS pin, replace EVDD with VDD, or replace EVSS with VSS.

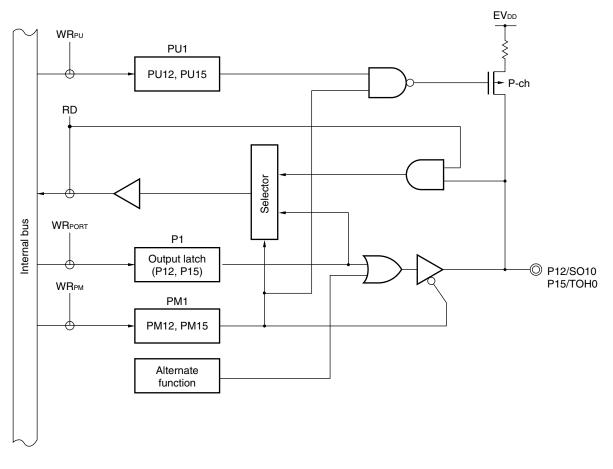

Figure 5-9. Block Diagram of P12 and P15

- P1: Port register 1

- PU1: Pull-up resistor option register 1

- PM1: Port mode register 1

- RD: Read signal

- WR××: Write signal

Remark With products not provided with an EVDD or EVSS pin, replace EVDD with VDD, or replace EVSS with VSS.

### (3) Port mode register 1 (PM1)

This register sets port 1 input/output in 1-bit units.

When using the P15/TOH0 and P16/TOH1/INTP5 pins for timer output, clear PM15 and PM16 and the output latches of P15 and P16 to 0.

PM1 can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets this register to FFH.

### Figure 9-8. Format of Port Mode Register 1 (PM1)

| Address: I | F21H Af | ter reset: FF | H R/W |      |      |      |      |      |

|------------|---------|---------------|-------|------|------|------|------|------|

| Symbol     | 7       | 6             | 5     | 4    | 3    | 2    | 1    | 0    |

| PM1        | PM17    | PM16          | PM15  | PM14 | PM13 | PM12 | PM11 | PM10 |

| PM1n                             | P1n pin I/O mode selection (n = 0 to 7) |  |  |  |  |

|----------------------------------|-----------------------------------------|--|--|--|--|

| 0 Output mode (output buffer on) |                                         |  |  |  |  |

| 1                                | Input mode (output buffer off)          |  |  |  |  |

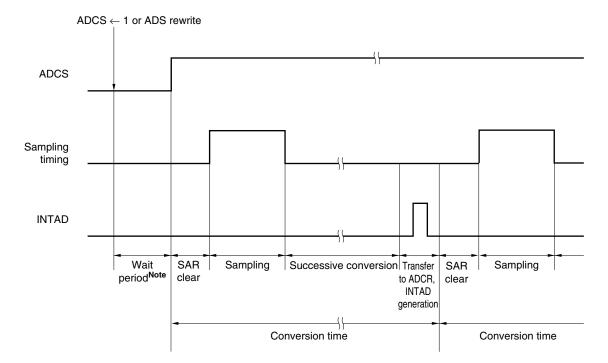

Figure 13-5. A/D Converter Sampling and A/D Conversion Timing

Note For details of wait period, see CHAPTER 36 CAUTIONS FOR WAIT.

### (2) 10-bit A/D conversion result register (ADCR)

This register is a 16-bit register that stores the A/D conversion result. The lower 6 bits are fixed to 0. Each time A/D conversion ends, the conversion result is loaded from the successive approximation register. The higher 8 bits of the conversion result are stored in FF09H and the lower 2 bits are stored in the higher 2 bits of FF08H.

ADCR can be read by a 16-bit memory manipulation instruction.

Reset signal generation clears this register to 0000H.

### Figure 13-6. Format of 10-Bit A/D Conversion Result Register (ADCR)

|        | Addres | s: FF08 | BH, FFO | 9H A | fter res | et: 000 | OH F | 1 |  |   |     |     |   |   |   |

|--------|--------|---------|---------|------|----------|---------|------|---|--|---|-----|-----|---|---|---|

| Symbol |        |         |         | FFC  | 9H       |         |      |   |  |   | FFC | )8H |   |   |   |

| ADCR   |        |         |         |      |          |         |      |   |  | 0 | 0   | 0   | 0 | 0 | 0 |

- Cautions 1. When writing to the A/D converter mode register (ADM), analog input channel specification register (ADS), and A/D port configuration register (ADPC), the contents of ADCR may become undefined. Read the conversion result following conversion completion before writing to ADM, ADS, and ADPC. Using timing other than the above may cause an incorrect conversion result to be read.

- 2. If data is read from ADCR, a wait cycle is generated. Do not read data from ADCR when the peripheral hardware clock (fprs) is stopped. For details, see CHAPTER 36 CAUTIONS FOR WAIT.

### (2) Asynchronous serial interface reception error status register 6 (ASIS6)

This register indicates an error status on completion of reception by serial interface UART6. It includes three error flag bits (PE6, FE6, OVE6).

This register is read-only by an 8-bit memory manipulation instruction.

Reset signal generation, or clearing bit 7 (POWER6) or bit 5 (RXE6) of ASIM6 to 0 clears this register to 00H. 00H is read when this register is read. If a reception error occurs, read ASIS6 and then read receive buffer register 6 (RXB6) to clear the error flag.

### Figure 15-6. Format of Asynchronous Serial Interface Reception Error Status Register 6 (ASIS6)

#### Address: FF53H After reset: 00H R

| Symbol | 7 | 6 | 5 | 4 | 3 | 2   | 1   | 0    |

|--------|---|---|---|---|---|-----|-----|------|

| ASIS6  | 0 | 0 | 0 | 0 | 0 | PE6 | FE6 | OVE6 |

| PE6 | Status flag indicating parity error                                                     |

|-----|-----------------------------------------------------------------------------------------|

| 0   | If POWER6 = 0 or RXE6 = 0, or if ASIS6 register is read                                 |

| 1   | If the parity of transmit data does not match the parity bit on completion of reception |

| FE6 | Status flag indicating framing error                       |

|-----|------------------------------------------------------------|

| 0   | If POWER6 = 0 or RXE6 = 0, or if ASIS6 register is read    |

| 1   | If the stop bit is not detected on completion of reception |

| OVE6 | Status flag indicating overrun error                                                                               |

|------|--------------------------------------------------------------------------------------------------------------------|

| 0    | If POWER6 = 0 or RXE6 = 0, or if ASIS6 register is read                                                            |

| 1    | If receive data is set to the RXB6 register and the next reception operation is completed before the data is read. |

Cautions 1. The operation of the PE6 bit differs depending on the set values of the PS61 and PS60 bits of asynchronous serial interface operation mode register 6 (ASIM6).

- 2. For the stop bit of the receive data, only the first stop bit is checked regardless of the number of stop bits.

- 3. If an overrun error occurs, the next receive data is not written to receive buffer register 6 (RXB6) but discarded.

- 4. If data is read from ASIS6, a wait cycle is generated. Do not read data from ASIS6 when the peripheral hardware clock (fprs) is stopped. For details, see CHAPTER 36 CAUTIONS FOR WAIT.

### (2) Communication operation

In the 3-wire serial I/O mode, data is transmitted or received in 8-bit units. Each bit of the data is transmitted or received in synchronization with the serial clock.

Data can be transmitted or received if bit 6 (TRMD1n) of serial operation mode register 1n (CSIM1n) is 1. Transmission/reception is started when a value is written to transmit buffer register 1n (SOTB1n). In addition, data can be received when bit 6 (TRMD1n) of serial operation mode register 1n (CSIM1n) is 0.

Reception is started when data is read from serial I/O shift register 1n (SIO1n).

However, communication is performed as follows if bit 5 (SSE11) of CSIM11 is 1 when serial interface CSI11 is in the slave mode.

- <1> Low level input to the SSI11 pin

- → Transmission/reception is started when SOTB11 is written, or reception is started when SIO11 is read.

- <2> High level input to the  $\overline{SSI11}$  pin

- → Transmission/reception or reception is held, therefore, even if SOTB11 is written or SIO11 is read, transmission/reception or reception will not be started.

- <3> Data is written to SOTB11 or data is read from SIO11 while a high level is input to the SSI11 pin, then a low level is input to the SSI11 pin

- $\rightarrow$  Transmission/reception or reception is started.

- <4> A high level is input to the SSI11 pin during transmission/reception or reception

- $\rightarrow$  Transmission/reception or reception is suspended.

After communication has been started, bit 0 (CSOT1n) of CSIM1n is set to 1. When communication of 8-bit data has been completed, a communication completion interrupt request flag (CSIIF1n) is set, and CSOT1n is cleared to 0. Then the next communication is enabled.

- Cautions 1. Do not access the control register and data register when CSOT1n = 1 (during serial communication).

- 2. When using serial interface CSI11, wait for the duration of at least one clock before the clock operation is started to change the level of the SSI11 pin in the slave mode; otherwise, malfunctioning may occur.

- **Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

- n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

## CHAPTER 22 STANDBY FUNCTION

### 22.1 Standby Function and Configuration

#### 22.1.1 Standby function

The standby function is mounted onto all 78K0/Kx2 microcontroller products.

The standby function is designed to reduce the operating current of the system. The following two modes are available.

### (1) HALT mode

HALT instruction execution sets the HALT mode. In the HALT mode, the CPU operation clock is stopped. If the highspeed system clock oscillator, internal high-speed oscillator, internal low-speed oscillator, or subsystem clock oscillator is operating before the HALT mode is set, oscillation of each clock continues. In this mode, the operating current is not decreased as much as in the STOP mode, but the HALT mode is effective for restarting operation immediately upon interrupt request generation and carrying out intermittent operations frequently.

**Note** The 78K0/KB2 is not provided with a subsystem clock oscillator.

#### (2) STOP mode

STOP instruction execution sets the STOP mode. In the STOP mode, the high-speed system clock oscillator and internal high-speed oscillator stop, stopping the whole system, thereby considerably reducing the CPU operating current.

Because this mode can be cleared by an interrupt request, it enables intermittent operations to be carried out. However, because a wait time is required to secure the oscillation stabilization time after the STOP mode is released when the X1 clock is selected, select the HALT mode if it is necessary to start processing immediately upon interrupt request generation.

In either of these two modes, all the contents of registers, flags and data memory just before the standby mode is set are held. The I/O port output latches and output buffer statuses are also held.

- Cautions 1. The STOP mode can be used only when the CPU is operating on the main system clock. The subsystem clock oscillation cannot be stopped. The HALT mode can be used when the CPU is operating on either the main system clock or the subsystem clock.

- 2. When shifting to the STOP mode, be sure to stop the peripheral hardware operation operating with main system clock before executing STOP instruction.

- 3. The following sequence is recommended for operating current reduction of the A/D converter when the standby function is used: First clear bit 7 (ADCS) and bit 0 (ADCE) of the A/D converter mode register (ADM) to 0 to stop the A/D conversion operation, and then execute the STOP instruction.

### CHAPTER 23 RESET FUNCTION

The reset function is mounted onto all 78K0/Kx2 microcontroller products. The following four operations are available to generate a reset signal.

- (1) External reset input via RESET pin

- (2) Internal reset by watchdog timer program loop detection

- (3) Internal reset by comparison of supply voltage and detection voltage of power-on-clear (POC) circuit

- (4) Internal reset by comparison of supply voltage and detection voltage of low-power-supply detector (LVI)

External and internal resets have no functional differences. In both cases, program execution starts at the address at 0000H and 0001H when the reset signal is generated.

A reset is applied when a low level is input to the RESET pin, the watchdog timer overflows, or by POC and LVI circuit voltage detection, and each item of hardware is set to the status shown in Tables 23-1 and 23-2. Each pin is high impedance during reset signal generation or during the oscillation stabilization time just after a reset release, except for P130, which is low-level output.

When a low level is input to the  $\overrightarrow{RESET}$  pin, the device is reset. It is released from the reset status when a high level is input to the  $\overrightarrow{RESET}$  pin and program execution is started with the internal high-speed oscillation clock after reset processing. A reset by the watchdog timer is automatically released, and program execution starts using the internal high-speed oscillation clock (see **Figures 23-2** to **23-4**) after reset processing. Reset by POC and LVI circuit power supply detection is automatically released when  $V_{DD} \ge V_{POC}$  or  $V_{DD} \ge V_{LVI}$  after the reset, and program execution starts using the internal high-speed oscillation clock (see **CHAPTER 24 POWER-ON-CLEAR CIRCUIT** and **CHAPTER 25 LOW-VOLTAGE DETECTOR**) after reset processing.

#### Cautions 1. For an external reset, input a low level for 10 $\mu$ s or more to the RESET pin.

- 2. During reset signal generation, the X1 clock, XT1 clock<sup>Note 1</sup>, internal high-speed oscillation clock, and internal low-speed oscillation clock stop oscillating. External main system clock input and external subsystem clock<sup>Note 1</sup> input become invalid.

- 3. When the STOP mode is released by a reset, the STOP mode contents are held during reset input. However, the port pins become high-impedance, except for P130<sup>Note 2</sup>, which is set to low-level output.

- Notes 1. The 78K0/KB2 is not provided with XT1 clock and external subsystem clock.

- 2. P130 pin is not mounted onto 38-pin and 44-pin products of the 78K0/KC2 and 78K0/KB2.

|                                       | Hardware                                                                  | Status After Reset<br>Acknowledgment <sup>Note 1</sup> |

|---------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------|

| Memory bank select registe            | er (BANK)                                                                 | 00H                                                    |

| Clock operation mode sele             | 00H                                                                       |                                                        |

| Processor clock control reg           | 01H                                                                       |                                                        |

| Internal oscillation mode re          | 80H                                                                       |                                                        |

| Main OSC control register             | (MOC)                                                                     | 80H                                                    |

| Main clock mode register (            | MCM)                                                                      | 00H                                                    |

| Oscillation stabilization time        | e counter status register (OSTC)                                          | 00H                                                    |

| Oscillation stabilization time        | e select register (OSTS)                                                  | 05H                                                    |

| 16-bit timer/event                    | Timer counters 00, 01 (TM00, TM01)                                        | 0000H                                                  |

| counters 00, 01                       | Capture/compare registers 000, 010, 001, 011 (CR000, CR010, CR001, CR011) | 0000H                                                  |

|                                       | Mode control registers 00, 01 (TMC00, TMC01)                              | 00H                                                    |

|                                       | Prescaler mode registers 00, 01 (PRM00, PRM01)                            | 00H                                                    |

|                                       | Capture/compare control registers 00, 01 (CRC00, CRC01)                   | 00H                                                    |

|                                       | Timer output control registers 00, 01 (TOC00, TOC01)                      | 00H                                                    |

| 8-bit timer/event counters            | Timer counters 50, 51 (TM50, TM51)                                        | 00H                                                    |

| 50, 51                                | Compare registers 50, 51 (CR50, CR51)                                     | 00H                                                    |

|                                       | Timer clock selection registers 50, 51 (TCL50, TCL51)                     | 00H                                                    |

|                                       | Mode control registers 50, 51 (TMC50, TMC51)                              | 00H                                                    |

| 8-bit timers H0, H1                   | Compare registers 00, 10, 01, 11 (CMP00, CMP10, CMP01, CMP11)             | 00H                                                    |

|                                       | Mode registers (TMHMD0, TMHMD1)                                           | 00H                                                    |

|                                       | Carrier control register 1 (TMCYC1) <sup>Note 2</sup>                     | 00H                                                    |

| Watch timer                           | Operation mode register (WTM)                                             | 00H                                                    |

| Clock output/buzzer output controller | Clock output selection register (CKS)                                     | 00H                                                    |

| Watchdog timer                        | Enable register (WDTE)                                                    | 1AH/9AH <sup>Note 3</sup>                              |

| A/D converter                         | 10-bit A/D conversion result register (ADCR)                              | 0000H                                                  |

|                                       | 8-bit A/D conversion result register (ADCRH)                              | 00H                                                    |

|                                       | Mode register (ADM)                                                       | 00H                                                    |

|                                       | Analog input channel specification register (ADS)                         | 00H                                                    |

|                                       | A/D port configuration register (ADPC)                                    | 00H                                                    |

| Serial interface UART0                | Receive buffer register 0 (RXB0)                                          | FFH                                                    |

|                                       | Transmit shift register 0 (TXS0)                                          | FFH                                                    |

|                                       | Asynchronous serial interface operation mode register 0 (ASIM0)           | 01H                                                    |

|                                       | Asynchronous serial interface reception error status register 0 (ASIS0)   | 00H                                                    |

|                                       | Baud rate generator control register 0 (BRGC0)                            | 1FH                                                    |

**Notes 1.** During reset signal generation or oscillation stabilization time wait, only the PC contents among the hardware statuses become undefined. All other hardware statuses remain unchanged after reset.

- 2. 8-bit timer H1 only.

- 3. The reset value of WDTE is determined by the option byte setting.

- Remark The special function register (SFR) mounted depend on the product. See 3.2.3 Special function registers (SFRs).

### (3) 0084H/1084H

- O On-chip debug operation control

- Disabling on-chip debug operation

- Enabling on-chip debug operation and erasing data of the flash memory in case authentication of the on-chip debug security ID fails

- Enabling on-chip debug operation and not erasing data of the flash memory even in case authentication of the on-chip debug security ID fails

- Cautions 1. Be sure to set 00H (disabling on-chip debug operation) to 0084H for products not equipped with the on-chip debug function (µPD78F05xx and 78F05xxA). Also set 00H to 1084H because 0084H and 1084H are switched during the boot operation.

- 2. To use the on-chip debug function with a product equipped with the on-chip debug function  $(\mu PD78F05xxD \text{ and } 78F05xxDA)$ , set 02H or 03H to 0084H. Set a value that is the same as that of 0084H to 1084H because 0084H and 1084H are switched during the boot operation.

### 26.2 Format of Option Byte

The format of the option byte is shown below.

### 27.6.1 FLMD0 pin

In the normal operation mode, 0 V is input to the FLMD0 pin. In the flash memory programming mode, the V<sub>DD</sub> write voltage is supplied to the FLMD0 pin. An FLMD0 pin connection example is shown below.

### 27.6.2 Serial interface pins

The pins used by each serial interface are listed below.

#### Table 27-5. Pins Used by Each Serial Interface

| Serial Interface | Pins Used         |

|------------------|-------------------|

| CSI10            | SO10, SI10, SCK10 |

| UART6            | TxD6, RxD6        |

To connect the dedicated flash memory programmer to the pins of a serial interface that is connected to another device on the board, care must be exercised so that signals do not collide or that the other device does not malfunction.

### Caution The pins mounted depend on the product. Refer to Caution at the beginning of this chapter.

| Parameter              | Symbol | Conditions                                                                                                                                                          | Ratings                                                                                    | Unit |

|------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------|

| Supply voltage         | VDD    |                                                                                                                                                                     | –0.5 to +6.5                                                                               | V    |

|                        | EVDD   |                                                                                                                                                                     | –0.5 to +6.5                                                                               | V    |

|                        | Vss    |                                                                                                                                                                     | –0.5 to +0.3                                                                               | V    |

|                        | EVss   |                                                                                                                                                                     | –0.5 to +0.3                                                                               | v    |

|                        | AVREF  |                                                                                                                                                                     | -0.5 to V <sub>DD</sub> + 0.3 <sup>Note</sup>                                              | V    |

|                        | AVss   |                                                                                                                                                                     | -0.5 to +0.3                                                                               | V    |

| REGC pin input voltage | VIREGC |                                                                                                                                                                     | –0.5 to +3.6 and –0.5 to $V_{\text{DD}}$                                                   | V    |

| Input voltage          | VII    | P00 to P06, P10 to P17, P20 to P27, P30<br>to P33, P40 to P47, P50 to P57, P64 to<br>P67, P70 to P77, P120 to P124, P140 to<br>P145, X1, X2, XT1, XT2, RESET, FLMD0 | -0.3 to V <sub>DD</sub> + 0.3 <sup>Note</sup>                                              | V    |

|                        | VI2    | P60 to P63 (N-ch open drain)                                                                                                                                        | –0.3 to +6.5                                                                               | v    |

| Output voltage         | Vo     |                                                                                                                                                                     | -0.3 to V <sub>DD</sub> + 0.3 <sup>Note</sup>                                              | V    |

| Analog input voltage   | Van    | ANI0 to ANI7                                                                                                                                                        | $-0.3$ to AV <sub>REF</sub> + $0.3^{Note}$<br>and $-0.3$ to V <sub>DD</sub> + $0.3^{Note}$ | V    |

## Absolute Maximum Ratings (T<sub>A</sub> = 25°C) (1/2)

Note Must be 6.5 V or lower.

- Caution Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

- Remark Unless specified otherwise, the characteristics of alternate-function pins are the same as those of port pins.

### Caution The pins mounted depend on the product. Refer to Caution at the beginning of this chapter.

| Parameter                                                   | Symbol        | Conditions                            | MIN.                              | TYP. | MAX. | Unit |

|-------------------------------------------------------------|---------------|---------------------------------------|-----------------------------------|------|------|------|

| SCK1n cycle time                                            | tKCY1         | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ | 200                               |      |      | ns   |

|                                                             |               | $2.7~V \leq V_{\text{DD}} < 4.0~V$    | 400                               |      |      | ns   |

| SCK1n high-/low-level width                                 | tкнı,<br>tк∟ı | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ | tkcy1/2 –<br>20 <sup>Note 1</sup> |      |      | ns   |

|                                                             |               | $2.7~V \leq V_{\text{DD}} < 4.0~V$    | tксү1/2 —<br>30 <sup>Note 1</sup> |      |      | ns   |

| SI1n setup time (to SCK1n↑)                                 | tsiĸ1         | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ | 70                                |      |      | ns   |

|                                                             |               | $2.7~V \leq V_{\text{DD}} < 4.0~V$    | 100                               |      |      | ns   |

| SI1n hold time (from SCK1n↑)                                | tksi1         |                                       | 30                                |      |      | ns   |

| Delay time from $\overline{SCK1n}\downarrow$ to SO1n output | tkso1         | $C = 50 \text{ pF}^{Note 2}$          |                                   |      | 40   | ns   |

## (d) CSI1n (master mode, SCK1n... internal clock output)

Notes 1. This value is when high-speed system clock  $(f_{XH})$  is used.

**2.** C is the load capacitance of the  $\overline{\text{SCK1n}}$  and SO1n output lines.

# (e) CSI1n (slave mode, SCK1n... external clock input)

| Parameter                                                   | Symbol | Conditions                        | MIN.    | TYP. | MAX. | Unit |

|-------------------------------------------------------------|--------|-----------------------------------|---------|------|------|------|

| SCK1n cycle time                                            | tксү2  |                                   | 400     |      |      | ns   |

| SCK1n high-/low-level width                                 | tкн2,  |                                   | tксү2/2 |      |      | ns   |

|                                                             | tĸl2   |                                   |         |      |      |      |

| SI1n setup time (to SCK1n↑)                                 | tsik2  |                                   | 80      |      |      | ns   |

| SI1n hold time (from SCK1n <sup>↑</sup> )                   | tksi2  |                                   | 50      |      |      | ns   |

| Delay time from $\overline{SCK1n}\downarrow$ to SO1n output | tkso2  | $C = 50 \text{ pF}^{\text{Note}}$ |         |      | 120  | ns   |

**Note** C is the load capacitance of the SO1n output line.

**Remark** n = 0, 1

|            | _              |                              |                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (21/30                                                                                                                                                                                                                                                         |          |

|------------|----------------|------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Chapter    | Classification | Function                     | Details of Function                                               | Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page                                                                                                                                                                                                                                                           |          |

| Chapter 17 | Soft           | Serial<br>interface<br>CSIA0 | Automatic<br>transmission/<br>reception suspension<br>and restart | If the HALT instruction is executed during automatic transmission/reception, communication is suspended and the HALT mode is set if during 8-bit data communication. When the HALT mode is cleared, automatic transmission/reception is restarted from the suspended point.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                |          |

|            |                |                              | -                                                                 | When suspending automatic transmission/reception, do not change the operating mode to 3-wire serial I/O mode while TSF0 = 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | p. 544 🗋                                                                                                                                                                                                                                                       |          |

|            |                |                              | Busy control option                                               | Busy control cannot be used simultaneously with the interval time control function of automatic data transfer interval specification register 0 (ADTI0).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                |          |

|            |                |                              | Busy & strobe control<br>option                                   | When TSF0 is cleared, the SOA0 pin goes low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | p. 547 🗌                                                                                                                                                                                                                                                       |          |

| Chapter 18 | Soft           | Serial<br>interface<br>IIC0  | -                                                                 | Do not use serial interface IIC0 and the multiplier/divider simultaneously, because various flags corresponding to interrupt request sources are shared among serial interface IIC0 and the multiplier/divider.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | p. 550 🗌                                                                                                                                                                                                                                                       |          |

| Ċ          |                |                              | IIC0: IIC shift register                                          | Do not write data to IIC0 during data transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | р. 553 🗌                                                                                                                                                                                                                                                       |          |

|            |                |                              | 0                                                                 | Write or read IIC0 only during the wait period. Accessing IIC0 in a communication state other than during the wait period is prohibited. When the device serves as the master, however, IIC0 can be written only once after the communication trigger bit (STT0) is set to 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | p. 553 🗌                                                                                                                                                                                                                                                       |          |

|            |                |                              |                                                                   | When communication is reserved, write data to the IIC0 register after the interrupt triggered by a stop condition is detected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | p. 553 🗌                                                                                                                                                                                                                                                       |          |

|            |                |                              | IICC0: IIC control register 0                                     | If the operation of $I^2C$ is enabled (IICE0 = 1) when the SCL0 line is high level, the SDA0 line is low level, and the digital filter is turned on (DFC0 of the IICCL0 register = 1), a start condition will be inadvertently detected immediately. In this case, set (1) the LREL0 bit by using a 1-bit memory manipulation instruction immediately after enabling operation of $I^2C$ (IICE0 = 1).                                                                                                                                                                                                                                                                                                                                                                           | p. 557 🗆                                                                                                                                                                                                                                                       |          |

|            |                |                              |                                                                   | When bit 3 (TRC0) of the IIC status register 0 (IICS0) is set to 1 (transmission status), bit 5 (WREL0) of the IICC0 register is set to 1 during the ninth clock and wait is canceled, after which the TRC0 bit is cleared (reception status) and the SDAA0 line is set to high impedance. Release the wait performed while the TRC bit is 1 (transmission status) by writing to the IIC shift register.                                                                                                                                                                                                                                                                                                                                                                        | p. 560 🗆                                                                                                                                                                                                                                                       |          |

|            |                |                              | IICS0: IIC status<br>register 0                                   | If data is read from IICS0 register, a wait cycle is generated. Do not read data from IICS0 register when the peripheral hardware clock (fPRs) is stopped. For details, see CHAPTER 36 CAUTIONS FOR WAIT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | p. 561 🗆                                                                                                                                                                                                                                                       |          |

|            |                |                              |                                                                   | Write to STCEN bit only when the operation is stopped (IICE0 = 0).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | р. 564 🗌                                                                                                                                                                                                                                                       |          |

|            |                |                              | 0                                                                 | As the bus release status (IICBSY = 0) is recognized regardless of the actual bus status when STCEN = 1, when generating the first start condition (STT0 = 1), it is necessary to verify that no third party communications are in progress in order to prevent such communications from being destroyed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | p. 564 🗆                                                                                                                                                                                                                                                       |          |

|            |                |                              |                                                                   | Write to IICRSV bit only when the operation is stopped (IICE0 = 0).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | p. 564 🗆                                                                                                                                                                                                                                                       |          |

|            |                |                              |                                                                   | Selection clock setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Determine the transfer clock frequency of I <sup>2</sup> C by using CLX0, SMC0, CL01, and CL00 before enabling the operation (by setting bit 7 (IICE0) of IIC control register 0 (IICC0) to 1). To change the transfer clock frequency, clear IICE0 once to 0. | p. 567 ∟ |

|            |                |                              | When<br>STCEN = 0                                                 | <ul> <li>Immediately after I<sup>2</sup>C operation is enabled (IICE0 = 1), the bus communication status (IICBSY (bit 6 of IICF0) = 1) is recognized regardless of the actual bus status. When changing from a mode in which no stop condition has been detected to a master device communication mode, first generate a stop condition to release the bus, then perform master device communication.</li> <li>When using multiple masters, it is not possible to perform master device communication has not been detected).</li> <li>Use the following sequence for generating a stop condition.</li> <li>Set IIC clock selection register 0 (IICCL0).</li> <li>Set bit 7 (IICE0) of IIC control register 0 (IICC0) to 1.</li> <li>Set bit 0 (SPT0) of IICC0 to 1.</li> </ul> | p. 584 🗆                                                                                                                                                                                                                                                       |          |

|            |                |                              | When<br>STCEN = 1                                                 | Immediately after $l^2C$ operation is enabled (IICE0 = 1), the bus released status (IICBSY = 0) is recognized regardless of the actual bus status. To generate the first start condition (STT0 (bit 1 of IIC control register 0 (IICC0)) = 1), it is necessary to confirm that the bus has been released, so as to not disturb other communications.                                                                                                                                                                                                                                                                                                                                                                                                                            | p. 584 🗌                                                                                                                                                                                                                                                       |          |

| r          |                |                            | Γ                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (25            | 5/30) |

|------------|----------------|----------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------|

| Chapter    | Classification | Function                   | Details of<br>Function                                        | Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Pag            | e     |

| Chapter 22 | Hard           | Standby<br>function        | OSTS:<br>Oscillation<br>stabilization time<br>select register | The X1 clock oscillation stabilization wait time does not include the time until clock oscillation starts ("a" below).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | p. 669         |       |

|            | Soft           |                            | STOP mode                                                     | Because the interrupt request signal is used to clear the standby mode, if there is an interrupt source with the interrupt request flag set and the interrupt mask flag reset, the standby mode is immediately cleared if set. Thus, the STOP mode is reset to the HALT mode immediately after execution of the STOP instruction and the system returns to the operating mode as soon as the wait time set using the oscillation stabilization time select register (OSTS) has elapsed.                                                                                                                                                                                                                                                                                                                                                                                                                                                             | p. 674         |       |

|            |                |                            |                                                               | To use the peripheral hardware that stops operation in the STOP mode, and the peripheral hardware for which the clock that stops oscillating in the STOP mode after the STOP mode is released, restart the peripheral hardware.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | p. 676         |       |