Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detalls                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | 78K/0                                                                                 |

| Core Size                  | 8-Bit                                                                                 |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                                    |

| Number of I/O              | 71                                                                                    |

| Program Memory Size        | 96KB (96K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 5K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 8x10b                                                                             |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 80-LQFP                                                                               |

| Supplier Device Package    | -                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0546agk-gak-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.2 Description of Pin Functions

Remark The pins mounted depend on the product. See 1.4 Ordering Information and 2.1 Pin Function List.

#### 2.2.1 P00 to P06 (port 0)

P00 to P06 function as an I/O port. These pins also function as timer I/O, serial interface data I/O, clock I/O, and chip select input.

|                 | 78K0/KB2 | 78K0/KC2 | 78K0/KD2            | 78K0                                                       | /KE2                                                      | 78K0/KF2 |

|-----------------|----------|----------|---------------------|------------------------------------------------------------|-----------------------------------------------------------|----------|

|                 |          |          |                     | Products<br>whose flash<br>memory is<br>less than<br>32 KB | Products<br>whose flash<br>memory is at<br>least<br>48 KB |          |

| P00/TI000       | ν        |          | $\checkmark$        | $\checkmark$                                               | $\checkmark$                                              |          |

| P01/TI010/TO00  | 1        | V        | $\checkmark$        | $\checkmark$                                               | $\checkmark$                                              |          |

| P02/SO11        | -        | -        | P02 <sup>Note</sup> | P02 <sup>Note</sup>                                        | $\checkmark$                                              |          |

| P03/SI11        | -        | _        | P03 <sup>Note</sup> | P03 <sup>Note</sup>                                        | √                                                         |          |

| P04/SCK11       | _        |          | _                   | P04 <sup>Note</sup>                                        | ν                                                         |          |

| P05/TI001/SSI11 | -        |          | _                   | P05 <sup>Note</sup>                                        | ١                                                         | I        |

| P06/TI011/TO01  | =        | -        | -                   | P06 <sup>Note</sup>                                        | ١                                                         | l        |

**Note** The 78K0/KE2 products whose flash memory is less than 32 KB and 78K0/KD2 products are only provided with port functions and not alternate functions.

#### **Remark** $\sqrt{:}$ Mounted, -: Not mounted

The following operation modes can be specified in 1-bit units.

#### (1) Port mode

P00 to P06 function as an I/O port. P00 to P06 can be set to input or output port in 1-bit units using port mode register 0 (PM0). Use of an on-chip pull-up resistor can be specified by pull-up resistor option register 0 (PU0).

#### (2) Control mode

P00 to P06 function as timer I/O, serial interface data I/O, clock I/O, and chip select input.

#### (a) TI000, TI001

These are the pins for inputting an external count clock to 16-bit timer/event counters 00 and 01 and are also for inputting a capture trigger signal to the capture registers (CR000, CR010 or CR001, CR011) of 16-bit timer/event counters 00 and 01.

#### (b) TI010, TI011

These are the pins for inputting a capture trigger signal to the capture register (CR000 or CR001) of 16-bit timer/event counters 00 and 01.

#### (c) TO00, TO01

These are timer output pins of 16-bit timer/event counters 00 and 01.

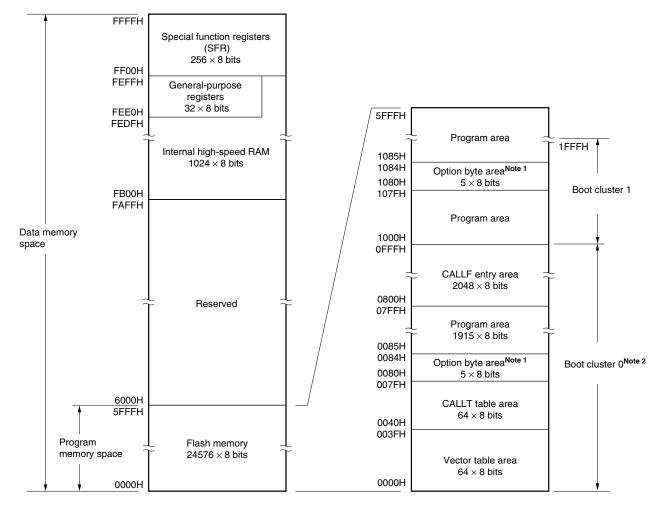

# Figure 3-3. Memory Map (*μ*PD78F0502, 78F0502A, 78F0512, 78F0512A, 78F0522, 78F0522A, 78F0532A, and 78F0532A)

Notes 1. When boot swap is not used: Set the option bytes to 0080H to 0084H.

When boot swap is used: Set the option bytes to 0080H to 0084H and 1080H to 1084H.

- 2. Writing boot cluster 0 can be prohibited depending on the setting of security (see 27.8 Security Settings).

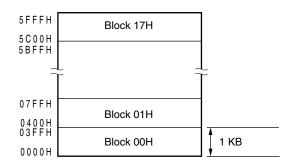

- **Remark** The flash memory is divided into blocks (one block = 1 KB). For the address values and block numbers, see **Table 3-3 Correspondence Between Address Values and Block Numbers in Flash Memory**.

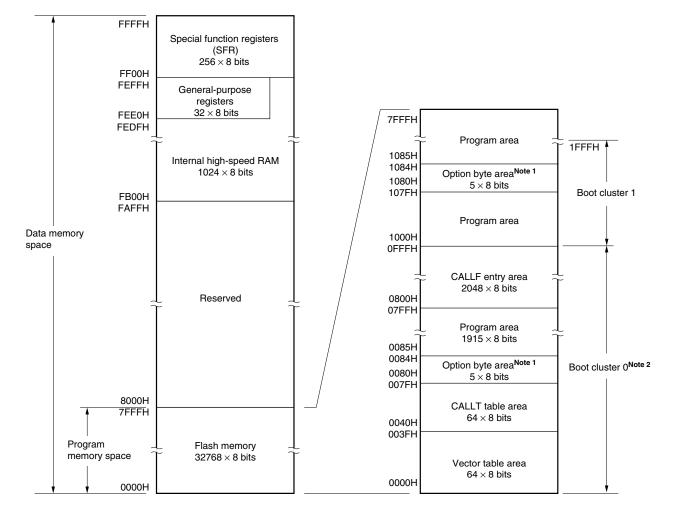

## Figure 3-4. Memory Map (µPD78F0503, 78F0503A, 78F0513, 78F0513A, 78F0523, 78F0523A, 78F0533 and 78F0533A)

Notes 1. When boot swap is not used: Set the option bytes to 0080H to 0084H.

When boot swap is used: Set the option bytes to 0080H to 0084H and 1080H to 1084H.

- 2. Writing boot cluster 0 can be prohibited depending on the setting of security (see 27.8 Security Settings).

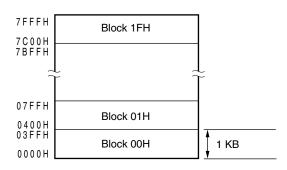

- RemarkThe flash memory is divided into blocks (one block = 1 KB). For the address values and block numbers, seeTable 3-3Correspondence Between Address Values and Block Numbers in Flash Memory.

#### (8) Oscillation stabilization time select register (OSTS)

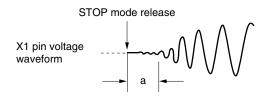

This register is used to select the X1 clock oscillation stabilization wait time when the STOP mode is released. When the X1 clock is selected as the CPU clock, the operation waits for the time set using OSTS after the STOP mode is released.

When the internal high-speed oscillation clock is selected as the CPU clock, confirm with OSTC that the desired oscillation stabilization time has elapsed after the STOP mode is released. The oscillation stabilization time can be checked up to the time set using OSTC.

OSTS can be set by an 8-bit memory manipulation instruction.

Reset signal generation sets OSTS to 05H.

#### Figure 6-11. Format of Oscillation Stabilization Time Select Register (OSTS)

Address: FFA4H After reset: 05H R/W Symbol 5 2 0 7 6 4 З 1 OSTS 0 0 0 0 0 OSTS2 OSTS1 OSTS0

| OSTS2 | OSTS1         | OSTS0 | Oscillation stabilization time selection |                  |                  |  |

|-------|---------------|-------|------------------------------------------|------------------|------------------|--|

|       |               |       |                                          | fx = 10 MHz      | fx = 20 MHz      |  |

| 0     | 0             | 1     | 2 <sup>11</sup> /fx                      | 204.8 μs         | 102.4 <i>µ</i> s |  |

| 0     | 1             | 0     | 2 <sup>13</sup> /fx                      | 819.2 <i>μ</i> s | 409.6 <i>µ</i> s |  |

| 0     | 1             | 1     | 2 <sup>14</sup> /fx                      | 1.64 ms          | 819.2 <i>µ</i> s |  |

| 1     | 0             | 0     | 2 <sup>15</sup> /fx                      | 3.27 ms          | 1.64 ms          |  |

| 1     | 0             | 1     | 2 <sup>16</sup> /fx                      | 6.55 ms          | 3.27 ms          |  |

| 0     | ther than abo | ve    | Setting prohibited                       |                  |                  |  |

| Cautions 1. | To set the STOP mode when the X1 clock is used as the CPU clock, set OSTS before |

|-------------|----------------------------------------------------------------------------------|

|             | executing the STOP instruction.                                                  |

- 2. Do not change the value of the OSTS register during the X1 clock oscillation stabilization time.

- 3. The oscillation stabilization time counter counts up to the oscillation stabilization time set by OSTS. If the STOP mode is entered and then released while the internal high-speed oscillation clock is being used as the CPU clock, set the oscillation stabilization time as follows.

- Desired OSTC oscillation stabilization time ≤ Oscillation stabilization time set by OSTS

Note, therefore, that only the status up to the oscillation stabilization time set by OSTS is set to OSTC after STOP mode is released.

4. The X1 clock oscillation stabilization wait time does not include the time until clock oscillation starts ("a" below).

Remark fx: X1 clock oscillation frequency

## 6.6.7 Condition before changing CPU clock and processing after changing CPU clock

Condition before changing the CPU clock and processing after changing the CPU clock are shown below.

|                              | CPU                                                            | Clock                                           | Condition Before Change                                                                                                                                                                                       | Processing After Change                                                                                                                                                                                                                                              |  |  |

|------------------------------|----------------------------------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| _                            | Before Change                                                  | After Change                                    |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                      |  |  |

| KB2,<br>KC2,<br>KD2,<br>KE2, | Internal high-<br>speed<br>oscillation<br>clock                | X1 clock                                        | <ul> <li>Stabilization of X1 oscillation</li> <li>MSTOP = 0, OSCSEL = 1, EXCLK = 0</li> <li>After elapse of oscillation stabilization time</li> </ul>                                                         | <ul> <li>Internal high-speed oscillator can be stopped (RSTOP = 1).</li> <li>Clock supply to CPU is stopped for 4.06 to 16.12 μs after AMPH has been set to 1.</li> </ul>                                                                                            |  |  |

| KF2                          |                                                                | External main<br>system clock                   | Enabling input of external clock from<br>EXCLK pin<br>• MSTOP = 0, OSCSEL = 1, EXCLK = 1                                                                                                                      | <ul> <li>Internal high-speed oscillator can be<br/>stopped (RSTOP = 1).</li> <li>Clock supply to CPU is stopped for the<br/>duration of 160 external clocks from the<br/>EXCLK pin after AMPH has been set to 1.</li> </ul>                                          |  |  |

|                              | X1 clock                                                       | Internal high-                                  | Oscillation of internal high-speed oscillator                                                                                                                                                                 | X1 oscillation can be stopped (MSTOP = 1).                                                                                                                                                                                                                           |  |  |

|                              | External main system clock                                     | speed<br>oscillation<br>clock                   | • RSTOP = 0                                                                                                                                                                                                   | External main system clock input can be disabled (MSTOP = 1).                                                                                                                                                                                                        |  |  |

| KC2,<br>KD2,<br>KE2,<br>KF2  | KD2, speed<br>KE2, oscillation<br>KF2 clock<br>(other X1 clock |                                                 | Stabilization of XT1 oscillation<br>• XTSTART = 0, EXCLKS = 0,<br>OSCSELS = 1, or XTSTART = 1<br>• After elapse of oscillation stabilization                                                                  | Operating current can be reduced by<br>stopping internal high-speed oscillator<br>(RSTOP = 1).                                                                                                                                                                       |  |  |

| `                            |                                                                |                                                 | time                                                                                                                                                                                                          | X1 oscillation can be stopped (MSTOP = 1).                                                                                                                                                                                                                           |  |  |

| than<br>KB2)                 | External main<br>system clock                                  |                                                 |                                                                                                                                                                                                               | External main system clock input can be disabled (MSTOP = 1).                                                                                                                                                                                                        |  |  |

|                              | Internal high-<br>speed<br>oscillation<br>clock                | External<br>subsystem<br>clock                  | Enabling input of external clock from<br>EXCLKS pin<br>• XTSTART = 0, EXCLKS = 1,<br>OSCSELS = 1                                                                                                              | Operating current can be reduced by<br>stopping internal high-speed oscillator<br>(RSTOP = 1).                                                                                                                                                                       |  |  |

|                              | X1 clock                                                       |                                                 |                                                                                                                                                                                                               | X1 oscillation can be stopped (MSTOP = 1).                                                                                                                                                                                                                           |  |  |

|                              | External main system clock                                     |                                                 |                                                                                                                                                                                                               | External main system clock input can be disabled (MSTOP = 1).                                                                                                                                                                                                        |  |  |

|                              | XT1 clock,<br>external<br>subsystem<br>clock                   | Internal high-<br>speed<br>oscillation<br>clock | Oscillation of internal high-speed oscillator<br>and selection of internal high-speed<br>oscillation clock as main system clock<br>• RSTOP = 0, MCS = 0                                                       | XT1 oscillation can be stopped or external<br>subsystem clock input can be disabled<br>(OSCSELS = 0).                                                                                                                                                                |  |  |

|                              |                                                                | X1 clock                                        | Stabilization of X1 oscillation and<br>selection of high-speed system clock as<br>main system clock<br>• MSTOP = 0, OSCSEL = 1, EXCLK = 0<br>• After elapse of oscillation stabilization<br>time<br>• MCS = 1 | <ul> <li>XT1 oscillation can be stopped or<br/>external subsystem clock input can be<br/>disabled (OSCSELS = 0).</li> <li>Clock supply to CPU is stopped for 4.06 to<br/>16.12 µs after AMPH has been set to 1.</li> </ul>                                           |  |  |

|                              |                                                                | External main<br>system clock                   | Enabling input of external clock from<br>EXCLK pin and selection of high-speed<br>system clock as main system clock<br>• MSTOP = 0, OSCSEL = 1, EXCLK = 1<br>• MCS = 1                                        | <ul> <li>XT1 oscillation can be stopped or<br/>external subsystem clock input can be<br/>disabled (OSCSELS = 0).</li> <li>Clock supply to CPU is stopped for the<br/>duration of 160 external clocks from the<br/>EXCLK pin after AMPH has been set to 1.</li> </ul> |  |  |

## Table 6-7. Changing CPU Clock

**Remark** The 78K0/KB2 is not provided with a subsystem clock.

#### (9) Capture operation

#### (a) When valid edge of TI00n is specified as count clock

When the valid edge of TI00n is specified as the count clock, the capture register for which TI00n is specified as a trigger does not operate correctly.

#### (b) Pulse width to accurately capture value by signals input to TI01n and TI00n pins

To accurately capture the count value, the pulse input to the TI00n and TI01n pins as a capture trigger must be wider than two count clocks selected by PRM0n (see **Figure 7-9**).

#### (c) Generation of interrupt signal

The capture operation is performed at the falling edge of the count clock but the interrupt signals (INTTM00n and INTTM01n) are generated at the rising edge of the next count clock (see **Figure 7-9**).

#### (d) Note when CRC0n1 (bit 1 of capture/compare control register 0n (CRC0n)) is set to 1

When the count value of the TM0n register is captured to the CR00n register in the phase reverse to the signal input to the TI00n pin, the interrupt signal (INTTM00n) is not generated after the count value is captured. If the valid edge is detected on the TI01n pin during this operation, the capture operation is not performed but the INTTM00n signal is generated as an external interrupt signal. Mask the INTTM00n signal when the external interrupt is not used.

#### (10) Edge detection

#### (a) Specifying valid edge after reset

If the operation of the 16-bit timer/event counter 0n is enabled after reset and while the TI00n or TI01n pin is at high level and when the rising edge or both the edges are specified as the valid edge of the TI00n or TI01n pin, then the high level of the TI00n or TI01n pin is detected as the rising edge. Note this when the TI00n or TI01n pin is pulled up. However, the rising edge is not detected when the operation is once stopped and then enabled again.

#### (b) Sampling clock for eliminating noise

The sampling clock for eliminating noise differs depending on whether the valid edge of TI00n is used as the count clock or capture trigger. In the former case, the sampling clock is fixed to fPRs. In the latter, the count clock selected by PRM0n is used for sampling.

When the signal input to the TI00n pin is sampled and the valid level is detected two times in a row, the valid edge is detected. Therefore, noise having a short pulse width can be eliminated (see **Figure 7-9**).

#### (11) Timer operation

The signal input to the TI00n/TI01n pin is not acknowledged while the timer is stopped, regardless of the operation mode of the CPU.

Remarks 1. fPRs: Peripheral hardware clock frequency

- n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

- n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

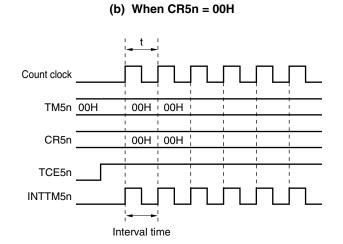

## Figure 8-11. Interval Timer Operation Timing (2/2)

**Remark** n = 0, 1

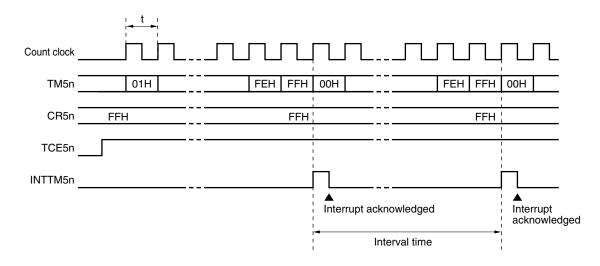

#### 8.4.3 Square-wave output operation

A square wave with any selected frequency is output at intervals determined by the value preset to 8-bit timer compare register 5n (CR5n).

The TO5n pin output status is inverted at intervals determined by the count value preset to CR5n by setting bit 0 (TOE5n) of 8-bit timer mode control register 5n (TMC5n) to 1. This enables a square wave with any selected frequency to be output (duty = 50%).

### Setting

<1> Set each register.

- Clear the port output latch (P17 or P33)<sup>Note</sup> and port mode register (PM17 or PM33)<sup>Note</sup> to 0.

- TCL5n: Select the count clock.

- CR5n: Compare value

- TMC5n: Stop the count operation, select the mode in which clear & start occurs on a match of TM5n and CR5n.

| LVS5n | LVR5n | Timer Output F/F Status Setting                                      |

|-------|-------|----------------------------------------------------------------------|

| 0     | 1     | Timer output F/F clear (0) (default value of TO5n output: low level) |

| 1     | 0     | Timer output F/F set (1) (default value of TO5n output: high level)  |

Timer output enabled

(TMC5n = 00001011B or 00000111B)

- <2> After TCE5n = 1 is set, the count operation starts.

- <3> The timer output F/F is inverted by a match of TM5n and CR5n. After INTTM5n is generated, TM5n is cleared to 00H.

- <4> After these settings, the timer output F/F is inverted at the same interval and a square wave is output from TO5n. The frequency is as follows.

- Frequency = 1/2t (N + 1) (N: 00H to FFH)

- Note 8-bit timer/event counter 50: P17, PM17 8-bit timer/event counter 51: P33, PM33

#### Caution Do not write other values to CR5n during operation.

**Remarks 1.** For how to enable the INTTM5n signal interrupt, see **CHAPTER 20 INTERRUPT FUNCTIONS**. **2.** n = 0, 1

#### (3) SO latch

The SO latch is used to retain the SDA0 pin's output level.

#### (4) Wake-up controller

This circuit generates an interrupt request (INTIIC0) when the address received by this register matches the address value set to slave address register 0 (SVA0) or when an extension code is received.

### (5) Prescaler

This selects the sampling clock to be used.

#### (6) Serial clock counter

This counter counts the serial clocks that are output or input during transmit/receive operations and is used to verify that 8-bit data was transmitted or received.

#### (7) Interrupt request signal generator

This circuit controls the generation of interrupt request signals (INTIIC0).

- An I<sup>2</sup>C interrupt request is generated by the following two triggers.

- Falling edge of eighth or ninth clock of the serial clock (set by WTIM0 bit)

- Interrupt request generated when a stop condition is detected (set by SPIE0 bit)

Remark WTIM0 bit: Bit 3 of IIC control register 0 (IICC0) SPIE0 bit: Bit 4 of IIC control register 0 (IICC0)

#### (8) Serial clock controller

In master mode, this circuit generates the clock output via the SCL0 pin from a sampling clock.

### (9) Serial clock wait controller

This circuit controls the wait timing.

(10) ACK generator, stop condition detector, start condition detector, and ACK detector These circuits generate and detect each status.

#### (11) Data hold time correction circuit

This circuit generates the hold time for data corresponding to the falling edge of the serial clock.

### (12) Start condition generator

This circuit generates a start condition when the STT0 bit is set to 1. However, in the communication reservation disabled status (IICRSV bit = 1), when the bus is not released (IICBSY bit = 1), start condition requests are ignored and the STCF bit is set to 1.

### (13) Stop condition generator

This circuit generates a stop condition when the SPT0 bit is set to 1.

## 18.3 Registers to Control Serial Interface IIC0

Serial interface IIC0 is controlled by the following seven registers.

- IIC control register 0 (IICC0)

- IIC flag register 0 (IICF0)

- IIC status register 0 (IICS0)

- IIC clock selection register 0 (IICCL0)

- IIC function expansion register 0 (IICX0)

- Port mode register 6 (PM6)

- Port register 6 (P6)

#### (1) IIC control register 0 (IICC0)

This register is used to enable/stop I<sup>2</sup>C operations, set wait timing, and set other I<sup>2</sup>C operations.

IICC0 register is set by a 1-bit or 8-bit memory manipulation instruction. However, set the SPIE0, WTIM0, and ACKE0 bits while IICE0 bit = 0 or during the wait period. These bits can be set at the same time when the IICE0 bit is set from "0" to "1".

Reset signal generation clears IICC0 to 00H.

| Address | : FFABH   | After re                  | set: 00H                                             | R/W <sup>Note</sup> | 1 |                                                                                                                                  |                |           |    |  |  |

|---------|-----------|---------------------------|------------------------------------------------------|---------------------|---|----------------------------------------------------------------------------------------------------------------------------------|----------------|-----------|----|--|--|

| Symbol  | <7>       | <6>                       | 5                                                    | 4                   | 3 | 2                                                                                                                                | <1>            | <0>       |    |  |  |

| IICF0   | STCF      | IICBSY                    | 0                                                    | 0                   | 0 | 0                                                                                                                                | STCEN          | IICRSV    |    |  |  |

|         |           |                           |                                                      |                     |   |                                                                                                                                  |                |           |    |  |  |

|         | STCF      |                           |                                                      | STT0 clear flag     |   |                                                                                                                                  |                |           |    |  |  |

|         | 0         | Generate                  | te start condition                                   |                     |   |                                                                                                                                  |                |           |    |  |  |

|         | 1         | Start cond                | t condition generation unsuccessful: clear STT0 flag |                     |   |                                                                                                                                  |                |           |    |  |  |

|         | Condition | n for clearin             | g (STCF =                                            | 0)                  |   | Conditio                                                                                                                         | on for setting | g (STCF = | 1) |  |  |

|         |           | d by STT0<br>IICE0 = 0 (o |                                                      | top)                |   | Generating start condition unsuccessful and STT0<br>bit cleared to 0 when communication reservation is<br>disabled (IICRSV = 1). |                |           |    |  |  |

#### Figure 18-7. Format of IIC Flag Register 0 (IICF0)

| IICBSY    | l <sup>2</sup> C bus status flag                                       |                                                                                               |  |

|-----------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|

| 0         | Bus release status (communication initial status when STCEN = 1)       |                                                                                               |  |

| 1         | Bus communication status (communication initial status when STCEN = 0) |                                                                                               |  |

| Condition | n for clearing (IICBSY = 0)                                            | Condition for setting (IICBSY = 1)                                                            |  |

| 1         | ion of stop condition<br>IICE0 = 0 (operation stop)                    | <ul> <li>Detection of start condition</li> <li>Setting of IICE0 bit when STCEN = 0</li> </ul> |  |

| STCEN                                     | Initial s                                                         | Initial start enable trigger                                                                                       |  |  |  |

|-------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0                                         | After operation is enabled (IICE0 = 1), enabled a stop condition. | ble generation of a start condition upon detection of                                                              |  |  |  |

| 1                                         | After operation is enabled (IICE0 = 1), enable a stop condition.  | After operation is enabled (IICE0 = 1), enable generation of a start condition without detecting a stop condition. |  |  |  |

| Condition                                 | for clearing (STCEN = 0)                                          | Condition for setting (STCEN = 1)                                                                                  |  |  |  |

| <ul><li>Detection</li><li>Reset</li></ul> | on of start condition                                             | Set by instruction                                                                                                 |  |  |  |

| IICRSV                                  | Communication re                  | eservation function disable bit    |  |

|-----------------------------------------|-----------------------------------|------------------------------------|--|

| 0                                       | Enable communication reservation  |                                    |  |

| 1                                       | Disable communication reservation |                                    |  |

| Condition                               | for clearing (IICRSV = 0)         | Condition for setting (IICRSV = 1) |  |

| <ul><li>Cleared</li><li>Reset</li></ul> | by instruction                    | Set by instruction                 |  |

**Note** Bits 6 and 7 are read-only.

Cautions 1. Write to STCEN bit only when the operation is stopped (IICE0 = 0).

- As the bus release status (IICBSY = 0) is recognized regardless of the actual bus status when STCEN = 1, when generating the first start condition (STT0 = 1), it is necessary to verify that no third party communications are in progress in order to prevent such communications from being destroyed.

- 3. Write to IICRSV bit only when the operation is stopped (IICE0 = 0).

Remark STT0: Bit 1 of IIC control register 0 (IICC0) IICE0: Bit 7 of IIC control register 0 (IICC0)

| Address: FF                                                                                                                                                              | E4H After r | eset: FFH     | R/W                         |        |                         |                             |                         |                                 |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------|-----------------------------|--------|-------------------------|-----------------------------|-------------------------|---------------------------------|--|--|

| Symbol                                                                                                                                                                   | <7>         | <6>           | <5>                         | <4>    | <3>                     | <2>                         | <1>                     | <0>                             |  |  |

| MK0L                                                                                                                                                                     | SREMK6      | PMK5          | PMK4                        | PMK3   | PMK2                    | PMK1                        | PMK0                    | LVIMK                           |  |  |

| Address: FF                                                                                                                                                              | E5H After r | eset: FFH     | R/W                         |        |                         |                             |                         |                                 |  |  |

| Symbol                                                                                                                                                                   | <7>         | <6>           | <5>                         | <4>    | <3>                     | <2>                         | <1>                     | <0>                             |  |  |

| МКОН                                                                                                                                                                     | TMMK010     | ТММК000       | TMMK50                      | ТММКНО | TMMKH1                  | DUALMK0<br>CSIMK10<br>STMK0 | STMK6                   | SRMK6                           |  |  |

| Address:         FFE6H         After reset:         FFH         R/W           Symbol         <7>         <6>         <4>         <3>         <2>         <1>         <0> |             |               |                             |        |                         |                             |                         |                                 |  |  |

| MK1L                                                                                                                                                                     | PMK7        | PMK6          | WTMK                        | KRMK   | TMMK51                  | WTIMK                       | SRMK0                   | ADMK                            |  |  |

|                                                                                                                                                                          |             | 1             |                             |        |                         |                             |                         |                                 |  |  |

| Address: FF                                                                                                                                                              | E7H After r | eset: FFH     | R/W                         |        |                         |                             |                         |                                 |  |  |

| Symbol                                                                                                                                                                   | 7           | 6             | 5                           | 4      | <3>                     | <2>                         | <1>                     | <0>                             |  |  |

| MK1H                                                                                                                                                                     | 1           | 1             | 1                           | 1      | TMMK011 <sup>Note</sup> | TMMK001 <sup>Note</sup>     | CSIMK11 <sup>Note</sup> | IICMK0<br>DMUMK <sup>Note</sup> |  |  |

|                                                                                                                                                                          |             |               |                             |        |                         |                             |                         |                                 |  |  |

|                                                                                                                                                                          | ХХМКХ       |               | Interrupt servicing control |        |                         |                             |                         |                                 |  |  |

|                                                                                                                                                                          | 0           | Interrupt ser | terrupt servicing enabled   |        |                         |                             |                         |                                 |  |  |

|                                                                                                                                                                          | 1           | Interrupt ser | errupt servicing disabled   |        |                         |                             |                         |                                 |  |  |

## Figure 20-10. Format of Interrupt Mask Flag Registers (MK0L, MK0H, MK1L, MK1H) (78K0/KE2)

Note Products whose flash memory is at least 48 KB only.

Caution Be sure to set bits 1 to 7 of MK1H to 1 for the products whose flash memory is less than 32 KB. Be sure to set bits 4 to 7 of MK1H to 1 for the products whose flash memory is at least 48 KB.

#### (2) When detecting level of input voltage from external input pin (EXLVI)

- When starting operation

- <1> Mask the LVI interrupt (LVIMK = 1).

- <2> Set bit 2 (LVISEL) of the low-voltage detection register (LVIM) to 1 (detects level of input voltage from external input pin (EXLVI)).

- <3> Set bit 7 (LVION) of LVIM to 1 (enables LVI operation).

- <4> Use software to wait for an operation stabilization time (10  $\mu$ s (MIN.)).

- <5> Wait until it is checked that (input voltage from external input pin (EXLVI) ≥ detection voltage (VEXLVI = 1.21 V (TYP.))) by bit 0 (LVIF) of LVIM.

- <6> Set bit 1 (LVIMD) of LVIM to 1 (generates reset signal when the level is detected).

Figure 25-6 shows the timing of the internal reset signal generated by the low-voltage detector. The numbers in this timing chart correspond to <1> to <6> above.

- Cautions 1. <1> must always be executed. When LVIMK = 0, an interrupt may occur immediately after the processing in <3>.

- 2. If input voltage from external input pin (EXLVI)  $\geq$  detection voltage (V<sub>EXLVI</sub> = 1.21 V (TYP.)) when LVIMD is set to 1, an internal reset signal is not generated.

- 3. Input voltage from external input pin (EXLVI) must be EXLVI < VDD.

- When stopping operation

Either of the following procedures must be executed.

- When using 8-bit memory manipulation instruction: Write 00H to LVIM.

- When using 1-bit memory manipulation instruction: Clear LVIMD to 0 and then LVION to 0.

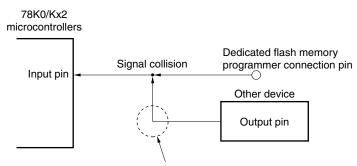

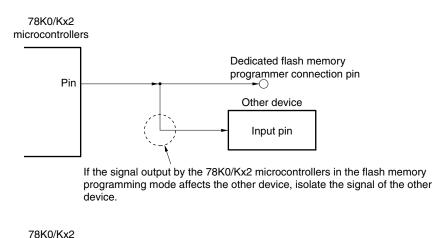

## (1) Signal collision

If the dedicated flash memory programmer (output) is connected to a pin (input) of a serial interface connected to another device (output), signal collision takes place. To avoid this collision, either isolate the connection with the other device, or make the other device go into an output high-impedance state.

Figure 27-7. Signal Collision (Input Pin of Serial Interface)

In the flash memory programming mode, the signal output by the device collides with the signal sent from the dedicated flash programmer. Therefore, isolate the signal of the other device.

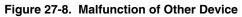

#### (2) Malfunction of other device

If the dedicated flash memory programmer (output or input) is connected to a pin (input or output) of a serial interface connected to another device (input), a signal may be output to the other device, causing the device to malfunction. To avoid this malfunction, isolate the connection with the other device.

If the signal output by the dedicated flash memory programmer in the flash memory programming mode affects the other device, isolate the signal of the other device.

#### Caution The pins mounted depend on the product. Refer to Caution at the beginning of this chapter.

#### DC Characteristics (2/4)

#### (TA = -40 to +85°C, 1.8 V $\leq$ Vdd = EVdd $\leq$ 5.5 V, AVREF $\leq$ Vdd, Vss = EVss = AVss = 0 V)

| Parameter                                                                                      | Symbol           | Condit                                                                           | ions                                                                                                  | MIN.                  | TYP.               | MAX.     | Unit |

|------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------|--------------------|----------|------|

| Input voltage, high<br>(products whose flash<br>memory is at least<br>48 KB) <sup>Note 1</sup> | VIH1             | P02, P12, P13, P15, P40 to<br>P67, P121 to P124, P144, F                         |                                                                                                       | 0.7V <sub>DD</sub>    |                    | Vdd      | V    |

|                                                                                                | VIH2             | P00, P01, P03 to P06, P10,<br>P30 to P33, P70 to P77, P1<br>EXCLK, EXCLKS, RESET |                                                                                                       | 0.8Vdd                |                    | Vdd      | V    |

|                                                                                                | VIH3             | P20 to P27                                                                       | $AV_{REF} = V_{DD}$                                                                                   | 0.7AVREF              |                    | AVREF    | V    |

|                                                                                                | VIH4             | P60 to P63                                                                       |                                                                                                       | 0.7VDD                |                    | 6.0      | V    |

| Input voltage, high<br>(products whose flash                                                   | VIH1             | P02 to P06, P12, P13, P15,<br>P121 to P124                                       | P40 to P43, P50 to P53,                                                                               | 0.7Vdd                |                    | Vdd      | V    |

| memory is less than<br>32 KB) <sup>Note 2</sup>                                                | VIH2             | P00, P01, P10, P11, P14, P<br>P70 to P77, P120, P140, P1<br>RESET                |                                                                                                       | 0.8Vdd                |                    | Vdd      | V    |

|                                                                                                | VIH3             | P20 to P27                                                                       | AVREF = VDD                                                                                           | 0.7AVREF              |                    | AVREF    | V    |

|                                                                                                | VIH4             | P60 to P63                                                                       | 0.7Vdd                                                                                                |                       | 6.0                | V        |      |

| Input voltage, low<br>(products whose flash                                                    | VIL1             | P02, P12, P13, P15, P40 to<br>P67, P121 to P124, P144, F                         | 0                                                                                                     |                       | 0.3Vdd             | V        |      |

| memory is at least<br>48 KB) <sup>Note 1</sup>                                                 | VIL2             | P00, P01, P03 to P06, P10,<br>P30 to P33, P70 to P77, P1<br>EXCLK, EXCLKS, RESET | 0                                                                                                     |                       | 0.2V <sub>DD</sub> | V        |      |

|                                                                                                | VIL3             | P20 to P27                                                                       | AVREF = VDD                                                                                           | 0                     |                    | 0.3AVREF | V    |

| Input voltage, low<br>(products whose flash                                                    | VIL1             | P02 to P06, P12, P13, P15,<br>P60 to P63, P121 to P124                           | 0                                                                                                     |                       | 0.3VDD             | V        |      |

| memory is less than<br>32 KB) <sup>Note 2</sup>                                                | VIL2             | P00, P01, P10, P11, P14, P<br>P70 to P77, P120, P140, P1<br>RESET                | 0                                                                                                     |                       | 0.2V <sub>DD</sub> | V        |      |

|                                                                                                | VIL3             | P20 to P27                                                                       | AVREF = VDD                                                                                           | 0                     |                    | 0.3AVREF | V    |

| Output voltage, high                                                                           | V <sub>OH1</sub> | P00 to P06, P10 to P17,<br>P30 to P33, P40 to P47,                               | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ \\ \text{Ioh1} = -3.0 \ mA \end{array}$ | $V_{\text{DD}}-0.7$   |                    |          | V    |

|                                                                                                |                  | P50 to P57, P64 to P67,<br>P70 to P77, P120, P130,                               | 2.7 V $\leq$ V_DD < 4.0 V,<br>Іон1 = -2.5 mA                                                          | $V_{\text{DD}}-0.5$   |                    |          | V    |

|                                                                                                |                  | P140 to P145                                                                     | 1.8 V $\leq$ Vdd < 2.7 V, loh1 = -1.0 mA                                                              | $V_{\text{DD}} - 0.5$ |                    |          | V    |

|                                                                                                | <b>V</b> он2     | P20 to P27                                                                       | AVREF = VDD,<br>IOH2 = $-100 \mu A$                                                                   | $V_{\text{DD}}-0.5$   |                    |          | V    |

|                                                                                                |                  | P121 to P124                                                                     | Іон2 = -100 <i>µ</i> А                                                                                | $V_{\text{DD}} - 0.5$ |                    |          | V    |

Notes 1. Supported products: 78K0/KD2 and 78K0/KE2 whose flash memory is at least 48 KB, and 78K0/KF2

Supported products: 78K0/KD2 and 78K0/KE2 whose flash memory is less than 32 KB, 78K0/KB2, and 78K0/KC2

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of port pins.

#### Caution The pins mounted depend on the product. Refer to Caution 2 at the beginning of this chapter.

#### (1) Basic operation (2/2)

```

(T_{A} = -40 \text{ to } +110^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{DD} = \text{EV}_{DD} \le 5.5 \text{ V}, \text{AV}_{REF} \le \text{V}_{DD}, \text{V}_{SS} = \text{EV}_{SS} = \text{AV}_{SS} = 0 \text{ V})

```

| Parameter                                                                                | Symbol                | Conditions                                                | MIN.                                          | TYP.   | MAX. | Unit |

|------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------|-----------------------------------------------|--------|------|------|

| External subsystem clock frequency <sup>Note 1</sup>                                     | fexclks               |                                                           | 32                                            | 32.768 | 35   | kHz  |

| External subsystem clock input<br>high-level width, low-level<br>width <sup>Note 1</sup> | texclksh,<br>texclksl |                                                           | 12                                            |        |      | μS   |

| TI000, TI010, TI001, TI011<br>input high-level width, low-level                          | tтіно,<br>tтіlo       | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                     | 2/f <sub>sam</sub> +<br>0.1 <sup>Note 2</sup> |        |      | μS   |

| width                                                                                    |                       | $2.7 \text{ V} \leq \text{V}_{\text{DD}} < 4.0 \text{ V}$ | 2/f <sub>sam</sub> +<br>0.2 <sup>Note 2</sup> |        |      | μs   |

| TI50, TI51 input frequency                                                               | ft15                  |                                                           |                                               |        | 10   | MHz  |

| TI50, TI51 input high-level width, low-level width                                       | t⊤iн₅,<br>t⊤i∟s       |                                                           | 50                                            |        |      | ns   |

| Interrupt input high-level width, low-level width                                        | tintн,<br>tintl       |                                                           | 1                                             |        |      | μS   |

| Key interrupt input low-level width                                                      | <b>t</b> KR           |                                                           | 250                                           |        |      | ns   |

| RESET low-level width                                                                    | <b>t</b> RSL          |                                                           | 10                                            |        |      | μS   |

Notes 1. The 78K0/KB2 is not provided with a subsystem clock.

2. Selection of fsam = fPRS, fPRS/4, fPRS/256, or fPRS, fPRS/16, fPRS/64 is possible using bits 0 and 1 (PRM000, PRM001 or PRM010, PRM011) of prescaler mode registers 00 and 01 (PRM00, PRM01). Note that when selecting the TI000 or TI001 valid edge as the count clock, fsam = fPRS.

# 34.3 78K0/KD2

• *µ*PD78F0521GB-UET-A, 78F0522GB-UET-A, 78F0523GB-UET-A, 78F0524GB-UET-A, 78F0525GB-UET-A, 78F0526GB-UET-A, 78F0527GB-UET-A, 78F0527DGB-UET-A

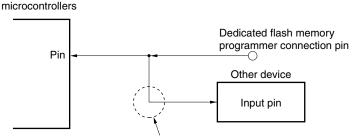

# 52-PIN PLASTIC LQFP(10x10)

## NOTE

Each lead centerline is located within 0.13 mm of its true position at maximum material condition.

1.10 P52GB-65-UET-1

0.13

0.10

1.10

Х

y

ZD

ΖE

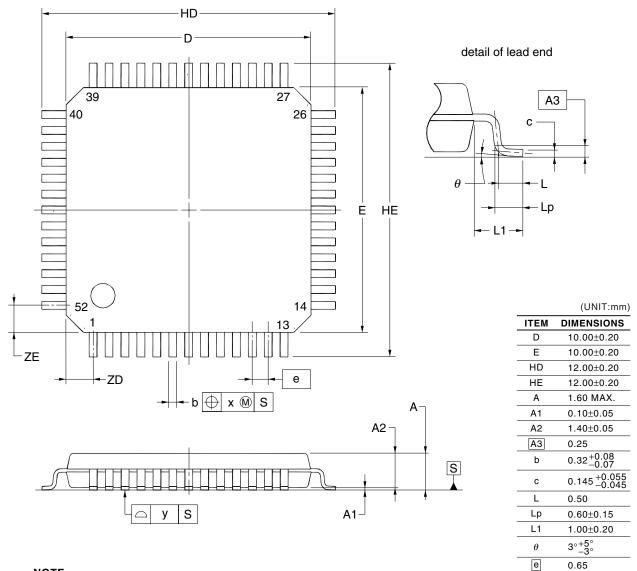

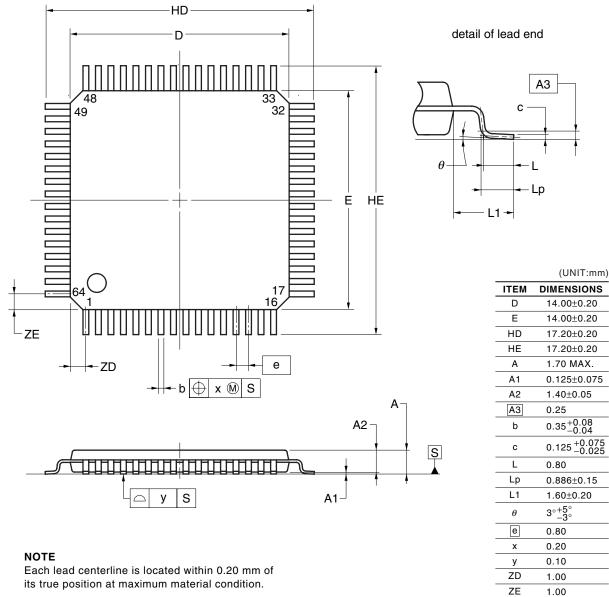

64-PIN PLASTIC LQFP (14x14)

- μPD78F0531GC(A)-GAL-AX, 78F0532GC(A)-GAL-AX, 78F0533GC(A)-GAL-AX, 78F0534GC(A)-GAL-AX, 78F0535GC(A)-GAL-AX, 78F0535GC(A)-GAL-AX, 78F0537GC(A)-GAL-AX

- *μ*PD78F0531GC(A2)-GAL-AX, 78F0532GC(A2)-GAL-AX, 78F0533GC(A2)-GAL-AX, 78F0534GC(A2)-GAL-AX, 78F0535GC(A2)-GAL-AX, 78F0535GC(A2)-GAL-AX, 78F0537GC(A2)-GAL-AX

- μPD78F0531AGC-GAL-AX, 78F0532AGC-GAL-AX, 78F0533AGC-GAL-AX, 78F0535AGC-GAL-AX, 78F0535AGC-GAL-AX, 78F0537AGC-GAL-AX, 78F0537

- µPD78F0531AGCA-GAL-G, 78F0532AGCA-GAL-G, 78F0533AGCA-GAL-G, 78F0535AGCA-GAL-G, 78F0535AGCA-GAL-G, 78F0536AGCA-GAL-G, 78F0537AGCA-GAL-G

- μPD78F0531AGCA2-GAL-G, 78F0532AGCA2-GAL-G, 78F0533AGCA2-GAL-G, 78F0535AGCA2-GAL-G, 78F0535AGCA2-GAL-G, 78F0535AGCA2-GAL-G, 78F0537AGCA2-GAL-G

P64GC-80-GAL

|                           |      |                                                                                                                                                                     | 1                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (26/30) |      |  |

|---------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|--|

| Chapter<br>Classification |      | Function                                                                                                                                                            | Details of<br>Function                           | Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         | Page |  |

| Chapter 24                | Ň    | Power-on-<br>clear<br>circuit                                                                                                                                       | In 2.7 V/1.59 V<br>POC mode                      | A voltage oscillation stabilization time of 1.93 to 5.39 ms is required after the supply voltage reaches 1.59 V (TYP.). If the supply voltage rises from 1.59 V (TYP.) to 2.7 V (TYP.) within 1.93 ms, the power supply oscillation stabilization time of 0 to 5.39 ms is automatically generated before reset processing.                                                                                                                                                                                                                                                                                                                                                                |         |      |  |

|                           |      |                                                                                                                                                                     | Cautions for<br>power-on-clear<br>circuit        | In a system where the supply voltage (V <sub>DD</sub> ) fluctuates for a certain period in the vicinity of the POC detection voltage (V <sub>POC</sub> ), the system may be repeatedly reset and released from the reset status. In this case, the time from release of reset to the start of the operation of the microcontroller can be arbitrarily set by taking the following action.                                                                                                                                                                                                                                                                                                 |         |      |  |

| Chapte                    | õ    | Low-<br>voltage<br>detector                                                                                                                                         | LVIM: Low-<br>voltage detection<br>register      | <ul> <li>To stop LVI, follow either of the procedures below.</li> <li>When using 8-bit memory manipulation instruction: Write 00H to LVIM.</li> <li>When using 1-bit memory manipulation instruction: Clear LVION to 0.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                        | p. 700  |      |  |

|                           | Hard | ר Input voltage from external input pin (EX                                                                                                                         |                                                  | Input voltage from external input pin (EXLVI) must be EXLVI < VDD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | p. 700  |      |  |

|                           | Soft |                                                                                                                                                                     |                                                  | When using LVI as an interrupt, if LVION is cleared (0) in a state below the LVI detection voltage, an INTLVI signal is generated and LVIIF becomes 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | p. 701  |      |  |

|                           |      |                                                                                                                                                                     | LVIM and LVIS                                    | With the conventional-specification products ( $\mu$ PD78F05xx and 78F05xxD), after an LVI reset has been generated, do not write values to LVIS and LVIM when LVION = 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | p. 701  |      |  |

|                           |      |                                                                                                                                                                     | LVIS: Low-                                       | Be sure to clear bits 4 to 7 to "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | p. 701  |      |  |

|                           |      |                                                                                                                                                                     | voltage detection<br>level selection<br>register | Do not change the value of LVIS during LVI operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | p. 701  |      |  |

|                           |      |                                                                                                                                                                     |                                                  | When an input voltage from the external input pin (EXLVI) is detected, the detection voltage ( $V_{EXLVI} = 1.21 V$ (TYP.)) is fixed. Therefore, setting of LVIS is not necessary.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | p. 701  |      |  |

|                           |      |                                                                                                                                                                     |                                                  | With the conventional-specification products ( $\mu$ PD78F05xx and 78F05xxD), after an LVI reset has been generated, do not write values to LVIS and LVIM when LVION = 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | p. 701  |      |  |

|                           |      |                                                                                                                                                                     | reset (When                                      | <1> must always be executed. When LVIMK = 0, an interrupt may occur immediately after the processing in <4>.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | p. 703  |      |  |

|                           |      |                                                                                                                                                                     |                                                  | If supply voltage (V_DD) $\geq$ detection voltage (V_LVI) when LVIMD is set to 1, an internal reset signal is not generated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | p. 703  |      |  |

|                           |      |                                                                                                                                                                     | When used as<br>reset (When                      | <1> must always be executed. When LVIMK = 0, an interrupt may occur immediately after the processing in <3>.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | p. 706  |      |  |

|                           |      |                                                                                                                                                                     |                                                  | If input voltage from external input pin (EXLVI) $\geq$ detection voltage (V <sub>EXLVI</sub> = 1.21 V (TYP.)) when LVIMD is set to 1, an internal reset signal is not generated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | p. 706  |      |  |

|                           | Hard |                                                                                                                                                                     |                                                  | Input voltage from external input pin (EXLVI) must be EXLVI $< V_{DD}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | p. 706  |      |  |

|                           |      | When used as<br>interrupt (When<br>detecting level of<br>input voltage from<br>external input pin<br>(EXLVI)       Input voltage from external input pin<br>(EXLVI) |                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | p. 711  |      |  |

|                           | Soft |                                                                                                                                                                     | Cautions for low-<br>voltage detector            | <ul> <li>In a system where the supply voltage (V<sub>DD</sub>) fluctuates for a certain period in the vicinity of the LVI detection voltage (V<sub>LVI</sub>), the operation is as follows depending on how the low-voltage detector is used.</li> <li>(1) When used as reset <ul> <li>The system may be repeatedly reset and released from the reset status.</li> <li>In this case, the time from release of reset to the start of the operation of the microcontroller can be arbitrarily set by taking action (1) below.</li> </ul> </li> <li>(2) When used as interrupt <ul> <li>Interrupt requests may be frequently generated. Take (b) of action (2) below.</li> </ul> </li> </ul> | p. 713  |      |  |

| 26                        | ~    | Option                                                                                                                                                              | 0082H, 0083H/                                    | Be sure to set 00H to 0082H and 0083H (0082H/1082H and 0083H/1083H when the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | p. 716  |      |  |