Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detalls                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | 78K/0                                                                                 |

| Core Size                  | 8-Bit                                                                                 |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                                    |

| Number of I/O              | 71                                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                                      |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 7K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 8x10b                                                                             |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 80-LQFP                                                                               |

| Supplier Device Package    | -                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0547agc-gad-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                              |                                              |                                            |                        | (5/6                                                                                                                                                                               |

|------------------------------|----------------------------------------------|--------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 78K0/Kx2<br>Microcontrollers | Package                                      | Product<br>type                            | Quality<br>grace       | Part Number                                                                                                                                                                        |

| 78K0/KE2                     | 64-pin plastic<br>LQFP (12x12)               | Conventional-<br>specification<br>products | Standard products      | μPD78F0531GK-UET-A, 78F0532GK-UET-A,<br>78F0533GK-UET-A, 78F0534GK-UET-A,<br>78F0535GK-UET-A, 78F0536GK-UET-A,<br>78F0537GK-UET-A, 78F0537DGK-UET-A <sup>Note</sup>                |

|                              |                                              |                                            | (A) grade<br>products  | μPD78F0531GK(A)-GAJ-AX, 78F0532GK(A)-GAJ-AX,<br>78F0533GK(A)-GAJ-AX, 78F0534GK(A)-GAJ-AX,<br>78F0535GK(A)-GAJ-AX, 78F0536GK(A)-GAJ-AX,<br>78F0537GK(A)-GAJ-AX                      |

|                              |                                              |                                            | (A2) grade<br>products | μPD78F0531GK(A2)-GAJ-AX, 78F0532GK(A2)-GAJ-AX,<br>78F0533GK(A2)-GAJ-AX, 78F0534GK(A2)-GAJ-AX,<br>78F0535GK(A2)-GAJ-AX, 78F0536GK(A2)-GAJ-AX,<br>78F0537GK(A2)-GAJ-AX               |

|                              |                                              | Expanded-<br>specification<br>products     | Standard<br>products   | µPD78F0531AGK-GAJ-AX, 78F0532AGK-GAJ-AX,<br>78F0533AGK-GAJ-AX, 78F0534AGK-GAJ-AX,<br>78F0535AGK-GAJ-AX, 78F0536AGK-GAJ-AX,<br>78F0537AGK-GAJ-AX, 78F0537DAGK-GAJ-AX <sup>№0®</sup> |

|                              |                                              |                                            | (A) grade<br>products  | µPD78F0531AGKA-GAJ-G, 78F0532AGKA-GAJ-G,<br>78F0533AGKA-GAJ-G, 78F0534AGKA-GAJ-G,<br>78F0535AGKA-GAJ-G, 78F0536AGKA-GAJ-G,<br>78F0537AGKA-GAJ-G                                    |

|                              |                                              |                                            | (A2) grade<br>products | μPD78F0531AGKA2-GAJ-G, 78F0532AGKA2-GAJ-G,<br>78F0533AGKA2-GAJ-G, 78F0534AGKA2-GAJ-G,<br>78F0535AGKA2-GAJ-G, 78F0536AGKA2-GAJ-G,<br>78F0537AGKA2-GAJ-G                             |

|                              | 64-pin plastic<br>TQFP (fine pitch)<br>(7x7) | Conventional-<br>specification<br>products | Standard products      | µPD78F0531GA-9EV-A, 78F0532GA-9EV-A,<br>78F0533GA-9EV-A, 78F0534GA-9EV-A, 78F0535GA-9EV-A,<br>78F0536GA-9EV-A, 78F0537GA-9EV-A,<br>78F0537DGA-9EV-A <sup>№0®</sup>                 |

|                              |                                              | Expanded-<br>specification<br>products     | Standard products      | μPD78F0531AGA-HAB-AX, 78F0532AGA-HAB-AX,<br>78F0533AGA-HAB-AX, 78F0534AGA-HAB-AX,<br>78F0535AGA-HAB-AX, 78F0536AGA-HAB-AX,<br>78F0537AGA-HAB-AX, 78F0537DAGA-HAB-AX <sup>№0®</sup> |

**Note** The μPD78F0537D and 78F0537DA have an on-chip debug function, which is provided for development and evaluation. Do not use the on-chip debug function in products designated for mass production, because the guaranteed number of rewritable times of the flash memory may be exceeded when this function is used, and product reliability therefore cannot be guaranteed. Renesas Electronics is not liable for problems occurring when the on-chip debug function is used.

## (2) Non-port functions (3/3): 78K0/KE2

|         | Function Name         | I/O   | Function                                                                                                                | After Reset | Alternate Function |

|---------|-----------------------|-------|-------------------------------------------------------------------------------------------------------------------------|-------------|--------------------|

|         | Vdd                   | -     | Positive power supply for P121 to P124 and other than ports                                                             | -           | -                  |

|         | EVDD                  | _     | Positive power supply for ports other than P20 to P27 and P121 to P124. Make $EV_{DD}$ the same potential as $V_{DD}$ . | _           | -                  |

| <r></r> | AVREF                 | _     | A/D converter reference voltage input and positive power<br>supply for P20 to P27 and A/D converter                     | _           | -                  |

|         | Vss                   | -     | Ground potential for P121 to P124 and other than ports                                                                  | -           | -                  |

|         | EVss                  | _     | Ground potential for ports other than P20 to P27 and P121 to P124. Make EVss the same potential as Vss.                 | _           | -                  |

|         | AVss                  | -     | A/D converter ground potential. Make the same potential as Vss.                                                         | -           | -                  |

|         | OCD0A <sup>Note</sup> | Input | Connection for on-chip debug mode setting pins                                                                          | Input port  | P121/X1            |

|         | OCD1A <sup>Note</sup> |       | (µPD78F0537D and 78F0537DA only)                                                                                        |             | P31/INTP2          |

|         | OCD0B <sup>Note</sup> | _     |                                                                                                                         |             | P122/X2/EXCLK      |

|         | OCD1B <sup>Note</sup> |       |                                                                                                                         |             | P32/INTP3          |

Note  $\mu$ PD78F0537D and 78F0537DA (product with on-chip debug function) only

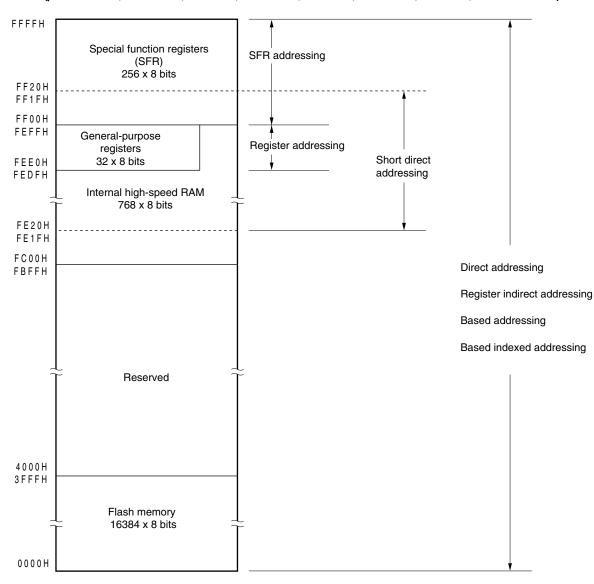

# Figure 3-13. Correspondence Between Data Memory and Addressing (μPD78F0501, 78F0501A, 78F0511, 78F0511A, 78F0521, 78F0521A, 78F0531, and 78F0531A)

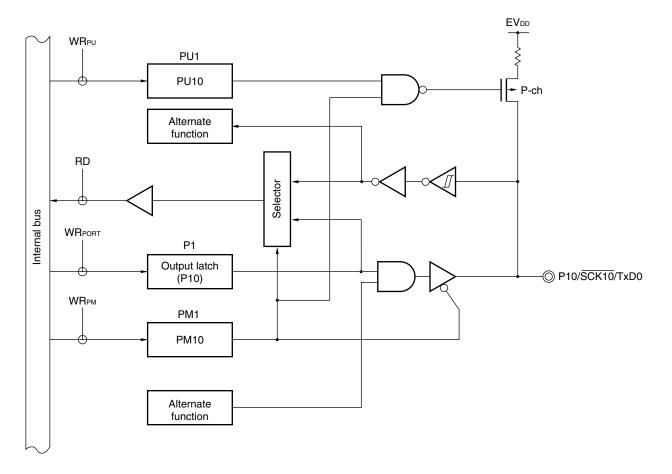

Figure 5-7. Block Diagram of P10

- P1: Port register 1

- PU1: Pull-up resistor option register 1

- PM1: Port mode register 1

- RD: Read signal

- WR××: Write signal

Remark With products not provided with an EVDD or EVSS pin, replace EVDD with VDD, or replace EVSS with VSS.

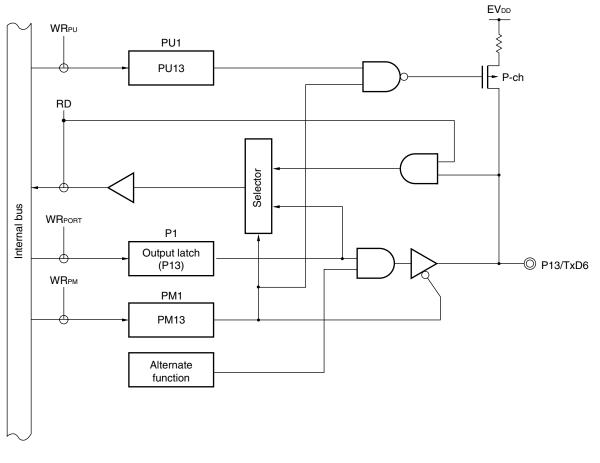

Figure 5-10. Block Diagram of P13

- P1: Port register 1

- PU1: Pull-up resistor option register 1

- PM1: Port mode register 1

- RD: Read signal

- WR××: Write signal

Remark With products not provided with an EVDD or EVSS pin, replace EVDD with VDD, or replace EVSS with VSS.

| Symbol | 7    | 6        | 5          | 4            | 3     | 2           | 1           | 0         | Address | After reset | R/W |

|--------|------|----------|------------|--------------|-------|-------------|-------------|-----------|---------|-------------|-----|

| PM0    | 1    | PM06     | PM05       | PM04         | PM03  | PM02        | PM01        | PM00      | FF20H   | FFH         | R/W |

|        |      |          |            |              |       |             |             |           |         |             |     |

| PM1    | PM17 | PM16     | PM15       | PM14         | PM13  | PM12        | PM11        | PM10      | FF21H   | FFH         | R/W |

|        |      | 1        |            | 1            | 1     | 1           |             | 1         |         |             |     |

| PM2    | PM27 | PM26     | PM25       | PM24         | PM23  | PM22        | PM21        | PM20      | FF22H   | FFH         | R/W |

|        |      |          |            | 1            | L     | 8           | 1           | 1         |         |             |     |

| PM3    | 1    | 1        | 1          | 1            | PM33  | PM32        | PM31        | PM30      | FF23H   | FFH         | R/W |

|        |      |          |            | 1            | L     | I           | 1           | 1         |         |             |     |

| PM4    | PM47 | PM46     | PM45       | PM44         | PM43  | PM42        | PM41        | PM40      | FF24H   | FFH         | R/W |

|        |      |          |            |              |       |             |             |           |         |             |     |

| PM5    | PM57 | PM56     | PM55       | PM54         | PM53  | PM52        | PM51        | PM50      | FF25H   | FFH         | R/W |

|        |      |          |            |              |       |             |             |           |         |             |     |

| PM6    | PM67 | PM66     | PM65       | PM64         | PM63  | PM62        | PM61        | PM60      | FF26H   | FFH         | R/W |

|        |      |          |            |              |       |             |             |           |         |             |     |

| PM7    | PM77 | PM76     | PM75       | PM74         | PM73  | PM72        | PM71        | PM70      | FF27H   | FFH         | R/W |

|        |      |          |            |              |       |             |             |           |         |             |     |

| PM12   | 1    | 1        | 1          | PM124        | PM123 | PM122       | PM121       | PM120     | FF2CH   | FFH         | R/W |

|        |      |          |            |              |       |             |             |           |         |             |     |

| PM14   | 1    | 1        | PM145      | PM144        | PM143 | PM142       | PM141       | PM140     | FF2EH   | FFH         | R/W |

|        |      |          |            |              |       |             |             |           |         |             |     |

|        | PMmn |          |            |              |       | Pmn pin I/0 | O mode se   | election  |         |             |     |

|        |      |          |            |              | (1    | m = 0 to 7, | 12, 14; n = | = 0 to 7) |         |             |     |

|        | 0    | Output m | ode (outpu | ut buffer on | )     |             |             |           |         |             |     |

|        | 1    | Input mo | de (output | buffer off)  |       |             |             |           |         |             |     |

### Figure 5-33. Format of Port Mode Register (78K0/KF2)

Caution Be sure to set bit 7 of PM0, bits 4 to 7 of PM3, bits 5 to 7 of PM12, and bits 6 and 7 of PM14 to "1".

| Symbol | 7    | 6         | 5            | 4           | 3       | 2             | 1           | 0            | Address | After reset | R/W |

|--------|------|-----------|--------------|-------------|---------|---------------|-------------|--------------|---------|-------------|-----|

| PU0    | 0    | 0         | 0            | 0           | PU03    | PU02          | PU01        | PU00         | FF30H   | 00H         | R/W |

|        |      |           |              |             |         |               |             |              |         |             |     |

| PU1    | PU17 | PU16      | PU15         | PU14        | PU13    | PU12          | PU11        | PU10         | FF31H   | 00H         | R/W |

|        |      |           |              |             |         |               |             |              | -       |             |     |

| PU3    | 0    | 0         | 0            | 0           | PU33    | PU32          | PU31        | PU30         | FF33H   | 00H         | R/W |

|        |      |           |              |             |         |               |             |              |         |             |     |

| PU4    | 0    | 0         | 0            | 0           | 0       | 0             | PU41        | PU40         | FF34H   | 00H         | R/W |

|        |      |           |              |             |         |               |             |              |         |             |     |

| PU7    | PU77 | PU76      | PU75         | PU74        | PU73    | PU72          | PU71        | PU70         | FF37H   | 00H         | R/W |

|        |      |           |              |             |         | -             |             |              |         |             |     |

| PU12   | 0    | 0         | 0            | 0           | 0       | 0             | 0           | PU120        | FF3CH   | 00H         | R/W |

|        |      |           |              |             |         |               |             |              |         |             |     |

| PU14   | 0    | 0         | 0            | 0           | 0       | 0             | 0           | PU140        | FF3EH   | 00H         | R/W |

|        |      |           |              |             |         |               |             |              |         |             |     |

|        | PUmn |           |              |             | Pmn pi  | n on-chip p   | oull-up res | istor select | ion     |             |     |

|        |      |           |              |             | (m =    | = 0, 1, 3, 4, | 7, 12, 14;  | n = 0 to 7)  |         |             |     |

|        | 0    | On-chip p | oull-up resi | stor not co | nnected |               |             |              |         |             |     |

|        | 1    | On-chip p | oull-up resi | stor conne  | cted    |               |             |              |         |             |     |

## Figure 5-41. Format of Pull-up Resistor Option Register (78K0/KD2)

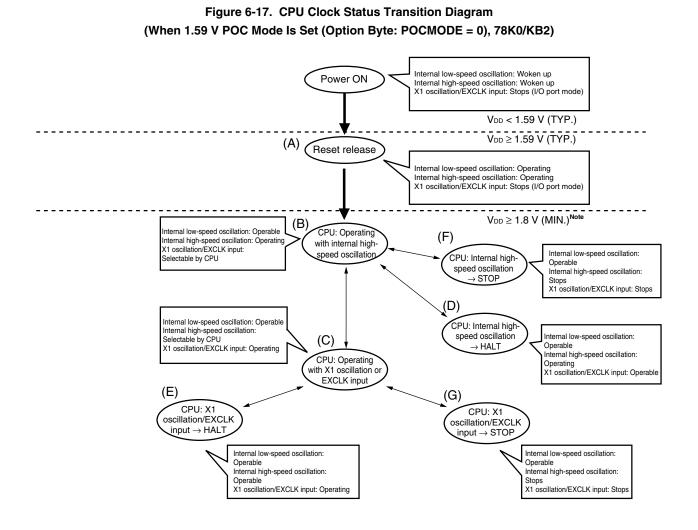

#### 6.6.6 CPU clock status transition diagram

Figure 6-17 and 6-18 shows the CPU clock status transition diagram of this product.

- Note Standard and (A) grade products: 1.8 V, (A2) grade products: 2.7 V

- **Remark** In the 2.7 V/1.59 V POC mode (option byte: POCMODE = 1), the CPU clock status changes to (A) in the above figure when the supply voltage exceeds 2.7 V (TYP.), and to (B) after reset processing (11 to  $45 \ \mu$ s).

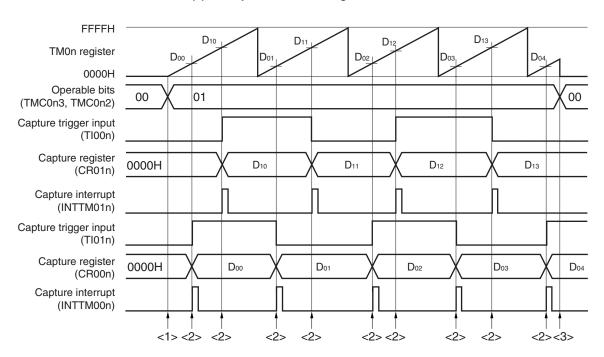

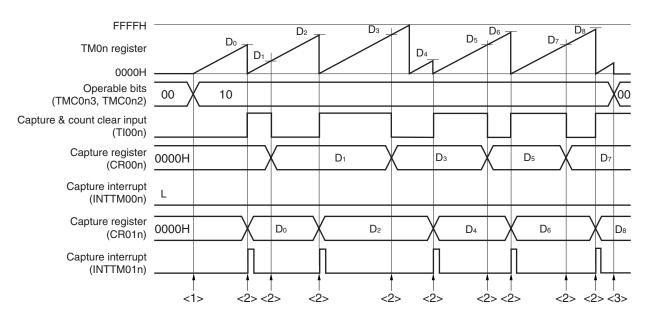

### Figure 7-57. Example of Software Processing for Pulse Width Measurement (1/2)

(a) Example of free-running timer mode

#### (b) Example of clear & start mode entered by TI00n pin valid edge

# **Remark** n = 0: 78K0/KE2 products whose flash memory is less than 32 KB, and 78K0/KB2, 78K0/KC2, 78K0/KD2 products

n = 0, 1: 78K0/KE2 products whose flash memory is at least 48 KB, and 78K0/KF2 products

## Caution Do not change the count clock and interval time (by setting bits 4 to 7 (WTM4 to WTM7) of WTM) during watch timer operation.

**Remarks 1.** fw: Watch timer clock frequency (fPRs/2<sup>7</sup> or fsub)

- 2. fprs: Peripheral hardware clock frequency

- 3. fsub: Subsystem clock frequency

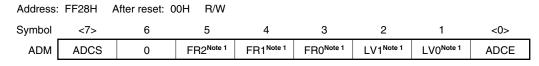

## 13.3 Registers Used in A/D Converter

The A/D converter uses the following six registers.

- A/D converter mode register (ADM)

- A/D port configuration register (ADPC)

- Analog input channel specification register (ADS)

- Port mode register 2 (PM2)

- 10-bit A/D conversion result register (ADCR)

- 8-bit A/D conversion result register (ADCRH)

#### (1) A/D converter mode register (ADM)

This register sets the conversion time for analog input to be A/D converted, and starts/stops conversion. ADM can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation clears this register to 00H.

#### Figure 13-3. Format of A/D Converter Mode Register (ADM)

| ADCS | A/D conversion operation control |  |  |  |  |

|------|----------------------------------|--|--|--|--|

| 0    | Stops conversion operation       |  |  |  |  |

| 1    | Enables conversion operation     |  |  |  |  |

| ADCE | Comparator operation control <sup>Note 2</sup> |

|------|------------------------------------------------|

| 0    | Stops comparator operation                     |

| 1    | Enables comparator operation                   |

- Notes 1. For details of FR2 to FR0, LV1, LV0, and A/D conversion, see Table 13-2 A/D Conversion Time Selection (Conventional-specification Products (μPD78F05xx and 78F05xxD)), and Table 13-3 A/D Conversion Time Selection (Expanded-specification Products (μPD78F05xxA and 78F05xxDA)).

- 2. The operation of the comparator is controlled by ADCS and ADCE, and it takes 1  $\mu$ s from operation start to operation stabilization. Therefore, when ADCS is set to 1 after 1  $\mu$ s or more has elapsed from the time ADCE is set to 1, the conversion result at that time has priority over the first conversion result. Otherwise, ignore data of the first conversion.

| Table 13-1. | Settings | of ADCS | and ADCE |

|-------------|----------|---------|----------|

|-------------|----------|---------|----------|

| ADCS | ADCE | A/D Conversion Operation                                                       |

|------|------|--------------------------------------------------------------------------------|

| 0    | 0    | Stop status (DC power consumption path does not exist)                         |

| 0    | 1    | Conversion waiting mode (comparator operation, only comparator consumes power) |

| 1    | 0    | Conversion mode (comparator operation stopped <sup>Note</sup> )                |

| 1    | 1    | Conversion mode (comparator operation)                                         |

**Note** Ignore the first conversion data.

## 14.2 Configuration of Serial Interface UART0

Serial interface UART0 includes the following hardware.

| Item              | Configuration                                                                                                                                                                                                                                      |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Registers         | Receive buffer register 0 (RXB0)<br>Receive shift register 0 (RXS0)<br>Transmit shift register 0 (TXS0)                                                                                                                                            |

| Control registers | Asynchronous serial interface operation mode register 0 (ASIM0)<br>Asynchronous serial interface reception error status register 0 (ASIS0)<br>Baud rate generator control register 0 (BRGC0)<br>Port mode register 1 (PM1)<br>Port register 1 (P1) |

### Table 14-1. Configuration of Serial Interface UART0

### (1) Receive buffer register 6 (RXB6)

This 8-bit register stores parallel data converted by receive shift register 6 (RXS6).

Each time 1 byte of data has been received, new receive data is transferred to this register from RXS6. If the data length is set to 7 bits, data is transferred as follows.

• In LSB-first reception, the receive data is transferred to bits 0 to 6 of RXB6 and the MSB of RXB6 is always 0.

• In MSB-first reception, the receive data is transferred to bits 1 to 7 of RXB6 and the LSB of RXB6 is always 0. If an overrun error (OVE6) occurs, the receive data is not transferred to RXB6.

RXB6 can be read by an 8-bit memory manipulation instruction. No data can be written to this register. Reset signal generation sets this register to FFH.

#### (2) Receive shift register 6 (RXS6)

This register converts the serial data input to the RxD6 pin into parallel data. RXS6 cannot be directly manipulated by a program.

#### (3) Transmit buffer register 6 (TXB6)

This buffer register is used to set transmit data. Transmission is started when data is written to TXB6. This register can be read or written by an 8-bit memory manipulation instruction. Reset signal generation sets this register to FFH.

- Cautions 1. Do not write data to TXB6 when bit 1 (TXBF6) of asynchronous serial interface transmission status register 6 (ASIF6) is 1.

- 2. Do not refresh (write the same value to) TXB6 by software during a communication operation (when bits 7 and 6 (POWER6, TXE6) of asynchronous serial interface operation mode register 6 (ASIM6) are 1 or when bits 7 and 5 (POWER6, RXE6) of ASIM6 are 1).

- 3. Set transmit data to TXB6 at least one base clock (fxcLK6) after setting TXE6 = 1.

#### (4) Transmit shift register 6 (TXS6)

This register transmits the data transferred from TXB6 from the TxD6 pin as serial data. Data is transferred from TXB6 immediately after TXB6 is written for the first transmission, or immediately before INTST6 occurs after one frame was transmitted for continuous transmission. Data is transferred from TXB6 and transmitted from the TxD6 pin at the falling edge of the base clock.

TXS6 cannot be directly manipulated by a program.

#### Figure 16-4. Format of Serial Operation Mode Register 11 (CSIM11)

Address: FF88H After reset: 00H R/WNote1

Symbo CSIM1

| bol | <7>    | 6      | 5     | 4     | 3 | 2 | 1 | 0      |

|-----|--------|--------|-------|-------|---|---|---|--------|

| 111 | CSIE11 | TRMD11 | SSE11 | DIR11 | 0 | 0 | 0 | CSOT11 |

| CSIE11 | Operation control in 3-wire serial I/O mode                                                             |

|--------|---------------------------------------------------------------------------------------------------------|

| 0      | Disables operation <sup>Note 2</sup> and asynchronously resets the internal circuit <sup>Note 3</sup> . |

| 1      | Enables operation                                                                                       |

| TRMD11 <sup>Note 4</sup> | Transmit/receive mode control         |

|--------------------------|---------------------------------------|

| 0 <sup>Note 5</sup>      | Receive mode (transmission disabled). |

| 1                        | Transmit/receive mode                 |

| SSE11 <sup>Notes 6, 7</sup> | SSI11 pin use selection |

|-----------------------------|-------------------------|

| 0                           | SSI11 pin is not used   |

| 1                           | SSI11 pin is used       |

| DIR11 <sup>Note 8</sup> | First bit specification |

|-------------------------|-------------------------|

| 0                       | MSB                     |

| 1                       | LSB                     |

| CSOT11 | Communication status flag     |

|--------|-------------------------------|

| 0      | Communication is stopped.     |

| 1      | Communication is in progress. |

#### Notes 1. Bit 0 is a read-only bit.

- 2. To use P02/SO11, P04/SCK11, and P05/SSI11/TI001 as general-purpose ports, set CSIM11 in the default status (00H).

- 3. Bit 0 (CSOT11) of CSIM11 and serial I/O shift register 11 (SIO11) are reset.

- 4. Do not rewrite TRMD11 when CSOT11 = 1 (during serial communication).

- 5. The SO11 output (see Figure 16-2) is fixed to the low level when TRMD11 is 0. Reception is started when data is read from SIO11.

- 6. Do not rewrite SSE11 when CSOT11 = 1 (during serial communication).

- 7. Before setting this bit to 1, fix the SSI11 pin input level to 0 or 1.

- 8. Do not rewrite DIR11 when CSOT11 = 1 (during serial communication).

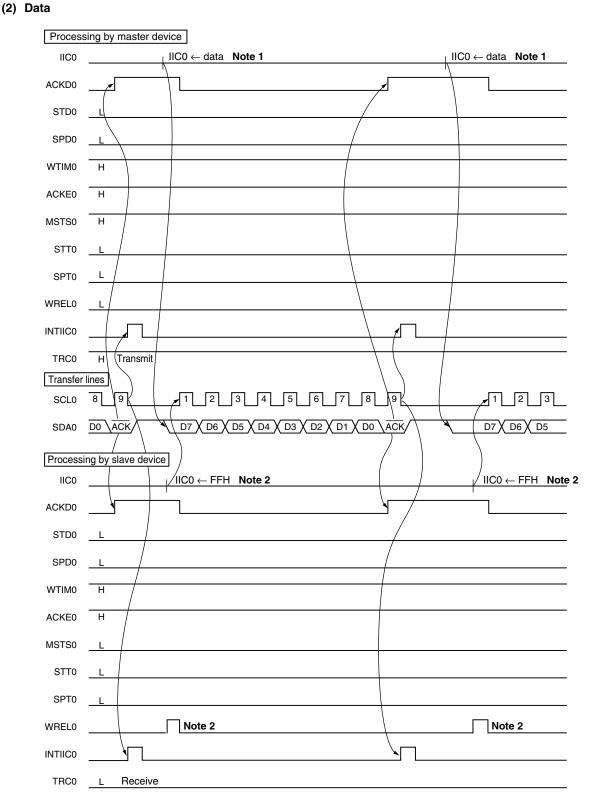

# Figure 18-27. Example of Master to Slave Communication (When 9-Clock Wait Is Selected for Both Master and Slave) (2/3)

RENESAS

## CHAPTER 21 KEY INTERRUPT FUNCTION

|               | 78K0/KB2 | 78K0/KC2                          | 78K0/KD2 | 78K0/KE2 | 78K0/KF2 |

|---------------|----------|-----------------------------------|----------|----------|----------|

| Key interrupt | -        | 38 pins: 2 ch<br>44/48 pins: 4 ch |          | 8 ch     |          |

## 21.1 Functions of Key Interrupt

A key interrupt (INTKR) can be generated by setting the key return mode register (KRM) and inputting a falling edge to the key interrupt input pins (KRn).

| Table 21-1. | Assignment of | <b>Key Interrupt</b> | <b>Detection Pins</b> |

|-------------|---------------|----------------------|-----------------------|

|-------------|---------------|----------------------|-----------------------|

| Flag | Description                         |

|------|-------------------------------------|

| KRMn | Controls KRn signal in 1-bit units. |

Remark n = 0, 1: 38-pin products of 78K0/KC2

n = 0 to 3: 44-pin and 48-pin products of 78K0/KC2

n = 0 to 7: 78K0/KD2, 78K0/KE2, 78K0/KF2

## Caution The pins mounted depend on the product. Refer to Caution 2 at the beginning of this chapter.

## Key Interrupt Input Timing

### **RESET** Input Timing

## (2) Non-port functions

|                      | Port 78K0/KB2 78K0/KC2   |                                                                               |                | 78K0/KD2      | 78K0/KE2      | 78K0/KF2                             |                                                                |                                                    |

|----------------------|--------------------------|-------------------------------------------------------------------------------|----------------|---------------|---------------|--------------------------------------|----------------------------------------------------------------|----------------------------------------------------|

|                      |                          | 30/36 Pins                                                                    | 38 Pins        | 44 Pins       | 48 Pins       | 52 Pins                              | 64 Pins                                                        | 80 Pins                                            |

| Power supply, ground |                          | Vdd, EVdd <sup>Note 1</sup> ,<br>Vss, EVss <sup>Note 1</sup> ,<br>AVref, AVss |                |               |               | Vdd, EVdd, Vss, EVss, AVref,<br>AVss |                                                                |                                                    |

| Reg                  | gulator                  | REGC                                                                          |                |               |               |                                      |                                                                |                                                    |

| Res                  | set RESET                |                                                                               |                |               |               |                                      |                                                                |                                                    |

| Clo<br>osc           | ck<br>illation           | X1, X2,<br>EXCLK                                                              | X1, X2, XT1, X | T2, EXCLK, EX | CLKS          |                                      |                                                                |                                                    |

|                      | ting to<br>h memory      | FLMD0                                                                         |                |               |               |                                      |                                                                |                                                    |

| Inte                 | errupt                   | INTP0 to INTP                                                                 | 5              | •             | INTP0 to INTP | 6                                    | INTP0 to INTP3                                                 | 7                                                  |

| Key                  | v interrupt              | -                                                                             | KR0, KR1       | KR0 to KR3    |               | KR0 to KR7                           |                                                                |                                                    |

|                      | ТМ00                     | TI000, TI010, T                                                               | ГО00           |               |               |                                      |                                                                |                                                    |

|                      | TM01                     |                                                                               |                | -             |               |                                      | TI001 <sup>Note 2</sup> , TI01                                 | 1 <sup>Note 2</sup> , TO01 <sup>Note 2</sup>       |

| Timer                | TM50                     | TI50, TO50                                                                    |                |               |               |                                      |                                                                |                                                    |

| Ę                    | TM51                     | TI51, TO51                                                                    |                |               |               |                                      |                                                                |                                                    |

|                      | тмно                     | TOH0                                                                          |                |               |               |                                      |                                                                |                                                    |

| TMH1 TOH1            |                          |                                                                               |                |               |               |                                      |                                                                |                                                    |

|                      | UART0                    | RxD0, TxD0                                                                    |                |               |               |                                      |                                                                |                                                    |

|                      | UART6                    | RxD6, TxD6                                                                    |                |               |               |                                      |                                                                |                                                    |

| ce                   | IIC0                     | SCL0, SDA0                                                                    | SCL0, SDA0, E  | EXSCL0        |               |                                      |                                                                |                                                    |

| iterfa               | CSI10                    | SCK10, SI10, S                                                                | SO10           |               |               |                                      |                                                                |                                                    |

| Serial interface     | CSI11                    |                                                                               |                | -             |               |                                      | SCK11 <sup>Note 2</sup> , SI1<br>SO11 <sup>Note 2</sup> , SSI1 | $\frac{1}{1}^{Note 2}$ ,<br>$\frac{1}{1}^{Note 2}$ |

| 0,                   | CSIA0                    |                                                                               |                |               | _             |                                      |                                                                | SCKAO, SIAO,<br>SOAO, BUSYO,<br>STBO               |

| A/D                  | converter                | ANI0 to ANI3                                                                  | ANI0 to ANI5   | ANI0 to ANI7  |               |                                      |                                                                |                                                    |

| Clo                  | ck output                |                                                                               | -              |               | PCL           |                                      | <u>.</u>                                                       |                                                    |

| Buz                  | zer output               |                                                                               |                | -             |               |                                      | BUZ                                                            |                                                    |

|                      | v-voltage<br>ector (LVI) | EXLVI                                                                         |                |               |               |                                      |                                                                |                                                    |

Notes 1. This is not mounted onto 30-pin products.

2. This is not mounted onto the 78K0/KE2 products whose flash memory is less than 32 KB.

Caution The pins mounted depend on the product. Refer to Caution at the beginning of this chapter.

#### A/D Converter Characteristics

(TA = -40 to +85°C, 2.3 V  $\leq$  AVREF  $\leq$  VDD = EVDD  $\leq$  5.5 V, Vss = EVss = AVss = 0 V)

| Parameter                                      | Symbol           | Conditions                                                   |                                         | MIN. | TYP. | MAX.  | Unit |

|------------------------------------------------|------------------|--------------------------------------------------------------|-----------------------------------------|------|------|-------|------|

| Resolution                                     | Res              |                                                              |                                         |      |      | 10    | bit  |

| Overall error <sup>Notes 1, 2</sup>            | AINL             | $4.0~V \leq AV_{\text{REF}} \leq 5.5~V$                      |                                         |      |      | ±0.4  | %FSR |

|                                                |                  | $2.7 \text{ V} \leq \text{AV}_{\text{REF}} < 4.0 \text{ V}$  |                                         |      |      | ±0.6  | %FSR |

|                                                |                  | $2.3 \text{ V} \leq AV_{\text{REF}} < 2.7$                   | 7 V                                     |      |      | ±1.2  | %FSR |

| Conversion time                                | tconv            | Conventional-                                                | $4.0~V \leq AV_{\text{REF}} \leq 5.5~V$ | 6.1  |      | 36.7  | μs   |

|                                                |                  | specification                                                | $2.7~V \leq AV_{\text{REF}} < 4.0~V$    | 12.2 |      | 36.7  | μs   |

|                                                |                  | Products<br>(µPD78F05xx(A))                                  | $2.3~V \leq AV_{\text{REF}} < 2.7~V$    | 27   |      | 66.6  | μS   |

|                                                |                  | Expanded-                                                    | $4.0~V \leq AV_{\text{REF}} \leq 5.5~V$ | 6.1  |      | 66.6  | μs   |

|                                                |                  | specification                                                | $2.7~V \leq AV_{\text{REF}} < 4.0~V$    | 12.2 |      | 66.6  | μs   |

|                                                |                  | Products<br>(μPD78F05xxA(A))                                 | $2.3~V \leq AV_{\text{REF}} < 2.7~V$    | 27   |      | 66.6  | μS   |

| Zero-scale error <sup>Notes 1, 2</sup>         | Ezs              | $4.0 \text{ V} \le \text{AV}_{\text{REF}} \le 5.5 \text{ V}$ |                                         |      |      | ±0.4  | %FSR |

|                                                |                  | $2.7~V \leq AV_{\text{REF}} < 4.0~V$                         |                                         |      |      | ±0.6  | %FSR |

|                                                |                  | $2.3 \text{ V} \leq \text{AV}_{\text{REF}} < 2.7 \text{ V}$  |                                         |      |      | ±0.6  | %FSR |

| Full-scale error <sup>Notes 1, 2</sup>         | E <sub>F</sub> s | $4.0~V \leq AV_{\text{REF}} \leq 5.5~V$                      |                                         |      |      | ±0.4  | %FSR |

|                                                |                  | $2.7~V \leq AV_{\text{REF}} < 4.0~V$                         |                                         |      |      | ±0.6  | %FSR |

|                                                |                  | $2.3~V \leq AV_{\text{REF}} < 2.7~V$                         |                                         |      |      | ±0.6  | %FSR |

| Integral non-linearity error <sup>Note 1</sup> | ILE              | $4.0~V \leq AV_{\text{REF}} \leq 5.5$                        | 5 V                                     |      |      | ±2.5  | LSB  |

|                                                |                  | $2.7 \text{ V} \leq \text{AV}_{\text{REF}} < 4.0 \text{ V}$  |                                         |      |      | ±4.5  | LSB  |

|                                                |                  | $2.3~V \leq AV_{\text{REF}} < 2.7~V$                         |                                         |      |      | ±6.5  | LSB  |

| Differential non-linearity error Note 1        | DLE              | $4.0~V \leq AV_{\text{REF}} \leq 5.5$                        | 5 V                                     |      |      | ±1.5  | LSB  |

|                                                |                  | $2.7 \text{ V} \leq AV_{\text{REF}} < 4.0$                   | V                                       |      |      | ±2.0  | LSB  |

|                                                |                  | $2.3~V \leq AV_{\text{REF}} < 2.7~V$                         |                                         |      |      | ±2.0  | LSB  |

| Analog input voltage                           | VAIN             |                                                              |                                         | AVss |      | AVREF | V    |

**Notes 1.** Excludes quantization error ( $\pm 1/2$  LSB).

2. This value is indicated as a ratio (%FSR) to the full-scale value.

## A.1 Software Package

| SP78K0                        | Development tools (software) common to the 78K0 microcontrollers are combined in this |

|-------------------------------|---------------------------------------------------------------------------------------|

| 78K0 microcontroller software | package.                                                                              |

| package                       |                                                                                       |

## A.2 Language Processing Software

| RA78K0 <sup>Note 1</sup>   | This assembler converts programs written in mnemonics into object codes executable      |

|----------------------------|-----------------------------------------------------------------------------------------|

| Assembler package          | with a microcontroller.                                                                 |

|                            | This assembler is also provided with functions capable of automatically creating symbol |

|                            | tables and branch instruction optimization.                                             |

|                            | This assembler should be used in combination with a device file (DF780547).             |

|                            | <precaution environment="" in="" pc="" ra78k0="" using="" when=""></precaution>         |

|                            | This assembler package is a DOS-based application. It can also be used in Windows,      |

|                            | however, by using the Project Manager (PM+) on Windows. PM+ is included in              |

|                            | assembler package.                                                                      |

| CC78K0 <sup>Note 1</sup>   | This compiler converts programs written in C language into object codes executable with |

| C compiler package         | a microcontroller.                                                                      |

|                            | This compiler should be used in combination with an assembler package and device file.  |

|                            | <precaution cc78k0="" environment="" in="" pc="" using="" when=""></precaution>         |

|                            | This C compiler package is a DOS-based application. It can also be used in Windows,     |

|                            | however, by using the Project Manager (PM+) on Windows. PM+ is included in              |

|                            | assembler package.                                                                      |

| DF780547 <sup>Note 2</sup> | This file contains information peculiar to the device.                                  |

| Device file                | This device file should be used in combination with a tool (RA78K0, CC78K0, ID78K0-     |

|                            | QB, and the system simulator).                                                          |

|                            | The corresponding OS and host machine differ depending on the tool to be used.          |

- **Notes 1.** If the versions of RA78K0 and CC78K0 are Ver.4.00 or later, different versions of RA78K0 and CC78K0 can be installed on the same machine.

- The DF780547 can be used in common with the RA78K0, CC78K0, ID78K0-QB, and the system simulator. Download the DF780547 from the download site for development tools (http://www2.renesas.com/micro/en/ods/index.html).