Welcome to E-XFL.COM

Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

#### Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

#### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application enacific microcontrollars are angineered to

#### Details

| Product Status          | Active                                                               |

|-------------------------|----------------------------------------------------------------------|

| Applications            | Keyboard and Embedded Controller                                     |

| Core Processor          | MIPS32® M14K™                                                        |

| Program Memory Type     | External Program Memory                                              |

| Controller Series       | -                                                                    |

| RAM Size                | 192KB                                                                |

| Interface               | I <sup>2</sup> C, LPC, SMBus, SPI, UART                              |

| Number of I/O           | 106                                                                  |

| Voltage - Supply        | 1.71V ~ 3.465V                                                       |

| Operating Temperature   | 0°C ~ 70°C                                                           |

| Mounting Type           | Surface Mount                                                        |

| Package / Case          | 128-TQFP                                                             |

| Supplier Device Package | 128-VTQFP (14x14)                                                    |

| Purchase URL            | https://www.e-xfl.com/product-detail/microchip-technology/mec1418-nu |

|                         |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| MEC140x       |            |             |                |                                |                         |                           |                |         |

|---------------|------------|-------------|----------------|--------------------------------|-------------------------|---------------------------|----------------|---------|

| VTQFP<br>Pin# | Mux        | Signal Name | Buffer<br>Type | Default<br>Buffer<br>Operation | Signal<br>Power<br>Well | Emulated<br>Power<br>Well | Gated<br>State | Notes   |

| 27            | 2          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                |         |

| 27            | 3          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                |         |

| 27            | Strap      |             |                |                                |                         |                           |                |         |

| 28            | Default: 0 | GPIO133     | PIO            | I-4                            | VTR                     | VTR/VCC                   | No Gate        |         |

| 28            | 1          | SHD_IO0     | PIO            |                                | VTR                     | VTR                       | Low            | Note 10 |

| 28            | 2          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                |         |

| 28            | 3          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                |         |

| 28            | Strap      |             |                |                                |                         |                           |                |         |

| 29            | Default: 0 | GPIO134     | PIO            | I-4                            | VTR                     | VTR/VCC                   | No Gate        |         |

| 29            | 1          | SHD_IO1     | PIO            |                                | VTR                     | VTR                       | Low            | Note 10 |

| 29            | 2          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                |         |

| 29            | 3          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                |         |

| 29            | Strap      |             |                |                                |                         |                           |                |         |

| 30            | Default: 0 | GPIO135     | PIO            | I-4                            | VTR                     | VTR/VCC                   | No Gate        |         |

| 30            | 1          | SHD_IO2     | PIO            |                                | VTR                     | VTR                       | Low            | Note 10 |

| 30            | 2          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                |         |

| 30            | 3          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                |         |

| 30            | Strap      |             |                |                                |                         |                           |                |         |

| 31            | Default: 0 | GPIO136     | PIO            | I-4                            | VTR                     | VTR/VCC                   | No Gate        |         |

| 31            | 1          | SHD_IO3     | PIO            |                                | VTR                     | VTR                       | Low            | Note 10 |

| 31            | 2          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                |         |

| 31            | 3          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                |         |

| 31            | Strap      |             |                |                                |                         |                           |                |         |

| 32            | Default: 0 | GPIO126     | PIO            | I-4                            | VTR                     | VTR/VCC                   | No Gate        |         |

| 32            | 1          | SHD_SCLK    | PIO            |                                | VTR                     | VTR                       | Reserved       | Note 10 |

| 32            | 2          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                |         |

| 32            | 3          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                |         |

| 32            | Strap      |             |                |                                |                         |                           |                |         |

| 33            | Default: 0 | GPIO062     | PIO            | I-4                            | VTR                     | VTR/VCC                   | No Gate        |         |

| 33            | 1          | SPI_IO3     | PIO            |                                | VTR                     | VTR                       | Low            |         |

| 33            | 2          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                |         |

| 33            | 3          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                |         |

| 33            | Strap      |             |                |                                |                         |                           |                |         |

| 34            | Default: 0 | GPIO030     | PIO            | I-4                            | VTR                     | VTR/VCC                   | No Gate        |         |

| 34            | 1          | BCM_INT0#   | PIO            |                                | VTR                     | VTR                       | High           |         |

| 34            | 2          | PWM4        | PIO            |                                | VTR                     | VTR                       | Reserved       |         |

| 34            | 3          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                |         |

| 34            | Strap      |             |                |                                |                         |                           |                |         |

| 35            | Default: 0 | GPIO031     | PIO            | I-4                            | VTR                     | VTR/VCC                   | No Gate        |         |

| 35            | 1          | BCM_DAT0    | PIO            |                                | VTR                     | VTR                       | Low            | Note 7  |

| 35            | 2          | PWM5        | PIO            |                                | VTR                     | VTR                       | Reserved       |         |

| 35            | 3          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                |         |

|               |            |             | Ν              | /IEC140x                       |                         |                           |                |           |

|---------------|------------|-------------|----------------|--------------------------------|-------------------------|---------------------------|----------------|-----------|

| VTQFP<br>Pin# | Mux        | Signal Name | Buffer<br>Type | Default<br>Buffer<br>Operation | Signal<br>Power<br>Well | Emulated<br>Power<br>Well | Gated<br>State | Notes     |

| 44            | 1          | PWM0        | PIO            |                                | VTR                     | VTR                       | Reserved       |           |

| 44            | 2          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                |           |

| 44            | 3          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                |           |

| 44            | Strap      |             |                |                                |                         |                           |                |           |

| 45            | Default: 0 | GPIO054     | PIO            | I-4                            | VTR                     | VTR/VCC                   | No Gate        |           |

| 45            | 1          | PWM1        | PIO            |                                | VTR                     | VTR                       | Reserved       | L         |

| 45            | 2          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                |           |

| 45            | 3          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                |           |

| 45            | Strap      |             |                |                                |                         |                           |                |           |

| 46            | Default: 0 | GPIO055     | PIO            | I-4                            | VTR                     | VTR/VCC                   | No Gate        |           |

| 46            | 1          | PWM2        | PIO            |                                | VTR                     | VTR                       | Reserved       |           |

| 46            | 2          | KSO08       | PIO            |                                | VTR                     | VTR                       | Reserved       | Note 15   |

| 46            | 3          | PVT_IO3     | PIO            |                                | VTR                     | VTR                       | Low            | Note 10   |

| 46            | Strap      |             |                |                                |                         |                           |                | <br>      |

| 47            | Default: 0 | GPIO056     | PIO            | I-4                            | VTR                     | VTR/VCC                   | No Gate        |           |

| 47            | 1          | PWM3        | PIO            |                                | VTR                     | VTR                       | Reserved       | <br>I     |

| 47            | 2          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                |           |

| 47            | 3          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                | ·         |

| 47            | Strap      |             |                |                                |                         |                           |                | ·         |

| 48            | Default: 0 | GPIO057     | PIO            | I-4                            | VTR                     | VTR/VCC                   | No Gate        |           |

| 48            | 1          | VCC_PWRGD   | PIO            |                                | VTR                     | VTR                       | High           |           |

| 48            | 2          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                | <br>I     |

| 48            | 3          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                | <br>I     |

| 48            | Strap      |             |                |                                |                         |                           |                | <br>I     |

| 49            | Default: 0 | GPIO060     | PIO            | I-4                            | VTR                     | VTR/VCC                   | No Gate        |           |

| 49            | 1          | KBRST       | PIO            |                                | VTR                     | VCC                       | Reserved       |           |

| 49            | 2          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                | <br>I     |

| 49            | 3          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                |           |

| 49            | Strap      |             |                |                                |                         |                           |                |           |

| 50            | Default: 0 | GPIO025     | PIO            | I-4                            | VTR                     | VTR/VCC                   | No Gate        |           |

| 50            | 1          | KSO07       | PIO            |                                | VTR                     | VTR                       | Reserved       | Note 15   |

| 50            | 2          | PVT_IO2     | PIO            |                                | VTR                     | VTR                       | Low            | Note 10   |

| 50            | 3          | Reserved    | Reserved       |                                | Reserved                | Reserved                  |                | ·         |

| 50            | Strap      |             |                |                                |                         |                           | 1              |           |

| 51            |            | VSS         | PWR            |                                | PWR                     | PWR                       |                |           |

| 51            |            |             |                |                                |                         |                           | 1              |           |

| 51            |            |             |                |                                |                         |                           | 1              | . <u></u> |

| 51            |            |             |                |                                |                         |                           | 1              |           |

| 51            | Strap      |             |                |                                |                         |                           | +              | . <u></u> |

|               | -          | GPIO026     | PIO            | I-4                            | VTR                     | VTR/VCC                   | No Gate        |           |

| 52            | Default: 0 | 00010       |                |                                |                         |                           |                |           |

| 52<br>52      | 1          | PS2_CLK1B   | PIO            |                                | VTR                     | VTR/VCC                   | Low            |           |

| Offset | 08h                                                                                                                                                                                                                                                                                               |      |         |                |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|----------------|

| Bits   | Description                                                                                                                                                                                                                                                                                       | Туре | Default | Reset<br>Event |

| 2      | BAR_CONFLICT<br>This bit is set to 1 whenever a BAR conflict occurs on an LPC<br>address. A Bar conflict occurs when more than one BAR matches<br>the address during of an LPC cycle access. Once this bit is set, it<br>remains set until cleared by being written with a 1.                     | R/WC | 0h      | nSYSR<br>ST    |

| 1      | EN_INTERNAL_ERR<br>When this bit is 0, only a BAR conflict, which occurs when two<br>BARs match the same LPC I/O address, will cause LPC_INTER-<br>NAL_ERR to be set. When this bit is 1, internal bus errors will also<br>cause LPC_INTERNAL_ERR to be set.                                      | R/W  | 0h      | nSYSR<br>ST    |

| 0      | LPC_INTERNAL_ERR<br>This bit is set whenever a BAR conflict or an internal bus error<br>occurs as a result of an LPC access. Once set, it remains set until<br>cleared by being written with a 1. This signal may be used to gen-<br>erate interrupts. See Section 4.6, "Interrupts," on page 98. | R/WC | 0h      | nSYSR<br>ST    |

# 4.11.3 EC SERIRQ REGISTER

| Offset | 0Ch                                                                                                                                                                                                                                               |      |         |                |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|----------------|

| Bits   | Description                                                                                                                                                                                                                                       | Туре | Default | Reset<br>Event |

| 31:1   | RESERVED                                                                                                                                                                                                                                          | RES  | -       | -              |

| 0      | EC_IRQ<br>If the LPC Logical Device is selected as the source for a Serial<br>Interrupt Request by an Interrupt Configuration register (see Sec-<br>tion 4.8.4.8, "SERIRQ Interrupts," on page 110), this bit is used as<br>the interrupt source. | R/W  | 0h      | nSYSR<br>ST    |

# 4.11.4 EC CLOCK CONTROL REGISTER

| Offset | 10h                                                                                                                                                                                                         |      |         |                |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|----------------|

| Bits   | Description                                                                                                                                                                                                 | Туре | Default | Reset<br>Event |

| 31:3   | RESERVED                                                                                                                                                                                                    | RES  | -       | -              |

| 2      | Handshake<br>This bit controls throughput of LPC transactions.<br>When this bit is a '0' the part supports a 33MHz PCI Clock. When<br>this bit is a '1', the part supports a PCI Clock from 24MHz to 33MHz. | RES  | 1h      | nSYSRS<br>T    |

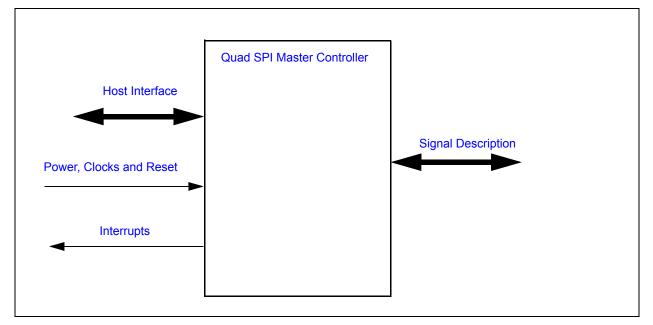

# 6.0 QUAD SPI MASTER CONTROLLER

## 6.1 Overview

The Quad SPI Master Controller may be used to communicate with various peripheral devices that use a Serial Peripheral Interface, such as EEPROMS, DACs and ADCs. The controller can be configured to support advanced SPI Flash devices with multi-phase access protocols. Data can be transfered in Half Duplex, Single Data Rate, Dual Data Rate and Quad Data Rate modes. In all modes and all SPI clock speeds, the controller supports back-to-back reads and writes without clock stretching if internal bandwidth permits.

# 6.2 References

No references have been cited for this feature.

#### 6.3 Terminology

No terminology for this block.

## 6.4 Interface

This block is designed to be accessed externally via the pin interface and internally via a registered host interface.

## FIGURE 6-1: I/O DIAGRAM OF BLOCK

### 6.5 Signal Description

#### TABLE 6-1:SIGNAL DESCRIPTION

| Name    | Direction | Description                                   |

|---------|-----------|-----------------------------------------------|

| SPI_CLK | Output    | SPI Clock output used to drive the SPCLK pin. |

| SPI_CS# | Output    | SPI chip select                               |

# **MEC140x/1x**

| Offset | 0Ch                                                                                                                    |      |         |                |

|--------|------------------------------------------------------------------------------------------------------------------------|------|---------|----------------|

| Bits   | Description                                                                                                            | Туре | Default | Reset<br>Event |

| 3      | HOLD_OUT_ENABLE                                                                                                        | R/W  | 0h      | RESET          |

|        | 1=HOLD SPI Output Port is driven<br>0=HOLD SPI Output Port is not driven                                               |      |         |                |

| 2      | HOLD_OUT_VALUE<br>This bit sets the value on the HOLD SPI Output Port if it is driven.<br>1=HOLD is driven to 1        | R/W  | 1h      | RESET          |

| 1      | 0=HOLD is driven to 0                                                                                                  | R/W  | Oh      | RESET          |

| I      | WRITE_PROTECT_OUT_ENABLE<br>1=WRITE PROTECT SPI Output Port is driven<br>0=WRITE PROTECT SPI Output Port is not driven | K/W  | UII     | RESET          |

| 0      | WRITE_PROTECT_OUT_VALUE<br>This bit sets the value on the WRITE PROTECT SPI Output Port if<br>it is driven.            | R/W  | 1h      | RESET          |

|        | 1=WRITE PROTECT is driven to 1<br>0=WRITE PROTECT is driven to 0                                                       |      |         |                |

# 6.11.5 QMSPI STATUS REGISTER

| Offset | 10h                                                                                                                                                                         |      |         |                |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|----------------|

| Bits   | Description                                                                                                                                                                 | Туре | Default | Reset<br>Event |

| 31:28  | Reserved                                                                                                                                                                    | R    | -       | -              |

| 27:24  | CURRENT_DESCRIPTION_BUFFER<br>This field shows the Description Buffer currently active. This field<br>has no meaning if Description Buffers are not enabled.                | R    | Oh      | RESET          |

| 23:17  | Reserved                                                                                                                                                                    | R    | -       | -              |

| 16     | TRANSFER_ACTIVE<br>1=A transfer is currently executing<br>0=No transfer currently in progress                                                                               | R    | Oh      | RESET          |

| 15     | RECEIVE_BUFFER_STALL<br>1=The SPI interface had been stalled due to a flow issue (an<br>attempt by the interface to write to a full Receive Buffer)<br>0=No stalls occurred | R/WC | 0h      | RESET          |

# **MEC140x/1x**

# 12.9.4 EC ADDRESS MSB REGISTER

| Offset | 03h                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |         |                |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|----------------|

| Bits   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Туре | Default | Reset<br>Event |

| 7      | <ul> <li>REGION</li> <li>The field specifies which of two segments in the 32-bit internal address space is to be accessed by the EC_Address[14:2] to generate accesses to the memory.</li> <li>1= The address defined by EC_Address[14:2] is relative to the base address specified by the Memory Base Address 1 Register.</li> <li>0= The address defined by EC_Address[14:2] is relative to the base address specified by the Memory Base Address 0 Register.</li> </ul> | R/W  | Oh      | nSYSR<br>ST    |

| 6:0    | EC_ADDRESS_MSB<br>This field defines bits[14:8] of EC_Address. Bits[1:0] of the EC_Ad-<br>dress are always forced to 00b.<br>The EC_Address is aligned on a DWord boundary. It is the address<br>of the memory being accessed by EC Data Byte 0 Register, which<br>is an offset from the programmed base address of the selected<br>REGION.                                                                                                                                | R/W  | Oh      | nSYSR<br>ST    |

# 12.9.5 EC DATA BYTE 0 REGISTER

| Offset | 04h                                                                                                            |      |         |                |

|--------|----------------------------------------------------------------------------------------------------------------|------|---------|----------------|

| Bits   | Description                                                                                                    | Туре | Default | Reset<br>Event |

| 7:0    | EC_DATA_BYTE_0<br>This is byte 0 (Least Significant Byte) of the 32-bit EC Data Regis-<br>ter.                 | R/W  | 0h      | nSYSR<br>ST    |

|        | Use of the Data Byte registers to access EC memory is defined in detail in Section 12.8.2, "EC Data Register". |      |         |                |

# 12.9.6 EC DATA BYTE 1 REGISTER

| Offset | 05h                                                                                                                                                                                   |      |         |                |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|----------------|

| Bits   | Description                                                                                                                                                                           | Туре | Default | Reset<br>Event |

| 7:0    | EC_DATA_BYTE_1<br>This is byte 1 of the 32-bit EC Data Register.<br>Use of the Data Byte registers to access EC memory is defined in<br>detail in Section 12.8.2, "EC Data Register". | R/W  | 0h      | nSYSR<br>ST    |

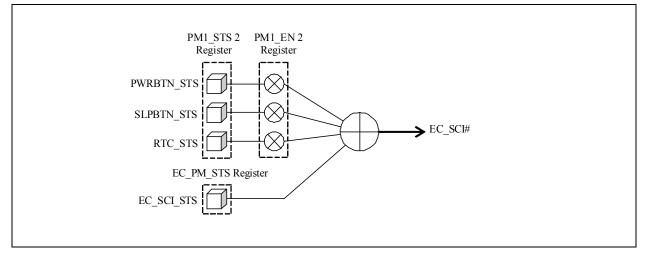

FIGURE 15-2: describes the relationship of PM1 Status and Enable bits to the EC\_SCI# pin.

#### 15.11 Runtime Registers

The registers listed in the Runtime Register Summary table are for a single instance of the ACPI PM1 interface. The addresses of each register listed in this table are defined as a relative offset to the host "Base Address" defined in the Runtime Register Base Address Table.

#### TABLE 15-2: RUNTIME REGISTER BASE ADDRESS TABLE

| Block Instance  | Instance<br>Number | Host | Address Space                 | Base Address   |

|-----------------|--------------------|------|-------------------------------|----------------|

| ACPI PM1 Inter- | 0                  | LPC  | I/O                           | Programmed BAR |

| face            | 0                  | EC   | 32-bit internal address space | 000F_1400h     |

The Base Address indicates where the first register can be accessed in a particular address space for a block instance.

All the registers in Table 15-3, "Runtime Registers Summary" may be accessed by the Host and EC with the exception of the EC\_PM\_STS Register register which is EC-accessed only.

#### TABLE 15-3: RUNTIME REGISTERS SUMMARY

| Offset | Register Name                         |

|--------|---------------------------------------|

| 00h    | Power Management 1 Status 1 Register  |

| 01h    | Power Management 1 Status 2 Register  |

| 02h    | Power Management 1 Enable 1 Register  |

| 03h    | Power Management 1 Enable 2 Register  |

| 04h    | Power Management 1 Control 1 Register |

| 05h    | Power Management 1 Control 2 Register |

| 06h    | Power Management 2 Control 1 Register |

© 2015 - 2016 Microchip Technology Inc.

# **MEC140x/1x**

# 17.11.1 RECEIVE BUFFER REGISTER

| Offset | 0h (DLAB=0)                                                                                                                                                                                                                                                                                                                                                                                                       |      |         |                |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|----------------|

| Bits   | Description                                                                                                                                                                                                                                                                                                                                                                                                       | Туре | Default | Reset<br>Event |

| 7:0    | RECEIVED_DATA<br>This register holds the received incoming data byte. Bit 0 is the<br>least significant bit, which is transmitted and received first.<br>Received data is double buffered; this uses an additional shift reg-<br>ister to receive the serial data stream and convert it to a parallel 8<br>bit word which is transferred to the Receive Buffer register. The<br>shift register is not accessible. | R    | 0h      | RESET          |

## 17.11.2 TRANSMIT BUFFER REGISTER

| Offset | 0h (DLAB=0)                                                                                                                                                                                                                                                                                                                                              |      |         |                |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|----------------|

| Bits   | Description                                                                                                                                                                                                                                                                                                                                              | Туре | Default | Reset<br>Event |

| 7:0    | TRANSMIT_DATA<br>This register contains the data byte to be transmitted. The trans-<br>mit buffer is double buffered, utilizing an additional shift register<br>(not accessible) to convert the 8 bit data word to a serial format.<br>This shift register is loaded from the Transmit Buffer when the<br>transmission of the previous byte is complete. | W    | 0h      | RESET          |

# 17.11.3 PROGRAMMABLE BAUD RATE GENERATOR LSB REGISTER

| Offset | 00h (DLAB=1)                                                           |      |         |                |

|--------|------------------------------------------------------------------------|------|---------|----------------|

| Bits   | Description                                                            | Туре | Default | Reset<br>Event |

| 7:0    | BAUD_RATE_DIVISOR_LSB<br>See Section 17.9.1, "Programmable Baud Rate". | R/W  | 0h      | RESET          |

| SUBWEEK_<br>TICK | Source                | SPISR | Frequency | Minimum<br>Duration | Maximum<br>Duration |  |  |  |

|------------------|-----------------------|-------|-----------|---------------------|---------------------|--|--|--|

| 5                | Week Counter<br>bit 5 | n/a   | 31.25 Hz  | 32 sec              | 272.5 min           |  |  |  |

| 6                | Week Counter<br>bit 7 | n/a   | 7.8125 Hz | 128 sec             | 18.17 hour          |  |  |  |

| 7                | Week Counter<br>bit 9 | n/a   | 1.95 Hz   | 512 sec             | 72.68 hour          |  |  |  |

TABLE 21-7: SUB-WEEK ALARM COUNTER CLOCK (CONTINUED)

- **Note 1:** The Week Alarm Counter **must not** be modified by firmware if Sub-Week Alarm Counter is using the Week Alarm Counter as its clock source (i.e., the SUBWEEK\_TICK field is set to any of the values 4, 5, 6 or 7). The Sub-Week Alarm Counter must be disabled before changing the Week Alarm Counter. For example, the following sequence may be used:

- 1. Write 0h to the Sub-Week Alarm Counter Register (disabling the Sub-Week Counter)

- 2. Write the Week Alarm Counter Register

- 3. Write a new value to the Sub-Week Alarm Counter Register, restarting the Sub-Week Counter

#### 21.9.1.3 15-bit Clock Divider

This counter is 15 bits wide. The clock for this counter is 32KHz\_Clk, and as long as the RTC/Week Timer is enabled, it is incremented at 32.768KHz rate. The Clock Divider automatically The Clock Divider generates a clock out of 1 Hz when the counter wraps from 7FFFh to 0h.

By selecting one of the 15 bits of the counter, using the Sub-Second Programmable Interrupt Select Register, the Clock Divider can be used either to generate a time base for the Sub-Week Alarm Counter or as an isochronous interrupt to the EC, the SUB\_SECOND interrupt.. See Table 21-10, "SPISR Encoding" for a list of available frequencies.

#### 21.9.2 TIMER VALID STATUS

If power on reset occurs on the VBAT power rail while the main device power is off, the counters in the RTC/Week Alarm are invalid. If firmware detects a POR on the VBAT power rail after a system boot, by checking the status bits in the Power, Clocks and Resets registers, the RTC/Week Alarm block must be reinitialized.

#### 21.9.3 APPLICATION NOTE: REGISTER TIMING

Register writes in the RTC/Week Alarm complete within two cycles of the 32KHz\_Clk clock. The write completes even if the main system clock is stopped before the two cycles of the 32K clock complete. Register reads complete in one cycle of the internal bus clock.

All RTC/Week Alarm interrupts that are asserted within the same cycle of the 32KHz\_Clk clock are synchronously asserted to the EC.

#### 21.9.4 APPLICATION NOTE: USE OF THE WEEK TIMER AS A 43-BIT COUNTER

The Week Timer cannot be directly used as a 42-bit counter that is incremented directly by the 32.768KHz clock domain. The upper 28 bits (28-bit Week Alarm Counter) are incremented at a 1Hz rate and the lower 16 bits (15-bit Clock Divider) are incremented at a 32.768KHz rate, but the increments are not performed in parallel. In particular, the upper 28 bits are incremented when the lower 15 bits increment from 0 to 1, so as long as the Clock Divider Register is 0 the two registers together, treated as a single value, have a smaller value then before the lower register rolled over from 7FFFh to 0h.

The following code can be used to treat the two registers as a single large counter. This example extracts a 32-bit value from the middle of the 43-bit counter:

```

dword TIME_STAMP(void)

{

AHB_dword wct_value;

AHB_dword cd_value1;

AHB_dword cd_value2;

dword irqEnableSave;

```

| Offset | See Table 22-2, "Register Summary"                                  |                                                                                                                                                                                                                                                                                                                                             |     |           |                |  |  |  |

|--------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|----------------|--|--|--|

| Bits   | Description                                                         |                                                                                                                                                                                                                                                                                                                                             |     | Default   | Reset<br>Event |  |  |  |

| 6:4    |                                                                     | vetection (int_det)<br>upt detection bits determine the event that generates a<br>ent.                                                                                                                                                                                                                                                      | R/W | Note 22-6 | nSYSRS<br>T    |  |  |  |

|        | Note:                                                               | See Table 22-3, "Edge Enable and Interrupt Detection Bits Definition".                                                                                                                                                                                                                                                                      |     |           |                |  |  |  |

|        | Note:                                                               | Since the GPIO input is always available, even when the GPIO is not selected as the alternate function, the GPIO interrupts may be used for detecting pin activity on alternate functions. The only exception to this is the analog functions (e.g., ADC, DAC, Comparator inputs)                                                           |     |           |                |  |  |  |

| 3:2    | The Powe<br>options. Th<br>(i.e., gated<br>The Emula<br>indicates t | ting Signals<br>r Gating Signals provide the chip Power Emulation<br>he pin will be tristated when the selected power well is off<br>I) as indicated.<br>ated Power Well column defined in Pin Multiplexing tables<br>he emulation options supported for each signal. The Sig-<br>Well column defines the buffer power supply per function. | R/W | Note 22-6 | nSYSRS<br>T    |  |  |  |

|        | 01 = VCC                                                            |                                                                                                                                                                                                                                                                                                                                             |     |           |                |  |  |  |

| 1:0    | tor device<br>00 = None<br>01 = Pull L<br>10 = Pull I<br>11 = Repe  | J_PD)<br>are used to enable an internal pull-up or pull-down resis-<br>on the pin.<br>Pin tristates when no active driver is present on the pin.<br>Jp Enabled<br>Down Enabled (Note 22-7)<br>ater mode. Pin is kept at previous voltage level when no<br>er is present on the pin.                                                         | R/W | Note 22-6 | nSYSRS<br>T    |  |  |  |

**Note 22-6** See Section 22.5.4, "Pin Control Registers," on page 320 for the offset and default values for each GPIO Pin Control Register.

**Note 22-7** The internal pull-down control should not be selected when configured for an LPC function, which uses the PCI\_PIO buffer. Signals with PCI\_PIO buffer type do not have an internal pull-down. This configuration option has no effect on the pin.

# 23.12 SMBus Registers

The registers listed in the *SMBus Core Register Summary* table in the SMBus Controller Core Interface specification (Ref [1]) are for a single instance of the SMBus Controller Core. The addresses of each register listed in this table are defined as a relative offset to the host "Base Address" defined in the following table:

#### TABLE 23-2: EC-ONLY REGISTER BASE ADDRESS TABLE

| Block Instance   | Instance<br>Number | Host | Address Space                    | Base Address |

|------------------|--------------------|------|----------------------------------|--------------|

| SMBus Controller | 0                  | EC   | 32-bit internal<br>address space | 0000_1800h   |

| SMBus Controller | 1                  | EC   | 32-bit internal address space    | 0000_AC00h   |

| SMBus Controller | 2                  | EC   | 32-bit internal address space    | 0000_B000h   |

**Note:** The Base Address indicates where the first register can be accessed in a particular address space for a block instance.

# 24.10 DMA Main Registers

The addresses of each register listed in these tables are defined as a relative offset to the "Base Address" defined in the DMA Main Register Base Address. The Base Address indicates where the first register can be accessed in a particular bank of registers.

#### TABLE 24-3: DMA MAIN REGISTER BASE ADDRESS

| Instance Name  | Channel<br>Number | Host | Address Space                 | Base Address |

|----------------|-------------------|------|-------------------------------|--------------|

| DMA Controller | Main Block        | EC   | 32-bit internal address space | 0000_2400h   |

#### TABLE 24-4: DMA MAIN REGISTER SUMMARY

| Offset | REGISTER NAME (Mnemonic)  |

|--------|---------------------------|

| 00h    | DMA Main Control Register |

| 04h    | DMA Data Packet Register  |

#### 24.10.1 DMA MAIN CONTROL REGISTER

| Offset | 00h                                                                                                                                             |      |         |                |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|----------------|

| Bits   | Description                                                                                                                                     | Туре | Default | Reset<br>Event |

| 7:2    | Reserved                                                                                                                                        | R    | -       | -              |

| 1      | SOFT_RESET<br>Soft reset the entire module.<br>This bit is self-clearing.                                                                       | W    | 0b      | -              |

| 0      | ACTIVATE<br>Enable the blocks operation.<br>1=Enable block. Each individual channel must be enabled sepa-<br>rately.<br>0=Disable all channels. | R/WS | Ob      | DMA_<br>RESET  |

#### 24.10.2 DMA DATA PACKET REGISTER

| Offset | 04h                                                                                                                                                     |      |         |                |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|----------------|

| Bits   | Description                                                                                                                                             | Туре | Default | Reset<br>Event |

| 31:0   | DATA_PACKET<br>Debug register that has the data that is stored in the Data Packet.<br>This data is read data from the currently active transfer source. | R    | 0000h   | -              |

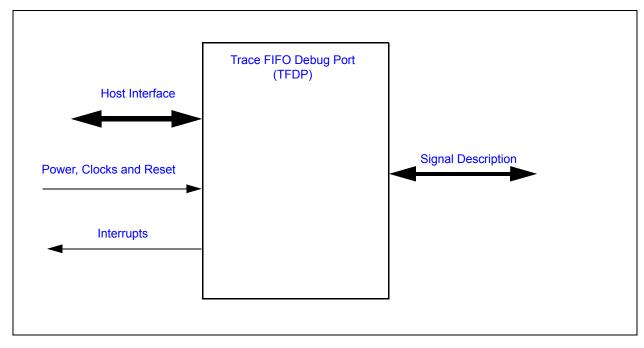

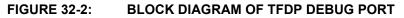

# 32.0 TRACE FIFO DEBUG PORT (TFDP)

# 32.1 Introduction

The TFDP serially transmits Embedded Controller (EC)-originated diagnostic vectors to an external debug trace system.

## 32.2 References

No references have been cited for this chapter.

## 32.3 Terminology

There is no terminology defined for this chapter.

## 32.4 Interface

This block is designed to be accessed externally via the pin interface and internally via a registered host interface.

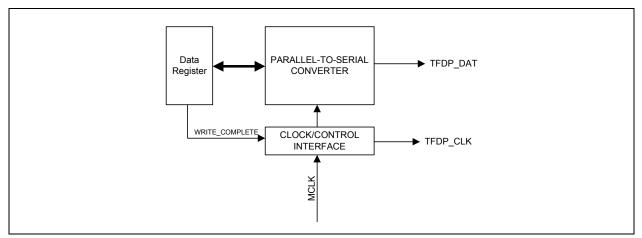

#### FIGURE 32-1: I/O DIAGRAM OF BLOCK

# 32.5 Signal Description

The Signal Description Table lists the signals that are typically routed to the pin interface.

| TABLE 32-1: | SIGNAL DESCRIPTION |

|-------------|--------------------|

|-------------|--------------------|

| Name      | Direction | Description                              |

|-----------|-----------|------------------------------------------|

| TFDP Clk  | Output    | Derived from EC Bus Clock.               |

| TFDP Data | Output    | Serialized data shifted out by TFDP Clk. |

The firmware executing on the embedded controller writes to the Debug Data Register to initiate a transfer cycle (32.11). At first, data from the Debug Data Register is shifted into the LSB. Afterwards, it is transmitted at the rate of one byte per transfer cycle.

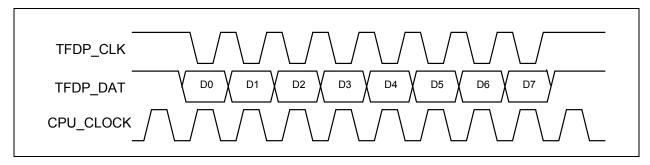

Data is transferred in one direction only from the Debug Data Register to the external interface. The data is shifted out at the clock edge. The clock edge is selected by the EDGE\_SEL bit in the Debug Control Register. After being shifted out, valid data is guaranteed at the opposite edge of the TFDP\_CLK. For example, when the EDGE\_SEL bit is '0' (default), valid data is provided at the falling edge of TFDP\_CLK. The Setup Time (to the falling edge of TFDP\_CLK) is 10 ns, minimum. The Hold Time is 1 ns, minimum.

When the Serial Debug Port is inactive, the TFDP\_CLK and TFDP\_DAT outputs are '1.' The EC Bus Clock clock input is the transfer clock.

#### FIGURE 32-3: DATA TRANSFER

#### 32.11 EC-Only Registers

The registers listed in the EC-Only Register Summary table are for a single instance of the Trace FIFO Debug Port (TFDP). The addresses of each register listed in this table are defined as a relative offset to the host "Base Address" defined in the EC-Only Register Base Address Table.

| TABLE 32-2: E | C-ONLY REGISTER BASE ADDRESS TABLE |

|---------------|------------------------------------|

|---------------|------------------------------------|

| Block Instance  | Instance<br>Number | Host | Address Space                 | Base Address |

|-----------------|--------------------|------|-------------------------------|--------------|

| TFDP Debug Port | 0                  | EC   | 32-bit internal address space | 0000_8C00h   |

#### TABLE 40-1: SIGNAL DESCRIPTION (CONTINUED)

| Name      | Direction | Description         |

|-----------|-----------|---------------------|

| CMP_VOUT0 | Output    | Comparator 0 output |

| CMP_VOUT1 | Output    | Comparator 1 output |

#### 40.6 Host Interface

The registers defined for the Comparator Interface are only accessible by the embedded controller. The Comparator Registers for both comparators are located in one register in the EC Subsystem register bank. See Section 34.8.2, "Comparator Control," on page 435.

#### 40.7 Power, Clocks and Reset

This section defines the Power, Clock, and Reset parameters of the block.

#### 40.7.1 POWER DOMAINS

| Name | Description                                                         |

|------|---------------------------------------------------------------------|

| VTR  | The logic implemented in this block are powered by this power well. |

#### 40.7.2 CLOCK INPUTS

This component does not require a clock input.

#### 40.7.3 RESETS

| Name       | Description                                                                                 |

|------------|---------------------------------------------------------------------------------------------|

| VTR_RESET# | This signal resets all the register in the EC Subsystem that interact with the comparators. |

#### 40.8 Interrupts

The comparators do not have a dedicated interrupt output event. An interrupt can be generated by the GPIO which shares the pin with the comparator output signal.

- · GPIO124/CMP VOUT0

- GPIO120/CMP\_VOUT1

The GPIO interrupt is very configurable, thereby allowing CMP\_VOUTx signal to generate an event when the CMP\_VINx input is greater than the CMP\_VREFx input or when it is less than the CMP\_VREFx input. See the definition of Bits[7:4] of the Pin Control Register on page 329.

#### 40.9 Low Power Modes

Each comparator is in its lowest powered state when its ENABLE bit is '0'.

# 42.0 ELECTRICAL SPECIFICATIONS

# 42.1 Maximum Ratings\*

\*Stresses exceeding those listed could cause permanent damage to the device. This is a stress rating only and functional operation of the device at any other condition above those indicated in the operation sections of this specification is not implied.

**Note:** When powering this device from laboratory or system power supplies, it is important that the Absolute Maximum Ratings not be exceeded or device failure can result. Some power supplies exhibit voltage spikes on their outputs when the AC power is switched on or off. In addition, voltage transients on the AC power line may appear on the DC output. If this possibility exists, it is suggested that a clamp circuit be used.

# 42.1.1 ABSOLUTE MAXIMUM THERMAL RATINGS

# TABLE 42-1: ABSOLUTE MAXIMUM THERMAL RATINGS

| Parameter                   | Maximum Limits                                       |

|-----------------------------|------------------------------------------------------|

| Operating Temperature Range | 0°C to +70°C Commercial<br>-40°C to +85°C Industrial |

| Storage Temperature Range   | -55° to +150°C                                       |

| Lead Temperature Range      | Refer to JEDEC Spec J-STD-020B                       |

# 42.1.2 ABSOLUTE MAXIMUM SUPPLY VOLTAGE RATINGS

#### TABLE 42-2:ABSOLUTE POWER SUPPLY RATINGS

| Symbol    | Parameter                                                                       | Maximum Limits   |

|-----------|---------------------------------------------------------------------------------|------------------|

| VBAT      | 3.0V Battery Backup Power Supply with respect to ground                         | -0.3V to +3.63V  |

| VTR       | 3.3V Suspend Power Supply with respect to ground                                | -0.3V to +3.465V |

| VTR_33_18 | 3.3V or 1.8V Power Supply with respect to ground                                | -0.3V to +3.465V |

| VCC       | 3.3V Main Power Supply with respect to ground (Con-<br>nected to VCC_PWRGD pin) | -0.3V to +3.465V |

#### 42.1.3 ABSOLUTE MAXIMUM I/O VOLTAGE RATINGS

| Parameter                                                                   | Maximum Limits                                                      |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------|

| Voltage with respect to ground on any pin without back-<br>drive protection | -0.3V to (Power Supply used to power the buffer) + 0.3V (Note 42-1) |

**Note 42-1** The Power Supply used to power the buffer is shown in the Signal Power Well column of the Pin Multiplexing Tables in **Section 2.0 "Pin Configuration**".

# 43.2 Clocking AC Timing Characteristics

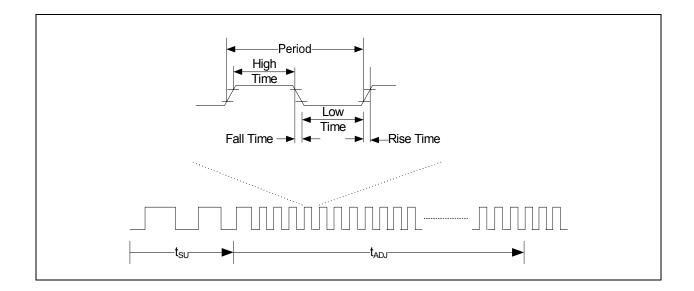

# FIGURE 43-2: CLOCK TIMING DIAGRAM

## TABLE 43-5: CLOCK TIMING PARAMETERS

| Clock                     | Parameters                                                                                                                                                      | Symbol           | MIN                 | ТҮР  | МАХ                 | Units |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------|------|---------------------|-------|

| 48 MHz Ring<br>Oscillator | Start-up accuracy (without 32 kHz present)                                                                                                                      | f <sub>SU</sub>  | 22                  | -    | 53                  | MHz   |

|                           | Start-up delay from 0 MHz to Start-<br>up accuracy                                                                                                              | t <sub>SU</sub>  | -                   | -    | 6                   | μs    |

|                           | Operating Frequency (with exter-<br>nal 32kHz clock source present<br>after frequency lock to 48 MHz)                                                           | f <sub>OP</sub>  | 47.04               | 48   | 48.95               | MHz   |

|                           | Operating Frequency (with inter-<br>nal 32 kHz oscillator present after<br>frequency lock to 48 MHz)<br>Note 43-3                                               | f <sub>OP</sub>  | 46.08               | 48   | 49.92               | MHz   |

|                           | Adjustment Delay from Start-up<br>accuracy to Operating accuracy<br>(time to attain frequency lock - with<br>32 kHz present)                                    | t <sub>ADJ</sub> | 0.03                | -    | 4<br>(Note 43-3)    | ms    |

|                           | Adjustment Delay when resuming<br>from Heavy Sleep 3 and System<br>Deepest Sleep state.<br>(time to re-attain frequency lock -<br>with external 32 kHz present) | t <sub>ADJ</sub> | -                   | 0.60 | 1<br>(Note 43-3)    | ms    |

|                           | Operating Frequency (with exter-<br>nal 32 kHz removed after fre-<br>quency locked to 48 MHz)                                                                   | f <sub>OP</sub>  | 43.2<br>(Note 43-5) | -    | 52.8<br>(Note 43-5) | MHz   |

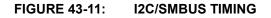

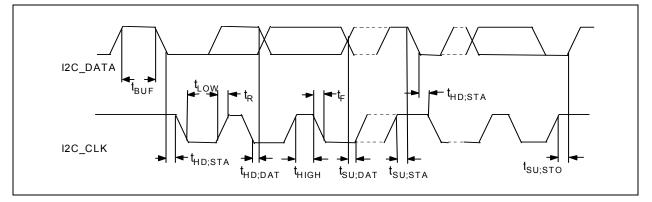

# 43.13 I2C/SMBus Timing

| TABLE 43-14: | <b>I2C/SMBUS TIMING PARAMETERS</b> |

|--------------|------------------------------------|

|--------------|------------------------------------|

| Symbol              | Parameter                   | Standard-<br>Mode |     | Fast-<br>Mode |     | Fast-<br>Mode Plus |      | Units |

|---------------------|-----------------------------|-------------------|-----|---------------|-----|--------------------|------|-------|

|                     |                             | MIN               | MAX | MIN           | MAX | MIN                | MAX  |       |

| f <sub>SCL</sub>    | SCL Clock Frequency         |                   | 100 |               | 400 |                    | 1000 | kHz   |

| t <sub>BUF</sub>    | Bus Free Time               | 4.7               |     | 1.3           |     | 0.5                |      | μs    |

| t <sub>SU;STA</sub> | START Condition Set-Up Time | 4.7               |     | 0.6           |     | 0.26               |      | μs    |

| t <sub>HD;STA</sub> | START Condition Hold Time   | 4.0               |     | 0.6           |     | 0.26               |      | μs    |

| t <sub>LOW</sub>    | SCL LOW Time                | 4.7               |     | 1.3           |     | 0.5                |      | μs    |

| t <sub>HIGH</sub>   | SCL HIGH Time               | 4.0               |     | 0.6           |     | 0.26               |      | μs    |

| t <sub>R</sub>      | SCL and SDA Rise Time       |                   | 1.0 |               | 0.3 |                    | 0.12 | μs    |

| t <sub>F</sub>      | SCL and SDA Fall Time       |                   | 0.3 |               | 0.3 |                    | 0.12 | μs    |

| t <sub>SU;DAT</sub> | Data Set-Up Time            | 0.25              |     | 0.1           |     | 0.05               |      | μs    |

| t <sub>HD;DAT</sub> | Data Hold Time              | 0                 |     | 0             |     | 0                  |      | μs    |

| t <sub>su;sto</sub> | STOP Condition Set-Up Time  | 4.0               |     | 0.6           |     | 0.26               |      | μs    |

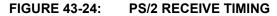

#### TABLE 43-25: PS/2 CHANNEL RECEIVE TIMING DIAGRAM PARAMETERS

| Name | Descritpion                                                                                                         | MIN | ТҮР | MAX   | Units |

|------|---------------------------------------------------------------------------------------------------------------------|-----|-----|-------|-------|

| t1   | The PS/2 Channel's CLK and DATA lines are floated following PS2_EN=1 and PS2_T/R=0.                                 |     |     | 1000  | ns    |

| t2   | Period of CLK                                                                                                       | 60  |     | 302   | μs    |

| t3   | Duration of CLK high (active)                                                                                       | 30  |     | 151   |       |

| t4   | Duration of CLK low (inactive)                                                                                      |     |     |       |       |

| t5   | DATA setup time to falling edge of CLK.<br>MEC140x/1x samples the data line on the<br>falling CLK edge.             | 1   |     |       |       |

| t6   | DATA hold time from falling edge of CLK.<br>MEC140x/1x samples the data line on the<br>falling CLK edge.            | 2   |     |       |       |

| t7   | Duration of Data Frame. Falling edge of<br>Start bit CLK (1st clk) to falling edge of<br>Parity bit CLK (10th clk). |     |     | 2.002 | ms    |

| t8   | Falling edge of 11th CLK to RDATA_RDY asserted.                                                                     |     |     | 1.6   | μs    |

# **PRODUCT IDENTIFICATION SYSTEM**

Not all of the possible combinations of Device, Temperature Range and Package may be offered for sale. To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO. <sup>(1)</sup> -    | <u>[X/] XXX<sup>(2)</sup> - [XX] - [X]<sup>(3)</sup></u>                                                                                                                                                                                                                                                                                                                                                | Examples:                                                                                                                                                                                                                   |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              | nperature Package ROM Version Tape and Ree<br>Range Option                                                                                                                                                                                                                                                                                                                                              | <ul> <li>a) MEC1404-NU = 128KB SRAM, LPC<br/>Interface, Commercial temperature,<br/>128 VTQFP</li> </ul>                                                                                                                    |

| Devices:                     | ndicate designators that have blank options<br>MEC1404 <sup>(1)</sup> = 128KB SRAM, LPC Interface<br>MEC1408 <sup>(1)</sup> = 160KB SRAM, LPC Interface<br>MEC1408 <sup>(1)</sup> = 192KB SRAM, LPC Interface<br>MEC1414 <sup>(1)</sup> = 128KB SRAM, eSPI or LPC Interface<br>MEC1416 <sup>(1)</sup> = 160KB SRAM, eSPI or LPC Interface<br>MEC1418 <sup>(1)</sup> = 192KB SRAM, eSPI or LPC Interface | <ul> <li>b) MEC1406-SZ = 160KB SRAM, LPC<br/>Interface, Commercial temperature,<br/>144 WFBGA</li> <li>c) MEC1418-NU-TR = 192KB SRAM,<br/>eSPI or LPC Interface, Commercial<br/>temperature, 128 VTQFP, tape and</li> </ul> |

| Temperature<br>Range Option: | Blank = 0°C to +70°C (Commercial)<br>I/ = -40°C to +85°C (Industrial)                                                                                                                                                                                                                                                                                                                                   | Note 1: These products meet the halogen maximum concentration values per IEC61249-2-21.                                                                                                                                     |

| Package:                     | NU = 128 pin VTQFP <sup>(2)</sup><br>SZ = 144 pin WFBGA <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                  | Note 2: All package options are RoHS compliant.<br>For RoHS compliance and environmental<br>information, please visit<br><u>http://www.microchip.com/pagehandler/en-us/aboutus/ehs.html</u> .                               |

| ROM Version:                 | Blank = Standard ROM                                                                                                                                                                                                                                                                                                                                                                                    | Note 3: Tape and Reel identifier only appears in the<br>catalog part number description. This identi-<br>fier is used for ordering purposes and is not                                                                      |

| Tape and Reel<br>Option:     | Blank = Tray packaging<br>TR = Tape and Reel <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                             | printed on the device package. Check with<br>your Microchip Sales Office for package<br>availability with the Tape and Reel option.                                                                                         |