Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | TriCore™                                                                          |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 150MHz                                                                            |

| Connectivity               | ASC, CANbus, EBI/EMI, MLI, MSC, SSC                                               |

| Peripherals                | DMA, POR, WDT                                                                     |

| Number of I/O              | 123                                                                               |

| Program Memory Size        | 2MB (2M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 256K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.42V ~ 1.58V                                                                     |

| Data Converters            | A/D 44x12b                                                                        |

| Oscillator Type            | External                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 416-BGA                                                                           |

| Supplier Device Package    | PG-BGA-416                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/tc1796256f150ebckduma1 |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Summary of Features**

### **Ordering Information**

The ordering code for Infineon microcontrollers provides an exact reference to the required product. This ordering code identifies:

- The derivative itself, i.e. its function set, the temperature range, and the supply voltage

- The package and the type of delivery.

For the available ordering codes for the TC1796 please refer to the **"Product Catalog Microcontrollers"**, which summarizes all available microcontroller variants.

This document describes the derivatives of the device. The **Table 1** enumerates these derivatives and summarizes the differences.

### Table 1TC1796 Derivative Synopsis

| Derivative          | Ambient Temperature Range                        |

|---------------------|--------------------------------------------------|

| SAK-TC1796-256F150E | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$ |

## **General Device Information**

| Table 2                  | able 2 Pin Definitions and Functions (cont d) |                  |              |                    |                                                                                                                |  |  |  |  |  |

|--------------------------|-----------------------------------------------|------------------|--------------|--------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Symbol                   | Pins                                          | I/O              | Pad<br>Class | Power<br>Supply    | Functions                                                                                                      |  |  |  |  |  |

| BFCLKO                   | AF25                                          | 0                | B2           | V <sub>DDEBU</sub> | Burst Mode Flash Clock Output (non-<br>differential)                                                           |  |  |  |  |  |

| BFCLKI                   | AF24                                          | I                | B1           | _                  | Burst Mode Flash Clock Input<br>(feedback clock)                                                               |  |  |  |  |  |

| RD                       | AF20                                          | 0                | B1           |                    | Read Control Line                                                                                              |  |  |  |  |  |

| RD/WR                    | AF21                                          | 0                | B1           | 1                  | Write Control Line                                                                                             |  |  |  |  |  |

| ADV                      | AF22                                          | 0                | B1           |                    | Address Valid Output                                                                                           |  |  |  |  |  |

| MR/W                     | AF19                                          | 0                | B1           |                    | Motorola-style Read/Write Control<br>Signal                                                                    |  |  |  |  |  |

| BC0<br>BC1<br>BC2<br>BC3 | AE17<br>AD17<br>AF18<br>AE18                  | 0<br>0<br>0<br>0 | B1           |                    | Byte Control Lines<br>Byte control line 0<br>Byte control line 1<br>Byte control line 2<br>Byte control line 3 |  |  |  |  |  |

| WAIT                     | AE20                                          | I                | B1           |                    | Wait Input for inserting Wait-States                                                                           |  |  |  |  |  |

| BAA                      | AF23                                          | 0                | B1           |                    | Burst Address Advance Output                                                                                   |  |  |  |  |  |

| HOLD                     | AF17                                          | I                | B1           |                    | Hold Request Input                                                                                             |  |  |  |  |  |

| HLDA                     | AD18                                          | 0                | B1           |                    | Hold Acknowledge Output                                                                                        |  |  |  |  |  |

| BREQ                     | AD22                                          | 0                | B1           | 1                  | Bus Request Output                                                                                             |  |  |  |  |  |

Table 2 Pin Definitions and Functions (cont'd)

## **General Device Information**

| Table 2Pin Definitions and Functions (cont'd) |      |     |              |                  |               |                                                                                                                                                        |  |  |  |  |

|-----------------------------------------------|------|-----|--------------|------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol                                        | Pins | I/O | Pad<br>Class | Power<br>Supply  | Functions     |                                                                                                                                                        |  |  |  |  |

| Р5                                            |      | I/O | A2           | V <sub>DDP</sub> | purpose I/O p | -bit bi-directional general-<br>ort which can be alternatively<br>0/1 or MSC0/1 lines.                                                                 |  |  |  |  |

| P5.0                                          | B13  | I/O |              |                  | RXD0A         | ASC0 receiver input /<br>output A                                                                                                                      |  |  |  |  |

| P5.1                                          | A13  | 0   |              |                  | TXD0A         | ASC0 transmitter output A                                                                                                                              |  |  |  |  |

| P5.2                                          | A14  | I/O |              |                  | RXD1A         | ASC1 receiver input /                                                                                                                                  |  |  |  |  |

| P5.3                                          | B14  | 0   |              |                  | TXD1A         | ASC1 transmitter output A<br>P5.3 is latched with the<br>rising edge of PORST if<br>BYPASS = 1 and stored in<br>inverted state as bit<br>OSC CON.MOSC. |  |  |  |  |

| P5.4                                          | C15  | 0   |              |                  | EN00          | MSC0 device select<br>output 0                                                                                                                         |  |  |  |  |

|                                               |      | 0   |              |                  | RREADY0B      | MLI0 receive channel ready output B                                                                                                                    |  |  |  |  |

| P5.5                                          | C14  | I   |              |                  | SDI0          | MSC0 serial data input                                                                                                                                 |  |  |  |  |

| P5.6                                          | B15  | 0   |              |                  | EN10          | MSC1 device select<br>output 0                                                                                                                         |  |  |  |  |

|                                               |      | 0   |              |                  | TVALID0B      | MLI0 transmit channel valid output B                                                                                                                   |  |  |  |  |

| P5.7                                          | A15  | I   |              |                  | SDI1          | MSC1 serial data input                                                                                                                                 |  |  |  |  |

Data Sheet

## **General Device Information**

| Table 2                          | Table 2Pin Definitions and Functions (cont'd) |        |              |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|----------------------------------|-----------------------------------------------|--------|--------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Symbol                           | Pins                                          | I/O    | Pad<br>Class | Power<br>Supply  | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| P10.0<br>P10.1<br>P10.2<br>P10.3 | A21<br>B21<br>C21<br>D21                      | 1      | A1           | V <sub>DDP</sub> | Hardware Configuration Inputs / Port 10<br>These inputs are boot mode (hardware<br>configuration) control inputs. They are<br>latched with the rising edge of HDRST.<br>Port 10 input line 0 / HWCFG0<br>Port 10 input line 1 / HWCFG1<br>Port 10 input line 2 / HWCFG2<br>Port 10 input line 3 / HWCFG3<br>After reset (HDRST = 1) the state of the<br>Port 10 input pins may be modified from the<br>reset configuration state. There actual state<br>can be read via software (P10_IN register).<br>During normal operation input HWCFG1<br>serves as emergency shut-off control input<br>for certain I/O lines (e.g. GPTA related<br>outputs). |  |  |  |  |  |  |

| Dedicate                         | d Periph                                      | neral  | I/Os         |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| SLSO0                            | AE14                                          | 0      | A2           | $V_{DDP}$        | SSC0 Slave Select Output Line 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| SLSO1                            | AC15                                          | 0      | -            |                  | SSC0 Slave Select Output Line 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| MTSR0                            | AF15                                          | 0<br>I |              |                  | SSC0 Master Transmit Output /<br>SSC0 Slave Receive Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| MRST0                            | AE15                                          | l<br>O |              |                  | SSC0 Master Receive Input /<br>SSC0 Slave Transmit Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| SCLK0                            | AF14                                          | I/O    | 1            |                  | SSC0 Clock Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| SLSI0                            | AD15                                          | I      | 1            |                  | SSC0 Slave Select Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

## **General Device Information**

| Table 2  | le 2 Pin Definitions and Functions (cont'd) |     |              |                  |                                                                                               |  |  |  |  |

|----------|---------------------------------------------|-----|--------------|------------------|-----------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol   | Pins                                        | I/O | Pad<br>Class | Power<br>Supply  | Functions                                                                                     |  |  |  |  |

|          |                                             |     | D            | _                | ADC Analog Input Port (cont'd)                                                                |  |  |  |  |

| AN32     | AC3                                         | 1   |              |                  | Analog input 32                                                                               |  |  |  |  |

| AN33     | AE2                                         | 1   |              |                  | Analog input 33                                                                               |  |  |  |  |

| AN34     | AD3                                         | 1   |              |                  | Analog input 34                                                                               |  |  |  |  |

| AN35     | AD5                                         | 1   |              |                  | Analog input 35                                                                               |  |  |  |  |

| AN36     | AE3                                         | 1   |              |                  | Analog input 36                                                                               |  |  |  |  |

| AN37     | AF2                                         | 1   |              |                  | Analog input 37                                                                               |  |  |  |  |

| AN38     | AC4                                         | 1   |              |                  | Analog input 38                                                                               |  |  |  |  |

| AN39     | AF3                                         | 1   |              |                  | Analog input 39                                                                               |  |  |  |  |

| AN40     | AD4                                         | 1   |              |                  | Analog input 40                                                                               |  |  |  |  |

| AN41     | AE4                                         | 1   |              |                  | Analog input 41                                                                               |  |  |  |  |

| AN42     | AC5                                         | 1   |              |                  | Analog input 42                                                                               |  |  |  |  |

| AN43     | AF4                                         | I   |              |                  | Analog input 43                                                                               |  |  |  |  |

| TR[15:0] |                                             | 0   | A3           | V <sub>DDP</sub> | OCDS Level 2 Debug Trace Lines <sup>2)</sup>                                                  |  |  |  |  |

|          |                                             |     |              |                  | (located on center balls)                                                                     |  |  |  |  |

| TR0      | U12                                         | 0   |              |                  | Trace output line 0                                                                           |  |  |  |  |

| TR1      | T12                                         | 0   |              |                  | Trace output line 1                                                                           |  |  |  |  |

| TR2      | U11                                         | 0   |              |                  | Trace output line 2                                                                           |  |  |  |  |

| TR3      | T11                                         | 0   |              |                  | Trace output line 3                                                                           |  |  |  |  |

| TR4      | U10                                         | 0   |              |                  | Trace output line 4                                                                           |  |  |  |  |

| TR5      | R12                                         | 0   |              |                  | Trace output line 5                                                                           |  |  |  |  |

| TR6      | R10                                         | 0   |              |                  | Trace output line 4                                                                           |  |  |  |  |

| TR7      | R11                                         | 0   |              |                  | Trace output line 7                                                                           |  |  |  |  |

| TR8      | M11                                         | 0   |              |                  | Trace output line 8                                                                           |  |  |  |  |

| TR9      | M10                                         | 0   |              |                  | Trace output line 9                                                                           |  |  |  |  |

| TR10     | L11                                         | 0   |              |                  | Trace output line 10                                                                          |  |  |  |  |

| TR11     | L10                                         | 0   |              |                  | Trace output line 11                                                                          |  |  |  |  |

| TR12     | K10                                         | 0   |              |                  | Trace output line 12                                                                          |  |  |  |  |

| TR13     | K11                                         | 0   |              |                  | Trace output line 13                                                                          |  |  |  |  |

| TR14     | L12                                         | 0   |              |                  | Trace output line 14                                                                          |  |  |  |  |

| TR15     | K12                                         | 0   |              |                  | Trace output line 15                                                                          |  |  |  |  |

| TRCLK    | T10                                         | 0   | A4           |                  | Trace Clock for OCDS Level 2 Debug<br>Trace Lines <sup>1)</sup><br>(located on a center ball) |  |  |  |  |

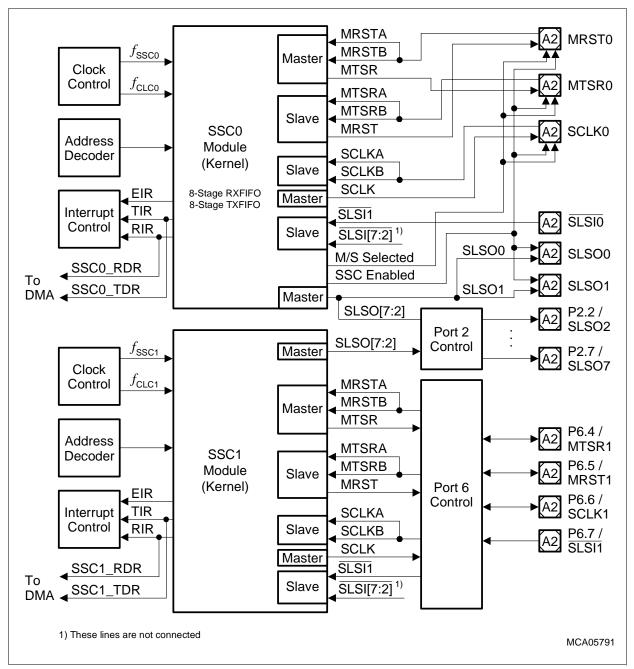

## 3.10 High-Speed Synchronous Serial Interfaces (SSC0, SSC1)

**Figure 9** shows a global view of the functional blocks and interfaces of the two High-Speed Synchronous Serial interfaces SSC0 and SSC1.

### Figure 9 Block Diagram of the SSC Interfaces

The SSC allows full-duplex and half-duplex serial synchronous communication up to 37.5 Mbit/s (@ 75 MHz module clock) with Receive and Transmit FIFO support. (FIFO only in SSC0). The serial clock signal can be generated by the SSC itself (Master Mode)

The downstream and upstream channels of the MSC module communicate with the external world via nine I/O lines. Eight output lines are required for the serial communication of the downstream channel (clock, data, and enable signals). One out of eight input lines SDI[7:0] is used as serial data input signal for the upstream channel. The source of the serial data to be transmitted by the downstream channel can be MSC register contents or data that is provided at the ALTINL/ALTINH input lines. These input lines are typically connected to other on-chip peripheral units (for example with a timer unit like the GPTA). An emergency stop input signal allows to set bits of the serial data stream to dedicated values in emergency case.

Clock control, address decoding, and interrupt service request control are managed outside the MSC module kernel. Service request outputs are able to trigger an interrupt or a DMA request.

### Features

- Fast synchronous serial interface to connect power switches in particular, or other peripheral devices via serial buses

- High-speed synchronous serial transmission on downstream channel

- Maximum serial output clock frequency:  $f_{FCL} = f_{MSC}/2$ (= 37.5 Mbit/s @ 75 MHz module clock)

- Fractional clock divider for precise frequency control of serial clock  $f_{\rm MSC}$

- Command, data, and passive frame types

- Start of serial frame: Software-controlled, timer-controlled, or free-running

- Programmable upstream data frame length (16 or 12 bits)

- Transmission with or without SEL bit

- Flexible chip select generation indicates status during serial frame transmission

- Emergency stop without CPU intervention

- Low-speed asynchronous serial reception on upstream channel

- Baud rate:  $f_{MSC}$  divided by 8, 16, 32, 64, 128, 256, or 512

- Standard asynchronous serial frames

- Parity error checker

- 8-to-1 input multiplexer for SDI lines

- Built-in spike filter on SDI lines

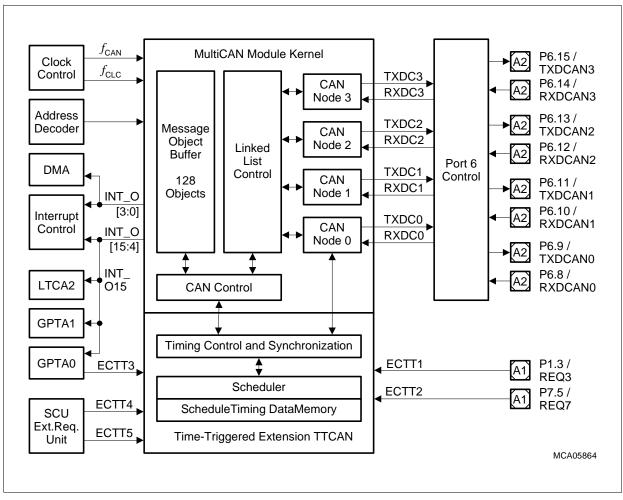

## 3.12 MultiCAN Controller (CAN)

**Figure 11** shows a global view of the MultiCAN module with its functional blocks and interfaces.

### Figure 11 Block Diagram of MultiCAN Module with Time-Triggered Extension

The MultiCAN module contains four independently operating CAN nodes with Full-CAN functionality that are able to exchange Data and Remote Frames via a gateway function. Transmission and reception of CAN frames is handled in accordance with CAN specification V2.0 B (active). Each CAN node can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers.

All four CAN nodes share a common set of message objects. Each message object can be individually allocated to one of the CAN nodes. Besides serving as a storage container for incoming and outgoing frames, message objects can be combined to build gateways between the CAN nodes or to setup a FIFO buffer.

The message objects are organized in double-chained linked lists, where each CAN node has it's own list of message objects. A CAN node stores frames only into message

The A/D converters operate by the method of the successive approximation. A multiplexer selects between up to 32 analog inputs that can be connected with the 16 conversion channels in each ADC module. An automatic self-calibration adjusts the ADC modules to changing temperatures or process variations.

External Clock control, address decoding, and service request (interrupt) control is managed outside the ADC module kernel. A synchronization bridge is used for synchronization of two ADC modules. External trigger conditions are controlled by an External Request Unit. This unit generates the control signals for auto-scan control (ASGT), software trigger control (SW0TR, SW0GT), the event trigger control (ETR, EGT), queue control (QTR, QGT), and timer trigger control (TTR, TGT).

### Features

- 8-bit, 10-bit, 12-bit A/D conversion

- Minimum conversion times (without sample time, @ 75 MHz module clock):

- 1.05 µs @ 8-bit resolution

- 1.25 μs @ 10-bit resolution

- 1.45 µs @ 12-bit resolution

- Extended channel status information on request source

- Successive approximation conversion method

- Total Unadjusted Error (TUE) of ±2 LSB @ 10-bit resolution

- Integrated sample & hold functionality

- Direct control of up to 16(32) analog input channels per ADC

- Dedicated control and status registers for each analog channel

- Powerful conversion request sources

- Selectable reference voltages for each channel

- Programmable sample and conversion timing schemes

- Limit checking

- Flexible ADC module service request control unit

- Synchronization of the two on-chip A/D converters

- Automatic control of external analog multiplexers

- · Equidistant samples initiated by timer

- External trigger and gating inputs for conversion requests

- Power reduction and clock control feature

- On-chip die temperature sensor output voltage measurement via ADC1

## 3.18 Watchdog Timer

The Watchdog Timer (WDT) provides a highly reliable and secure way to detect and recover from software or hardware failure. The WDT helps to abort an accidental malfunction of the TC1796 in a user-specified time period. When enabled, the WDT will cause the TC1796 system to be reset if the WDT is not serviced within a user-programmable time period. The CPU must service the WDT within this time interval to prevent the WDT from causing a TC1796 system reset. Hence, routine service of the WDT confirms that the system is functioning properly.

In addition to this standard "Watchdog" function, the WDT incorporates the EndInit feature and monitors its modifications. A system-wide line is connected to the End-of-Initialization (Endinit) feature and monitors its modifications. A system-wide line is connected to the WDT\_CON0.ENDINIT bit, serving as an additional write-protection for critical registers (besides Supervisor Mode protection)

A further enhancement in the TC1796's WDT is its reset pre-warning operation. Instead of immediately resetting the device on the detection of an error (the way that standard Watchdogs do), the WDT first issues an Non-Maskable Interrupt (NMI) to the CPU before finally resetting the device at a specified time period later. This gives the CPU a chance to save system state to memory for later examination of the cause of the malfunction, an important aid in debugging.

### Features

- 16-bit Watchdog counter

- Selectable input frequency:  $f_{SYS}/256 \text{ or } f_{SYS}/16384$

- 16-bit user-definable reload value for normal Watchdog operation, fixed reload value for Time-Out and Pre-warning Modes

- Incorporation of the ENDINIT bit and monitoring of its modifications

- Sophisticated password access mechanism with fixed and user-definable password fields

- Proper access always requires two write accesses. The time between the two accesses is monitored by the WDT and limited.

- Access Error Detection: Invalid password (during first access) or invalid guard bits (during second access) trigger the Watchdog reset generation.

- Overflow Error Detection: An overflow of the counter triggers the Watchdog reset generation.

- Watchdog function can be disabled; access protection and ENDINIT monitor function remain enabled.

- Double Reset Detection: If a Watchdog induced reset occurs twice, a severe system malfunction is assumed and the TC1796 is held in reset until a power-on reset. This prevents the device from being periodically reset if, for instance, connection to the external memory has been lost such that even system initialization could not be performed

#### 3.21 **Power Management System**

The TC1796 power management system allows software to configure the various processing units so that they automatically adjust to draw the minimum necessary power for the application. There are three power management modes:

- Run Mode

- Idle Mode

- Sleep Mode

The operation of each system component in each of these states can be configured by software. The power-management modes provide flexible reduction of power consumption through a combination of techniques, including stopping the CPU clock, stopping the clocks of other system components individually, and individually clockspeed reduction of some peripheral components.

Besides these explicit software-controlled power-saving modes, in the TC1796 special attention has been paid for automatic power-saving in those operating units which are currently not required or idle. In that case they are shut off automatically until their operation is required again.

| Table 8 | Power Management Mode Summary                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Run     | The system is fully operational. All clocks and peripherals are enabled, as determined by software.                                                                                                                                                                                                                                                                                                                                          |

| Idle    | The CPU clock is disabled, waiting for a condition to return it to Run<br>Mode. Idle Mode can be entered by software when the processor has no<br>active tasks to perform. All peripherals remain powered and clocked.<br>Processor memory is accessible to peripherals. A reset, Watchdog Timer<br>event, a falling edge on the NMI pin, or any enabled interrupt event will<br>return the system to Run Mode.                              |

| Sleep   | The system clock signal is distributed only to those peripherals<br>programmed to operate in Sleep Mode. The other peripheral module will<br>be shut down by the suspend signal. Interrupts from operating<br>peripherals, the Watchdog Timer, a falling edge on the NMI pin, or a reset<br>event will return the system to Run Mode. Entering this state requires an<br>orderly shut-down controlled by the Power Management State Machine. |

In typical operation, Idle Mode and Sleep Mode may be entered and exited frequently during the run time of an application. For example, system software will typically cause the CPU to enter Idle Mode each time it has to wait for an interrupt before continuing its tasks. In Sleep Mode and Idle Mode, wake-up is performed automatically when any enabled interrupt signal is detected, or if the Watchdog Timer signals the CPU with an NMI trap.

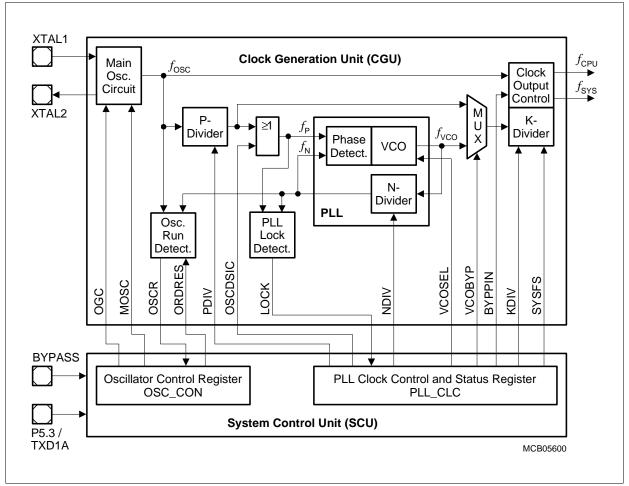

are derived from  $f_{\rm VCO}$  only by the K-Divider. In this mode, the system clock  $f_{\rm SYS}$  can be equal to  $f_{\rm CPU}$  or  $f_{\rm CPU}/2$ .

Figure 19 Clock Generation Unit

### **Recommended Oscillator Circuits**

The oscillator circuit, a Pierce oscillator, is designed to work with both, an external crystal oscillator or an external stable clock source. It basically consists of an inverting amplifier and a feedback element with XTAL1 as input, and XTAL2 as output.

When using a crystal, a proper external oscillator circuitry must be connected to both pins, XTAL1 and XTAL2. The crystal frequency can be within the range of 4 MHz to 25 MHz. Additionally are necessary, two load capacitances  $C_{\rm X1}$  and  $C_{\rm X2}$ , and depending on the crystal type a series resistor  $R_{\rm X2}$  to limit the current. A test resistor  $R_{\rm Q}$  may be temporarily inserted to measure the oscillation allowance (negative resistance) of the oscillator circuitry.  $R_{\rm Q}$  values are typically specified by the crystal vendor. The  $C_{\rm X1}$  and  $C_{\rm X2}$  values shown in Figure 20 can be used as starting points for the negative resistance evaluation and for non-productive systems. The exact values and related operating range are dependent on the crystal frequency and have to be determined and

# **Functional Description**

| Table 9TC1796 Identification Registers (cont'd) |                        |                        |          |  |  |  |  |  |  |  |

|-------------------------------------------------|------------------------|------------------------|----------|--|--|--|--|--|--|--|

| Short Name                                      | Address                | Value                  | Stepping |  |  |  |  |  |  |  |

| ADC0_ID                                         | F010 0408 <sub>H</sub> | 0030 C002 <sub>H</sub> | -        |  |  |  |  |  |  |  |

| MLI0_ID                                         | F010 C008 <sub>H</sub> | 0025 C005 <sub>H</sub> | -        |  |  |  |  |  |  |  |

| MLI1_ID                                         | F010 C108 <sub>H</sub> | 0025 C005 <sub>H</sub> | -        |  |  |  |  |  |  |  |

| MCHK_ID                                         | F010 C208 <sub>H</sub> | 001B C001 <sub>H</sub> | -        |  |  |  |  |  |  |  |

| CPS_ID                                          | F7E0 FF08 <sub>H</sub> | 0015 C006 <sub>H</sub> | -        |  |  |  |  |  |  |  |

| CPU_ID                                          | F7E1 FE18 <sub>H</sub> | 000A C005 <sub>H</sub> | -        |  |  |  |  |  |  |  |

| EBU_ID                                          | F800 0008 <sub>H</sub> | 0014 C005 <sub>H</sub> | -        |  |  |  |  |  |  |  |

| PMU_ID                                          | F800 0508 <sub>H</sub> | 002E C002 <sub>H</sub> | -        |  |  |  |  |  |  |  |

| FLASH_ID                                        | F800 2008 <sub>H</sub> | 0031 C002 <sub>H</sub> | -        |  |  |  |  |  |  |  |

| DMU_ID                                          | F801 0108 <sub>H</sub> | 002D C002 <sub>H</sub> | -        |  |  |  |  |  |  |  |

| DBCU_ID                                         | F87F FA08 <sub>H</sub> | 000F C005 <sub>H</sub> | -        |  |  |  |  |  |  |  |

| DMI_ID                                          | F87F FC08 <sub>H</sub> | 0008 C004 <sub>H</sub> | -        |  |  |  |  |  |  |  |

| PMI_ID                                          | F87F FD08 <sub>H</sub> | 000B C004 <sub>H</sub> | -        |  |  |  |  |  |  |  |

| LFI_ID                                          | F87F FF08 <sub>H</sub> | 000C C005 <sub>H</sub> | -        |  |  |  |  |  |  |  |

| PBCU_ID                                         | F87F FE08 <sub>H</sub> | 000F C005 <sub>H</sub> | -        |  |  |  |  |  |  |  |

# 4 Electrical Parameters

## 4.1 General Parameters

### 4.1.1 Parameter Interpretation

The parameters listed in this section partly represent the characteristics of the TC1796 and partly its requirements on the system. To aid interpreting the parameters easily when evaluating them for a design, they are marked with an two-letter abbreviation in column "Symbol":

• cc

Such parameters indicate **C**ontroller **C**haracteristics which are a distinctive feature of the TC1796 and must be regarded for a system design.

• SR

Such parameters indicate **S**ystem **R**equirements which must provided by the microcontroller system in which the TC1796 designed in.

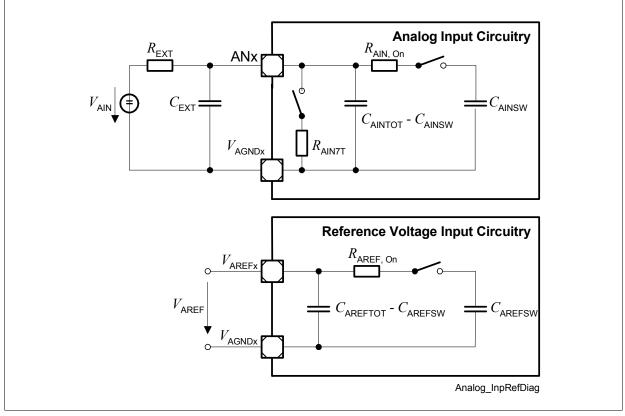

Figure 23 ADC0/ADC1 Input Circuits

## 4.2.6 Power Supply Current

### Table 21 Power Supply Currents (Operating Conditions apply)

| Parameter                                                                              | Symbol                           |         |    | Value | S                                                  | Unit | Note /                                                              |  |

|----------------------------------------------------------------------------------------|----------------------------------|---------|----|-------|----------------------------------------------------|------|---------------------------------------------------------------------|--|

|                                                                                        |                                  |         |    | Тур.  | Max.                                               |      | Test Condition                                                      |  |

| <b>PORST</b> low current at $V_{\rm DD}$                                               | I <sub>DD_PORST</sub>            | СС      | _  | -     | 300                                                | mA   | The PLL running at the base frequency                               |  |

| PORST low current at $V_{\text{DDP}}$ , and PORST highcurrent without any portactivity | I <sub>DDP_PORS</sub>            | т<br>СС | _  | -     | 25                                                 | mA   | The PLL running at the base frequency                               |  |

| Active mode core supply current <sup>1)2)</sup>                                        | $I_{\rm DD}$                     | сс      | 10 | -     | 700                                                | mA   | f <sub>CPU</sub> =150MHzf <sub>CPU</sub> /f<br><sub>SYS</sub> = 2:1 |  |

| Active mode analog<br>supply current                                                   | $I_{\rm DDAx;} \\ I_{\rm DDMx}$  | сс      | _  | -     | -                                                  | mA   | See ADC0/1<br>FADC                                                  |  |

| Stand-by RAM supply<br>current in stand-by                                             | $I_{\rm SBSB}$                   | сс      | _  | -     | 9                                                  | mA   | $V_{\text{DDSB}}$ = 1V,<br>$T_{\text{j}}$ = 150°C                   |  |

| Oscillator and PLL core power supply                                                   | I <sub>DDOSC</sub> <sup>3)</sup> | сс      | _  | -     | 5                                                  | mA   | _                                                                   |  |

| Oscillator and PLL pads power supply                                                   | I <sub>DDOSC3</sub>              | сс      | -  | _     | 3.6                                                | mA   | _                                                                   |  |

| LVDS port supply (via $V_{\text{DDP}}$ ) <sup>4)</sup>                                 | I <sub>LVDS</sub>                | сс      | -  | _     | 50                                                 | mA   | LVDS pads active                                                    |  |

| Flash power supply current                                                             | I <sub>DDFL3</sub>               | сс      | -  | _     | 80                                                 | mA   | _                                                                   |  |

| Maximum Allowed<br>Power Dissipation <sup>5)</sup>                                     | P <sub>D</sub>                   | SR      | _  | _     | $P_{\rm D} \times R_{\rm TJA} < 25^{\circ}{\rm C}$ | -    | worst case<br>$T_A = 125^{\circ}C$                                  |  |

1) Infineon Power Loop: CPU and PCP running, all peripherals active. The power consumption of each custom application will most probably be lower than this value, but must be evaluated separately.

2) The  $I_{DD}$  decreases for typically 120 mA if the  $f_{CPU}$  is decreased for 50 MHz, at constant  $T_{J}$  = 150C, for the Infineon Max Power Loop.

The dependency in this range is, at constant junction temperature, linear.

- 3)  $V_{\text{DDOSC}}$  and  $V_{\text{SSOSC}}$  are not bonded externally in the BC and BD steps of TC1796. An option for bonding them in future steps and products is kept open.

- 4) In case the LVDS pads are disabled, the power consumption pro pair is negligible (less than  $1\mu A$ ).

- 5) For the calculation of junction to ambient thermal resistance  $R_{TJA}$ , see Page 130.

## 4.3.4 Power, Pad and Reset Timing

### Table 23Power, Pad and Reset Timing Parameters

| Parameter                                                                           | Symbol                |                       | V                                       | alues | Unit                                | Note /        |                 |  |

|-------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------------------------|-------|-------------------------------------|---------------|-----------------|--|

|                                                                                     | V <sub>DDPPA</sub> CC |                       | Min.                                    | Тур.  | Max.                                |               | Test Con dition |  |

| Min. $V_{\text{DDP}}$ voltage to ensure defined pad states <sup>1)</sup>            |                       |                       | 0.6                                     | -     | -                                   | V             | _               |  |

| Oscillator start-up time <sup>2)</sup>                                              | t <sub>oscs</sub>     | CC                    | _                                       | _     | 10                                  | ms            | _               |  |

| Minimum PORST active time<br>after power supplies are stable<br>at operating levels | t <sub>POA</sub>      | SR                    | 10                                      | _     | -                                   | ms            | _               |  |

| HDRST pulse width                                                                   | t <sub>HD</sub>       | CC                    | 1024<br>clock<br>cycles <sup>3)6)</sup> | _     | -                                   | $f_{\rm SYS}$ | _               |  |

| PORST rise time                                                                     | t <sub>POR</sub>      | SR                    | -                                       | _     | 50                                  | ms            | -               |  |

| Setup time to PORST rising edge <sup>4)</sup>                                       | t <sub>POS</sub>      | SR                    | 0                                       | -     | -                                   | ns            | -               |  |

| Hold time from PORST rising edge <sup>4)</sup>                                      | t <sub>POH</sub>      | SR                    | 100                                     | -     | -                                   | ns            | _               |  |

| Setup time to HDRST rising edge <sup>5)</sup>                                       | t <sub>HDS</sub>      | SR                    | 0                                       | -     | -                                   | ns            | -               |  |

| Hold time from HDRST rising edge <sup>5)</sup>                                      | t <sub>HDH</sub>      | SR                    | $100 + (2 \times 1/f_{SYS})^{6)}$       | _     | -                                   | ns            | -               |  |

| Ports inactive after PORST reset active <sup>7)8)</sup>                             | t <sub>PIP</sub>      | CC                    | -                                       | -     | 150                                 | ns            | -               |  |

| Ports inactive after HDRST reset active                                             | t <sub>PI</sub>       | CC                    | -                                       | _     | 150 +<br>5 × 1/<br>f <sub>SYS</sub> | ns            | -               |  |

| Minimum $V_{\text{DDP}}$ <b>PORST</b> activation threshold <sup>9)</sup>            | V <sub>PORST</sub>    | <sup>73.3</sup><br>SR | -                                       | -     | 2.9                                 | V             | _               |  |

| Minimum $V_{\text{DD}}$ <b>PORST</b> activation threshold <sup>9)</sup>             | V <sub>PORST</sub>    | <sup>1.5</sup><br>SR  | -                                       | -     | 1.32                                | V             | -               |  |

| Power on Reset Boot Time <sup>9)</sup>                                              | t <sub>BP</sub>       | CC                    | -                                       | _     | 2                                   | ms            | -               |  |

| Hardware/Software Reset<br>Boot Time at $f_{CPU}$ =150MHz <sup>10)</sup>            | t <sub>B</sub>        | CC                    | 150                                     | _     | 350                                 | μS            | _               |  |

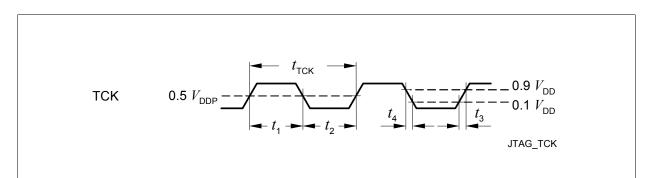

## 4.3.8 JTAG Interface Timing

Operating Conditions apply, CL = 50 pF

### Table 27 TCK Clock Timing Parameter

| Parameter                      | Symb                  | ol |    | Values | Unit | Note /<br>Test Con<br>dition |      |

|--------------------------------|-----------------------|----|----|--------|------|------------------------------|------|

|                                |                       |    |    | Тур.   |      |                              | Max. |

| TCK clock period <sup>1)</sup> | t <sub>TCK</sub>      | SR | 25 | —      | -    | ns                           | -    |

| TCK high time                  | <i>t</i> <sub>1</sub> | SR | 10 | _      | _    | ns                           | -    |

| TCK low time                   | <i>t</i> <sub>2</sub> | SR | 10 | _      | _    | ns                           | -    |

| TCK clock rise time            | t <sub>3</sub>        | SR | _  | _      | 4    | ns                           | _    |

| TCK clock fall time            | <i>t</i> <sub>4</sub> | SR | -  | _      | 4    | ns                           | -    |

1)  $f_{\text{TCK}}$  should be lower or equal to  $\overline{f_{\text{SYS}}}$ .

Figure 36 TCK Clock Timing

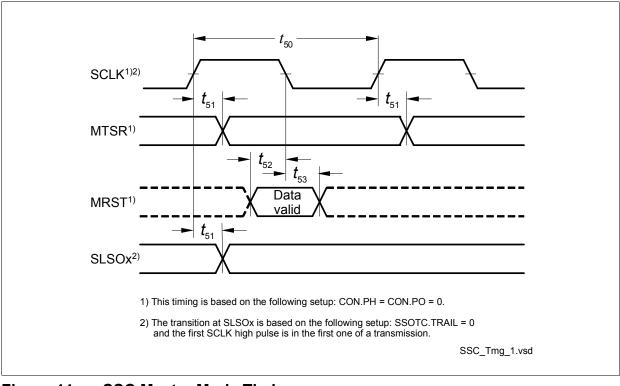

## 4.3.12.3 Synchronous Serial Channel (SSC) Master Mode Timing

| Parameter                              | Symbol                 |    | Values                      |      |      | Unit | Note /             |

|----------------------------------------|------------------------|----|-----------------------------|------|------|------|--------------------|

|                                        |                        |    | Min.                        | Тур. | Max. |      | Test Con<br>dition |

| SCLK clock period <sup>1)2)</sup>      | <i>t</i> <sub>50</sub> | CC | $2 \times T_{\rm SSC}^{3)}$ | _    | _    | ns   | -                  |

| MTSR/SLSOx delay from SCLK rising edge | t <sub>51</sub>        | CC | 0                           | -    | 8    | ns   | -                  |

| MRST setup to SCLK falling edge        | t <sub>52</sub>        | SR | 10                          | -    | -    | ns   | -                  |

| MRST hold from SCLK falling edge       | t <sub>53</sub>        | SR | 5                           | -    | -    | ns   | -                  |

1) SCLK signal rise/fall times are the same as the A2 Pads rise/fall times.

2) SCLK signal high and low times can be minimum 1  $\times$   $T_{\rm SSC}.$

3)  $T_{\text{SSCmin}} = T_{\text{SYS}} = 1/f_{\text{SYS}}$ . When  $f_{\text{SYS}} = 75$  MHz,  $t_{50} = 26,67$  ns

Figure 44 SSC Master Mode Timing

### Package and Reliability

### 5.3 Flash Memory Parameters

The data retention time of the TC1796's Flash memory (i.e. the time after which stored data can still be retrieved) depends on the number of times the Flash memory has been erased and programmed.

| Parameter                                                                  | Symbol               |                                        | Values |      | Unit  | Note /<br>Test Condition             |  |

|----------------------------------------------------------------------------|----------------------|----------------------------------------|--------|------|-------|--------------------------------------|--|

|                                                                            |                      | Min.                                   | Тур.   | Max. |       |                                      |  |

| Program / Data Flash<br>Retention Time,<br>Physical Sector <sup>1)2)</sup> | t <sub>RET</sub> CC  | 20                                     | -      | -    | years | Max. 1000<br>erase/program<br>cycles |  |

| Program / Data Flash<br>Retention Time<br>Logical Sector <sup>1)2)</sup>   | t <sub>RETL</sub> CC | 20                                     | _      | -    | years | Max. 100<br>erase/program<br>cycles  |  |

| Data Flash<br>Endurance<br>(128 KB)                                        | N <sub>E</sub> CC    | 15 000                                 | -      | -    | -     | Max. data retention<br>time 5 years  |  |

| Data Flash<br>Endurance,<br>EEPROM Emulation<br>$(8 \times 16 \text{ KB})$ | N <sub>E8</sub> CC   | 120 000                                | _      | -    | -     | Max. data retention<br>time 5 years  |  |

| Programming Time per Page <sup>3)</sup>                                    | t <sub>PR</sub> CC   | -                                      | -      | 5    | ms    | -                                    |  |

| Program Flash<br>Erase Time<br>per 256-KB Sector                           | t <sub>ERP</sub> CC  | -                                      | -      | 5    | S     | <i>f</i> <sub>СРU</sub> = 150 MHz    |  |

| Data Flash<br>Erase Time<br>per 64-KB Sector                               | t <sub>ERD</sub> CC  | -                                      | -      | 2.5  | S     | <i>f</i> <sub>СРU</sub> = 150 MHz    |  |

| Wake-up time                                                               | t <sub>WU</sub> CC   | 4300 ×<br>1/f <sub>CPU</sub><br>+ 40μs | -      | -    | -     | -                                    |  |

### Table 36Flash Parameters

1) Storage and inactive time included.

2) At average weighted junction temperature  $T_j = 100^{\circ}$ C, or the retention time at average weighted temperature of  $T_j = 110^{\circ}$ C is minimum 10 years, or the retention time at average weighted temperature of  $T_j = 150^{\circ}$ C is minimum 0.7 years.

3) In case the Program Verify feature detects weak bits, these bits will be programmed once more. The reprogramming takes additional 5 ms.