# E·XFL

### Zilog - Z86E6316FSC00TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                   |

|----------------------------|------------------------------------------------------------|

| Core Processor             | Z8                                                         |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 16MHz                                                      |

| Connectivity               | UART/USART                                                 |

| Peripherals                |                                                            |

| Number of I/O              | 32                                                         |

| Program Memory Size        | 32KB (32K x 8)                                             |

| Program Memory Type        | OTP                                                        |

| EEPROM Size                | -                                                          |

| RAM Size                   | 236 x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                |

| Data Converters            | -                                                          |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                            |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 44-LQFP                                                    |

| Supplier Device Package    | 44-LQFP (10x10)                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z86e6316fsc00tr |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Overview**

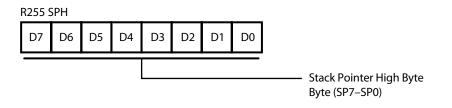

The Z86E61/Z86E63 microcontrollers are members of the Z8® single-chip microcontroller family with 16K/32KB of EPROM and 236 bytes of general-purpose RAM. Offered in 40-pin DIP, 44-pin PLCC or 44-pin LQFP package styles, these devices are pin-compatible EPROM versions of the Z86C61/63. The ROMless pin option is available on the 44-pin versions only.

With 16KB/32KB of ROM and 236 bytes of general-purpose RAM, the Z86E61/Z86E63 MCU offers fast execution, efficient use of memory, sophisticated interrupts, input/output bit manipulation capabilities, and easy hardware/software system expansion.

For applications demanding powerful I/O capabilities, the Z86E61/Z86E63 MCU offers 32 pins dedicated to input and output. These lines are grouped into four ports. Each port consists of eight lines, and is configurable under software control to provide timing, status signals, serial or parallel I/O with or without handshake, and an address/data bus for interfacing external memory.

The Z86E61/Z86E63 MCU can address both external memory and preprogrammed ROM, making it well suited for high-volume applications or where code flexibility is required. There are three basic address spaces available to support this configuration:

- Program memory

- Data memory

- 236 General-purpose registers

### **Features**

The Z86E61 and Z86E63 MCUs offer the following features:

- 8-Bit CMOS microcontroller

- 40-pin DIP, 44-pin PLCC and 44-pin LQFP packages

- 4.5V to 5.5V operating range

- Clock speeds: 16MHz and 20MHz

- Low power consumption: 275 mW (max)

- Two Standby modes: STOP and HALT

- 32 Input/Output lines

- Full-duplex UART

- All digital inputs are TTL levels

Figure 1. Z86E61/Z86E63 MCU Functional Block Diagram

Power connections follow the conventional descriptions listed in Table 24.

| Table 24. Powe | <b>Connection</b> | Conventions |

|----------------|-------------------|-------------|

|----------------|-------------------|-------------|

| Connection | Circuit         | Device          |

|------------|-----------------|-----------------|

| Power      | V <sub>CC</sub> | V <sub>DD</sub> |

| Ground     | GND             | V <sub>SS</sub> |

# **Pin Functions**

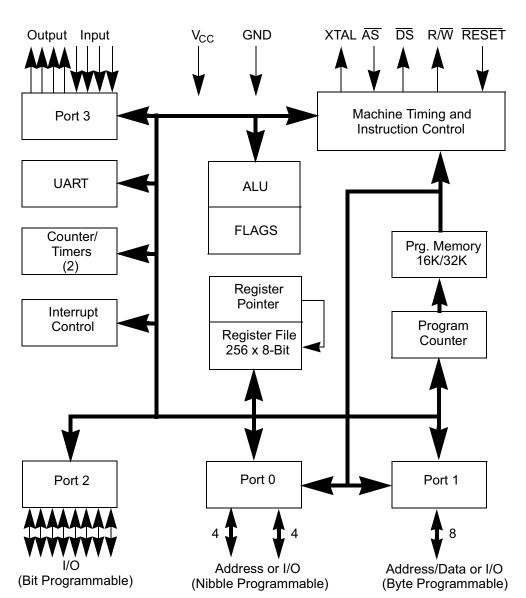

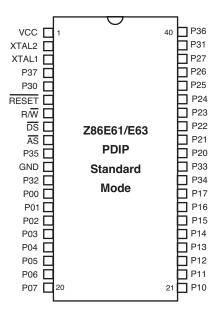

The Z86E61/Z86E63 MCU is available in variety of package styles, programming modes and pin configurations. This section describes the pin signals and configurations for each of the 40-pin PDIP, 44-pin PLCC and 44-pin LQFP packages in both Standard and EPROM Programming modes.

### **Pin Signals**

Figure 2 shows the pin-outs for the 40-pin PDIP Standard Mode package; Table 25 describes each pin.

Figure 2. Z86E61/Z86E63 PDIP Pin Diagram, Standard Mode

| Table 25. Z86E61/Z86E63 | PDIP Pin | Description. | Standard Mode |

|-------------------------|----------|--------------|---------------|

|                         |          |              |               |

| Pin Signal | Description              | I/O    |

|------------|--------------------------|--------|

| XTAL2      | Crystal Oscillator Clock | Output |

| XTAL1      | Crystal Oscillator Clock | Input  |

| RESET      | Reset                    | Input  |

| R/W        | Read/Write               | Output |

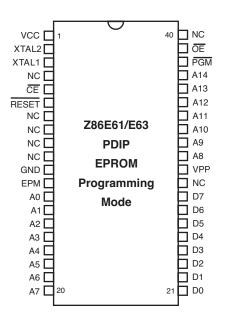

Figure 3 shows the pin-outs for the 40-pin PDIP EPROM Programming Mode package; Table 26 describes each pin.

Figure 3. Z86E61/Z86E63 PDIP Pin Diagram, EPROM Programming Mode

| Table 26. Z86E61/Z86E63 PDIP Pin | Description    | ogramming Mode |

|----------------------------------|----------------|----------------|

| Table 20. 200E01/200E03 FDIF FIL | i Description, |                |

| Pin Signal      | Description              | I/O          |

|-----------------|--------------------------|--------------|

| XTAL2           | Crystal Oscillator Clock | Output       |

| XTAL1           | Crystal Oscillator Clock | Input        |

| CE              | Chip Enable              | Input        |

| RESET           | Reset                    | Input        |

| EPM             | EPROM Programming Mode   | Input        |

| A0–A14          | 15-bit Address Bus       | Input        |

| D7-D0           | 8-bit Data Bus           | Input/Output |

| V <sub>PP</sub> | Programming Voltage      | Input        |

| PGM             | Programming Mode         | Input        |

| OE              | Output Enable            | Input        |

| NC              | Not Connected            | Input        |

| GND             | Ground                   | Input        |

| V <sub>CC</sub> | Power Supply             | Input        |

|                 |                          |              |

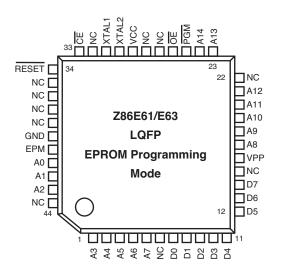

Figure 5 shows the pin-outs for the 44-pin LQFP EPROM Programming Mode package; Table 28 describes each pin.

#### Figure 5. Z86E61/Z86E63 LQFP Pin Diagram, EPROM Programming Mode

| Pin Signal      | Description              | I/O          |

|-----------------|--------------------------|--------------|

| XTAL2           | Crystal Oscillator Clock | Output       |

| XTAL1           | Crystal Oscillator Clock | Input        |

| CE              | Chip Enable              | Input        |

| RESET           | Reset                    | Input        |

| EPM             | EPROM Programming Mode   | Input        |

| A0–A14          | 15-bit Address Bus       | Input        |

| D7-D0           | 8-bit Data Bus           | Input/Output |

| V <sub>PP</sub> | Programming Voltage      | Input        |

| PGM             | Programming Mode         | Input        |

| OE              | Output Enable            | Input        |

| NC              | Not Connected            | Input        |

| GND             | Ground                   | Input        |

| V <sub>CC</sub> | Power Supply             | Input        |

Table 28. Z86E61/Z86E63 LQFP Pin Description, EPROM Programming Mode

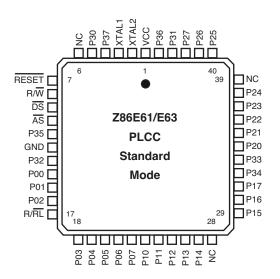

Figure 6 shows the pin-outs for the 44-pin PLCC Standard Mode package; Table 29 describes each pin.

#### Figure 6. Z86E61/Z86E63 PLCC Pin Diagram, Standard Mode

| Pin Signal      | Description              | I/O          |

|-----------------|--------------------------|--------------|

| XTAL2           | Crystal Oscillator Clock | Output       |

| XTAL1           | Crystal Oscillator Clock | Input        |

| RESET           | Reset                    | Input        |

| R/W             | Read/Write               | Output       |

| DS              | Data Strobe              | Output       |

| AS              | Address Strobe           | Output       |

| P00-P07 Port 0  | 8-bit General I/O        | Input/Output |

| P10-P17 Port 1  | 8-bit General I/O        | Input/Output |

| P20-P27 Port 2  | 8-bit General I/O        | Input/Output |

| P30-P33 Port 3  | 4-bit Input              | Input        |

| P34–P37 Port 3  | 4-bit Output             | Output       |

| R/RL            | ROM/ROMIess Control      | Input        |

| GND             | Ground                   | Input        |

| V <sub>CC</sub> | Power Supply             | Input        |

Table 29. Z86E61/Z86E63 PLCC Pin Description, Standard Mode

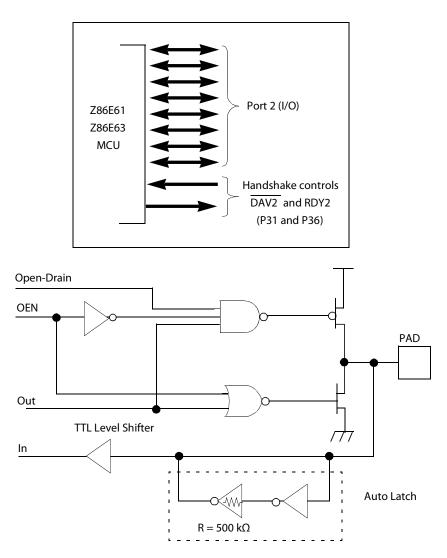

open-drain output. Port 2 is always available for I/ 0 operation. When used as an I/0 port, Port 2 can be placed under handshake control. In this configuration, Port 3 lines P31 and P36 are used as the handshake control lines DAV2 and RDY2. The handshake signal assignment for Port 3 lines, P31 and P36, is dictated by the direction (input or output) assigned to P27; see Figure 10 and Table 31 on page 16).

Figure 10. Port 2 Configuration

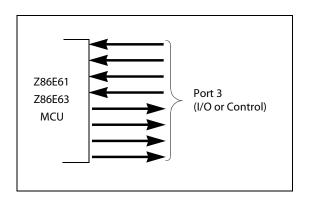

### Port 3 (P37–P30)

Port 3 is an 8-bit, CMOS compatible four-fixed input and four-fixed output port. These eight I/O lines have four-fixed (P33–P30) input and four-fixed (P37–P34) output ports. Port 3, when used as serial I/O, is programmed as serial in and serial out, respectively; see Figure 11.

Figure 11. Port 3 Configuration

Port 3 is configured under software control to provide the following control functions: handshake for Ports 0 and 2 (DAV and RDY); four external interrupt request signals (IRQ3–IRQ0); timer input and output signals ( $T_{IN}$  and  $T_{OUT}$ ) Data Memory Select ( $\overline{DM}$ ) and EPROM control signals (P30 =  $\overline{CE}$ , P31 =  $\overline{OE}$ , P32 = EPM and P33 =  $V_{PP}$ ).

Table 31 lists the pin assignments for Port 3.

| Table 3 | 31. Po | rt 3 Pin | Assignments* |

|---------|--------|----------|--------------|

|---------|--------|----------|--------------|

| Pin   | I/O          | СТСІ             | Interrupt      | P0 HS       | P1 HS    | P2 HS | UART       | Ext | EPROM           |

|-------|--------------|------------------|----------------|-------------|----------|-------|------------|-----|-----------------|

| P30   | In           | T <sub>IN</sub>  | IRQ3           |             |          |       | Serial In  |     | CE              |

| P31   | In           | T <sub>IN</sub>  | IRQ2           |             |          | D/R   |            |     | OE              |

| P32   | In           | T <sub>IN</sub>  | IRQ0           | D/R         |          |       |            |     | EPM             |

| P33   | In           | T <sub>IN</sub>  | IRQ1           |             | D/R      |       |            |     | V <sub>PP</sub> |

| P34   | Out          | T <sub>OUT</sub> |                |             | R/D      |       |            | DM  |                 |

| P35   | Out          | T <sub>OUT</sub> |                | R/D         |          |       |            |     |                 |

| P36   | Out          | T <sub>OUT</sub> |                |             |          | R/D   |            |     |                 |

| P37   | Out          | T <sub>OUT</sub> |                |             |          |       | Serial Out |     |                 |

| Т0    |              |                  | IRQ4           |             |          |       |            |     |                 |

| T1    |              |                  | IRQ5           |             |          |       |            |     |                 |

| Note: | *HS = Handsh | nake Signa       | ls; D = Data A | vailable; R | = Ready. |       |            |     |                 |

# **Address Space**

This section describes the memory and addressing functions of the Z86E61/Z86E63 MCU.

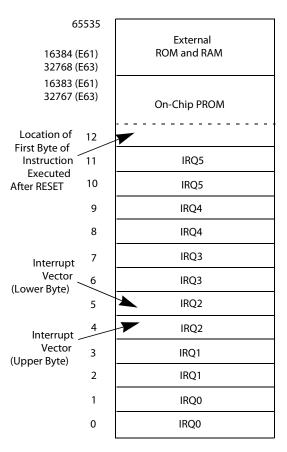

### **Program Memory**

The Z86E61/Z86E63 MCU can address 48KB (Z86E61) or 32KB (Z86E63) of external program memory; see Figure 13. The first 12 bytes of program memory are reserved for the interrupt vectors. These locations contain six 16-bit vectors that correspond to the six available interrupts. For EPROM Mode, byte 13 to byte 16383 (Z86E61) or 32767 (Z86E63) consists of on-chip EPROM. At addresses 16384 (Z86E61) or 32768 (Z86E63) and above, the Z86E61/Z86E63 MCU executes external program memory fetches. In ROMless Mode, the Z86E61/Z86E63 MCU can address up to 64KB of program memory. Program execution begins at external location 000C (HEX) after a reset.

Figure 13. Program Memory Configuration

## **Functional Description**

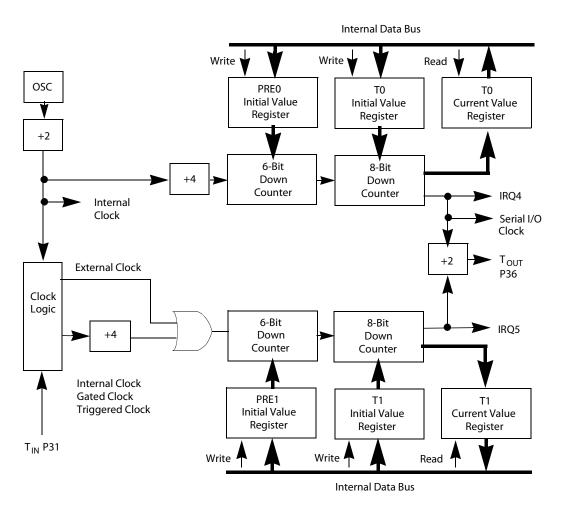

This section describes the counter/timer, interrupt, clock and timer mode functions of the Z86E61/Z86E63 MCU.

### **Counter/Timers**

There are two 8-bit programmable counter/timers (T0–T1), each driven by its own 6-bit programmable prescaler. The T1 prescaler is driven by internal or external clock sources; however, the T0 prescaler is driven by the internal clock only, as shown in Figure 17.

Figure 17. Counter/Timers Block Diagram

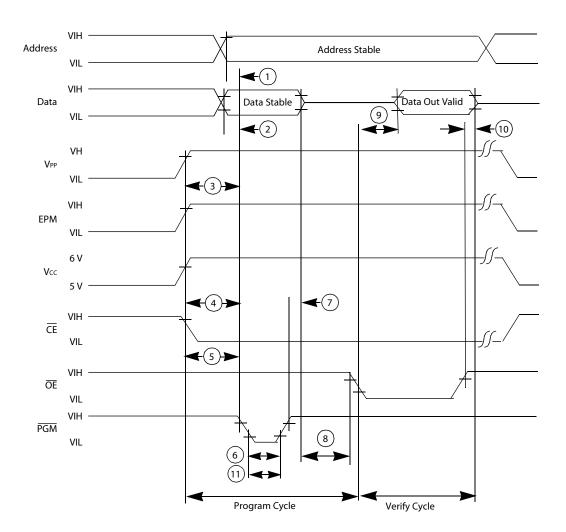

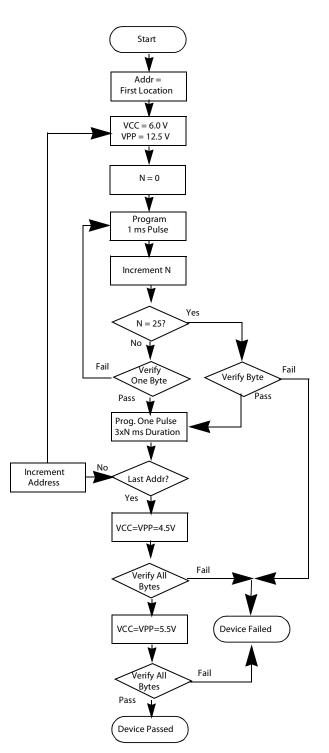

Figure 21. EPROM Program and Verify Timing

#### **User Mode 3: PROM Verify**

The Program Verify cycle is used as part of the intelligent programming algorithm to insure data integrity under worst-case conditions. It differs from the EPROM Read cycle in that  $V_{PP}$  is active and  $V_{CC}$  must be driven to 6.0V. Timing is shown in Figure 21.

### User Modes 4 and 5: EPROM and RAM Protect

To extend program security, EPROM and RAM protect cycles are provided for the Z86E61/Z86E63 MCU. Execution of the EPROM protect cycle prohibits proper execution of the EPROM Read, EPROM Verify, and EPROM programming cycles. Execution of the RAM protect cycle disables accesses to the upper 128 bytes of register memory (excluding

Figure 23. Intelligent Programming Flowchart

## **Absolute Maximum Ratings**

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for an extended period may affect device reliability.

Table 34 lists the absolute maximum ratings of the Z86E61/Z86E63 MCU.

| Symbol           | Description                   | Min  | Max        | Unit |

|------------------|-------------------------------|------|------------|------|

| V <sub>CC</sub>  | Supply Voltage <sup>1</sup>   | -0.3 | +7.0       | V    |

| T <sub>STG</sub> | Storage Temperature           | -65  | +150       | °C   |

| Τ <sub>Α</sub>   | Operating Ambient Temperature |      | See Note 2 | °C   |

Table 34. Absolute Maximum Ratings

Voltages on all pins with respect to <u>GND</u>.

2. See Ordering Information on page 60.

## **Standard Test Conditions**

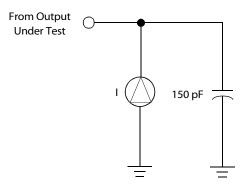

The characteristics described in this document apply to standard test conditions, as noted. All voltages are referenced to GND, and positive current flows into the referenced pin; see Figure 24.

Figure 24. Test Load Diagram

### **DC Characteristics**

Table 35 lists voltage and direct current characteristics for the Z86E61/Z86E63 MCU under differing conditions. Be advised that  $I_{CC2}$  requires loading TMR (F1Hh) with any value prior to STOP execution. Use the following sequence:

LD TMR,#00 NOP STOP

| Symbol           | Parameter                | Min  | Max                  | Typical<br>@ 25°C | Units | Conditions                                                 |

|------------------|--------------------------|------|----------------------|-------------------|-------|------------------------------------------------------------|

|                  | Max Input Voltage        |      | 7                    |                   | V     | Ι <sub>IN</sub> < 250μΑ.                                   |

|                  | Max Input Voltage        | 13   |                      |                   | V     | P33–P30 Only.                                              |

| V <sub>CH</sub>  | Clock Input High Voltage | 3.8  | V <sub>CC</sub> +0.3 |                   | V     | Driven by External Clock Generator.                        |

| V <sub>CL</sub>  | Clock Input Low Voltage  | -0.3 | 0.8                  |                   | V     | Driven by External Clock Generator.                        |

| V <sub>IH</sub>  | Input High Voltage       | 2.0  | V <sub>CC</sub> +0.3 |                   | V     |                                                            |

| V <sub>IL</sub>  | Input Low Voltage        | -0.3 | 0.8                  |                   | V     |                                                            |

| V <sub>OH</sub>  | Output High Voltage      | 2.4  |                      |                   | V     | I <sub>OH</sub> = -2.0mA.                                  |

| V <sub>OL</sub>  | Output Low Voltage       |      | 0.4                  |                   | V     | I <sub>OL</sub> = +2.0mA.                                  |

| V <sub>RH</sub>  | Reset Input High Voltage | 3.8  | V <sub>CC</sub> +0.3 |                   | V     |                                                            |

| V <sub>RL</sub>  | Reset Input Low Voltage  | -0.3 | 0.8                  |                   | V     |                                                            |

| IIL              | Input Leakage            | -10  | 10                   |                   | μA    | $V_{IN} = 0V, 5.25V.$                                      |

| I <sub>OL</sub>  | Output Leakage           | -10  | 10                   |                   | μA    | $V_{IN} = 0V, 5.25V.$                                      |

| I <sub>IR</sub>  | Reset Input Current      |      | -50                  |                   | μA    | V <sub>CC</sub> =+5.25V; V <sub>RL</sub> =0V.              |

| I <sub>CC</sub>  | Supply Current           |      | 50                   | 25                | mA    | @ 16MHz.                                                   |

|                  |                          |      | 60                   | 35                | mA    | @ 20MHz.                                                   |

| I <sub>CC1</sub> | Standby Current          |      | 15                   | 5                 | mA    | HALT Mode @ 16MHz;<br>V <sub>IN</sub> =0V, V <sub>CC</sub> |

|                  |                          |      | 20                   | 10                | mA    | HALT Mode @ 20MHz;<br>V <sub>IN</sub> =0V, V <sub>CC</sub> |

| I <sub>CC2</sub> | Standby Current          |      | 20                   | 5                 | μA    | STOP Mode<br>V <sub>IN</sub> =0V, V <sub>CC</sub>          |

#### **Table 35. Direct Current Characteristics**

### 35

### **Supply Current**

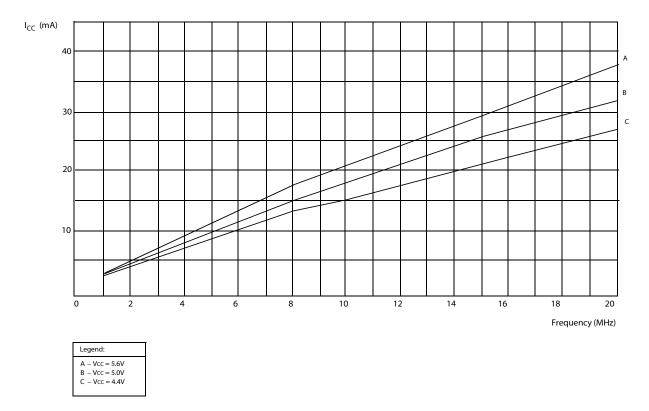

Figure 25 shows the typical supply current values (in milliamps), for the Z86E61/Z86E63 MCU as a function of frequency (in megahertz).

Figure 25. Typical  $\ensuremath{\mathsf{I}_{CC}}$  vs. Frequency

Table 36 lists the alternating current characteristics for the Z86E61/Z86E63 MCU as they relate to Figure 27. Formulas for each parameter are listed in Table 37.

|     |           |                                                               | T <sub>A</sub> = 0°C to +70°C |     |       |     |       |       |

|-----|-----------|---------------------------------------------------------------|-------------------------------|-----|-------|-----|-------|-------|

|     |           | -                                                             | 16MHz <sup>1</sup>            |     | 20MHz |     | -     |       |

| No. | Symbol    | Parameter                                                     | Min                           | Max | Min   | Max | Units | Notes |

| 1   | TdA(AS)   | Address Valid to AS Rise Delay                                | 20                            |     | 26    |     | ns    | 2,3   |

| 2   | TdAS(A)   | AS Rise to Address Float Delay                                | 30                            |     | 28    |     | ns    | 2,3   |

| 3   | TdAS(DR)  | AS Rise to Read Data Req'd Valid                              |                               | 180 |       | 160 | ns    | 2,3,4 |

| 4   | TwAS      | AS Low Width                                                  | 35                            |     | 36    |     | ns    | 2,3   |

| 5   | TdAZ(DS)  | Address Float to DS Fall                                      | 0                             |     | 0     |     | ns    |       |

| 6   | TwDSR     | DS (Read) Low Width                                           | 135                           |     | 130   |     | ns    | 2,3,4 |

| 7   | TwDSW     | DS (Write) Low Width                                          | 80                            |     | 75    |     | ns    | 2,3,4 |

| 8   | TdDSR(DR) | DS Fall to Read Data Req'd Valid                              |                               | 75  |       | 100 | ns    | 2,3,4 |

| 9   | ThDR(DS)  | Read Data to DS Rise Hold Time                                | 0                             |     | 0     |     | ns    | 2,3   |

| 10  | TdDS(A)   | DS Rise to Address Active Delay                               | 35                            |     | 48    |     | ns    | 2,3   |

| 11  | TdDS(AS)  | DS Rise to AS Fall Delay                                      | 30                            |     | 36    |     | ns    | 2,3   |

| 12  | TdR/W(AS) | R/W Valid to AS Rise Delay                                    | 20                            |     | 32    |     | ns    | 2,3   |

| 13  | TdDS(R/W) | DS Rise to R//W Not Valid                                     | 30                            |     | 36    |     | ns    | 2,3   |

| 14  | TdDW(DSW) | Write Data Valid to $\overline{\text{DS}}$ Fall (Write) Delay | 25                            |     | 40    |     | ns    | 2,3   |

| 15  | TdDS(DW)  | DS Rise to Write Data Not Valid Delay                         | 30                            |     | 40    |     | ns    | 2,3   |

| 16  | TdA(DR)   | Address Valid to Read Data<br>Req'd Valid                     |                               | 200 |       | 200 | ns    | 2,3,4 |

| 17  | TdAS(DS)  | AS Rise to $\overline{\text{DS}}$ Fall Delay                  | 40                            |     | 48    |     | ns    | 2,3   |

| 18  | TdDM(AS)  | DM Valid to AS Fall Delay                                     | 30                            |     | 36    |     | ns    | 2,3   |

Table 36. External I/O or Memory Read and Write Timing

Notes:

1. All timing references use 2.0V for a logic 1 and 0.8V for a logic 0.

2. Timing numbers given are for minimum TpC.

3. See <u>Table 37</u>.

4. When using extended memory timing, add 2 TpC.

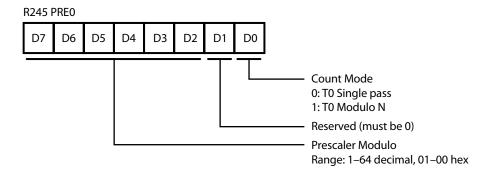

Figure 36. Prescaler 0 Register (F5H: Write Only)

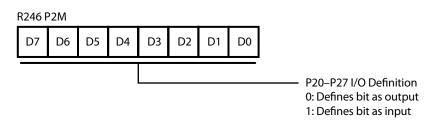

Figure 37. Port 2 Mode Register (F6H: Write Only)

#### Z86E61/Z86E63 Microcontrollers Product Specification

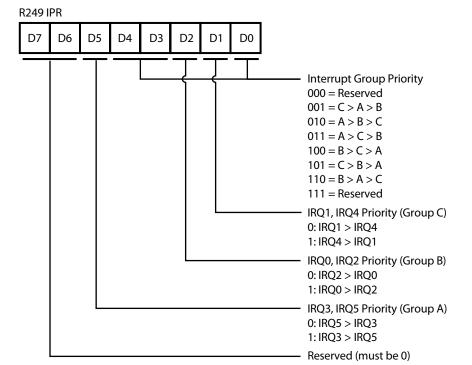

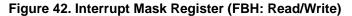

Figure 40. Interrupt Priority Register (F9H: Write Only)

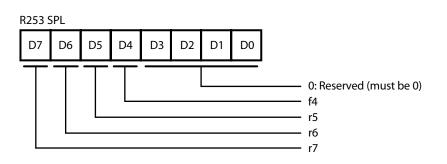

Figure 44. Register Pointer Register (FDH: Read/Write)