Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                 |

|----------------------------|--------------------------------------------------------|

| Core Processor             | Z8                                                     |

| Core Size                  | 8-Bit                                                  |

| Speed                      | 16MHz                                                  |

| Connectivity               | UART/USART                                             |

| Peripherals                | -                                                      |

| Number of I/O              | 32                                                     |

| Program Memory Size        | 32KB (32K x 8)                                         |

| Program Memory Type        | OTP                                                    |

| EEPROM Size                | -                                                      |

| RAM Size                   | 236 x 8                                                |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                            |

| Data Converters            | -                                                      |

| Oscillator Type            | Internal                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                        |

| Mounting Type              | Through Hole                                           |

| Package / Case             | 40-DIP (0.620", 15.75mm)                               |

| Supplier Device Package    | -                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z86e6316psg |

|                            |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

Each instance in the following revision history table reflects a change to this document from its previous version. For more details, refer to the corresponding pages or appropriate links provided in the table.

|             | Revision |                                                                                                              |             |

|-------------|----------|--------------------------------------------------------------------------------------------------------------|-------------|

| Date        | Level    | Description                                                                                                  | Page        |

| Feb<br>2012 | 04       | Globally updated for style and content.                                                                      | All         |

| Oct<br>2008 | 03       | Updated pin descriptions.                                                                                    | <u>11</u>   |

| May<br>2008 | 02       | Added LQFP pin diagram (Standard and Programming modes); replaced 44-pin QFP with 44-pin LQFP for CR #10886. | <u>7, 8</u> |

| Nov<br>2001 | 01       | Original issue.                                                                                              | All         |

# **Pin Functions**

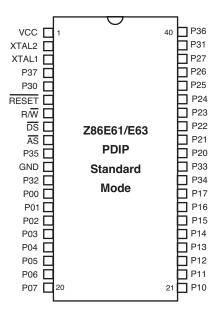

The Z86E61/Z86E63 MCU is available in variety of package styles, programming modes and pin configurations. This section describes the pin signals and configurations for each of the 40-pin PDIP, 44-pin PLCC and 44-pin LQFP packages in both Standard and EPROM Programming modes.

# **Pin Signals**

Figure 2 shows the pin-outs for the 40-pin PDIP Standard Mode package; Table 25 describes each pin.

Figure 2. Z86E61/Z86E63 PDIP Pin Diagram, Standard Mode

| Table 25. Z86E61/Z86E63 | PDIP Pin | Description. | Standard Mode |

|-------------------------|----------|--------------|---------------|

|                         |          |              |               |

| Pin Signal | Description              | I/O    |

|------------|--------------------------|--------|

| XTAL2      | Crystal Oscillator Clock | Output |

| XTAL1      | Crystal Oscillator Clock | Input  |

| RESET      | Reset                    | Input  |

| R/W        | Read/Write               | Output |

| Pin Signal      | Description         | I/O          |

|-----------------|---------------------|--------------|

| DS              | Data Strobe         | Output       |

| AS              | Address Strobe      | Output       |

| P00-P07 Port 0  | 8-bit General I/O   | Input/Output |

| P10-P17 Port 1  | 8-bit General I/O   | Input/Output |

| P20-P27 Port 2  | 8-bit General I/O   | Input/Output |

| P30-P33 Port 3  | 4-bit Input         | Input        |

| P34-P37 Port 3  | 4-bit Output        | Output       |

| R/RL            | ROM/ROMless Control | Input        |

| GND             | Ground              | Input        |

| V <sub>CC</sub> | Power Supply        | Input        |

# Table 25. Z86E61/Z86E63 PDIP Pin Description, Standard Mode (Continued)

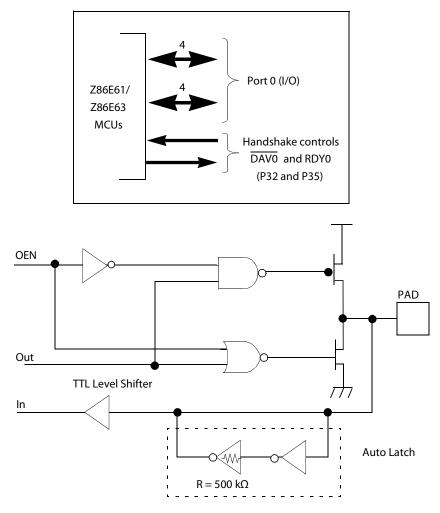

Figure 8. Port 0 Configuration

### Port 1 (P17-P10)

Port 1 is an 8-bit, byte programmable, bidirectional, TTL compatible port. It has multiplexed Address (A7–A0) and Data (D7–D0) ports. For the Z86E61/Z86E63 MCU, these eight I/O lines can be programmed as input or output lines or are configured under software control as an address/data port for interfacing external memory. When used as an I/O port, Port 1 can be placed under handshake control. In this configuration, Port 3 lines, P33 and P34, are used as the handshake controls RDY1 and DAV1.

Memory locations greater than 16384 (Z86E61) or 32768 (Z86E63) are referenced through Port 1. To interface external memory, Port 1 must be programmed for the multi-

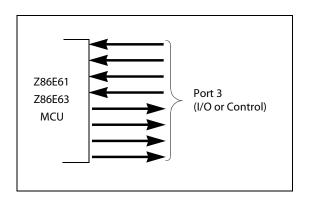

### Port 3 (P37–P30)

Port 3 is an 8-bit, CMOS compatible four-fixed input and four-fixed output port. These eight I/O lines have four-fixed (P33–P30) input and four-fixed (P37–P34) output ports. Port 3, when used as serial I/O, is programmed as serial in and serial out, respectively; see Figure 11.

Figure 11. Port 3 Configuration

Port 3 is configured under software control to provide the following control functions: handshake for Ports 0 and 2 (DAV and RDY); four external interrupt request signals (IRQ3–IRQ0); timer input and output signals ( $T_{IN}$  and  $T_{OUT}$ ) Data Memory Select ( $\overline{DM}$ ) and EPROM control signals (P30 =  $\overline{CE}$ , P31 =  $\overline{OE}$ , P32 = EPM and P33 =  $V_{PP}$ ).

Table 31 lists the pin assignments for Port 3.

| Table 3 | 31. Po | rt 3 Pin | Assignments* |

|---------|--------|----------|--------------|

|---------|--------|----------|--------------|

| Pin   | I/O          | СТСІ             | Interrupt      | P0 HS       | P1 HS    | P2 HS | UART       | Ext | EPROM           |

|-------|--------------|------------------|----------------|-------------|----------|-------|------------|-----|-----------------|

| P30   | In           | T <sub>IN</sub>  | IRQ3           |             |          |       | Serial In  |     | CE              |

| P31   | In           | T <sub>IN</sub>  | IRQ2           |             |          | D/R   |            |     | OE              |

| P32   | In           | T <sub>IN</sub>  | IRQ0           | D/R         |          |       |            |     | EPM             |

| P33   | In           | T <sub>IN</sub>  | IRQ1           |             | D/R      |       |            |     | V <sub>PP</sub> |

| P34   | Out          | T <sub>OUT</sub> |                |             | R/D      |       |            | DM  |                 |

| P35   | Out          | T <sub>OUT</sub> |                | R/D         |          |       |            |     |                 |

| P36   | Out          | T <sub>OUT</sub> |                |             |          | R/D   |            |     |                 |

| P37   | Out          | T <sub>OUT</sub> |                |             |          |       | Serial Out |     |                 |

| Т0    |              |                  | IRQ4           |             |          |       |            |     |                 |

| T1    |              |                  | IRQ5           |             |          |       |            |     |                 |

| Note: | *HS = Handsh | nake Signa       | ls; D = Data A | vailable; R | = Ready. |       |            |     |                 |

**UART Operation.** Port 3 lines, P37 and P30, are programmed as serial I/0 lines for fullduplex serial asynchronous receiver/transmitter operation. The bit rate is controlled by Counter/ Timer0.

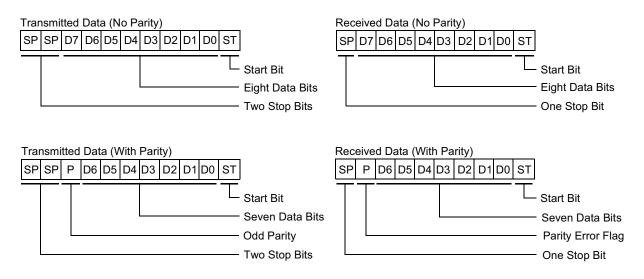

The Z86E61/Z86E63 MCU automatically adds a start bit and two stop bits to transmitted data; see Figure 12. Odd parity is also available as an option. Eight data bits are always transmitted, regardless of parity selection. If parity is enabled, the eighth bit is the odd parity bit. An interrupt request (IRQ4) is generated on all transmitted characters.

Received data must have a start bit, eight data bits, and at least one stop bit. If parity is on, bit 7 of the received data is replaced by a parity error flag. Received characters generate the IRQ3 interrupt request.

Figure 12. Serial Data Formats

**Auto Latch.** The Auto Latch puts valid CMOS levels on all CMOS inputs that are not externally driven. This reduces excessive supply current flow in the input buffer when it is not driven by any source.

**Note:** P33–P30 inputs differ from the Z86C61/C63 in that there is no clamping diode to  $V_{CC}$  because of the EPROM high voltage detection circuits. Exceeding the  $V_{IH}$  maximum specification during standard operating mode may cause the device to enter EPROM Mode.

# **Data Memory**

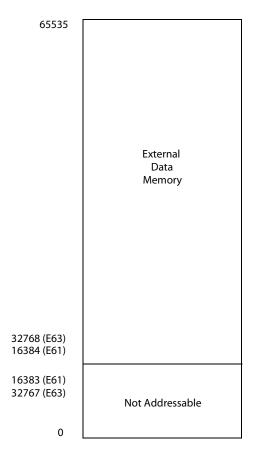

The EPROM version can address up to 48KB (Z86E61) or 32KB (Z86E63) of external data memory (DM) space beginning at location 16384 (Z86E61) or 32768 (Z86E63). The ROMless version can address up to 64KB of external data memory. External data memory may be included with, or separated from, the external program memory space. DM, an optional I/0 function that can be programmed to appear on pin P34, is used to distinguish between data and program memory space; see Figure 14. The state of the DM signal is controlled by the type instruction being executed. An LDC opcode references PROGRAM (DM inactive) memory, and an LDE instruction references DATA (DM active Low) memory.

Figure 14. Data Memory Configuration

# **Register File**

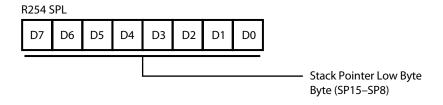

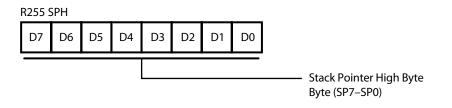

The register file consists of four I/0 port registers, 236 general-purpose registers, and 16 control and status registers, as shown in Figure 15. The instructions can access registers directly or indirectly through an 8-bit address field. The Z86E61/Z86E63 MCU also allows short 4-bit register addressing using the Register Pointer, which is shown in Figure 16. In 4-bit mode, the Register File is divided into 16 working register groups, each occupying 16 continuous locations. The Register Pointer addresses the starting location of the active working register group.

| LOCATION |                              | IDENTIFIERS |

|----------|------------------------------|-------------|

| R255     | Stack Pointer (Bits 7–0)     | SPL         |

| R254     | Stack Pointer (Bits 15–8)    | SPH         |

| R253     | Register Pointer             | RP          |

| R252     | Program Control Flags        | FLAGS       |

| R251     | Interrupt Mask Register      | IMR         |

| R250     | Interrupt Request Register   | IRQ         |

| R249     | Interrupt Priority Register  | IPR         |

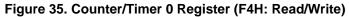

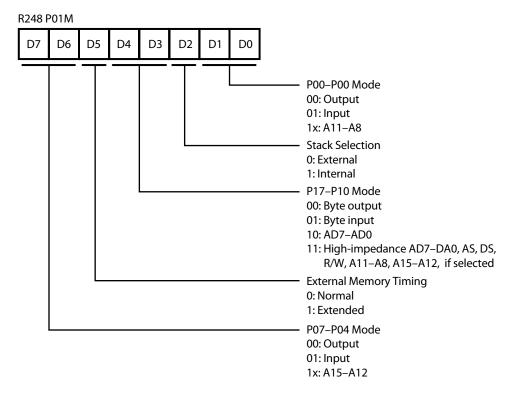

| R248     | Port 0–1 Mode                | P01M        |

| R247     | Port 3 Mode                  | РЗМ         |

| R246     | Port 2 Mode                  | P2M         |

| R245     | T0 Prescaler                 | PRE0        |

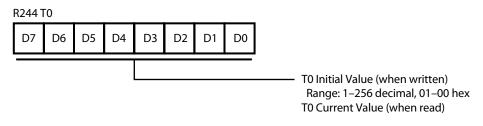

| R244     | Timer/Counter0               | Т0          |

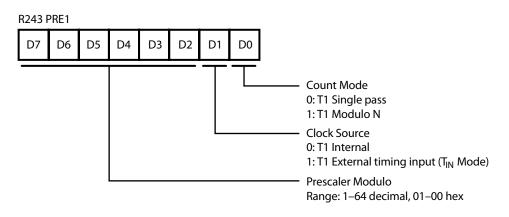

| R243     | T1 Prescaler                 | PRE1        |

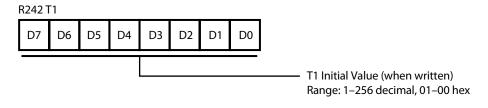

| R242     | Timer/Counter1               | T1          |

| R241     | Timer Mode                   | TMR         |

| R240     | Serial I/O                   | SIO         |

| R239     |                              |             |

|          | General Purpose<br>Registers |             |

| R4       |                              | 53          |

| R3       | Port 3                       | Р3          |

| R2       | Port 2                       | P2          |

| R1       | Port 1                       | P1          |

| RO       | Port 0                       | PO          |

Figure 15. Register File

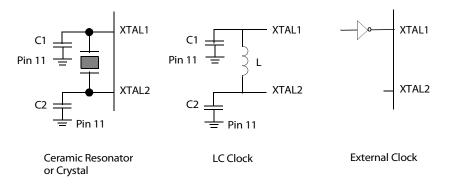

Figure 19. Oscillator Configuration

**Note:** The actual capacitor value is specified by the crystal manufacturer.

## HALT

Turns off the internal CPU clock but not the XTAL oscillation. The counter/timers and external interrupts IRQ0, IRQ1, IRQ2, and IRQ3 remain active. The devices are recovered by interrupts, either externally or internally generated. An interrupt request must be executed (enabled) to exit HALT Mode. After the interrupt service routine, the program continues from the instruction after the HALT.

## STOP

This instruction turns off the internal clock and external crystal oscillation, and reduces the standby current to  $5\mu A$  (typical) or less. The STOP Mode is terminated by a reset, which causes the processor to restart the application program at address 000Ch.

To enter STOP (or HALT) Mode, it is necessary to first flush the instruction pipeline to avoid suspending execution in mid-instruction. To do this, the user must execute a NOP (opcode = 0FFH) immediately before the appropriate SLEEP instruction, as shown in the following code segment.

| FF | NOP  | ; | clear | the pipeline |

|----|------|---|-------|--------------|

| 6F | STOP | ; | enter | STOP Mode    |

| or |      |   |       |              |

| FF | NOP  | ; | clear | the pipeline |

| 7F | HALT | ; | enter | HALT Mode    |

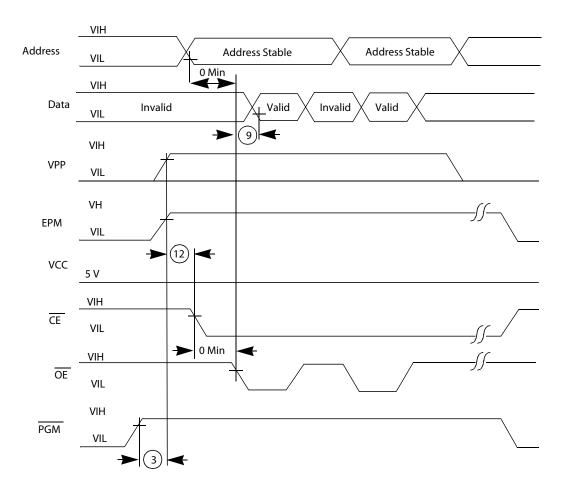

### **User MODE 2: EPROM Program**

The Z86E61/Z86E63 MCU's Program function conforms to the Intelligent programming algorithm. The device is programmed with  $V_{CC}$ , at 6.0 V and  $V_{PP} = 12.5$  V. Programming pulses are applied in 1 ms increments to a maximum of 25 pulses before proper verification. After verification, a programming pulse of three times the duration of the cycles necessary to program the device is issued to ensure proper programming. After all addresses are programmed, a final data comparison is executed and the programming cycle is complete. Timing for the Z86E61/Z86E63 MCU programming cycle is shown in Figure 21.

# **DC Characteristics**

Table 35 lists voltage and direct current characteristics for the Z86E61/Z86E63 MCU under differing conditions. Be advised that  $I_{CC2}$  requires loading TMR (F1Hh) with any value prior to STOP execution. Use the following sequence:

LD TMR,#00 NOP STOP

| Symbol           | Parameter                | Min  | Max                  | Typical<br>@ 25°C | Units | Conditions                                                 |

|------------------|--------------------------|------|----------------------|-------------------|-------|------------------------------------------------------------|

|                  | Max Input Voltage        |      | 7                    |                   | V     | Ι <sub>IN</sub> < 250μΑ.                                   |

|                  | Max Input Voltage        | 13   |                      |                   | V     | P33–P30 Only.                                              |

| V <sub>CH</sub>  | Clock Input High Voltage | 3.8  | V <sub>CC</sub> +0.3 |                   | V     | Driven by External Clock Generator.                        |

| V <sub>CL</sub>  | Clock Input Low Voltage  | -0.3 | 0.8                  |                   | V     | Driven by External Clock Generator.                        |

| VIH              | Input High Voltage       | 2.0  | V <sub>CC</sub> +0.3 |                   | V     |                                                            |

| V <sub>IL</sub>  | Input Low Voltage        | -0.3 | 0.8                  |                   | V     |                                                            |

| V <sub>OH</sub>  | Output High Voltage      | 2.4  |                      |                   | V     | I <sub>OH</sub> = -2.0mA.                                  |

| V <sub>OL</sub>  | Output Low Voltage       |      | 0.4                  |                   | V     | I <sub>OL</sub> = +2.0mA.                                  |

| V <sub>RH</sub>  | Reset Input High Voltage | 3.8  | V <sub>CC</sub> +0.3 |                   | V     |                                                            |

| V <sub>RL</sub>  | Reset Input Low Voltage  | -0.3 | 0.8                  |                   | V     |                                                            |

| IIL              | Input Leakage            | -10  | 10                   |                   | μA    | $V_{IN} = 0V, 5.25V.$                                      |

| I <sub>OL</sub>  | Output Leakage           | -10  | 10                   |                   | μA    | $V_{IN} = 0V, 5.25V.$                                      |

| I <sub>IR</sub>  | Reset Input Current      |      | -50                  |                   | μA    | V <sub>CC</sub> =+5.25V; V <sub>RL</sub> =0V.              |

| I <sub>CC</sub>  | Supply Current           |      | 50                   | 25                | mA    | @ 16MHz.                                                   |

|                  |                          |      | 60                   | 35                | mA    | @ 20MHz.                                                   |

| I <sub>CC1</sub> | Standby Current          |      | 15                   | 5                 | mA    | HALT Mode @ 16MHz;<br>V <sub>IN</sub> =0V, V <sub>CC</sub> |

|                  |                          |      | 20                   | 10                | mA    | HALT Mode @ 20MHz;<br>V <sub>IN</sub> =0V, V <sub>CC</sub> |

| I <sub>CC2</sub> | Standby Current          |      | 20                   | 5                 | μA    | STOP Mode<br>V <sub>IN</sub> =0V, V <sub>CC</sub>          |

### **Table 35. Direct Current Characteristics**

# **AC Characteristics**

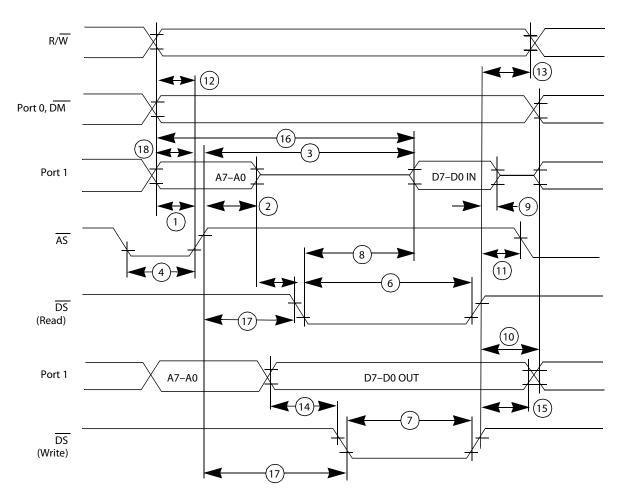

Figure 27 displays the timing characteristics for the Z86E61/Z86E63 MCU. The circled numbers in this figure reference a description in Table 36 of each symbol, its parameter and its frequency range for these 16MHz and 20MHz parts.

Figure 27. External I/O or Memory Read/Write Timing

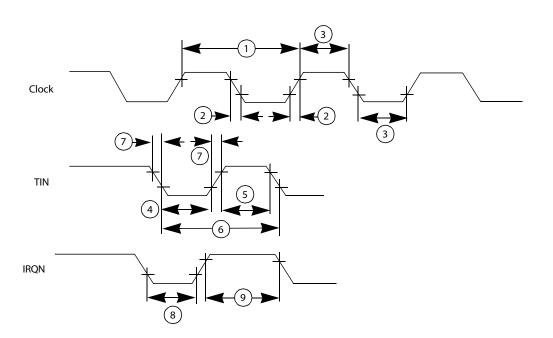

Additional timing characteristics are shown in Figure 30 and described in Table 39.

Figure 30. Additional Timing

### Table 39. Additional Timing

|     |                                      |                               | ٦    |                  |      |      |       |       |

|-----|--------------------------------------|-------------------------------|------|------------------|------|------|-------|-------|

|     |                                      |                               | 16M  | lHz <sup>1</sup> | 20 M | ΛHz  | -     |       |

| No. | Symbol                               | Parameter                     | Min  | Мах              | Min  | Max  | Units | Notes |

| 1   | ТрС                                  | Input Clock Period            | 62.5 | 1000             | 50   | 1000 | ns    | 1     |

| 2   | TrC,TfC                              | Clock Input Rise & Fall Times |      | 10               |      | 15   | ns    | 1     |

| 3   | TwC                                  | Input Clock Width             | 21   |                  | 37   |      | ns    | 1     |

| 4   | TwT <sub>IN</sub> L                  | Timer Input Low Width         | 50   |                  | 75   |      | ns    | 2     |

| 5   | TwT <sub>IN</sub> H                  | Timer Input High Width        | 5TpC |                  | 5TpC |      |       | 2     |

| 6   | TpT <sub>IN</sub>                    | Timer Input Period            | 8TpC |                  | 8TpC |      |       | 2     |

| 7   | TrT <sub>IN</sub> ,TfT <sub>IN</sub> | Timer Input Rise & Fall times | 100  |                  | 100  |      | ns    | 2     |

### Notes:

1. Clock timing references use 3.8V for a logic 1 and 0.8V for a logic 0.

2. Timing references use 2.0V for a logic 1 and 0.8V for a logic 0.

3. Interrupt request through Port 3 (P33–P31).

- 4. Interrupt request through Port 30.

- 5. Interrupt references request through Port 3.

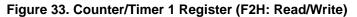

Figure 34. Prescaler 1 Register (F3H: Write Only)

### Z86E61/Z86E63 Microcontrollers Product Specification

Figure 39. Port 0 and 1 Mode Register (F8H: Write Only)

### Z86E61/Z86E63 Microcontrollers Product Specification

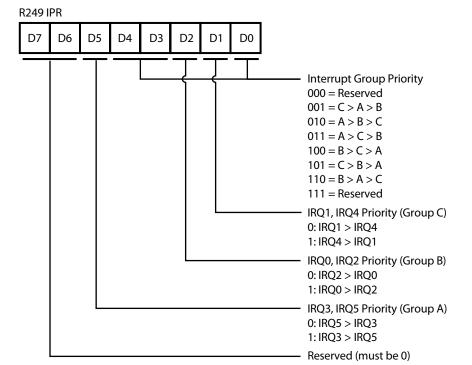

Figure 40. Interrupt Priority Register (F9H: Write Only)

# **Z8 Instruction Set**

This section discusses the addressing modes, symbols, flags, condition codes and instruction formats that apply to the Z8 instruction set. A summary of the Z8 instruction set follows on page 55.

The notations listed in Table 40 are used to describe addressing modes and instruction operations.

| Notation | Definition                                                        |

|----------|-------------------------------------------------------------------|

| IRR      | Indirect register pair or indirect working register pair address. |

| Irr      | Indirect working register pair only.                              |

| Х        | Indexed address.                                                  |

| DA       | Direct address.                                                   |

| RA       | Relative address.                                                 |

| IM       | Immediate.                                                        |

| R        | Register or working register address.                             |

| r        | Working register address only.                                    |

| IR       | Indirect register or indirect working register address.           |

| lr       | Indirect working register address only.                           |

| RR       | Register pair or working register pair address.                   |

### Table 40. Instruction Set Notation

The symbols listed in Table 41are used to describe the Z8 instruction set.

### Table 41. Instruction Set Symbols

| Definition                            |

|---------------------------------------|

| Destination location or contents.     |

| Source location or contents.          |

| Condition code.                       |

| Indirect address prefix.              |

| Stack Pointer.                        |

| Program Counter.                      |

| Flag Register (Control Register 252). |

| Register Pointer (R253).              |

| Interrupt Mask Register (R251).       |

|                                       |

| 57 |

|----|

|----|

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Instruction and Operation | Address Mode |     | Op Code Byte | Flags Affected |   |   |   |   |   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------|-----|--------------|----------------|---|---|---|---|---|

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                           | dst          | src |              |                | Ζ | S | V | D | Н |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | LD dst, src               | r            | Im  | rC           | _              | _ | _ | _ | _ | _ |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | dst ← src                 | r            | R   | r8           |                |   |   |   |   |   |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                           | R            | r   | r9           |                |   |   |   |   |   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                           |              |     | r = 0 – F    |                |   |   |   |   |   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                           |              | Х   | C7           |                |   |   |   |   |   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                           | Х            | r   |              |                |   |   |   |   |   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                           | r            | lr  | E3           |                |   |   |   |   |   |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                           | Ir           | r   | F3           |                |   |   |   |   |   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                           | R            | R   | E4           |                |   |   |   |   |   |

| $\begin{array}{c c c c c c c c c } & IR & IM & E7 \\ IR & R & F5 \\ \hline LDC dst, src & r & Irr & C2 & - & - & - & - & - & - \\ dst \leftarrow src & r & Irr & Irr & C3 & - & - & - & - & - & - \\ dst \leftarrow src & r \leftarrow r+1; & & & & & & & & & & & & & & & & & & &$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           | R            | IR  | E5           |                |   |   |   |   |   |

| $\begin{array}{c c c c c c c c c } IR & R & F5 \\ \hline LDC dst, src & r & Irr & C2 & - & - & - & - & - & - & - & - & - & $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                           | R            | IM  | E6           |                |   |   |   |   |   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                           | IR           | IM  | E7           |                |   |   |   |   |   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                           | IR           | R   | F5           |                |   |   |   |   |   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | LDC dst, src              | r            | Irr | C2           | _              | _ | _ | _ | _ | _ |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | dst ← src                 |              |     |              |                |   |   |   |   |   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | LDCI dst, src             | lr           | Irr | C3           | _              | _ | _ | _ | _ | _ |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | dst   ← src               |              |     |              |                |   |   |   |   |   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | r ← r + 1;                |              |     |              |                |   |   |   |   |   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | rr ← rr + 1               |              |     |              |                |   |   |   |   |   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | NOP                       |              |     | FF           | -              | _ | _ | _ | _ | - |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | OR dst, src               | See Note 1   |     | 4[ 1         | _              | * | * | 0 | _ | _ |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                           |              |     | -            |                |   |   |   |   |   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | POP                       | R            |     | 50           | _              | _ | _ | _ | _ | _ |

| PUSH src       R       70       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <th< td=""><td>dst <math>\leftarrow</math> @SP;</td><td>IR</td><td></td><td>51</td><td></td><td></td><td></td><td></td><td></td><td></td></th<> | dst $\leftarrow$ @SP;     | IR           |     | 51           |                |   |   |   |   |   |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $SP \leftarrow SP + 1$    |              |     |              |                |   |   |   |   |   |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PUSH src                  | R            |     | 70           | _              | _ | _ | _ | _ | _ |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $SP \leftarrow SP - 1;$   | IR           |     | 71           |                |   |   |   |   |   |

| $\begin{array}{c c} C \leftarrow 0 \\ \hline \textbf{RET} & & AF & - & - & - & - & - & - & - & - & - & $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                           |              |     |              |                |   |   |   |   |   |

| $\begin{array}{c c} C \leftarrow 0 \\ \hline \textbf{RET} & & AF & - & - & - & - & - & - & - & - & - & $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RCF                       |              |     | CF           | 0              | _ | _ | _ | _ | _ |

| $\begin{array}{c} PC \leftarrow @SP;\\ SP \leftarrow SP + 2\\ \hline \mathbf{RL}  \mathrm{dst} & R & 90 & * & * & * & * & - & - \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                           |              |     | •            | -              |   |   |   |   |   |

| $\begin{array}{c} PC \leftarrow @SP;\\ SP \leftarrow SP + 2\\ \hline \mathbf{RL}  \mathrm{dst} & R & 90 & * & * & * & * & - & - \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RET                       |              |     | AF           | _              | _ | _ | _ | _ | _ |

| $SP \leftarrow SP + 2 \\ \hline RL dst \\ R \\ 90 \\ * \\ * \\ * \\ * \\ - \\ - \\ - \\ - \\ - \\ -$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                           |              |     |              |                |   |   |   |   |   |

| <b>RL</b> USI R 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           |              |     |              |                |   |   |   |   |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RL dst                    | R            |     | 90           | *              | * | * | * | _ | _ |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           | IR           |     | 91           |                |   |   |   |   |   |

### Table 45. Instruction Summary (Continued)

Note: These instructions have an identical set of addressing modes, which are encoded for brevity. The first Op Code nibble is found in this instruction set table. The second nibble is expressed symbolically by a '[]' in this table, and its value is found on the left of the applicable addressing mode pair in the Op Code Map in Figure 48.

For example, the op code of an ADC instruction using the addressing modes r (destination) and Ir (source) is 13.

**Flags Affected**

V

\*

0

[

Х

0

1

D

1

Н

S

+

\*

**Instruction and Operation**

RLC dst

RR dst

RRC dst

SCF

$C \leftarrow 1$ SRA dst

SRP dst

RP ← src STOP

SUB dst, src

SWAP dst

TCM dst, src

(NOT dst)

$dst \leftarrow dst \leftarrow src$

SBC dst, src

$\mathsf{dst} \gets \mathsf{dst} \gets \mathsf{src} \gets \mathsf{C}$

| AND src                                |                                     |                   |         |          |         |         |       |      |

|----------------------------------------|-------------------------------------|-------------------|---------|----------|---------|---------|-------|------|

| TM dst, src<br>dst AND src             | See Note 1                          | 7[]               | _       | *        | *       | 0       | -     | _    |

| XOR dst, src<br>dst   ← dst<br>XOR src | See Note 1                          | B[ ]              | _       | *        | *       | 0       | _     | -    |

| Noto: Those instruction                | a have an identical act of addressi | a madaa which are | onoodoo | l for br | ov it v | Tho fir | ot On | Codo |

#### Table 45. Instruction Summary (Continued)

src

Op Code Byte

(Hex)

10

11

E0

E1

C0

C1

3[]

DF

D0

D1

31

6F

2[]

F0

F1

6[]

С

+

\*

\*

\*

1

\*

1

[

Х

[

\*

\*

ſ

\*

\*

Ζ

+

\*

\*

Address Mode

dst

R

IR

R

IR

R

IR

See Note 1

R

IR

Im

See Note 1

R

IR

See Note 1

Note: These instructions have an identical set of addressing modes, which are encoded for brevity. The first Op Code nibble is found in this instruction set table. The second nibble is expressed symbolically by a '[]' in this table, and its value is found on the left of the applicable addressing mode pair in the Op Code Map in Figure 48.

For example, the op code of an ADC instruction using the addressing modes r (destination) and Ir (source) is 13.