# E·XFL

## NXP USA Inc. - PNX1501E,557 Datasheet

Welcome to E-XFL.COM

**Embedded - Microcontrollers - Application Specific:** Tailored Solutions for Precision and Performance

#### Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

#### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application charific microcontrollars are applicated to

#### Details

| Product Status          | Obsolete                                                             |

|-------------------------|----------------------------------------------------------------------|

| Applications            | Multimedia                                                           |

| Core Processor          | TM3260                                                               |

| Program Memory Type     | -                                                                    |

| Controller Series       | Nexperia                                                             |

| RAM Size                | -                                                                    |

| Interface               | I <sup>2</sup> C, 2-Wire Serial                                      |

| Number of I/O           | 61                                                                   |

| Voltage - Supply        | 1.14V ~ 1.26V                                                        |

| Operating Temperature   | 0°C ~ 85°C                                                           |

| Mounting Type           | Surface Mount                                                        |

| Package / Case          | 456-BGA                                                              |

| Supplier Device Package | 456-BGA (27x27)                                                      |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/pnx1501e-557 |

|                         |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Philips Semiconductors**

#### Volume 1 of 1

| 3.1 | Registers Summary 5-31 | 3.2 |

|-----|------------------------|-----|

|-----|------------------------|-----|

#### **Chapter 6: Boot Module**

| 1.    | Introduction                                   |

|-------|------------------------------------------------|

| 2.    | Functional Description6-1                      |

| 2.1   | The Boot Modes 6-2                             |

| 2.2   | Boot Module Operation 6-4                      |

| 2.2.1 | MMIO Bus Interface 6-4                         |

| 2.2.2 | I2C Master 6-4                                 |

| 2.2.3 | Boot Control/State Machine 6-5                 |

| 2.3   | The Boot Command Language                      |

| 3.    | PNX15xx Series Boot Scripts Content 6-6        |

| 3.1   | The Common Behavior                            |

| 3.1.1 | Binary Sequence for the Common Boot Script 6-9 |

# **Chapter 7: PCI-XIO Module**

| 1.    | Introduction                                      | 4.         |

|-------|---------------------------------------------------|------------|

| 2.    | Functional Description7-2                         | 4.1        |

| 2.1   | Document title variable Block Level Diagram . 7-3 | 4.2        |

| 2.2   | Architecture                                      | 4.:        |

| 3.    | <b>Operation</b>                                  | 4.3        |

| 3.1   | Overview                                          | 4.3<br>4.3 |

| 3.1.1 | NAND-Flash Interface Operation                    | 4<br>4.:   |

| 3.1.2 | Motorola Style Interface                          | 4.         |

| 3.1.3 | NOR Flash Interface7-12                           |            |

| 3.1.4 | IDE Description                                   | 4.         |

| 3.2   | PCI Interrupt Enable Register                     | 5.         |

#### **Chapter 8: General Purpose Input Output Pins**

| 1.    | Introduction8-1                         | 3.1  |

|-------|-----------------------------------------|------|

| 2.    | Functional Description8-2               | 3.2  |

| 2.1   | GPIO: The Basic Pin Behavior8-2         | 4.   |

| 2.1.1 | GPIO Mode settings8-4                   | 4.1  |

| 2.1.2 | GPIO Data Settings MMIO Registers 8-4   | 4.2  |

| 2.1.3 | GPIO Pin Status Reading 8-6             | 4.3  |

| 2.2   | GPIO: The Event Monitoring Mode         | 4.4  |

| 2.2.1 | Timestamp Reference clock 8-7           |      |

| 2.2.2 | Timestamp format 8-7                    | 4.5  |

| 2.3   | GPIO: The Signal Monitoring & Pattern   |      |

|       | Generation Modes8-7                     | 4.6  |

| 2.3.1 | The Signal Monitoring Mode 8-8          | 4.7  |

| 2.3.2 | The Signal Pattern Generation Mode 8-11 | 4.8  |

| 2.4   | GPIO Error Behaviour 8-14               | 4.9  |

| 2.4.1 | GPIO Frequency Restrictions 8-15        | 4.10 |

| 2.5   | The GPIO Clock Pins                     | 4.11 |

| 2.6   | GPIO Interrupts8-17                     |      |

| 2.7   | Timer Sources8-18                       | 4.12 |

| 2.8   | Wake-up Interrupt8-18                   |      |

| 2.9   | External Watchdog8-18                   | 4.13 |

| 3.    | IR Applications                         | 4.14 |

| -     | FF                                      | 4.15 |

| 3.2   | Registers Description5-34                                  |

|-------|------------------------------------------------------------|

| 3.2   | The Specifics of the Boot From Flash Memory<br>Devices6-10 |

| 3.2.1 | Binary Sequence for the Section of the Flash Boot<br>6-12  |

| 3.3 | The Specifics of the Host-Assisted Mode 6-12 |

|-----|----------------------------------------------|

| 4.  | The Boot From an I2C EEPROM6-14              |

| 4.1 | External I2C Boot EEPROM Types6-14           |

| 4.2 | The Boot Commands and The Endian Mode. 6-15  |

| 4.3 | Details on I2C Operation6-15                 |

| 5.  | References                                   |

| 4.    | Application Notes                             |

|-------|-----------------------------------------------|

| 4.1   | DTL Interface                                 |

| 4.2   | System Memory Bus Interface, the MTL Bus 7-19 |

| 4.3   | XIO Interface                                 |

| 4.3.1 | Motorola Interface                            |

| 4.3.2 | NAND-Flash Interface7-20                      |

| 4.3.3 | NOR Flash Interface7-20                       |

| 4.3.4 | IDE Interface                                 |

| 4.4   | PCI Endian Support7-21                        |

| 4.5   | General Notes7-21                             |

| 5.    | Register Descriptions7-21                     |

| 5.1   | Register Summary7-22                          |

|        | Duty-cycle programming8-19                        |

|--------|---------------------------------------------------|

| ,<br>, | Spike Filtering                                   |

| -      |                                                   |

|        | MMIO Registers                                    |

|        | GPIO Mode Control Registers8-24                   |

| 2      | GPIO Data Control8-26                             |

| 3      | Readable Internal PNX15xx Series Signals 8-26     |

| 1      | Sampling and Pattern Generation Control           |

|        | Registers for the FIFO Queues8-27                 |

| 5      | Signal and Event Monitoring Control Registers for |

|        | the Timestamp Units8-34                           |

| 6      | Timestamp Unit Registers8-34                      |

| 7      | GPIO Time Counter8-34                             |

| 3      | GPIO TM3260 Timer Input Select                    |

| )      | GPIO Interrupt Status8-35                         |

| 0      | Clock Out Select                                  |

| 1      | GPIO Interrupt Registers for the FIFO Queues      |

|        | (One for each FIFO Queue)8-37                     |

| 2      | GPIO Module Status Register for all 12            |

|        | Timestamp Units8-38                               |

| 3      | GPIO POWERDOWN8-43                                |

| 4      | GPIO Module ID8-43                                |

| 5      | GPIO IO SEL Selection Values                      |

| 0      |                                                   |

|        |                                                   |

| Table 11: | Pixel Format Bit Assignments         |

|-----------|--------------------------------------|

| Table 12: | Dithering                            |

| Table 13: | Source Linear                        |

| Table 14: | Destination Linear                   |

| Table 15: | Source Stride                        |

| Table 16: | Destination Stride                   |

| Table 17: | Color Compare                        |

| Table 18: | Mono Host F Color or SurfAlpha       |

| Table 19: | Mono Host B Color or HAlpha Color    |

| Table 20: | Blt Control                          |

| Table 21: | Source Address, XY Coordinates       |

| Table 22: | Destination Address, XY Coordinates  |

| Table 23: | BLT Size                             |

| Table 24: | Destination Address, XY2 Coordinates |

| Table 25: | Vector Constant                      |

| Table 26: | Vector Count Control                 |

| Table 27: | TransMask                            |

| Table 28: | MonoPatFColor                        |

| Table 29: | MonoPatBColor                        |

| Table 30: | EngineStatus                         |

| Table 31: | PanicControl                         |

| Table 32: | EngineConfig                         |

| Table 33: | HostFIFOStatus                       |

| Table 34: | POWERDOWN                            |

| Table 35: | Module ID                            |

| Table 36: | Drawing Engine Data Registers        |

# Chapter 21: MPEG-1 and MPEG-2 Variable Length Decoder

| Table 1:  | Software Reset Procedure                              |

|-----------|-------------------------------------------------------|

| Table 2:  | VLD STATUS                                            |

| Table 3:  | VLD Control                                           |

| Table 4:  | VLD Commands                                          |

| Table 5:  | VLD Command Register                                  |

| Table 6:  | References for the MPEG-2 Macroblock Header Data21-11 |

| Table 7:  | References for the MPEG-1 Macroblock Header Data21-13 |

| Table 8:  | VLD Error Handling                                    |

| Table 9:  | Register Summary                                      |

| Table 10: | VLD Registers                                         |

#### **Chapter 22: Digital Video Disc Descrambler**

#### Chapter 23: LAN100 — Ethernet Media Access Controller

| Table 1: | LAN100 MMIO Register Map                   |  |

|----------|--------------------------------------------|--|

| Table 2: | LAN100 Registers                           |  |

| Table 3: | PatternMatchJoin Register Nibble Functions |  |

| Table 4: | Receive Descriptor Structure               |  |

| Table 5: | Receive Descriptor Control Word            |  |

| Table 6: | Receive Status Structure                   |  |

| Table 7: | Receive Status Information Word            |  |

| Table 8: | Transmit Descriptor Fields                 |  |

| Table 9: | Transmit Descriptor Control Word           |  |

**Chapter 1: Integrated Circuit Data**

# 6. DC/AC I/O Characteristics

The characteristics listed in the following tables apply to the worst case operating condition defined in <u>Section 5. on page 1-24</u>. All voltages are referenced to VSS (0 V digital ground). The following I/O characteristics includes the effect of process variation.

# 6.3 BPX2T14MCP Type I/O Circuit

#### Table 23: BPX2T14MCP Characteristics

| Symbol           | Parameter             | Condition/Notes                                | Min                 | Тур | Max                    | Unit |

|------------------|-----------------------|------------------------------------------------|---------------------|-----|------------------------|------|

| V <sub>OH</sub>  | Output High Voltage   |                                                | 0.9V <sub>CCP</sub> |     |                        | V    |

| V <sub>OL</sub>  | Output Low Voltage    |                                                |                     |     | 0.1V <sub>CCP</sub>    | V    |

| V <sub>IHT</sub> | DC Input High Voltage | Logic Threshold                                | 2.0                 |     |                        | V    |

| V <sub>ILT</sub> | DC Input Low Voltage  | Logic Threshold                                |                     |     | 0.8                    | V    |

| V <sub>IH</sub>  | DC Input High Voltage | This is the overshoot/                         |                     |     | V <sub>CCP</sub> + 0.3 | V    |

| $V_{\text{IL}}$  | DC Input Low Voltage  | undershoot protection specification of the pad | -0.3                |     |                        | V    |

| Z <sub>O</sub>   | Output AC Impedance   | High/Low level output state                    |                     | 22  |                        | Ω    |

| Pull             | Pull-up/down Resistor | If applicable                                  | 38                  | 66  | 165                    | KΩ   |

| C <sub>IN</sub>  | Input pin capacitance |                                                |                     |     | 6                      | pF   |

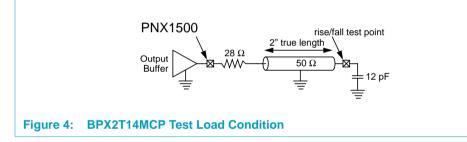

BPX2T14MCP I/Os require a board level 27-33  $\Omega$  series resistor to reduce ringing.

# 5. References

[1] "PNX1300 Series Media Processor", Feb. 15th 2002, Philips Semiconductors, Inc.

[2] "PCI Local Bus Specification, Rev 2.2", Dec. 18th, 1998, PCI Special Interest Group.

#### Registers

All IDE device registers are defined in the ATA-2 Specification. These registers can be accessed directly from PI or indirectly via GPXIO registers. The lower five bits of the GPXIO address register need to be configured as follows:

Table 4: GPXIO Address Configuration

| Address to be |                                    | Addre | ss on IDE |     |     |     |

|---------------|------------------------------------|-------|-----------|-----|-----|-----|

| Written       | Register Name                      | CS1   | CS0       | DA2 | DA1 | DA0 |

| 5'b40         | Data register                      | 1     | 0         | 0   | 0   | 0   |

| 5'b44         | ERR/Feature                        | 1     | 0         | 0   | 0   | 1   |

| 5'b48         | Sector count                       | 1     | 0         | 0   | 1   | 0   |

| 5'b4C         | Sector number                      | 1     | 0         | 0   | 1   | 1   |

| 5'b50         | Cylinder Low                       | 1     | 0         | 1   | 0   | 0   |

| 5'b54         | Cylinder High                      | 1     | 0         | 1   | 0   | 1   |

| 5'b58         | Device/Head                        | 1     | 0         | 1   | 1   | 0   |

| 5'b5C         | Status/Command                     | 1     | 0         | 1   | 1   | 1   |

| 5'b38         | Alternate status/Device<br>control | 0     | 1         | 1   | 1   | 0   |

#### **Programming IDE Registers**

IDE is a submodule of Document title variable. It shares PCI pins with other XIO blocks. Three XIO SEL pins can be configured for use by any XIO device. Each SEL pin is associated with the profile register in the PCI block. The profile register determines the mode of the SEL pin, pulse width for control signals and memory apertures for each mode.

Before accessing any IDE register, the appropriate profile register needs to be programmed. For example, if XIO\_SEL[1] has been used for IDE, the sel1\_profile register needs to be programmed and IDE needs to be enabled.

- At power on, the IDE disk will respond in PIO-0 mode only.

- Program the appropriate register in PIO-0 mode to set PIO-4 mode.

- Using sel1\_profile register, set lo and high period of DIOR/DIOW pulses for PIO-4 mode.

- High period in selx\_profile register is used for the setup time of DA/CS lines with DIOR/DIOW.

- Low period in selx\_profile register is used for the lo period of the DIOR/DIOW pulse.

- Hold of DA/CS with respect to DIOR/DIOW is always for one PCI clock.

- Recommended values for sel\_we\_hi and sel\_we\_lo for PIO-0 mode are 7 and 13, respectively (assuming a 33 MHz PCI clock).

- Recommended values for sel\_we\_hi and sel\_we\_lo for PIO-4 mode are 1 and 3 respectively.

## Table 8: Registers Description

|         |                         | Acces            |           |                                                                                                                                                                                                                                                                                 |

|---------|-------------------------|------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit     | Symbol                  | S                | Value     | Description                                                                                                                                                                                                                                                                     |

| Offset  | 0x04 0820               | GPXIO_addre      | ss        |                                                                                                                                                                                                                                                                                 |

| 31:0    | gpxio_addr              | R/W              | 0         | General Purpose XIO cycle address. This register sets the address<br>for an indirect read or write to/from XIO address space. Only 4 byte<br>writes are allowed in this register. The values programmed for bits (<br>and 1 are not used by the XIO module. Refer to gpxio_ben. |

| Offset  | 0x04 0824               | GPXIO_write_     | data      |                                                                                                                                                                                                                                                                                 |

| 31:0    | gpxio_wdata             | R/W              | 0         | General Purpose XIO cycle data. This register is programmed with data for a write cycle.                                                                                                                                                                                        |

| Offset  | 0x04 0828               | GPXIO_read_      | data      |                                                                                                                                                                                                                                                                                 |

| 31:0    | gpxio_rdata             | R                | 0         | General Purpose XIO cycle data. This register contains the data of a read cycle after completion.                                                                                                                                                                               |

| Offset  | 0x04 082C               | GPXIO_ctrl       |           |                                                                                                                                                                                                                                                                                 |

| This re | egister controls the ty | /pe of access to | XIO and p | provides status.                                                                                                                                                                                                                                                                |

| 31:10   | Reserved                | R                | 0         |                                                                                                                                                                                                                                                                                 |

| 9       | gpxio_cyc_pendin        | g R              | 0         | <ul><li>1 = GPXIO transaction on XIO is pending.</li><li>0 = GPXIO has completed or not yet started.</li></ul>                                                                                                                                                                  |

| 8       | gpxio_done              | R                | 0         | General Purpose XIO cycle complete. This bit is cleared by writing to bit 6 or 7. It will also be cleared by writing to the GPXIO interrup clear register.                                                                                                                      |

| 7       | clr_gpxio_done          | W                | 0         | 1 = Clear "gpxio_done."                                                                                                                                                                                                                                                         |

| 6       | gpxio_init              | R/W              | 0         | 1 = Initiate a transaction on XIO. The type of transaction will match<br>the profile of the selected aperture. This bit gets cleared if the cycle<br>has been initiated. This bit clears bit 8 if set.                                                                          |

| 5       | Reserved                | R                | 0         |                                                                                                                                                                                                                                                                                 |

| 4       | gpxio_rd                | R/W              | 0         | 1 = Read command on XIO<br>0 = Write command on XIO                                                                                                                                                                                                                             |

| 3:0     | gpxio_ben               | R/W              | 0         | Active low byte enables to be used on the indirect XIO cycle. These are used to determine how many bytes to access and the lower two address bits for use in "gpxio_addr".                                                                                                      |

| Offset  | 0x04 0830               | NAND-Flash o     | ontrols   |                                                                                                                                                                                                                                                                                 |

| 31:22   | Reserved                |                  |           |                                                                                                                                                                                                                                                                                 |

| 21:16   | nand_ctrls              | R/W              | 17        | This field controls the type of NAND-Flash access cycle. The bits are defined as follows:                                                                                                                                                                                       |

|         |                         |                  |           | [21]: 1= 64-MB device support; 0 = 32 MB and smaller device support                                                                                                                                                                                                             |

|         |                         |                  |           | <ul> <li>[20]: 1 = Include data in access cycle; 0 access does not include data phase(s)</li> <li>[19:18] = No. of commands to be used in NAND-Flash access</li> <li>[17:16] = No. of address phases to be used in NAND-Flash access</li> </ul>                                 |

|         |                         |                  |           |                                                                                                                                                                                                                                                                                 |

valid data and by putting their base addresses in the two BASEx\_PTR registers, their maximum size into the SIZE register and the number of valid words for DMA buffer 1 into the PG\_BUF\_CTRLx.BUF\_LEN bits.

When the FIFO queue is programmed into Pattern Generation mode, i.e. FIFO\_MODE[1]=1, BUF1\_RDY and BUF2\_RDY flags will get set, indicating that it is ready for a new DMA buffer containing valid data to be assigned.

Once two valid buffers are assigned and FIFO queue has been enabled the BUF1\_RDY flag must be cleared by software so that the GPIO module can load the BASE1\_PTR and the PG\_BUF\_CTRLx.BUF\_LEN values. After BUF1\_RDY has been cleared the software can program the BUF\_LEN value for DMA buffer 2. When the BUF2\_RDY flag is cleared the BASE2\_PTR and BUF\_LEN values for DMA buffer 2 are loaded by the GPIO modules.

**Remark:** If the BUF\_LEN values for DMA buffer1 and DMA buffer 2 are identical both BUF1\_RDY and BUF2\_RDY can be cleared at the same time.

The GPIO hardware now proceeds to empty DMA buffer 1 and transmitting the samples/timestamps on the selected GPIO pins. Once DMA buffer 1 is empty, BUF1\_RDY is asserted. If BUF2\_RDY has been cleared, transmission continues without interruption from DMA buffer 2. If BUF1\_RDY\_EN is enabled, a level triggered system level interrupt request is generated.

While BUF1\_RDY is high, the system software is required to assign a new buffer to BASE1\_PTRx, the number of valid words in the new buffer by setting PG\_BUF\_CTRLx.BUF\_LEN and then clear BUF1\_RDY (write a '1' to BUF1\_RDY\_CLR) before DMA buffer 2 fills up to avoid an Underrun condition.Transmission continues from buffer 2, until it is empty. At that time, BUF2\_RDY is asserted, and transmission continues from the new buffer 1, and so on. If an Underrun condition is reached the GPIO module stops the transmission, holds current values on the pins and does not warn the CPU that an underrun condition occurred.

**Remark:** The BASEx\_PTRx and PG\_BUF\_CTRLx.BUF\_LEN values for a DMA buffer are only loaded into the GPIO pattern generation logic when the relevant BUFx\_RDY signal has been cleared. Since the PG\_BUF\_CTRLx.BUF\_LEN register is shared between both DMA buffers it important that the value in BUF\_LEN when BUFx\_RDY is being cleared is the correct value for that DMA buffer.

The BASEx\_PTRx and BUF\_LEN values should be stable before software clears BUFx\_RDY.

**Remark:** The DMA buffer sizes must be a multiple of 64 bytes. SIZE is a static configuration register and must not be changed during GPIO operation.

#### Pattern Generation using timestamps

This form of pattern generation is the inverse of event timestamping. Software fills a (per signal) DMA buffer with timed events (31-bit timestamp + 1-bit direction). The hardware performs the scheduled event on a selected GPIO pin when the reference timestamp clock reaches this value.

# 3.2 Error Signaling

The MMIO port does not support error signaling. Reads from invalid addresses return the value "0", writes to invalid addresses are ignored. The errors are not reported at system level.

Changing MMIO registers of an initiated DDR SDRAM Controller may cause incorrect behavior. Forcing the DDR controller into halt mode, programming MMIO registers while in halt mode, then unhalting the DDR controller when the MMIO registers have been programmed is the suggested series of actions to take.

# 3.3 Latency

The DDR SDRAM Controller uses two pipeline stages to calculate the command(s) that will be issued to the DDR memories after a MTL command is accepted by the DDR controller.

We will describe the latency of a MTL read command. Assume we have a MTL read command on one of the MTL ports in cycle 0 which is accepted by the DDR controller. In cycle 1, the DDR controller will determine the first DDR burst for the MTL read command. In cycle 2, the DDR SDRAM Controller will determine the DDR commands that need to be sent out on the DDR interface (we assume we do not have

The outputs of all mixers are connected to the back-end part of the QVCP --- the output formatter. The output formatter performs all necessary functions to adopt the final composited image to the display requirements. Among the functions performed in the output formatter are: gamma correction, chrominance downsampling, output formatting, and VBI insertion.

# 2.3 Layer Resources and Functions

This section focuses on the elements comprising a layer. Note that all of the described modules are present in each layer exactly once, the justification being that they (elements) are either always needed for the basic operation of a layer or they are so small (in design size) that assigning them to the resource pool would be inefficient due to the multiplexing and routing overhead associated with the pool elements.

#### 2.3.1 Memory Access Control (DMA CTRL)

QVCP has 4 DMA agents, each of which connects to a 512-Byte buffer in the DMA adapter. DMA agents 1-2 are hard coded to layer1-2 respectively. DMA4 is used to fetch a VBI packet or a data packet for DMA-based control-register programming. DMA3 can be assigned to any of the two layers for supporting the semi-planar input format.

For video data fetches, the request block size is equal to the initial layer width (before horizontal scaling). If start fetch is disabled (i.e., Enable bit 31 of register 0x10E2C8 is programmed to zero), the first DMA request starts right after the layer enable is asserted and QVCP works as if prefetch is enabled. However, if start fetch is enabled (i.e., Enable bit 31 of register 0x10E2C8 is programmed to one), then the DMA starts fetching only when QVCP s internal line counter reaches the 12-bit line threshold programmed in the Fetch Start bits [11:0] of register 0x10E2C8. Data fetched for the first field (interlaced) or frame (progressive) is not used and is flushed at the FCU (Flow Control Unit) FIFO. Thereafter, the pixels for the second field/frame start marching into the FCU FIFO, waiting for the correct layer position. The FCU FIFO releases pixels only if the x.v coordinates generated by the Screen Timing Generator (STG) match the layer position. In case of an interlaced output, the field ID is also checked. The DMA fetch request for the next active video line starts as soon as the last active pixel of the current line moves from the adapter FIFO into the processing pipeline and this request must be served in time to guarantee that the first active pixel of this new line is ready at the FCU FIFO before the STG signals the start of active video for the new line.

The DMA-based register-control programming only needs to be done once for a particular display scenario; thus, DMA4 is mainly used for VBI data fetch. QVCP is designed such that a VBI packet will only be inserted in the horizontal blanking interval and only one VBI packet is allowed in any one horizontal blanking interval. To insert this packet, there are two DMA requests. The first request has a block size of 1 since it is used to fetch only the header (which contains the size information). The second request is meant to fetch actual data of the required size and so, the maximum DMA request size (for the second request) is equal the length of horizontal blanking interval. The VBI data for the current horizontal blanking interval is always fetched in advance and stored in the DMA buffer (in the adapter). After sending out this prefetched data, the VBI DMA control unit (DMA4) requests a prefetch of the next packet (and correct operation requires that the sequence of the next two fetches must

| Table 20: | QVCP 1 | Registers | Continued |

|-----------|--------|-----------|-----------|

|-----------|--------|-----------|-----------|

| Bit    | Symbol         | Acces<br>s  | Value       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|----------------|-------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8      | PF_10B_MODE    | R/W         | 0           | 10-bit Input format modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|        |                |             |             | 0: 8-bit input format mode<br>1: 10-bit input format mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7:0    | PF_IPFMT       | R/W         | 0           | Input Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        |                |             |             | 08 (hex) = YUV 4:2:2 semi-planar<br>24 (hex) = 1-bit indexed <sup>Note1</sup><br>45 (hex) = 2-bit indexed <sup>Note1</sup><br>66 (hex) = 4-bit indexed <sup>Note1</sup><br>87 (hex) = 8-bit indexed <sup>Note1</sup><br>A0 (hex) = packed YUY2 4:2:2<br>A1 (hex) = packed UYVY 4:2:2<br>AC (hex) = 16 bits variable contents 4:4:4<br>CC (hex) = 24 bits variable contents 4:4:4<br>E8 (hex) = 32 bits variable contents 4:4:4<br>E8 (hex) = 32 bits variable contents 4:4:4<br>Note1: For indexed modes Variable format register should be set<br>'E7E7E7E7'<br>Note 2: Only YUV 4:2:2 semi-plana format (08) and packed formats<br>(A0 & A1) are available when PF_10B_MODE is on |

| Offset | 0x10 E2C0 Lay  | ver Backgro | und Color   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 31     | BG_enable      | R/W         | 0           | This bit enables the replacement of the previous input by the specified background color.<br>1 = Replace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|        |                |             |             | 0 = Use previous mixer output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 30:24  | Unused         |             | -           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 23:16  | Upper          | R/W         | 0           | Upper channel of the background color (R/Y) (two's complement)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 15:8   | Middle         | R/W         | 0           | Middle channel of the background color (G/U) (two's complement)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7:0    | Lower          | R/W         | 0           | Lower channel of the background color (B/V) (two's complement)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Offset | 0x10 E2C4 Var  | iable Forma | at register |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 31:29  | PF_SIZE_A[2:0] | R/W         | 0           | Size component for alpha<br>Number of bits minus 1 (e.g. 7 => 8 bits per component)<br>Not available when PF_10B_MODE is on.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 28:24  | PF_OFFS_A[4:0] | R/W         | 0           | Offset component for alpha<br>Index of MSB position within 32-bit word (0-31)<br>Not available when PF_10B_MODE is on.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 23:21  | PF_SIZE_L[2:0] | R/W         | 0           | Size component for V or B<br>Number of bits minus 1 (e.g. 7 => 8 bits per component)<br>Not available when PF_10B_MODE is on.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 20:16  | PF_OFFS_L[4:0] | R/W         | 0           | Offset component for V or B<br>Index of MSB position within 32-bit word (0-31)<br>Not available when PF_10B_MODE is on.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 15:13  | PF_SIZE_M[2:0] | R/W         | 0           | Size component for U or G<br>Number of bits minus 1 (e.g. 7 => 8 bits per component)<br>Not available when PF_10B_MODE is on.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 12:8   | PF_OFFS_M[4:0] | R/W         | 0           | Offset component for U or G<br>Index of MSB position within 32-bit word (0-31)<br>Not available when PF_10B_MODE is on.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

#### **Enabling the Dither Units**

Immediately after the Dither unit is enabled or after a reset, the unit waits for the beginning of a newly-captured image. Only then the unit starts dithering.

Once the Dither unit is operational (enabled), it keeps track of the order in which the images arrive: we refer to the very first image at the unit dither as the *even* image, the second image as the *odd* image, and so on. A frame here is defined as two images: an even image followed by an odd image. This maintained state does not depend on the selected alternation options, it is maintained as long as the Dither unit is enabled. Any alternative activity corresponds to the internally-maintained state of a frame and field (even or odd) and has nothing to do if the signal is coming from the top or the bottom field.

Dithering operation also distinguishes between even and odd pixel-components of the same type (either Y, U or V) in a line.

The first occurrence of a Y or U or V component in the first line in the first received image is considered to be an **even** occurrence (or *set*).

#### 2.5.5 Horizontal Video Filters (Sampling, Scaling, Color Space Conversion)

#### Interpolation Filter (Upsampling)

All horizontal video processing is based on equidistant sampled components. All 4:2:2 video streams, therefore, have to be upsampled before being scaled horizontally. The interpolation FIR filter used can interpolate interspersed or co-sited chroma samples. Mirroring of samples at the field boundaries compensate for run-in and run-out conditions of the filter.

The following coefficients are used:

- co-sited: A=(1) and B=(-3,19,19,-3)/32

- interspersed: C=(-1,5,13,-1)/16 and D=(-1,13,5,-1)/16

#### **Decimation Filter (Downsampling)**

After horizontal processing, the chrominance may be down-sampled to reduce memory bandwidth or allow a higher-quality vertical processing not available otherwise. Mirroring of samples at the field boundaries compensate for run in and run out conditions of the filter.

The following coefficients are used:

- co-sited: low pass A=(1,2,1)/4 or sub-sample A=(0,1,0)

- interspersed: B=(-3,19,19,-3)/32

#### Normal Polyphase Filter (Horizontal Scaling)

The normal polyphase filter can be used to zoom up (upscale) or downscale a video image. Depending on the number of components, the filter is used with 6 taps (three-component mode) or 3 taps (four-component mode).

#### **Capture Enable Mode**

Using the *cfen* bits, video capture can be limited to odd or even or both fields. If both fields are to be captured, the capture starts with the next odd field.

The status of the *osm* (one-shot) bit in the mode-control-register specifies the capture mode (one-shot or continuous):

- If *osm*=0, the corresponding incoming video stream is captured continuously. For example, in a video conference application the vanity image would be a continuous stream to the frame buffer.

- If *osm*=1, the corresponding incoming video stream is captured one field or frame at a time (depending on the *cfen* bits).

Programming hint: In a video conference application the captured image would be a one-shot stream to the host memory. If you write *osm*=1 and select field/frame in the register, it is captured on the next VSYNC and *cfen* bits are cleared to 0. To capture the next image, the *cfen and osm* bits must be reprogrammed.

#### **Address Generation**

The line address is generated by loading the base address from the corresponding register set at the beginning of each field and adding the line pitch to it at the beginning of every new line. The lower three bits of the first three base address registers are used as an intra-long-word offset for the left-most pixel components of each line. The offset has to be a multiple of the number of bytes per component.

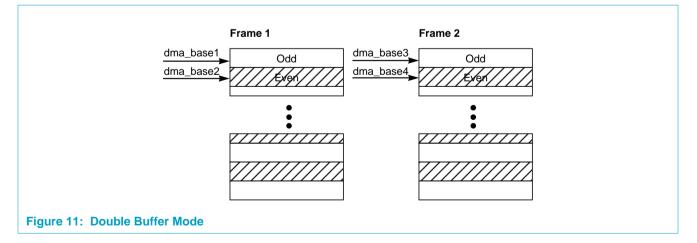

#### **Double Buffer Mode**

To avoid line tear caused by trying to display a frame at the same time that it is being updated, a double buffer mode is available. In this double buffer mode, a second set of DMA base addresses is available. After capturing and storing one complete frame in the location described by one set, the other set is used for the next frame. The idea is illustrated in Figure 11.

If the alpha value, after horizontal and vertical processing, is below a fixed threshold (0x80), the sample is replaced by the color key.

#### • Fixed Alpha Insert

The alpha value defined in the Color Key register is inserted, as the fourth component after horizontal and vertical processing, in the PSU unit (if CKEY\_K2A=1).

#### 2.4.7 Alpha Processing

Alpha processing is only available when the horizontal and vertical filter blocks are either bypassed or operated in the four-component mode. If the horizontal filter is used for color space conversion, the alpha information is kept time-aligned with the other three components.

#### 2.4.8 Video Data Output

After processing the video stream, the MBS can split the video data into one or more (up to three) different streams. For each stream, there is a memory base address. There are two line-pitch registers further defining the DMA streams. The number of streams (planes) is defined by the output-format register. Depending on its value, the video components get packed into 64-bit words. These words then get buffered and transferred to the external memory in more effective clusters. A list of the supported output video formats is shown in <u>Table 6</u>. Packing of a pixel into 64-bit units is always done from right to left, while bytes within one pixel unit are ordered according to the Endian settings (according to the global Endian setting, the Endian bit in the output format register can invert the setting).

| Format                     | 3<br>1 | 3<br>0     | 2<br>9 | 2<br>8 | 2<br>7 | 2<br>6 | 2<br>5 | 2<br>4 | 2<br>3 | 2<br>2 | 2<br>1 | 2<br>0 | 1<br>9 | 1<br>8 | 1<br>7 | 1<br>6 | 1<br>5 | 1<br>4 | 1<br>3 | 1<br>2 | 1<br>1 | 1<br>0 | 9 | 8 | 76    | 54              | 32 <sup>-</sup> | 10 |

|----------------------------|--------|------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---|---|-------|-----------------|-----------------|----|

| planar YUV or RGB          | •      | ine        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |   |   | Y8 or | R8              |                 |    |

| (4:4:4, 4:2:2 or<br>4:2:0) |        | ine<br>ine |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |   |   | U8 oi | <sup>.</sup> G8 |                 |    |

| )                          | 1.0    |            |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |   |   | V8 or | B8              |                 |    |

| semi planar YUV            | •      | ine        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |   |   | Y8 or | R8              |                 |    |

| (4:2:2 or 4:2:0)           | pla    | ine        | #2     |        |        |        |        |        |        |        |        |        |        |        |        |        | V      | 3      |        |        |        |        |   |   | U8    |                 |                 |    |

| packed 4/4/4 RGBa          |        |            |        |        |        |        |        |        |        |        |        |        |        |        |        |        | al     | oha    |        |        | R4     | 1      |   |   | G4    |                 | B4              |    |

| packed 4/5/3 RGBa          |        |            |        |        |        |        |        |        |        |        |        |        |        |        |        |        | al     | oha    |        |        | R4     | 1      |   |   | G5    |                 | B3              |    |

| packed 5/6/5 RGB           |        |            |        |        |        |        |        |        |        |        |        |        |        |        |        |        | R      | 5      |        |        |        | G      | 6 |   |       | B5              | 5               |    |

| packed YUY2 4:2:2          |        |            |        |        |        |        |        |        |        |        |        |        |        |        |        |        | U      | 3 or   | V8     |        |        |        |   |   | Y8    |                 |                 |    |

| packed UYVY 4:2:2          |        |            |        |        |        |        |        |        |        |        |        |        |        |        |        |        | Y٤     | 3      |        |        |        |        |   |   | U8 oi | · V8            |                 |    |

| packed 888 RGB(a)          | (al    | pha        | ı)     |        |        |        |        |        | R8     | s or   | Y8     |        |        |        |        |        | G      | 3 or   | U8     |        |        |        |   |   | B8 or | · V8            |                 |    |

| packed 4:4:4<br>VYU(a)     | (al    | pha        | 1)     |        |        |        |        |        | V8     | •      |        |        |        |        |        |        | Y      | 3      |        |        |        |        |   |   | U8    |                 |                 |    |

Table 6: Output Pixel Formats

**Remark:** <u>Table 6</u> shows location of the first 'pixel unit' within a 64 bit word in the little endian mode. The selected endian mode will affect the position of the components within multi-byte pixel units!

| Table 8: Mer | nory Based Scale | r (MBS) Registers | Continued |

|--------------|------------------|-------------------|-----------|

|--------------|------------------|-------------------|-----------|

| BitSymbolsValueDescription29:28CKEY_A2KR/W0Alpha mode to color key convert<br>00 = no alpha manipulation<br>01 = reserved<br>10 = reserved<br>11 = alpha to color key convert<br>Samples with alpha component below 80 (hex) are replaced with<br>values defined in CKEY_COMP 1-3.27:26CKEY_REPLACER/W0Color keying replace mode<br>00 = no color component manipulation<br>01 = replace keyed color components with black (10, 10, 10)<br>10 = replace keyed color components with black (10, 10, 10)<br>11 = replace keyed color components with last non-key value25:24ReservedImage: Market the term of term of the term of term                                                                                                                                                                                               |        |                         | Acces    |          |                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00 = no alpha manipulation<br>01 = reserved<br>11 = alpha to color key convert<br>Samples with alpha component below 80 (hex) are replaced with<br>Values defined in CKEY_COMP 1-3.       27:26     CKEY_REPLACE     R/W     0     Color keying replace mode<br>00 = no color component simulpulation<br>01 = replace keyed color components with black (10, 10, 10)<br>10 = replace keyed color components with black (10, 10, 10)<br>10 = replace keyed color components with black (10, 10, 10)<br>11 = replace keyed color components with last non-key value       25:24     Reserved     Color key mask component 1<br>Defines bits of color component with last non-key value       25:25     CKEY_MASK1     R/W     0     Color key mask component 1<br>Defines bits of color component that are compared against color ke<br>value setting to key sample.       15: 8     CKEY_MASK3     R/W     0     Color key mask component 1<br>Defines bits of color component that are compared against color ke<br>value setting to key sample.       21: 16     CKEY_ALPHA     R/W     0     Alpha value<br>Defines bits of color component 1<br>Defines value of color key for component 1<br>Defines value of color key for component 1 (red or Y).       15: 8     CKEY_COMP1     R/W     0     Color key component 1<br>Defines value of color key for component 1 (red or Y).       15: 8     CKEY_COMP2     R/W     0     Color key component 1<br>Defines value of color key for component 2 (green or U).       7: 0     CKEY_COMP3     R/W     0     Color key component 3<br>Defines value of color key for component 3 (blue or V).       15: 8     CKEY_COMP3<                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit    | Symbol                  |          | Value    | Description                                                                                                                                                                                                                                                  |

| 00 = no color component manipulation<br>01 = replace keyed color components with black (10, 10, 10)<br>10 = replace keyed color components with at non-key value       25:24     Reserved     Image: Color key mask component 1<br>Defines bits of color component that are compared against color key<br>value setting to key sample.       15:8     CKEY_MASK2     R/W     0     Color key mask component 1<br>Defines bits of color component that are compared against color key<br>value setting to key sample.       15:8     CKEY_MASK3     R/W     0     Color key mask component 2<br>Defines bits of color component that are compared against color key<br>value setting to key sample.       7:0     CKEY_MASK3     R/W     0     Color key mask component 3<br>Defines bits of color component that are compared against color key<br>value setting to key sample.       31:24     CKEY_COMP1     R/W     0     Alpha value<br>Defines to key for component 1 (red or Y).       15:8     CKEY_COMP2     R/W     0     Color key component 1<br>Defines value of color key for component 2 (green or U).       15:8     CKEY_COMP3     R/W     0     Color key component 2<br>Defines value of color key for component 3 (blue or V).       15:8     CKEY_COMP3     R/W     0     Color key component 3<br>Defines value of color key for component 3 (blue or V).       16:0     CKEY_COMP3     R/W     0     Color key component 3<br>Defines value of color key for component 3 (blue or V).       17:0     CKEY_COMP3     R/W     0     Color key compon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 29:28  | CKEY_A2K                | R/W      | 0        | 00 = no alpha manipulation<br>01 = reserved<br>10 = reserved<br>11 = alpha to color key convert<br>Samples with alpha component below 80 (hex) are replaced with                                                                                             |

| 23: 16CKEY_MASK1R/W0Color key mask component 1<br>Defines bits of color component that are compared against color key<br>value setting to key sample.15: 8CKEY_MASK2R/W0Color key mask component 2<br>Defines bits of color component that are compared against color key<br>value setting to key sample.7: 0CKEY_MASK3R/W0Color key mask component 3<br>Defines bits of color component that are compared against color key<br>value setting to key sample.7: 10C284Color Key Components7: 21CKEY_ALPHAR/W023: 16CKEY_COMP1R/W023: 16CKEY_COMP1R/W024: 16CKEY_COMP2R/W07: 0CKEY_COMP3R/W07: 0CSU_COMP3R/W07: 0CKEY_COMP3R/W07: 0CSU_COMP3R/W07: 0CSU_COMP3R/W07: 0CSU_COMP3R/W07: 0CSU_COMP3R/W00Sea address mode<br>0 = single set (e.g. progressive video source)<br>base 1-3,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 27:26  | CKEY_REPLACE            | R/W      | 0        | 00 = no color component manipulation<br>01 = replace keyed color components with black (10, 10, 10)<br>10 = replace keyed color components with gray (80, 80, 80)                                                                                            |

| Defines bits of color component that are compared against color ke<br>value setting to key sample.15: 8CKEY_MASK2R/W0Color key mask component 2<br>Defines bits of color component that are compared against color ke<br>value setting to key sample.7: 0CKEY_MASK3R/W0Color key mask component 3<br>Defines bits of color component that are compared against color ke<br>value setting to key sample.0ffset UX10 C284Color Key Components31: 24CKEY_ALPHAR/W0Alpha value<br>Defines the alpha value to be used for keyed samples.23: 16CKEY_COMP1R/W0Color key component 1<br>Defines value of color key for component 1 (red or Y).15: 8CKEY_COMP2R/W0Color key component 2<br>Defines value of color key for component 1 (red or Y).15: 8CKEY_COMP3R/W0Color key component 2<br>Defines value of color key for component 2 (green or U).7: 0CKEY_COMP3R/W0Color key component 3<br>Defines value of color key for component 3 (blue or V).Video Utput Format Control RegistersOffset UT 0 C300Video Output Format31:30PSU_BAMODER/W0Base address mode<br>00 = single set (e.g. progressive video source)<br>base 1-3 according to number of planes (plane 1-3)<br>01 = alternate sets each line (e.g. anti-ficker mode)<br>base 4-6, second line out, etc. (plane 1-3)<br>base 4-6, second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 25:24  | Reserved                |          |          |                                                                                                                                                                                                                                                              |

| Defines bits of color component that are compared against color key<br>value setting to key sample.7: 0CKEY_MASK3R/W0Color key mask component 3<br>Defines bits of color component that are compared against color key<br>value setting to key sample.0ffset 0x10 C284Color Key Components31: 24CKEY_ALPHAR/W0Alpha value<br>Defines the alpha value to be used for keyed samples.23: 16CKEY_COMP1R/W0Color key component 1<br>Defines value of color key for component 1 (red or Y).15: 8CKEY_COMP2R/W0Color key component 2<br>Defines value of color key for component 2 (green or U).7: 0CKEY_COMP3R/W0Color key component 3<br>Defines value of color key for component 3 (blue or V).Video Output Format Control RegistersUties output format Control Registers0113: 0PSU_BAMODER/W0Base address mode<br>00 = single set (e.g. progressive video source)<br>base 1-3 according to number of planes (plane 1-3)<br>01 = alternate sets each line (e.g. anti-flicker mode)<br>base 1-3, first line out, etc. (plane 1-3)<br>01 = alternate sets each line (e.g. anti-flicker mode)<br>base 1-3, first line out, etc. (plane 1-3)<br>01 = alternate sets each line (e.g. anti-flicker mode)<br>base 1-3, first line out, etc. (plane 1-3)<br>01 = alternate sets each line (e.g. anti-flicker mode)<br>base 1-3, first line out, etc. (plane 1-3)<br>01 = alternate sets each line (e.g. anti-flicker mode)<br>base 1-3, first line out, etc. (plane 1-3)<br>01 = alternate sets each line (e.g. anti-flicker mode)<br>base 1-3, first line out, etc. (plane 1-3)<br>01 = alternate sets each line (e.g. anti-flicker mode)<br>base 1-3, first line out, etc. (plane 1-3)<br>01 = alterna                                                                                                                                                                                                                                                                                                                                                                                                                   | 23: 16 | CKEY_MASK1              | R/W      | 0        | Defines bits of color component that are compared against color key                                                                                                                                                                                          |

| Offset Dx10 C284       Color Key Components         31: 24       CKEY_ALPHA       R/W       0       Alpha value<br>Defines the alpha value to be used for keyed samples.         23: 16       CKEY_COMP1       R/W       0       Color key component 1<br>Defines value of color key for component 1 (red or Y).         15: 8       CKEY_COMP2       R/W       0       Color key component 2<br>Defines value of color key for component 2 (green or U).         7: 0       CKEY_COMP3       R/W       0       Color key component 3<br>Defines value of color key for component 3 (blue or V).         Video Output Format Control Registers         Offset V10 C300       Video Output Format         31:30       PSU_BAMODE       R/W       0       Base address mode<br>00 = single set (e.g. anti-flicker mode)<br>base 1-3 according to number of planes (plane 1-3)<br>01 = alternate sets each line (e.g. anti-flicker mode)<br>base 4-3, first line out, etc. (plane 1-3)<br>01 = alternate sets each line (e.g. anti-flicker mode)<br>base 4-3, first line out, etc. (plane 1-3)<br>01 × = reserved         29:14       Reserved       Image: Color c                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15: 8  | CKEY_MASK2              | R/W      | 0        | Defines bits of color component that are compared against color key                                                                                                                                                                                          |

| 31: 24CKEY_ALPHAR/W0Alpha value<br>Defines the alpha value to be used for keyed samples.23: 16CKEY_COMP1R/W0Color key component 1<br>Defines value of color key for component 1 (red or Y).15: 8CKEY_COMP2R/W0Color key component 2<br>Defines value of color key for component 2 (green or U).7: 0CKEY_COMP3R/W0Color key component 3<br>Defines value of color key for component 3 (blue or V).Video Utput Format Control RegistersOffset V10 C300 Video Utput Format31:30PSU_BAMODER/W0Base address mode<br>00 = single set (e.g. progressive video source)<br>base 1-3 according to number of planes (plane 1-3)<br>01 = alternate sets each line (e.g. anti-flicker mode)<br>base 1-3, first line out, etc. (plane 1-3)<br>1x = reserved29:14ReservedImage: R/W0Output format endian mode<br>0: same as system endian mode<br>1: opposite of system endian mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7: 0   | CKEY_MASK3              | R/W      | 0        | Defines bits of color component that are compared against color key                                                                                                                                                                                          |